Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                          |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 39                                                          |

| Program Memory Size        | 60KB (60K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 2K x 8                                                      |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 16x12b                                                  |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-LQFP                                                     |

| Supplier Device Package    | 48-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dn60amlf |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

Title

Page

| Chapter 1  | Device Overview                                  |

|------------|--------------------------------------------------|

| Chapter 2  | Pins and Connections23                           |

| Chapter 3  | Modes of Operation                               |

| Chapter 4  | Memory                                           |

| Chapter 5  | Resets, Interrupts, and General System Control63 |

| Chapter 6  | Parallel Input/Output Control79                  |

| Chapter 7  | Central Processor Unit (S08CPUV3)109             |

| Chapter 8  | Multi-Purpose Clock Generator (S08MCGV1)         |

| Chapter 9  | Analog Comparator (S08ACMPV3)161                 |

| Chapter 10 | Analog-to-Digital Converter (S08ADC12V1)167      |

| Chapter 11 | Inter-Integrated Circuit (S08IICV2)193           |

| Chapter 12 | Serial Peripheral Interface (S08SPIV3)213        |

| Chapter 13 | Serial Communications Interface (S08SCIV4)229    |

| Chapter 14 | Real-Time Counter (S08RTCV1)                     |

| Chapter 15 | Timer Pulse-Width Modulator (S08TPMV3)259        |

| Chapter 16 | Development Support                              |

| Appendix A | Electrical Characteristics                       |

| Appendix B | Timer Pulse-Width Modulator (TPMV2)              |

| Appendix C | Ordering Information and Mechanical Drawings     |

**Chapter 2 Pins and Connections**

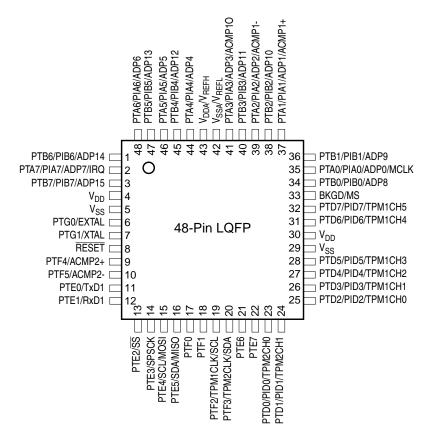

Figure 2-2. 48-Pin LQFP

#### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pull-up devices or change the direction of unused or non-bonded pins to outputs so they do not float.

### 4.4 RAM

The MC9S08DN60 Series includes static RAM. The locations in RAM below 0x0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data while the MCU is in low-power wait, stop2, or stop3 mode. At power-on the contents of RAM are uninitialized. RAM data is unaffected by any reset if the supply voltage does not drop below the minimum value for RAM retention ( $V_{RAM}$ ).

For compatibility with M68HC05 MCUs, the HCS08 resets the stack pointer to 0x00FF. In the MC9S08DN60 Series, it is usually best to reinitialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables. Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM in the Freescale Semiconductor equate file).

LDHX #RamLast+1 ;point one past RAM TXS ;SP<-(H:X-1)

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or code executing from non-secure memory. See Section 4.5.9, "Security", for a detailed description of the security feature.

## 4.5 Flash and EEPROM

MC9S08DN60 Series devices include Flash and EEPROM memory intended primarily for program and data storage. In-circuit programming allows the operating program and data to be loaded into Flash and EEPROM, respectively, after final assembly of the application product. It is possible to program the arrays through the single-wire background debug interface. Because no special voltages are needed for erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I*, Freescale Semiconductor document order number HCS08RMv1.

### 4.5.1 Features

Features of the Flash and EEPROM memory include:

- Array size (see Table 1-1 for exact array sizes)

- Flash sector size: 768 bytes

- EEPROM sector size: selectable 4-byte or 8-byte sector mapping operation

- Single power supply program and erase

- Command interface for fast program and erase operation

- Up to 100,000 program/erase cycles at typical voltage and temperature

- Flexible block protection and vector redirection

- Security feature for Flash, EEPROM, and RAM

| Table 4-14. FSTAT | <b>Register Field</b> | Descriptions | (continued) |

|-------------------|-----------------------|--------------|-------------|

|-------------------|-----------------------|--------------|-------------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>FACCERR | Access Error Flag — FACCERR is set automatically when the proper command sequence is not obeyed exactly (the erroneous command is ignored), if a program or erase operation is attempted before the FCDIV register has been initialized, or if the MCU enters stop while a command was in progress. For a more detailed discussion of the exact actions that are considered access errors, see Section 4.5.6, "Access Errors." FACCERR is cleared by writing a 1 to FACCERR. Writing a 0 to FACCERR has no meaning or effect.<br>0 No access error.<br>1 An access error has occurred.                      |

| 2<br>FBLANK  | <ul> <li>Verified as All Blank (erased) Flag — FBLANK is set automatically at the conclusion of a blank check command if the entire Flash or EEPROM array was verified to be erased. FBLANK is cleared by clearing FCBEF to write a new valid command. Writing to FBLANK has no meaning or effect.</li> <li>O After a blank check command is completed and FCCF = 1, FBLANK = 0 indicates the Flash or EEPROM array is not completely erased.</li> <li>1 After a blank check command is completed and FCCF = 1, FBLANK = 1 indicates the Flash or EEPROM array is completely erased (all 0xFFF).</li> </ul> |

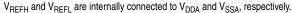

### 4.5.11.6 Flash and EEPROM Command Register (FCMD)

Only six command codes are recognized in normal user modes, as shown in Table 4-15. All other command codes are illegal and generate an access error. Refer to Section 4.5.3, "Program and Erase Command Execution," for a detailed discussion of Flash and EEPROM programming and erase operations.

Figure 4-10. Flash and EEPROM Command Register (FCMD)

| Command            | FCMD | Equate File Label |

|--------------------|------|-------------------|

| Blank check        | 0x05 | mBlank            |

| Byte program       | 0x20 | mByteProg         |

| Burst program      | 0x25 | mBurstProg        |

| Sector erase       | 0x40 | mSectorErase      |

| Mass erase         | 0x41 | mMassErase        |

| Sector erase abort | 0x47 | mEraseAbort       |

It is not necessary to perform a blank check command after a mass erase operation. Only blank check is required as part of the security unlocking mechanism.

**Chapter 6 Parallel Input/Output Control**

### 6.5.2 Port B Registers

Port B is controlled by the registers listed below.

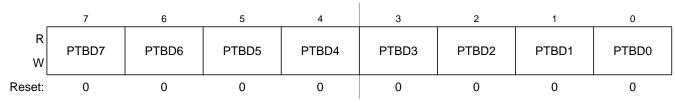

### 6.5.2.1 Port B Data Register (PTBD)

#### Figure 6-11. Port B Data Register (PTBD)

#### Table 6-9. PTBD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups/pull-downs disabled. |

### 6.5.2.2 Port B Data Direction Register (PTBDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-12. Port B Data Direction Register (PTBDD)

#### Table 6-10. PTBDD Register Field Descriptions

| Field | Description                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data Direction for Port B Bits</b> — These read/write bits control the direction of port B pins and what is read for PTBD reads.                                                 |

|       | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn.</li> </ul> |

| Table 7-5. Opcode Ma    |                        |                       |                       |                       |                       |        |                       |                        |                         | 012)                 |                      |                      |                      |                      |                     |

|-------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------|-----------------------|------------------------|-------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

|                         | ipulation              | Branch                | Read-Modify-Write     |                       |                       |        |                       |                        | trol                    | Register/Memory      |                      |                      |                      |                      |                     |

| 00 5                    |                        | 20 3                  | 30 5                  | 40 1                  | 50 1                  | 60 5   | 70 4                  | 80 9                   | 90 3                    | A0 2                 | B0 3                 | C0 4                 | D0 4                 | E0 3                 | F0 3                |

| BRSET0                  |                        | BRA                   | NEG                   | NEGA                  | NEGX                  | NEG    | NEG                   | RTI                    | BGE                     | SUB                  | SUB                  | SUB                  | SUB                  | SUB                  | SUB                 |

| 3 DIR                   |                        | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  | 1 INH                  | 2 REL                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 01 5                    | 11 5                   | 21 3                  | 31 5                  | 41 4                  | 51 4                  | 61 5   | 71 5                  | 81 6                   | 91 3                    | A1 2                 | B1 3                 | C1 4                 | D1 4                 | E1 3                 | F1 3                |

| BRCLR0                  | BCLR0                  | BRN                   | CBEQ                  | CBEQA                 | CBEQX                 | CBEQ   | CBEQ                  | RTS                    | BLT                     | CMP                  | CMP                  | CMP                  | CMP                  | CMP                  | CMP                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 3 DIR                 | 3 IMM                 | 3 IMM                 | 3 IX1+ | 2 IX+                 | 1 INH                  | 2 REL                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 02 5                    | 12 5                   | 22 3                  | 32 5                  | 42 5                  | 52 6                  | 62 1   | 72 1                  | 82 5+                  | 92 3                    | A2 2                 | B2 3                 | C2 4                 | D2 4                 | E2 3                 | F2 3                |

| BRSET1                  | BSET1                  | BHI                   | LDHX                  | MUL                   | DIV                   | NSA    | DAA                   | BGND                   | BGT                     | SBC                  | SBC                  | SBC                  | SBC                  | SBC                  | SBC                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 3 EXT                 | 1 INH                 | 1 INH                 | 1 INH  | 1 INH                 | 1 INH                  | 2 REL                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 03 5                    | 13 5                   | 23 3                  | 33 5                  | 43 1                  | 53 1                  | 63 5   | 73 4                  | 83 11                  | 93 3                    | A3 2                 | B3 3                 | C3 4                 | D3 4                 | E3 3                 | F3 3                |

| BRCLR1                  | BCLR1                  | BLS                   | COM                   | COMA                  | COMX                  | COM    | COM                   | SWI                    | BLE                     | CPX                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  | 1 INH                  | 2 REL                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 04 5                    | 14 5                   | 24 3                  | 34 5                  | 44 1                  | 54 1                  | 64 5   | 74 4                  | 84 1                   | 94 2                    | A4 2                 | B4 3                 | C4 4                 | D4 4                 | E4 3                 | F4 3                |

| BRSET2                  | BSET2                  | BCC                   | LSR                   | LSRA                  | LSRX                  | LSR    | LSR                   | TAP                    | TXS                     | AND                  | AND                  | AND                  | AND                  | AND                  | AND                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  | 1 INH                  | 1 INH                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 05 5                    | 15 5                   | 25 3                  | 35 4                  | 45 3                  | 55 4                  | 65 3   | 75 5                  | 85 1                   | 95 2                    | A5 2                 | B5 3                 | C5 4                 | D5 4                 | E5 3                 | F5 3                |

| BRCLR2                  | BCLR2                  | BCS                   | STHX                  | LDHX                  | LDHX                  | CPHX   | CPHX                  | TPA                    | TSX                     | BIT                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 3 IMM                 | 2 DIR                 | 3 IMM  | 2 DIR                 | 1 INH                  | 1 INH                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 06 5                    | 16 5                   | 26 3                  | 36 5                  | 46 1                  | 56 1                  | 66 5   | 76 4                  | 86 3                   | 96 5                    | A6 2                 | B6 3                 | C6 4                 | D6 4                 | E6 3                 | F6 3                |

| BRSET3                  | BSET3                  | BNE                   | ROR                   | RORA                  | RORX                  | ROR    | ROR                   | PULA                   | STHX                    | LDA                  | LDA                  | LDA                  | LDA                  | LDA                  | LDA                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  | 1 INH                  | 3 EXT                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 07 5                    | 17 5                   | 27 3                  | 37 5                  | 47 1                  | 57 1                  | 67 5   | 77 4                  | 87 2                   | 97 1                    | A7 2                 | B7 3                 | C7 4                 | D7 4                 | E7 3                 | F7 2                |

| BRCLR3                  | BCLR3                  | BEQ                   | ASR                   | ASRA                  | ASRX                  | ASR    | ASR                   | PSHA                   | TAX                     | AIS                  | STA                  | STA                  | STA                  | STA                  | STA                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  | 1 INH                  | 1 INH                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 08 5                    |                        | 28 3                  | 38 5                  | 48 1                  | 58 1                  | 68 5   | 78 4                  | 88 3                   | 98 1                    | A8 2                 | B8 3                 | C8 4                 | D8 4                 | E8 3                 | F8 3                |

| BRSET4                  |                        | BHCC                  | LSL                   | LSLA                  | LSLX                  | LSL    | LSL                   | PULX                   | CLC                     | EOR                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                 |

| 3 DIR                   |                        | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  | 1 INH                  | 1 INH                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 09 5<br>BRCLR4<br>3 DIR | 19 5                   | 29 3<br>BHCS<br>2 REL | 39 5<br>ROL<br>2 DIR  | 49 1<br>ROLA<br>1 INH | 59 1<br>ROLX<br>1 INH |        | 79 4<br>ROL<br>1 IX   | 89 2<br>PSHX<br>1 INH  | 99 1<br>SEC<br>1 INH    | A9 2<br>ADC<br>2 IMM |                      | C9 4<br>ADC<br>3 EXT |                      | E9 3<br>ADC<br>2 IX1 | F9 3<br>ADC<br>1 IX |

| 0A 5                    | 1A 5                   | 2A 3                  | 3A 5                  | 4A 1                  | 5A 1                  | 6A 5   | 7A 4                  | 8A 3                   | 9A 1                    | AA 2                 | BA 3                 | CA 4                 | DA 4                 | EA 3                 | FA 3                |

| BRSET5                  | BSET5                  | BPL                   | DEC                   | DECA                  | DECX                  | DEC    | DEC                   | PULH                   | CLI                     | ORA                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  | 1 INH                  | 1 INH                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0B 5                    | 1B 5                   | 2B 3                  | 3B 7                  | 4B 4                  | 5B 4                  | 6B 7   | 7B 6                  | 8B 2                   | 9B 1                    | AB 2                 | BB 3                 | CB 4                 | DB 4                 | EB 3                 | FB 3                |

| BRCLR5                  | BCLR5                  | BMI                   | DBNZ                  | DBNZA                 | DBNZX                 | DBNZ   | DBNZ                  | PSHH                   | SEI                     | ADD                  | ADD                  | ADD                  | ADD                  | ADD                  | ADD                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 3 DIR                 | 2 INH                 | 2 INH                 | 3 IX1  | 2 IX                  | 1 INH                  | 1 INH                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0C 5                    | 1C 5                   | 2C 3                  | 3C 5                  | 4C 1                  | 5C 1                  | 6C 5   | 7C 4                  | 8C 1                   | 9C 1                    |                      | BC 3                 | CC 4                 | DC 4                 | EC 3                 | FC 3                |

| BRSET6                  | BSET6                  | BMC                   | INC                   | INCA                  | INCX                  | INC    | INC                   | CLRH                   | RSP                     |                      | JMP                  | JMP                  | JMP                  | JMP                  | JMP                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  | 1 INH                  | 1 INH                   |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0D 5                    | 1D 5                   | 2D 3                  | 3D 4                  | 4D 1                  | 5D 1                  | 6D 4   | 7D 3                  |                        | 9D 1                    | AD 5                 | BD 5                 | CD 6                 | DD 6                 | ED 5                 | FD 5                |

| BRCLR6                  | BCLR6                  | BMS                   | TST                   | TSTA                  | TSTX                  | TST    | TST                   |                        | NOP                     | BSR                  | JSR                  | JSR                  | JSR                  | JSR                  | JSR                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  |                        | 1 INH                   | 2 REL                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0E 5<br>BRSET7<br>3 DIR | 1E 5<br>BSET7<br>2 DIR | 2E 3<br>BIL<br>2 REL  | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD   | 5E 5<br>MOV<br>2 DIX+ | MOV    | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | <sup>9E</sup><br>Page 2 | AE 2<br>LDX<br>2 IMM | BE 3<br>LDX<br>2 DIR | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5                    | 1F 5                   | 2F 3                  | 3F 5                  | 4F 1                  | 5F 1                  | 6F 5   | 7F 4                  | 8F 2+                  | 9F 1                    | AF 2                 | BF 3                 | CF 4                 | DF 4                 | EF 3                 | FF 2                |

| BRCLR7                  | BCLR7                  | BIH                   | CLR                   | CLRA                  | CLRX                  | CLR    | CLR                   | WAIT                   | TXA                     | AIX                  | STX                  | STX                  | STX                  | STX                  | STX                 |

| 3 DIR                   | 2 DIR                  | 2 REL                 | 2 DIR                 | 1 INH                 | 1 INH                 | 2 IX1  | 1 IX                  | 1 INH                  | 1 INH                   | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

#### Table 7-3. Opcode Map (Sheet 1 of 2)

| INH  | Inherent   |

|------|------------|

| IMM  | Immediate  |

| DIR  | Direct     |

| EXT  | Extended   |

| DD   | DIR to DIR |

| IX+D | IX+ to DIR |

|      |            |

REL IX IX1 IX2 IMD DIX+

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

MC9S08DN60 Series Data Sheet, Rev 3

Opcode in Hexadecimal F0 3 SUB 1 IX Addressing Mode Number of Bytes 1

#### Chapter 7 Central Processor Unit (S08CPUV3)

| Bit-Manipulation | Branch | Read-Modify-Write |  |  |                                  |  | Control Register/Memory |  |                        |      |      |                                                  |                        |                         |

|------------------|--------|-------------------|--|--|----------------------------------|--|-------------------------|--|------------------------|------|------|--------------------------------------------------|------------------------|-------------------------|

|                  |        |                   |  |  | 9E60 6<br>NEG<br>3 SP1           |  |                         |  |                        |      |      | 9ED0 5<br>SUB<br>4 SP2                           | 9EE0 4<br>SUB<br>3 SP1 |                         |

|                  |        |                   |  |  | 9E61 6<br>CBEQ<br>4 SP1          |  |                         |  |                        |      |      | 9ED1 5                                           | 9EE1 4                 |                         |

|                  |        |                   |  |  |                                  |  |                         |  |                        |      |      | 4 SP2<br>9ED2 5<br>SBC<br>4 SP2                  | 3 SP1                  |                         |

|                  |        |                   |  |  | 9E63 6<br>COM<br>3 SP1           |  |                         |  |                        |      |      | 9ED3 5<br>CPX<br>4 SP2<br>9ED4 5                 | CPX<br>3 SP1           | 9EF3 6<br>CPHX<br>3 SP1 |

|                  |        |                   |  |  | 9E64 6<br>LSR<br>3 SP1           |  |                         |  |                        |      |      | 9ED4 5<br>AND<br>4 SP2<br>9ED5 5<br>BIT<br>4 SP2 | 9EE4 4<br>AND<br>3 SP1 |                         |

|                  |        |                   |  |  |                                  |  |                         |  |                        |      |      | 9ED5 5<br>BIT<br>4 SP2<br>9ED6 5                 | 9EE5 4<br>BIT<br>3 SP1 |                         |

|                  |        |                   |  |  | 9E66 6<br>ROR<br>3 SP1<br>9E67 6 |  |                         |  |                        |      |      |                                                  |                        |                         |

|                  |        |                   |  |  | ASR<br>3 SP1                     |  |                         |  |                        |      |      | 4 SP2<br>9ED7 5<br>STA<br>4 SP2                  | 9EE7 4<br>STA<br>3 SP1 |                         |

|                  |        |                   |  |  | 9E68 6<br>LSL<br>3 SP1<br>9E69 6 |  |                         |  |                        |      |      | 9ED8 5<br>EOR<br>4 SP2                           | 9EE8 4<br>EOR<br>3 SP1 |                         |

|                  |        |                   |  |  | ROL<br>3 SP1                     |  |                         |  |                        |      |      | 9ED9 5<br>ADC<br>4 SP2                           | ADC<br>3 SP1           |                         |

|                  |        |                   |  |  | 9E6A 6<br>DEC<br>3 SP1<br>9E6B 8 |  |                         |  |                        |      |      | 9EDA 5<br>ORA<br>4 SP2                           | ORA<br>3 SP1           |                         |

|                  |        |                   |  |  | DBNZ<br>4 SP1                    |  |                         |  |                        |      |      | 9EDB 5<br>ADD<br>4 SP2                           | ADD                    |                         |

|                  |        |                   |  |  | 9E6C 6<br>INC<br>3 SP1           |  |                         |  |                        |      |      |                                                  |                        |                         |

|                  |        |                   |  |  | 9E6D 5<br>TST<br>3 SP1           |  |                         |  |                        |      |      |                                                  |                        |                         |

|                  |        |                   |  |  |                                  |  |                         |  | 9EAE 5<br>LDHX<br>2 IX | LDHX | Іпнх | 9EDE 5<br>LDX<br>4 SP2<br>9EDF 5                 | אחו                    |                         |

|                  |        |                   |  |  | 9E6F 6<br>CLR<br>3 SP1           |  |                         |  |                        |      |      | 9EDF 5<br>STX<br>4 SP2                           | 9EEF 4<br>STX<br>3 SP1 | 9EFF 5<br>STHX<br>3 SP1 |

#### Table 7-3. Opcode Map (Sheet 2 of 2)

Inherent Immediate Direct Extended DIR to DIR IX+ to DIR INH IMM DIR EXT DD IX+D

REL IX IX1 IX2 IMD DIX+ Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+ Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+ IX1+

Note: All Sheet 2 Opcodes are Preceded by the Page 2 Prebyte (9E)

Prebyte (9E) and Opcode in Hexadecimal 9E60 6 NEG Number of Bytes 3 SP1 Addressing Mode

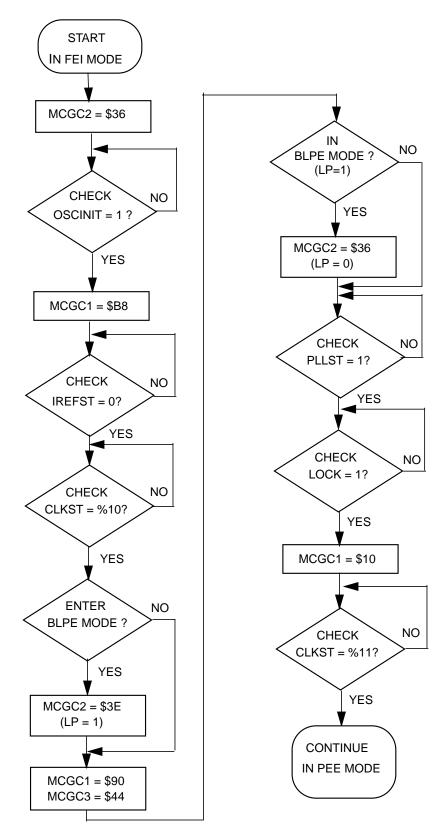

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

Figure 8-9. Flowchart of FEI to PEE Mode Transition using a 4 MHz crystal

Chapter 11 Inter-Integrated Circuit (S08IICV2)

## 11.7 Initialization/Application Information

|    |                                                                 | Medule Initialization (Slove)                                                                     |  |  |  |  |  |

|----|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1. | 1. Write: IICC2                                                 |                                                                                                   |  |  |  |  |  |

| 1. |                                                                 | nable or disable general call                                                                     |  |  |  |  |  |

|    |                                                                 | elect 10-bit or 7-bit addressing mode                                                             |  |  |  |  |  |

| 2. | Write: IIC                                                      | -                                                                                                 |  |  |  |  |  |

|    | — to se                                                         | et the slave address                                                                              |  |  |  |  |  |

| 3. | Write: IIC                                                      | CC1                                                                                               |  |  |  |  |  |

|    |                                                                 | nable IIC and interrupts                                                                          |  |  |  |  |  |

| 4. |                                                                 | RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                         |  |  |  |  |  |

| 5. | Initialize                                                      | RAM variables used to achieve the routine shown in Figure 11-12                                   |  |  |  |  |  |

|    |                                                                 |                                                                                                   |  |  |  |  |  |

|    |                                                                 | Module Initialization (Master)                                                                    |  |  |  |  |  |

| 1. | Write: IIC                                                      |                                                                                                   |  |  |  |  |  |

|    |                                                                 | et the IIC baud rate (example provided in this chapter)                                           |  |  |  |  |  |

| 2. | Write: IIC                                                      |                                                                                                   |  |  |  |  |  |

|    | — to er                                                         | nable IIC and interrupts                                                                          |  |  |  |  |  |

| 3. |                                                                 | RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                         |  |  |  |  |  |

| 4. |                                                                 | RAM variables used to achieve the routine shown in Figure 11-12                                   |  |  |  |  |  |

| 5. | Write: IIC                                                      |                                                                                                   |  |  |  |  |  |

| ~  | — to er                                                         |                                                                                                   |  |  |  |  |  |

| 6. | Write: IIC                                                      |                                                                                                   |  |  |  |  |  |

| 7. | Write: IIC                                                      | nable MST (master mode)                                                                           |  |  |  |  |  |

| 1. |                                                                 | the address of the target slave. (The lsb of this byte determines whether the communication is    |  |  |  |  |  |

|    |                                                                 | ter receive or transmit.)                                                                         |  |  |  |  |  |

|    |                                                                 | Module Use                                                                                        |  |  |  |  |  |

|    | The routi                                                       | ne shown in Figure 11-12 can handle both master and slave IIC operations. For slave operation, an |  |  |  |  |  |

|    | incoming                                                        | IIC message that contains the proper address begins IIC communication. For master operation,      |  |  |  |  |  |

|    | commun                                                          | ication must be initiated by writing to the IICD register.                                        |  |  |  |  |  |

|    | · · · · · · · · · · · · · · · · · · ·                           |                                                                                                   |  |  |  |  |  |

|    |                                                                 |                                                                                                   |  |  |  |  |  |

|    |                                                                 | Register Model                                                                                    |  |  |  |  |  |

|    |                                                                 |                                                                                                   |  |  |  |  |  |

|    | IICA                                                            | AD[7:1] 0                                                                                         |  |  |  |  |  |

|    |                                                                 | When addressed as a slave (in slave mode), the module responds to this address                    |  |  |  |  |  |

|    | IICF                                                            | MULT                                                                                              |  |  |  |  |  |

|    |                                                                 |                                                                                                   |  |  |  |  |  |

|    | Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))                 |                                                                                                   |  |  |  |  |  |

|    | IICC1                                                           | IICEN IICIE MST TX TXAK RSTA 0 0                                                                  |  |  |  |  |  |

|    |                                                                 | Module configuration                                                                              |  |  |  |  |  |

|    | IICS                                                            | TCF IAAS BUSY ARBL 0 SRW IICIF RXAK                                                               |  |  |  |  |  |

|    |                                                                 |                                                                                                   |  |  |  |  |  |

|    | Module status flags                                             |                                                                                                   |  |  |  |  |  |

|    | IICD                                                            | DATA                                                                                              |  |  |  |  |  |

|    | Data register; Write to transmit IIC data read to read IIC data |                                                                                                   |  |  |  |  |  |

|    | IICC2                                                           | GCAEN ADEXT 0 0 0 AD10 AD9 AD8                                                                    |  |  |  |  |  |

|    |                                                                 |                                                                                                   |  |  |  |  |  |

|    | Address configuration                                           |                                                                                                   |  |  |  |  |  |

Figure 11-11. IIC Module Quick Start

Chapter 13 Serial Communications Interface (S08SCIV4)

## 13.2 Register Definition

The SCI has eight 8-bit registers to control baud rate, select SCI options, report SCI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SCI registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

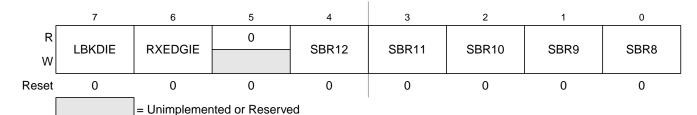

## 13.2.1 SCI Baud Rate Registers (SCI1BDH, SCI1BDL)

This pair of registers controls the prescale divisor for SCI baud rate generation. To update the 13-bit baud rate setting [SBR12:SBR0], first write to SCI1BDH to buffer the high half of the new value and then write to SCI1BDL. The working value in SCI1BDH does not change until SCI1BDL is written.

SCI1BDL is reset to a non-zero value, so after reset the baud rate generator remains disabled until the first time the receiver or transmitter is enabled (RE or TE bits in SCI1C2 are written to 1).

#### Figure 13-4. SCI Baud Rate Register (SCI1BDH)

| Field            | Description                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LBKDIE      | <ul> <li>LIN Break Detect Interrupt Enable (for LBKDIF)</li> <li>0 Hardware interrupts from LBKDIF disabled (use polling).</li> <li>1 Hardware interrupt requested when LBKDIF flag is 1.</li> </ul>                                                                                                                                        |

| 6<br>RXEDGIE     | RxD Input Active Edge Interrupt Enable (for RXEDGIF)0Hardware interrupts from RXEDGIF disabled (use polling).1Hardware interrupt requested when RXEDGIF flag is 1.                                                                                                                                                                          |

| 4:0<br>SBR[12:8] | <b>Baud Rate Modulo Divisor</b> — The 13 bits in SBR[12:0] are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/(16×BR). See also BR bits in Table 13-2. |

#### Table 13-5. SCI1S1 Field Descriptions (continued)

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1<br>FE | <ul> <li>Framing Error Flag — FE is set at the same time as RDRF when the receiver detects a logic 0 where the stop bit was expected. This suggests the receiver was not properly aligned to a character frame. To clear FE, read SCI1S1 with FE = 1 and then read the SCI data register (SCI1D).</li> <li>0 No framing error detected. This does not guarantee the framing is correct.</li> <li>1 Framing error.</li> </ul> |  |  |

| 0<br>PF | <ul> <li>Parity Error Flag — PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCI1S1 and then read the SCI data register (SCI1D).</li> <li>0 No parity error.</li> <li>1 Parity error.</li> </ul>                                                                                            |  |  |

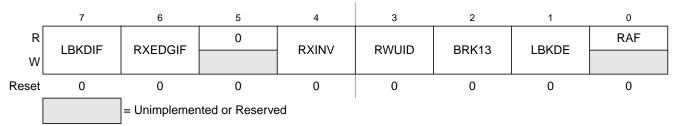

## 13.2.5 SCI Status Register 2 (SCI1S2)

This register has one read-only status flag.

#### Figure 13-9. SCI Status Register 2 (SCI1S2)

#### Table 13-6. SCI1S2 Field Descriptions

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LBKDIF             | LIN Break Detect Interrupt Flag — LBKDIF is set when the LIN break detect circuitry is enabled and a LIN break character is detected. LBKDIF is cleared by writing a "1" to it.<br>0 No LIN break character has been detected.<br>1 LIN break character has been detected.                                                                                                           |

| 6<br>RXEDGIF            | RxD Pin Active Edge Interrupt Flag — RXEDGIF is set when an active edge (falling if RXINV = 0, rising if RXINV=1) on the RxD pin occurs. RXEDGIF is cleared by writing a "1" to it.         0       No active edge on the receive pin has occurred.         1       An active edge on the receive pin has occurred.                                                                  |

| 4<br>RXINV <sup>1</sup> | Receive Data Inversion — Setting this bit reverses the polarity of the received data input.         0       Receive data not inverted         1       Receive data inverted                                                                                                                                                                                                          |

| 3<br>RWUID              | <ul> <li>Receive Wake Up Idle Detect— RWUID controls whether the idle character that wakes up the receiver sets the IDLE bit.</li> <li>0 During receive standby state (RWU = 1), the IDLE bit does not get set upon detection of an idle character.</li> <li>1 During receive standby state (RWU = 1), the IDLE bit gets set upon detection of an idle character.</li> </ul>         |

| 2<br>BRK13              | <ul> <li>Break Character Generation Length — BRK13 is used to select a longer transmitted break character length.</li> <li>Detection of a framing error is not affected by the state of this bit.</li> <li>0 Break character is transmitted with length of 10 bit times (11 if M = 1)</li> <li>1 Break character is transmitted with length of 13 bit times (14 if M = 1)</li> </ul> |

Chapter 13 Serial Communications Interface (S08SCIV4)

### 14.1.2 Features

Features of the RTC module include:

- 8-bit up-counter

- 8-bit modulo match limit

- Software controllable periodic interrupt on match

- Three software selectable clock sources for input to prescaler with selectable binary-based and decimal-based divider values

- 1-kHz internal low-power oscillator (LPO)

- External clock (ERCLK)

- 32-kHz internal clock (IRCLK)

### 14.1.3 Modes of Operation

This section defines the operation in stop, wait and background debug modes.

#### 14.1.3.1 Wait Mode

The RTC continues to run in wait mode if enabled before executing the appropriate instruction. Therefore, the RTC can bring the MCU out of wait mode if the real-time interrupt is enabled. For lowest possible current consumption, the RTC should be stopped by software if not needed as an interrupt source during wait mode.

#### 14.1.3.2 Stop Modes

The RTC continues to run in stop2 or stop3 mode if the RTC is enabled before executing the STOP instruction. Therefore, the RTC can bring the MCU out of stop modes with no external components, if the real-time interrupt is enabled.

The LPO clock can be used in stop2 and stop3 modes. ERCLK and IRCLK clocks are only available in stop3 mode.

Power consumption is lower when all clock sources are disabled, but in that case, the real-time interrupt cannot wake up the MCU from stop modes.

### 14.1.3.3 Active Background Mode

The RTC suspends all counting during active background mode until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as the RTCMOD register is not written and the RTCPS and RTCLKS bits are not altered.

Chapter 15 Timer/PWM Module (S08TPMV3)

#### **Chapter 16 Development Support**

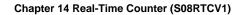

Figure 16-3 shows the host receiving a logic 1 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the perceived start of the bit time in the target MCU. The host holds the BKGD pin low long enough for the target to recognize it (at least two target BDC cycles). The host must release the low drive before the target MCU drives a brief active-high speedup pulse seven cycles after the perceived start of the bit time. The host should sample the bit level about 10 cycles after it started the bit time.

Figure 16-3. BDC Target-to-Host Serial Bit Timing (Logic 1)

| Command<br>Mnemonic | Active BDM/<br>Non-intrusive | Coding<br>Structure | Description                                                                              |  |

|---------------------|------------------------------|---------------------|------------------------------------------------------------------------------------------|--|

| SYNC                | Non-intrusive                | n/a <sup>1</sup>    | Request a timed reference pulse to determine target BDC communication speed              |  |

| ACK_ENABLE          | Non-intrusive                | D5/d                | Enable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.       |  |

| ACK_DISABLE         | Non-intrusive                | D6/d                | Disable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.      |  |

| BACKGROUND          | Non-intrusive                | 90/d                | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                   |  |

| READ_STATUS         | Non-intrusive                | E4/SS               | Read BDC status from BDCSCR                                                              |  |

| WRITE_CONTROL       | Non-intrusive                | C4/CC               | Write BDC controls in BDCSCR                                                             |  |

| READ_BYTE           | Non-intrusive                | E0/AAAA/d/RD        | Read a byte from target memory                                                           |  |

| READ_BYTE_WS        | Non-intrusive                | E1/AAAA/d/SS/RD     | Read a byte and report status                                                            |  |

| READ_LAST           | Non-intrusive                | E8/SS/RD            | Re-read byte from address just read and report status                                    |  |

| WRITE_BYTE          | Non-intrusive                | C0/AAAA/WD/d        | Write a byte to target memory                                                            |  |

| WRITE_BYTE_WS       | Non-intrusive                | C1/AAAA/WD/d/SS     | Write a byte and report status                                                           |  |

| READ_BKPT           | Non-intrusive                | E2/RBKP             | Read BDCBKPT breakpoint register                                                         |  |

| WRITE_BKPT          | Non-intrusive                | C2/WBKP             | Write BDCBKPT breakpoint register                                                        |  |

| GO                  | Active BDM                   | 08/d                | Go to execute the user application program starting at the address currently in the PC   |  |

| TRACE1              | Active BDM                   | 10/d                | Trace 1 user instruction at the address in the PC, then return to active background mode |  |

| TAGGO               | Active BDM                   | 18/d                | Same as GO but enable external tagging<br>(HCS08 devices have no external tagging pin)   |  |

| READ_A              | Active BDM                   | 68/d/RD             | Read accumulator (A)                                                                     |  |

| READ_CCR            | Active BDM                   | 69/d/RD             | Read condition code register (CCR)                                                       |  |

| READ_PC             | Active BDM                   | 6B/d/RD16           | Read program counter (PC)                                                                |  |

| READ_HX             | Active BDM                   | 6C/d/RD16           | Read H and X register pair (H:X)                                                         |  |

| READ_SP             | Active BDM                   | 6F/d/RD16           | Read stack pointer (SP)                                                                  |  |

| READ_NEXT           | Active BDM                   | 70/d/RD             | Increment H:X by one then read memory byte located at H:X                                |  |

| READ_NEXT_WS        | Active BDM                   | 71/d/SS/RD          | Increment H:X by one then read memory byte located at H:X. Report status and data.       |  |

| WRITE_A             | Active BDM                   | 48/WD/d             | Write accumulator (A)                                                                    |  |

| WRITE_CCR           | Active BDM                   | 49/WD/d             | Write condition code register (CCR)                                                      |  |

| WRITE_PC            | Active BDM                   | 4B/WD16/d           | Write program counter (PC)                                                               |  |

| WRITE_HX            | Active BDM                   | 4C/WD16/d           | Write H and X register pair (H:X)                                                        |  |

| WRITE_SP            | Active BDM                   | 4F/WD16/d           | Write stack pointer (SP)                                                                 |  |

| WRITE_NEXT          | Active BDM                   | 50/WD/d             | Increment H:X by one, then write memory byte<br>located at H:X                           |  |

| WRITE_NEXT_WS       | Active BDM                   | 51/WD/d/SS          | Increment H:X by one, then write memory byte located at H:X. Also report status.         |  |

| Table 16-1. BDC Command Summa |

|-------------------------------|

|-------------------------------|

<sup>1</sup> The SYNC command is a special operation that does not have a command code.

## Appendix A Electrical Characteristics

## A.1 Introduction

This section contains the most accurate electrical and timing information for the MC9S08DN60 Series of microcontrollers available at the time of publication.

## A.2 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |  |  |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| с | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |  |  |  |

| т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |  |  |  |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |  |  |  |

#### Table A-1. Parameter Classifications

#### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

## A.3 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table A-2 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

#### Appendix B Timer Pulse-Width Modulator (TPMV2)

As an up-counter, the main 16-bit counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts upward from 0x0000 through its terminal count and then counts downward to 0x0000 where it returns to up-counting. Both 0x0000 and the terminal count value (value in TPMxMODH:TPMxMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The 0x0000 count value corresponds to the center of a period.)

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter for read operations. Whenever either byte of the counter is read (TPMxCNTH or TPMxCNTL), both bytes are captured into a buffer so when the other byte is read, the value will represent the other byte of the count at the time the first byte was read. The counter continues to count normally, but no new value can be read from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer count TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only one byte of the counter was read before resetting the count.

### B.3.2 Channel Mode Selection

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

### B.3.2.1 Input Capture Mode

With the input capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter into the channel value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

$\overline{3}$  datums a, b, and d to be determined at datum plane h.

$\overline{/4.}$  dimensions to be determined at seating plane datum c.

<u>/5</u> DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION: 0.07 MM.

<u>6</u> DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

$\overline{/7.}$  exact shape of each corner is optional.

$\overline{/8.}$  These dimensions apply to the flat section of the lead between 0.1 MM and 0.25 MM from the lead tip.

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. |                                 | L OUTLINE      | PRINT VERSION NOT TO SCALE |  |

|---------------------------------------------------------|---------------------------------|----------------|----------------------------|--|

| TITLE:                                                  | DOCUMENT NE                     | 1: 98ASH70029A | RE∨∶D                      |  |

| LOW PROFILE QUAD FLAT PA                                | CASE NUMBER: 873A-03 19 MAY 200 |                | 19 MAY 2005                |  |

| 32 LEAD, 0.8 PITCH (7 X                                 | STANDARD: JE                    | DEC MS-026 BBA |                            |  |