Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dn60clc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Chapter 4 Memory**

| 0x0000<br>DIRECT PAGE REGISTERS<br>0x007F 128 BYTES<br>0x0080<br>RAM<br>2048 BYTES | 0x0000<br>DIRECT PAGE REGISTERS<br>0x007F 128 BYTES<br>0x0080<br>RAM<br>2048 BYTES | 0x0000<br>DIRECT PAGE REGISTERS<br>0x007F 128 BYTES<br>0x0080<br>RAM<br>1536 BYTES<br>0x067F | 0x0000<br>DIRECT PAGE REGISTERS<br>0x007F 128 BYTES<br>0x0080<br>RAM<br>0x047F<br>0x0480 |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 0x0880                                                                             | 0x0880                                                                             | 0x0680                                                                                       |                                                                                          |

| FLASH<br>0x13FF 2944 BYTES<br>0x1400 EEPROM                                        | UNIMPLEMENTED 3200 BYTES  0x14FF 0x1500 EEPROM 2 x 768 BYTES                       | UNIMPLEMENTED 3968 BYTES  0x15FF 0x1600 EEPROM                                               | UNIMPLEMENTED<br>4736 BYTES                                                              |

| 0x17FF 2 x 1024 BYTES                                                              | 0x17FF                                                                             | 2 x 512 BYTES<br>0x17FF                                                                      | 0x1700 EEPROM<br>0x17FF 2 x 256 BYTES                                                    |

| 0x1800<br>HIGH PAGE REGISTERS<br>256 BYTES<br>0x18FF                               | 0x1800<br>HIGH PAGE REGISTERS<br>256 BYTES<br>0x18FF                               | ÖXT800<br>HIGH PAGE REGISTERS<br>256 BYTES<br>0x18FF                                         | 0x1800<br>HIGH PAGE REGISTERS<br>256 BYTES<br>0x18FF                                     |

| 0x1900                                                                             | 0x1900                                                                             | 0x18FF<br>0x1900                                                                             | 0x1900                                                                                   |

|                                                                                    | UNIMPLEMENTED<br>9984 BYTES<br>0x3FFF<br>0x4000                                    | UNIMPLEMENTED<br>25344 BYTES                                                                 | UNIMPLEMENTED<br>42240 BYTES                                                             |

| FLASH<br>59136 BYTES                                                               | FLASH<br>49152 BYTES                                                               | 0x7BFF<br>0x7C00<br>FLASH<br>33792 BYTES                                                     | 0xBDFF<br>0xBE00<br>FLASH<br>16896 BYTES                                                 |

| 9S08DN60                                                                           | 9S08DN48                                                                           | 9S08DN32                                                                                     | 9S08DN16                                                                                 |

Figure 4-1. MC9S08DN60 Series Memory Map

# 4.2 Reset and Interrupt Vector Assignments

Table 4-1 shows address assignments for reset and interrupt vectors. The vector names shown in this table are the labels used in the MC9S08DN60 Series equate file provided by Freescale Semiconductor.

**Table 4-1. Reset and Interrupt Vectors**

| Address<br>(High/Low) | Vector         | Vector Name |

|-----------------------|----------------|-------------|

| 0xFFC0:0xFFC1         | ACMP2          | Vacmp2      |

| 0xFFC2:0xFFC3         | ACMP1          | Vacmp1      |

| 0xFFC4:0xFFCB         | Reserved       | _           |

| 0xFFCC:0xFFCD         | RTC            | Vrtc        |

| 0xFFCE:0xFFCF         | IIC            | Viic        |

| 0xFFD0:0xFFD1         | ADC Conversion | Vadc        |

MC9S08DN60 Series Data Sheet, Rev 3

Table 4-1. Reset and Interrupt Vectors

| Address<br>(High/Low) | Vector                 | Vector Name |

|-----------------------|------------------------|-------------|

| 0xFFD2:0xFFD3         | Port A, Port B, Port D | Vport       |

| 0xFFD4:0xFFD9         | Reserved               | _           |

| 0xFFDA:0xFFDB         | SCI1 Transmit          | Vsci1tx     |

| 0xFFDC:0xFFDD         | SCI1 Receive           | Vsci1rx     |

| 0xFFDE:0xFFDF         | SCI1 Error             | Vsci1err    |

| 0xFFE0:0xFFE1         | SPI                    | Vspi        |

| 0xFFE2:0xFFE3         | TPM2 Overflow          | Vtpm2ovf    |

| 0xFFE4:0xFFE5         | TPM2 Channel 1         | Vtpm2ch1    |

| 0xFFE6:0xFFE7         | TPM2 Channel 0         | Vtpm2ch0    |

| 0xFFE8:0xFFE9         | TPM1 Overflow          | Vtpm1ovf    |

| 0xFFEA:0xFFEB         | TPM1 Channel 5         | Vtpm1ch5    |

| 0xFFEC:0xFFED         | TPM1 Channel 4         | Vtpm1ch4    |

| 0xFFEE:0xFFEF         | TPM1 Channel 3         | Vtpm1ch3    |

| 0xFFF0:0xFFF1         | TPM1 Channel 2         | Vtpm1ch2    |

| 0xFFF2:0xFFF3         | TPM1 Channel 1         | Vtpm1ch1    |

| 0xFFF4:0xFFF5         | TPM1 Channel 0         | Vtpm1ch0    |

| 0xFFF6:0xFFF7         | MCG Loss of lock       | VIol        |

| 0xFFF8:0xFFF9         | Low-Voltage Detect     | Vlvd        |

| 0xFFFA:0xFFFB         | IRQ                    | Virq        |

| 0xFFFC:0xFFFD         | SWI                    | Vswi        |

| 0xFFFE:0xFFFF         | Reset                  | Vreset      |

# Chapter 5 Resets, Interrupts, and General System Control

## 5.1 Introduction

This section discusses basic reset and interrupt mechanisms and their various sources in the MC9S08DN60 Series. Some interrupt sources from peripheral modules are discussed in greater detail within other sections of this data sheet. This section gathers basic information about all reset and interrupt sources in one place for easy reference. A few reset and interrupt sources, including the computer operating properly (COP) watchdog, are not part of on-chip peripheral systems with their own chapters.

## 5.2 Features

Reset and interrupt features include:

- Multiple sources of reset for flexible system configuration and reliable operation

- Reset status register (SRS) to indicate source of most recent reset

- Separate interrupt vector for each module (reduces polling overhead); see Table 5-1

## 5.3 MCU Reset

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset, most control and status registers are forced to initial values and the program counter is loaded from the reset vector (0xFFFE:0xFFFF). On-chip peripheral modules are disabled and I/O pins are initially configured as general-purpose high-impedance inputs with pull-up devices disabled. The I bit in the condition code register (CCR) is set to block maskable interrupts so the user program has a chance to initialize the stack pointer (SP) and system control settings. (See the CPU chapter for information on the Interrupt (I) bit.) SP is forced to 0x00FF at reset.

The MC9S08DN60 Series has eight sources for reset:

- Power-on reset (POR)

- External pin reset (PIN)

- Computer operating properly (COP) timer

- Illegal opcode detect (ILOP)

- Illegal address detect (ILAD)

- Low-voltage detect (LVD)

- Loss of clock (LOC)

- Background debug forced reset (BDFR)

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register (SRS).

**Chapter 6 Parallel Input/Output Control**

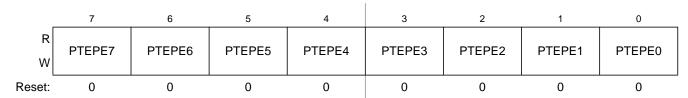

# 6.5.5.3 Port E Pull Enable Register (PTEPE)

Figure 6-34. Internal Pull Enable for Port E Register (PTEPE)

Table 6-32. PTEPE Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                         |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTEPE[7:0] | Internal Pull Enable for Port E Bits — Each of these control bits determines if the internal pull-up device is enabled for the associated PTE pin. For port E pins that are configured as outputs, these bits have no effect and the internal pull devices are disabled.  0 Internal pull-up device disabled for port E bit n.  1 Internal pull-up device enabled for port E bit n. |

#### **NOTE**

Pull-down devices only apply when using pin interrupt functions, when corresponding edge select and pin select functions are configured.

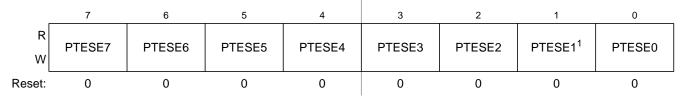

# 6.5.5.4 Port E Slew Rate Enable Register (PTESE)

Figure 6-35. Slew Rate Enable for Port E Register (PTESE)

**Table 6-33. PTESE Register Field Descriptions**

| Field             | Description                                                                                                                                                                                                                                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTESE[7:0] | Output Slew Rate Enable for Port E Bits — Each of these control bits determines if the output slew rate control is enabled for the associated PTE pin. For port E pins that are configured as inputs, these bits have no effect.  Output slew rate control disabled for port E bit n.  Output slew rate control enabled for port E bit n. |

**Note:** Slew rate reset default values may differ between engineering samples and final production parts. Always initialize slew rate control to the desired value to ensure correct operation.

PTESE1 has no effect on the input-only PTE1 pin.

# 6.5.7 Port G Registers

Port G is controlled by the registers listed below.

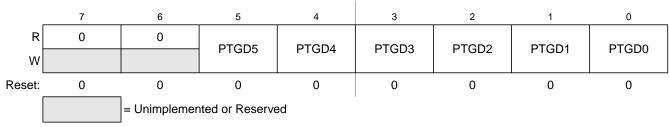

# 6.5.7.1 Port G Data Register (PTGD)

Figure 6-42. Port G Data Register (PTGD)

Table 6-40. PTGD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0<br>PTGD[5:0] | Port G Data Register Bits — For port G pins that are inputs, reads return the logic level on the pin. For port G pins that are configured as outputs, reads return the last value written to this register.  Writes are latched into all bits of this register. For port G pins that are configured as outputs, the logic level is driven out the corresponding MCU pin.  Reset forces PTGD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups disabled. |

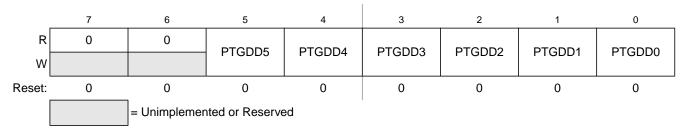

# 6.5.7.2 Port G Data Direction Register (PTGDD)

Figure 6-43. Port G Data Direction Register (PTGDD)

Table 6-41. PTGDD Register Field Descriptions

| Field      | Description                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------|

| 5:0        | Data Direction for Port G Bits — These read/write bits control the direction of port G pins and what is read for |

| PTGDD[5:0] | PTGD reads.                                                                                                      |

|            | 0 Input (output driver disabled) and reads return the pin value.                                                 |

|            | 1 Output driver enabled for port G bit n and PTGD reads return the contents of PTGDn.                            |

|            |                                                                                                                  |

MC9S08DN60 Series Data Sheet, Rev 3

Freescale Semiconductor

105

# Chapter 7 Central Processor Unit (S08CPUV3)

## 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

#### 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

MC9S08DN60 Series Data Sheet, Rev 3

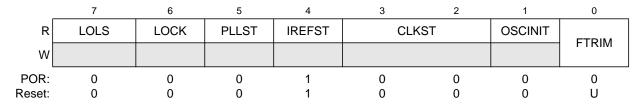

# 8.3.4 MCG Status and Control Register (MCGSC)

Figure 8-6. MCG Status and Control Register (MCGSC)

**Table 8-4. MCG Status and Control Register Field Descriptions**

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOLS    | Loss of Lock Status — This bit is a sticky indication of lock status for the FLL or PLL. LOLS is set when lock detection is enabled and after acquiring lock, the FLL or PLL output frequency has fallen outside the lock exit frequency tolerance, D <sub>unl</sub> . LOLIE determines whether an interrupt request is made when set. LOLS is cleared by reset or by writing a logic 1 to LOLS when LOLS is set. Writing a logic 0 to LOLS has no effect.  0 FLL or PLL has not lost lock since LOLS was last cleared.  1 FLL or PLL has lost lock since LOLS was last cleared.                                                                                                                                                                                                                      |

| 6<br>LOCK    | Lock Status — Indicates whether the FLL or PLL has acquired lock. Lock detection is disabled when both the FLL and PLL are disabled. If the lock status bit is set then changing the value of any of the following bits IREFS, PLLS, RDIV[2:0], TRIM[7:0] (if in FEI or FBI modes), or VDIV[3:0] (if in PBE or PEE modes), will cause the lock status bit to clear and stay cleared until the FLL or PLL has reacquired lock. Stop mode entry will also cause the lock status bit to clear and stay cleared until the FLL or PLL has reacquired lock. Entry into BLPI or BLPE mode will also cause the lock status bit to clear and stay cleared until the MCG has exited these modes and the FLL or PLL has reacquired lock.  O FLL or PLL is currently unlocked.  1 FLL or PLL is currently locked. |

| 5<br>PLLST   | PLL Select Status — The PLLST bit indicates the current source for the PLLS clock. The PLLST bit does not update immediately after a write to the PLLS bit due to internal synchronization between clock domains.  0 Source of PLLS clock is FLL clock.  1 Source of PLLS clock is PLL clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4<br>IREFST  | Internal Reference Status — The IREFST bit indicates the current source for the reference clock. The IREFST bit does not update immediately after a write to the IREFS bit due to internal synchronization between clock domains.  O Source of reference clock is external reference clock (oscillator or external clock source as determined by the EREFS bit in the MCGC2 register).  Source of reference clock is internal reference clock.                                                                                                                                                                                                                                                                                                                                                        |

| 3:2<br>CLKST | Clock Mode Status — The CLKST bits indicate the current clock mode. The CLKST bits do not update immediately after a write to the CLKS bits due to internal synchronization between clock domains.  00 Encoding 0 — Output of FLL is selected.  01 Encoding 1 — Internal reference clock is selected.  10 Encoding 2 — External reference clock is selected.  11 Encoding 3 — Output of PLL is selected.                                                                                                                                                                                                                                                                                                                                                                                              |

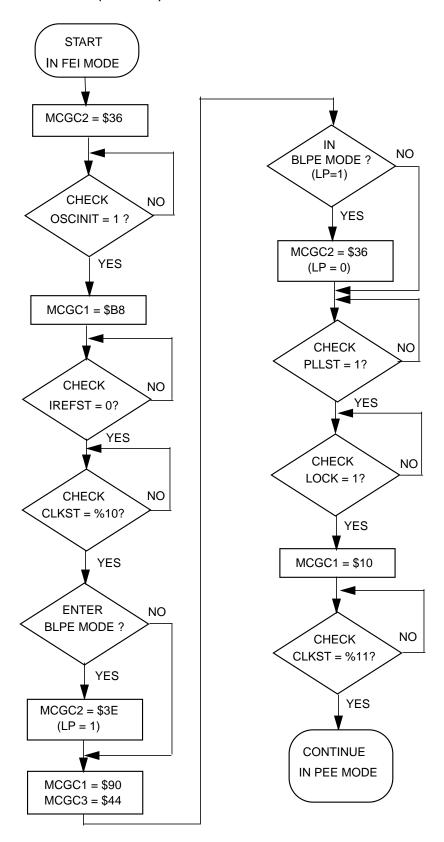

#### Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

Figure 8-9. Flowchart of FEI to PEE Mode Transition using a 4 MHz crystal

external crystal and a maximum reference divider factor of 128, the resulting frequency of the reference clock for the FLL is 62.5 kHz (greater than the 39.0625 kHz maximum allowed).

Care must be taken in the software to minimize the amount of time spent in this state where the FLL is operating in this condition.

The following code sequence describes how to move from FEI mode to PEE mode until the 8 MHz crystal reference frequency is set to achieve a bus frequency of 8 MHz. Because the MCG is in FEI mode out of reset, this example also shows how to initialize the MCG for PEE mode out of reset. First, the code sequence will be described. Then a flowchart will be included which illustrates the sequence.

- 1. First, FEI must transition to FBE mode:

- a) MCGC2 = 0x36 (%00110110)

- BDIV (bits 7 and 6) set to %00, or divide-by-1

- RANGE (bit 5) set to 1 because the frequency of 8 MHz is within the high frequency range

- HGO (bit 4) set to 1 to configure external oscillator for high gain operation

- EREFS (bit 2) set to 1, because a crystal is being used

- ERCLKEN (bit 1) set to 1 to ensure the external reference clock is active

- b) Loop until OSCINIT (bit 1) in MCGSC is 1, indicating the crystal selected by the EREFS bit has been initialized.

- c) Block Interrupts (If applicable by setting the interrupt bit in the CCR).

- d) MCGC1 = 0xB8 (%10111000)

- CLKS (bits 7 and 6) set to %10 in order to select external reference clock as system clock source

- RDIV (bits 5-3) set to %111, or divide-by-128.

#### NOTE

$8 \, \text{MHz} / 128 = 62.5 \, \text{kHz}$  which is greater than the  $31.25 \, \text{kHz}$  to  $39.0625 \, \text{kHz}$  range required by the FLL. Therefore after the transition to FBE is complete, software must progress through to BLPE mode immediately by setting the LP bit in MCGC2.

- IREFS (bit 2) cleared to 0, selecting the external reference clock

- e) Loop until IREFST (bit 4) in MCGSC is 0, indicating the external reference is the current source for the reference clock

- f) Loop until CLKST (bits 3 and 2) in MCGSC are %10, indicating that the external reference clock is selected to feed MCGOUT

- 2. Then, FBE mode transitions into BLPE mode:

- a) MCGC2 = 0x3E (%001111110)

- LP (bit 3) in MCGC2 to 1 (BLPE mode entered)

#### NOTE

There must be no extra steps (including interrupts) between steps 1d and 2a.

b) Enable Interrupts (if applicable by clearing the interrupt bit in the CCR).

#### MC9S08DN60 Series Data Sheet, Rev 3

# 10.1.5 Temperature Sensor

To use the on-chip temperature sensor, the user must perform the following:

- Configure ADC for long sample with a maximum of 1 MHz clock

- Convert the bandgap voltage reference channel (AD27)

- By converting the digital value of the bandgap voltage reference channel using the value of V<sub>BG</sub> the user can determine V<sub>DD</sub>. For value of bandgap voltage, see Section A.6, "DC Characteristics".

- Convert the temperature sensor channel (AD26)

- By using the calculated value of  $V_{DD}$ , convert the digital value of AD26 into a voltage,  $V_{TEMP}$

Equation 10-1 provides an approximate transfer function of the temperature sensor.

Temp = 25 -

$$((V_{TEMP} - V_{TEMP25}) \div m)$$

Eqn. 10-1

where:

- V<sub>TEMP</sub> is the voltage of the temperature sensor channel at the ambient temperature.

- V<sub>TEMP25</sub> is the voltage of the temperature sensor channel at 25°C.

- m is the hot or cold voltage versus temperature slope in V/°C.

For temperature calculations, use the V<sub>TEMP25</sub> and m values from the ADC Electricals table.

In application code, the user reads the temperature sensor channel, calculates  $V_{TEMP}$  and compares to  $V_{TEMP25}$ . If  $V_{TEMP}$  is greater than  $V_{TEMP25}$  the cold slope value is applied in Equation 10-1. If  $V_{TEMP}$  is less than  $V_{TEMP25}$  the hot slope value is applied in Equation 10-1. To improve accuracy the user should calibrate the bandgap voltage reference and temperature sensor.

Calibrating at 25°C will improve accuracy to  $\pm 4.5$ °C.

Calibration at three points, -40°C, 25°C, and 125°C will improve accuracy to  $\pm 2.5$ °C. Once calibration has been completed, the user will need to calculate the slope for both hot and cold. In application code, the user would then calculate the temperature using Equation 10-1 as detailed above and then determine if the temperature is above or below 25°C. Once determined if the temperature is above or below 25°C, the user can recalculate the temperature using the hot or cold slope value obtained during calibration.

#### Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

ALTCLK for this MCU. Consult the module introduction for information on ALTCLK specific to this MCU.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from wait mode if the ADC interrupt is enabled (AIEN = 1).

# 10.4.7 MCU Stop3 Mode Operation

Stop mode is a low power-consumption standby mode during which most or all clock sources on the MCU are disabled.

# 10.4.7.1 Stop3 Mode With ADACK Disabled

If the asynchronous clock, ADACK, is not selected as the conversion clock, executing a stop instruction aborts the current conversion and places the ADC in its idle state. The contents of ADCRH and ADCRL are unaffected by stop3 mode. After exiting from stop3 mode, a software or hardware trigger is required to resume conversions.

## 10.4.7.2 Stop3 Mode With ADACK Enabled

If ADACK is selected as the conversion clock, the ADC continues operation during stop3 mode. For guaranteed ADC operation, the MCU's voltage regulator must remain active during stop3 mode. Consult the module introduction for configuration information for this MCU.

If a conversion is in progress when the MCU enters stop3 mode, it continues until completion. Conversions can be initiated while the MCU is in stop3 mode by means of the hardware trigger or if continuous conversions are enabled.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from stop3 mode if the ADC interrupt is enabled (AIEN = 1).

#### **NOTE**

The ADC module can wake the system from low-power stop and cause the MCU to begin consuming run-level currents without generating a system level interrupt. To prevent this scenario, software should ensure the data transfer blocking mechanism (discussed in Section 10.4.4.2, "Completing Conversions) is cleared when entering stop3 and continuing ADC conversions.

# 10.4.8 MCU Stop2 Mode Operation

The ADC module is automatically disabled when the MCU enters stop2 mode. All module registers contain their reset values following exit from stop2. Therefore, the module must be re-enabled and re-configured following exit from stop2.

#### Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

For 12-bit conversions the code transitions only after the full code width is present, so the quantization error is –1 lsb to 0 lsb and the code width of each step is 1 lsb.

## 10.6.2.5 Linearity Errors

The ADC may also exhibit non-linearity of several forms. Every effort has been made to reduce these errors but the system should be aware of them because they affect overall accuracy. These errors are:

- Zero-scale error (E<sub>ZS</sub>) (sometimes called offset) This error is defined as the difference between

the actual code width of the first conversion and the ideal code width (1/2 lsb in 8-bit or 10-bit

modes and 1 lsb in 12-bit mode). If the first conversion is 0x001, the difference between the actual

0x001 code width and its ideal (1 lsb) is used.

- Full-scale error (E<sub>FS</sub>) This error is defined as the difference between the actual code width of the last conversion and the ideal code width (1.5 lsb in 8-bit or 10-bit modes and 1LSB in 12-bit mode). If the last conversion is 0x3FE, the difference between the actual 0x3FE code width and its ideal (1LSB) is used.

- Differential non-linearity (DNL) This error is defined as the worst-case difference between the actual code width and the ideal code width for all conversions.

- Integral non-linearity (INL) This error is defined as the highest-value the (absolute value of the) running sum of DNL achieves. More simply, this is the worst-case difference of the actual transition voltage to a given code and its corresponding ideal transition voltage, for all codes.

- Total unadjusted error (TUE) This error is defined as the difference between the actual transfer function and the ideal straight-line transfer function and includes all forms of error.

# 10.6.2.6 Code Jitter, Non-Monotonicity, and Missing Codes

Analog-to-digital converters are susceptible to three special forms of error. These are code jitter, non-monotonicity, and missing codes.

Code jitter is when, at certain points, a given input voltage converts to one of two values when sampled repeatedly. Ideally, when the input voltage is infinitesimally smaller than the transition voltage, the converter yields the lower code (and vice-versa). However, even small amounts of system noise can cause the converter to be indeterminate (between two codes) for a range of input voltages around the transition voltage. This range is normally around 1/2lsb in 8-bit or 10-bit mode, or around 2 lsb in 12-bit mode, and increases with noise.

This error may be reduced by repeatedly sampling the input and averaging the result. Additionally the techniques discussed in Section 10.6.2.3 reduces this error.

Non-monotonicity is defined as when, except for code jitter, the converter converts to a lower code for a higher input voltage. Missing codes are those values never converted for any input value.

In 8-bit or 10-bit mode, the ADC is guaranteed to be monotonic and have no missing codes.

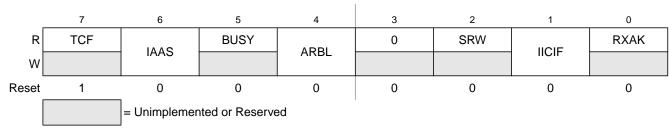

# 11.3.4 IIC Status Register (IICS)

Figure 11-6. IIC Status Register (IICS)

**Table 11-6. IICS Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TCF   | Transfer Complete Flag. This bit is set on the completion of a byte transfer. This bit is only valid during or immediately following a transfer to the IIC module or from the IIC module. The TCF bit is cleared by reading the IICD register in receive mode or writing to the IICD in transmit mode.  O Transfer in progress Transfer complete                                                                          |

| 6<br>IAAS  | Addressed as a Slave. The IAAS bit is set when the calling address matches the programmed slave address or when the GCAEN bit is set and a general call is received. Writing the IICC register clears this bit.  0 Not addressed 1 Addressed as a slave                                                                                                                                                                   |

| 5<br>BUSY  | Bus Busy. The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is set when a start signal is detected and cleared when a stop signal is detected.  O Bus is idle  1 Bus is busy                                                                                                                                                                                                  |

| 4<br>ARBL  | Arbitration Lost. This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be cleared by software by writing a 1 to it.  O Standard bus operation  1 Loss of arbitration                                                                                                                                                                                                                     |

| 2<br>SRW   | Slave Read/Write. When addressed as a slave, the SRW bit indicates the value of the R/W command bit of the calling address sent to the master.  O Slave receive, master writing to slave  1 Slave transmit, master reading from slave                                                                                                                                                                                     |

| 1<br>IICIF | <ul> <li>IIC Interrupt Flag. The IICIF bit is set when an interrupt is pending. This bit must be cleared by software, by writing a 1 to it in the interrupt routine. One of the following events can set the IICIF bit: <ul> <li>One byte transfer completes</li> <li>Match of slave address to calling address</li> <li>Arbitration lost</li> </ul> </li> <li>No interrupt pending</li> <li>Interrupt pending</li> </ul> |

| 0<br>RXAK  | Receive Acknowledge. When the RXAK bit is low, it indicates an acknowledge signal has been received after the completion of one byte of data transmission on the bus. If the RXAK bit is high it means that no acknowledge signal is detected.  O Acknowledge received  No acknowledge received                                                                                                                           |

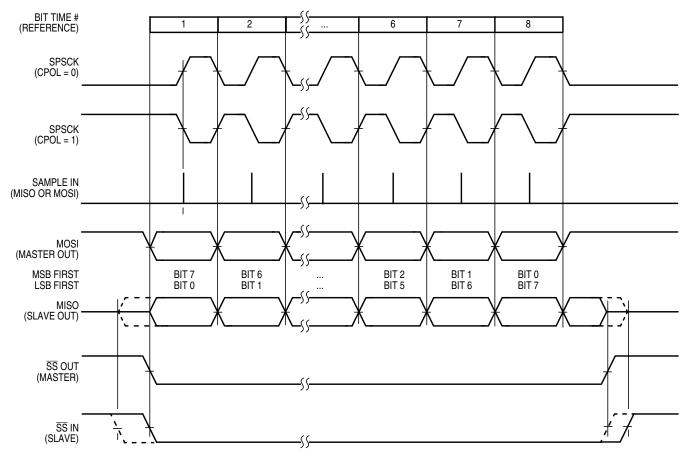

#### Chapter 12 Serial Peripheral Interface (S08SPIV3)

in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 12-11. SPI Clock Formats (CPHA = 0)

When CPHA = 0, the slave begins to drive its MISO output with the first data bit value (MSB or LSB depending on LSBFE) when  $\overline{SS}$  goes to active low. The first SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the second SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CPHA = 0, the slave's  $\overline{SS}$  input must go to its inactive high level between transfers.

#### 15.2.1.1 EXTCLK — External Clock Source

Control bits in the timer status and control register allow the user to select nothing (timer disable), the bus-rate clock (the normal default source), a crystal-related clock, or an external clock as the clock which drives the TPM prescaler and subsequently the 16-bit TPM counter. The external clock source is synchronized in the TPM. The bus clock clocks the synchronizer; the frequency of the external source must be no more than one-fourth the frequency of the bus-rate clock, to meet Nyquist criteria and allowing for jitter.

The external clock signal shares the same pin as a channel I/O pin, so the channel pin will not be usable for channel I/O function when selected as the external clock source. It is the user's responsibility to avoid such settings. If this pin is used as an external clock source (CLKSB:CLKSA = 1:1), the channel can still be used in output compare mode as a software timer (ELSnB:ELSnA = 0:0).

## 15.2.1.2 TPMxCHn — TPM Channel n I/O Pin(s)

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the channel configuration. The TPM pins share with general purpose I/O pins, where each pin has a port data register bit, and a data direction control bit, and the port has optional passive pullups which may be enabled whenever a port pin is acting as an input.

The TPM channel does not control the I/O pin when (ELSnB:ELSnA = 0:0) or when (CLKSB:CLKSA = 0:0) so it normally reverts to general purpose I/O control. When CPWMS = 1 (and ELSnB:ELSnA not = 0:0), all channels within the TPM are configured for center-aligned PWM and the TPMxCHn pins are all controlled by the TPM system. When CPWMS=0, the MSnB:MSnA control bits determine whether the channel is configured for input capture, output compare, or edge-aligned PWM.

When a channel is configured for input capture (CPWMS=0, MSnB:MSnA = 0:0 and ELSnB:ELSnA not = 0:0), the TPMxCHn pin is forced to act as an edge-sensitive input to the TPM. ELSnB:ELSnA control bits determine what polarity edge or edges will trigger input-capture events. A synchronizer based on the bus clock is used to synchronize input edges to the bus clock. This implies the minimum pulse width—that can be reliably detected—on an input capture pin is four bus clock periods (with ideal clock pulses as near as two bus clocks can be detected). TPM uses this pin as an input capture input to override the port data and data direction controls for the same pin.

When a channel is configured for output compare (CPWMS=0, MSnB:MSnA = 0:1 and ELSnB:ELSnA not = 0:0), the associated data direction control is overridden, the TPMxCHn pin is considered an output controlled by the TPM, and the ELSnB:ELSnA control bits determine how the pin is controlled. The remaining three combinations of ELSnB:ELSnA determine whether the TPMxCHn pin is toggled, cleared, or set each time the 16-bit channel value register matches the timer counter.

When the output compare toggle mode is initially selected, the previous value on the pin is driven out until the next output compare event—then the pin is toggled.

Input capture, output compare, and edge-aligned PWM functions do not make sense when the counter is operating in up/down counting mode so this implies that all active channels within a TPM must be used in CPWM mode when CPWMS=1.

The TPM may be used in an 8-bit MCU. The settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers.

In center-aligned PWM mode, the TPMxCnVH:L registers are updated with the value of their write buffer according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter, the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

When TPMxCNTH:TPMxCNTL=TPMxMODH:TPMxMODL, the TPM can optionally generate a TOF interrupt (at the end of this count).

Writing to TPMxSC cancels any values written to TPMxMODH and/or TPMxMODL and resets the coherency mechanism for the modulo registers. Writing to TPMxCnSC cancels any values written to the channel value registers and resets the coherency mechanism for TPMxCnVH:TPMxCnVL.

## 15.5 Reset Overview

#### 15.5.1 General

The TPM is reset whenever any MCU reset occurs.

# 15.5.2 Description of Reset Operation

Reset clears the TPMxSC register which disables clocks to the TPM and disables timer overflow interrupts (TOIE=0). CPWMS, MSnB, MSnA, ELSnB, and ELSnA are all cleared which configures all TPM channels for input-capture operation with the associated pins disconnected from I/O pin logic (so all MCU pins related to the TPM revert to general purpose I/O pins).

# 15.6 Interrupts

### 15.6.1 **General**

The TPM generates an optional interrupt for the main counter overflow and an interrupt for each channel. The meaning of channel interrupts depends on each channel's mode of operation. If the channel is configured for input capture, the interrupt flag is set each time the selected input capture edge is recognized. If the channel is configured for output compare or PWM modes, the interrupt flag is set each time the main timer counter matches the value in the 16-bit channel value register.

**Table 16-1. BDC Command Summary**

| Command Active BDM/ Coding |               |                     |                                                                                          |  |

|----------------------------|---------------|---------------------|------------------------------------------------------------------------------------------|--|

| Mnemonic                   | Non-intrusive | Coding<br>Structure | Description                                                                              |  |

| SYNC                       | Non-intrusive | n/a <sup>1</sup>    | Request a timed reference pulse to determine target BDC communication speed              |  |

| ACK_ENABLE                 | Non-intrusive | D5/d                | Enable acknowledge protocol. Refer to Freescale document order no. HCS08RMv1/D.          |  |

| ACK_DISABLE                | Non-intrusive | D6/d                | Disable acknowledge protocol. Refer to Freescale document order no. HCS08RMv1/D.         |  |

| BACKGROUND                 | Non-intrusive | 90/d                | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                   |  |

| READ_STATUS                | Non-intrusive | E4/SS               | Read BDC status from BDCSCR                                                              |  |

| WRITE_CONTROL              | Non-intrusive | C4/CC               | Write BDC controls in BDCSCR                                                             |  |

| READ_BYTE                  | Non-intrusive | E0/AAAA/d/RD        | Read a byte from target memory                                                           |  |

| READ_BYTE_WS               | Non-intrusive | E1/AAAA/d/SS/RD     | Read a byte and report status                                                            |  |

| READ_LAST                  | Non-intrusive | E8/SS/RD            | Re-read byte from address just read and report status                                    |  |

| WRITE_BYTE                 | Non-intrusive | C0/AAAA/WD/d        | Write a byte to target memory                                                            |  |

| WRITE_BYTE_WS              | Non-intrusive | C1/AAAA/WD/d/SS     | Write a byte and report status                                                           |  |

| READ_BKPT                  | Non-intrusive | E2/RBKP             | Read BDCBKPT breakpoint register                                                         |  |

| WRITE_BKPT                 | Non-intrusive | C2/WBKP             | Write BDCBKPT breakpoint register                                                        |  |

| GO                         | Active BDM    | 08/d                | Go to execute the user application program starting at the address currently in the PC   |  |

| TRACE1                     | Active BDM    | 10/d                | Trace 1 user instruction at the address in the PC, then return to active background mode |  |

| TAGGO                      | Active BDM    | 18/d                | Same as GO but enable external tagging (HCS08 devices have no external tagging pin)      |  |

| READ_A                     | Active BDM    | 68/d/RD             | Read accumulator (A)                                                                     |  |

| READ_CCR                   | Active BDM    | 69/d/RD             | Read condition code register (CCR)                                                       |  |

| READ_PC                    | Active BDM    | 6B/d/RD16           | Read program counter (PC)                                                                |  |

| READ_HX                    | Active BDM    | 6C/d/RD16           | Read H and X register pair (H:X)                                                         |  |

| READ_SP                    | Active BDM    | 6F/d/RD16           | Read stack pointer (SP)                                                                  |  |

| READ_NEXT                  | Active BDM    | 70/d/RD             | Increment H:X by one then read memory byte located at H:X                                |  |

| READ_NEXT_WS               | Active BDM    | 71/d/SS/RD          | Increment H:X by one then read memory byte located at H:X. Report status and data.       |  |

| WRITE_A                    | Active BDM    | 48/WD/d             | Write accumulator (A)                                                                    |  |

| WRITE_CCR                  | Active BDM    | 49/WD/d             | Write condition code register (CCR)                                                      |  |

| WRITE_PC                   | Active BDM    | 4B/WD16/d           | Write program counter (PC)                                                               |  |

| WRITE_HX                   | Active BDM    | 4C/WD16/d           | Write H and X register pair (H:X)                                                        |  |

| WRITE_SP                   | Active BDM    | 4F/WD16/d           | Write stack pointer (SP)                                                                 |  |

| WRITE_NEXT                 | Active BDM    | 50/WD/d             | Increment H:X by one, then write memory byte located at H:X                              |  |

| WRITE_NEXT_WS              | Active BDM    | 51/WD/d/SS          | Increment H:X by one, then write memory byte located at H:X. Also report status.         |  |

$<sup>^{\</sup>mbox{\scriptsize 1}}$  The SYNC command is a special operation that does not have a command code.

## MC9S08DN60 Series Data Sheet, Rev 3

#### **Appendix A Electrical Characteristics**

Table A-6. DC Characteristics (continued)

| Num | С | Characteristic                                                                                                  | Symbol            | Condition                                             | Min          | Typ <sup>1</sup> | Max             | Unit |

|-----|---|-----------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------|--------------|------------------|-----------------|------|

| 14  | D | POR re-arm voltage <sup>3</sup>                                                                                 | V <sub>POR</sub>  |                                                       | 0.9          | 1.4              | 2.0             | V    |

| 15  | D | POR re-arm time <sup>4</sup>                                                                                    | t <sub>POR</sub>  |                                                       | 10           | _                | _               | μs   |

| 16  | Р | Low-voltage detection threshold — high range V <sub>DD</sub> falling V <sub>DD</sub> rising                     | V <sub>LVD1</sub> |                                                       | 3.9<br>4.0   | 4.0<br>4.1       | 4.1<br>4.2      | V    |

| 17  | Р |                                                                                                                 | V <sub>LVD0</sub> |                                                       | 2.48<br>2.54 | 2.56<br>2.62     | 2.64<br>2.70    | V    |

| 18  | С | Low-voltage warning threshold — high range 1 V <sub>DD</sub> falling V <sub>DD</sub> rising                     | V <sub>LVW3</sub> |                                                       | 4.5<br>4.6   | 4.6<br>4.7       | 4.7<br>4.8      | V    |

| 19  | Р | Low-voltage warning threshold — high range 0 V <sub>DD</sub> falling V <sub>DD</sub> rising                     | V <sub>LVW2</sub> |                                                       | 4.2<br>4.3   | 4.3<br>4.4       | 4.4<br>4.5      | V    |

| 20  | Р | Low-voltage warning threshold low range 1 V <sub>DD</sub> falling V <sub>DD</sub> rising                        | V <sub>LVW1</sub> |                                                       | 2.84<br>2.90 | 2.92<br>2.98     | 3.00<br>3.06    | V    |

| 21  | С | Low-voltage warning threshold — low range 0 V <sub>DD</sub> falling V <sub>DD</sub> rising                      | V <sub>LVW0</sub> |                                                       | 2.66<br>2.72 | 2.74<br>2.80     | 2.82<br>2.88    | V    |

| 22  | Т | Low-voltage inhibit reset/recover                                                                               | V <sub>hys</sub>  | 5 V                                                   | _            | 100              | _               | mV   |

|     |   | hysteresis                                                                                                      |                   | 3 V                                                   | _            | 60               |                 | 1117 |

| 23  | D | dc injection current <sup>5, 6, 7, 8</sup> Single pin limit  Total MCU limit, includes sum of all stressed pins | I <sub>IC</sub>   | $V_{IN} > V_{DD}$ $V_{IN} < V_{SS}$ $V_{IN} > V_{DD}$ | 0<br>0<br>0  | _<br>            | 2<br>-0.2<br>25 | mA   |

|     |   |                                                                                                                 |                   | V <sub>IN</sub> < V <sub>SS</sub>                     | 0            | _                | <b>-</b> 5      |      |

| 24  | С | Bandgap Voltage Reference<br>Factory trimmed at<br>V <sub>DD</sub> = 5.0 V, Temp = 25°C                         | V <sub>BG</sub>   |                                                       | 1.19         | 1.20             | 1.21            | V    |

<sup>&</sup>lt;sup>1</sup> Typical values are measured at 25°C. Characterized, not tested

#### MC9S08DN60 Series Data Sheet, Rev 3

<sup>&</sup>lt;sup>2</sup> When a pin interrupt is configured to detect rising edges, pulldown resistors are used in place of pullup resistors.

<sup>&</sup>lt;sup>3</sup> Maximum is highest voltage that POR is guaranteed.

<sup>&</sup>lt;sup>4</sup> Simulated, not tested

Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low which (would reduce overall power consumption).

$<sup>^{\</sup>rm 6}~$  All functional non-supply pins are internally clamped to  $\rm V_{SS}$  and  $\rm V_{DD}$

# Appendix A Electrical Characteristics

## A.12.3 SPI

Table A-15 and Figure A-7 through Figure A-10 describe the timing requirements for the SPI system.

**Table A-15. SPI Electrical Characteristic**

| Num <sup>1</sup> | С | Rating <sup>2</sup>                           | Symbol                                   | Min                          | Max                      | Unit             |

|------------------|---|-----------------------------------------------|------------------------------------------|------------------------------|--------------------------|------------------|

| 1                | D | Cycle time<br>Master<br>Slave                 | t <sub>SCK</sub>                         | 2<br>4                       | 2048<br>—                | t <sub>cyc</sub> |

| 2                | D | Enable lead time<br>Master<br>Slave           | t <sub>Lead</sub><br>t <sub>Lead</sub>   | 1/2                          | 1/2<br>—                 | t <sub>SCK</sub> |

| 3                | D | Enable lag time<br>Master<br>Slave            | t <sub>Lag</sub><br>t <sub>Lag</sub>     | <br>1/2                      | 1/2<br>—                 | t <sub>SCK</sub> |

| 4                | D | Clock (SPSCK) high time<br>Master and Slave   | t <sub>sckh</sub>                        | (1/2 t <sub>SCK</sub> )– 25  | _                        | ns               |

| 5                | D | Clock (SPSCK) low time<br>Master and Slave    | t <sub>SCKL</sub>                        | (1/2 t <sub>SCK</sub> ) – 25 | _                        | ns               |

| 6                | D | Data setup time (inputs)  Master Slave        | t <sub>SI(M)</sub><br>t <sub>SI(S)</sub> | 30<br>30                     | _                        | ns<br>ns         |

| 7                | D | Data hold time (inputs)  Master Slave         | t <sub>HI(M)</sub><br>t <sub>HI(S)</sub> | 30<br>30                     |                          | ns<br>ns         |

| 8                | D | Access time, slave <sup>3</sup>               | t <sub>A</sub>                           | 0                            | 40                       | ns               |

| 9                | D | Disable time, slave <sup>4</sup>              | t <sub>dis</sub>                         | _                            | 40                       | ns               |

| 10               | D | Data setup time (outputs)  Master Slave       | t <sub>so</sub>                          | 25<br>25                     | _<br>_                   | ns<br>ns         |

| 11               | D | Data hold time (outputs)  Master Slave        | t <sub>HO</sub>                          | -10<br>-10                   | _<br>_                   | ns<br>ns         |

| 12               | D | Operating frequency <sup>5</sup> Master Slave | f <sub>op</sub><br>f <sub>op</sub>       | f <sub>Bus</sub> /2048<br>dc | 5<br>f <sub>Bus</sub> /4 | MHz              |

Refer to Figure A-7 through Figure A-10.

<sup>&</sup>lt;sup>2</sup> All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins. All timing assumes slew rate control disabled and high drive strength enabled for SPI output pins.

<sup>&</sup>lt;sup>3</sup> Time to data active from high-impedance state.

<sup>&</sup>lt;sup>4</sup> Hold time to high-impedance state.

<sup>&</sup>lt;sup>5</sup> Maximum baud rate must be limited to 5 MHz due to pad input characteristics.

All TPM channels are programmable independently as input capture, output compare, or buffered edge-aligned PWM channels.

# **B.1** External Signal Description

When any pin associated with the timer is configured as a timer input, a passive pullup can be enabled. After reset, the TPM modules are disabled and all pins default to general-purpose inputs with the passive pullups disabled.

### **B.1.1** External TPM Clock Sources

When control bits CLKSB:CLKSA in the timer status and control register are set to 1:1, the prescaler and consequently the 16-bit counter for TPMx are driven by an external clock source, TPMxCLK, connected to an I/O pin. A synchronizer is needed between the external clock and the rest of the TPM. This synchronizer is clocked by the bus clock so the frequency of the external source must be less than one-half the frequency of the bus rate clock. The upper frequency limit for this external clock source is specified to be one-fourth the bus frequency to conservatively accommodate duty cycle and phase-locked loop (PLL) or frequency-locked loop (FLL) frequency jitter effects.

On some devices the external clock input is shared with one of the TPM channels. When a TPM channel is shared as the external clock input, the associated TPM channel cannot use the pin. (The channel can still be used in output compare mode as a software timer.) Also, if one of the TPM channels is used as the external clock input, the corresponding ELSnB:ELSnA control bits must be set to 0:0 so the channel is not trying to use the same pin.

## B.1.2 TPMxCHn — TPMx Channel n I/O Pins

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the configuration of the channel. In some cases, no pin function is needed so the pin reverts to being controlled by general-purpose I/O controls. When a timer has control of a port pin, the port data and data direction registers do not affect the related pin(s). See the Pins and Connections chapter for additional information about shared pin functions.

# **B.2** Register Definition

The TPM includes:

- An 8-bit status and control register (TPMxSC)

- A 16-bit counter (TPMxCNTH:TPMxCNTL)

- A 16-bit modulo register (TPMxMODH:TPMxMODL)

Each timer channel has:

- An 8-bit status and control register (TPMxCnSC)

- A 16-bit channel value register (TPMxCnVH:TPMxCnVL)

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all TPM registers. This section refers to registers and control bits only by their names. A

MC9S08DN60 Series Data Sheet, Rev 3