Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                         |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 25                                                         |

| Program Memory Size        | 60KB (60K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | 2K x 8                                                     |

| RAM Size                   | 2K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 10x12b                                                 |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 32-LQFP                                                    |

| Supplier Device Package    | 32-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dn60mlc |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Chapter 2 Pins and Connections**

Whenever any reset is initiated (whether from an external signal or from an internal system), the  $\overline{\text{RESET}}$  pin is driven low for about 34 bus cycles. The reset circuitry decodes the cause of reset and records it by setting a corresponding bit in the system reset status register (SRS).

## 2.2.4 Background / Mode Select (BKGD/MS)

While in reset, the BKGD/MS pin functions as a mode select pin. Immediately after reset rises, the pin functions as the background pin and can be used for background debug communication. While functioning as a background or mode select pin, the pin includes an internal pull-up device, input hysteresis, a standard output driver, and no output slew rate control.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD low during the rising edge of reset which forces the MCU to active background mode.

The BKGD/MS pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the bus clock rate, so there should never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD/MS pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pull-up device play almost no role in determining rise and fall times on the BKGD/MS pin.

# 2.2.5 ADC Reference Pins (V<sub>REFH</sub>, V<sub>REFL</sub>)

The  $V_{REFH}$  and  $V_{REFL}$  pins are the voltage reference high and voltage reference low inputs, respectively, for the ADC module.

### 2.2.6 General-Purpose I/O and Peripheral Ports

The MC9S08DN60 Series series of MCUs support up to 53 general-purpose I/O pins and 1 input-only pin, which are shared with on-chip peripheral functions (timers, serial I/O, ADC, etc.).

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pull-up device. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pull-up devices disabled.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output Control."

To maintain I/O states for pins that were configured as general-purpose I/O before entering stop2, the user must restore the contents of the I/O port registers, which have been saved in RAM, to the port registers before writing to the PPDACK bit. If the port registers are not restored from RAM before writing to PPDACK, then the pins will switch to their reset states when PPDACK is written.

For pins that were configured as peripheral I/O, the user must reconfigure the peripheral module that interfaces to the pin before writing to the PPDACK bit. If the peripheral module is not enabled before writing to PPDACK, the pins will be controlled by their associated port control registers when the I/O latches are opened.

### 3.6.3 On-Chip Peripheral Modules in Stop Modes

When the MCU enters any stop mode, system clocks to the internal peripheral modules are stopped. Even in the exception case (ENBDM = 1), where clocks to the background debug logic continue to operate, clocks to the peripheral systems are halted to reduce power consumption. Refer to Section 3.6.2, "Stop2 Mode" and Section 3.6.1, "Stop3 Mode" for specific information on system behavior in stop modes.

| Deviational             | Mode                       |                            |  |  |  |

|-------------------------|----------------------------|----------------------------|--|--|--|

| Peripheral              | Stop2                      | Stop3                      |  |  |  |

| CPU                     | Off                        | Standby                    |  |  |  |

| RAM                     | Standby                    | Standby                    |  |  |  |

| Flash/EEPROM            | Off                        | Standby                    |  |  |  |

| Parallel Port Registers | Off                        | Standby                    |  |  |  |

| ACMP                    | Off                        | Off                        |  |  |  |

| ADC                     | Off                        | Optionally On <sup>1</sup> |  |  |  |

| IIC                     | Off                        | Standby                    |  |  |  |

| MCG                     | Off                        | Optionally On <sup>2</sup> |  |  |  |

| RTC                     | Optionally On <sup>3</sup> | Optionally On <sup>3</sup> |  |  |  |

| SCI                     | Off                        | Standby                    |  |  |  |

| SPI                     | Off                        | Standby                    |  |  |  |

| ТРМ                     | Off                        | Standby                    |  |  |  |

| Voltage Regulator       | Off                        | Optionally On <sup>4</sup> |  |  |  |

| XOSC                    | Off                        | Optionally On <sup>5</sup> |  |  |  |

| I/O Pins                | States Held                | States Held                |  |  |  |

| BDM                     | Off <sup>6</sup>           | Optionally On              |  |  |  |

| LVD/LVW                 | Off <sup>7</sup>           | Optionally On              |  |  |  |

| Table 3-2. Stop Mode Behavior | Table 3-2 | 2. Stop | Mode | <b>Behavior</b> |

|-------------------------------|-----------|---------|------|-----------------|

|-------------------------------|-----------|---------|------|-----------------|

<sup>1</sup> Requires the asynchronous ADC clock and LVD to be enabled, else in standby.

<sup>2</sup> IRCLKEN and IREFSTEN set in MCGC1, else in standby.

<sup>3</sup> Requires the RTC to be enabled, else in standby.

<sup>4</sup> Requires the LVD or BDC to be enabled.

**Chapter 4 Memory**

| Table 4-2. Direct-Page Register | Summary (Sheet 3 of 3) |

|---------------------------------|------------------------|

|---------------------------------|------------------------|

| Address                            | Register<br>Name | Bit 7                  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|------------------------------------|------------------|------------------------|-------|-------|-------|-------|-------|-------|-------|

| 0x00 <b>56</b> –<br>0x00 <b>57</b> | Reserved         |                        |       |       | _     |       | _     | _     | _     |

| 0x00 <b>58</b>                     | IICA             | AD7                    | AD6   | AD5   | AD4   | AD3   | AD2   | AD1   | 0     |

| 0x00 <b>59</b>                     | IICF             | ML                     | JLT   |       |       | IC    | R     |       |       |

| 0x00 <b>5A</b>                     | IICC1            | IICEN                  | IICIE | MST   | ΤX    | TXAK  | RSTA  | 0     | 0     |

| 0x00 <b>5B</b>                     | IICS             | TCF                    | IAAS  | BUSY  | ARBL  | 0     | SRW   | IICIF | RXAK  |

| 0x00 <b>5C</b>                     | IICD             |                        |       |       | DA    | TA    |       |       |       |

| 0x00 <b>5D</b>                     | IICC2            | GCAEN                  | ADEXT | 0     | 0     | 0     | AD10  | AD9   | AD8   |

| 0x00 <b>5E</b> –<br>0x00 <b>5F</b> | Reserved         | _                      |       | _     | _     | _     | _     | _     | _     |

| 0x00 <b>60</b>                     | TPM2SC           | TOF                    | TOIE  | CPWMS | CLKSB | CLKSA | PS2   | PS1   | PS0   |

| 0x00 <b>61</b>                     | TPM2CNTH         | Bit 15                 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x00 <b>62</b>                     | TPM2CNTL         | Bit 7                  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x00 <b>63</b>                     | TPM2MODH         | Bit 15                 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x00 <b>64</b>                     | TPM2MODL         | Bit 7                  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x00 <b>65</b>                     | TPM2C0SC         | CH0F                   | CH0IE | MS0B  | MS0A  | ELS0B | ELS0A | 0     | 0     |

| 0x00 <b>66</b>                     | TPM2C0VH         | Bit 15                 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x00 <b>67</b>                     | TPM2C0VL         | Bit 7                  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x00 <b>68</b>                     | TPM2C1SC         | CH1F                   | CH1IE | MS1B  | MS1A  | ELS1B | ELS1A | 0     | 0     |

| 0x00 <b>69</b>                     | TPM2C1VH         | Bit 15                 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x00 <b>6A</b>                     | TPM2C1VL         | Bit 7                  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x00 <b>6B</b>                     | Reserved         |                        |       |       | _     |       |       |       | —     |

| 0x00 <b>6C</b>                     | RTCSC            | RTIF RTCLKS RTIE RTCPS |       |       |       |       |       |       |       |

| 0x00 <b>6D</b>                     | RTCCNT           |                        |       |       | RTC   | CNT   |       |       |       |

| 0x00 <b>6E</b>                     | RTCMOD           |                        |       |       | RTCI  | MOD   |       |       |       |

| 0x00 <b>6F</b>                     | Reserved         | —                      |       | —     | _     |       |       | _     | —     |

| 0x00 <b>70</b> –<br>0x00 <b>7F</b> | Reserved         |                        |       |       |       |       |       | —     |       |

|                                    |                  |                        |       |       |       |       |       |       |       |

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

Table 4-3. High-Page Register Summary (Sheet 1 of 3)

| Address            | Register Name | Bit 7   | 6    | 5     | 4      | 3     | 2    | 1     | Bit 0 |

|--------------------|---------------|---------|------|-------|--------|-------|------|-------|-------|

| 0x1800             | SRS           | POR     | PIN  | COP   | ILOP   | ILAD  | LOCS | LVD   | 0     |

| 0x1801             | SBDFR         | 0       | 0    | 0     | 0      | 0     | 0    | 0     | BDFR  |

| 0x1802             | SOPT1         | CO      | PT   | STOPE | SCI2PS | IICPS | 0    | 0     | 0     |

| 0x1803             | SOPT2         | COPCLKS | COPW | 0     | ADHTS  | 0     |      | MCSEL |       |

| 0x1804 —<br>0x1805 | Reserved      | _       | _    | _     | _      | _     | _    | _     | _     |

Chapter 4 Memory

| Address           | Register Name | Bit 7  | 6      | 5              | 4                     | 3      | 2      | 1      | Bit 0  |

|-------------------|---------------|--------|--------|----------------|-----------------------|--------|--------|--------|--------|

| 0x1806            | SDIDH         | —      |        | —              | —                     | ID11   | ID10   | ID9    | ID8    |

| 0x1807            | SDIDL         | ID7    | ID6    | ID5            | ID4                   | ID3    | ID2    | ID1    | ID0    |

| 0x1808            | Reserved      | _      |        | _              | _                     | _      | _      |        | _      |

| 0x1809            | SPMSC1        | LVWF   | LVWACK | LVWIE          | LVDRE                 | LVDSE  | LVDE   | 0      | BGBE   |

| 0x180A            | SPMSC2        | 0      | 0      | LVDV           | LVWV                  | PPDF   | PPDACK | 0      | PPDC   |

| 0x180B–<br>0x180F | Reserved      |        | _      |                | _                     |        | _      | _      | _      |

| 0x1810            | DBGCAH        | Bit 15 | 14     | 13             | 12                    | 11     | 10     | 9      | Bit 8  |

| 0x1811            | DBGCAL        | Bit 7  | 6      | 5              | 4                     | 3      | 2      | 1      | Bit 0  |

| 0x1812            | DBGCBH        | Bit 15 | 14     | 13             | 12                    | 11     | 10     | 9      | Bit 8  |

| 0x1813            | DBGCBL        | Bit 7  | 6      | 5              | 4                     | 3      | 2      | 1      | Bit 0  |

| 0x1814            | DBGFH         | Bit 15 | 14     | 13             | 12                    | 11     | 10     | 9      | Bit 8  |

| 0x1815            | DBGFL         | Bit 7  | 6      | 5              | 4                     | 3      | 2      | 1      | Bit 0  |

| 0x1816            | DBGC          | DBGEN  | ARM    | TAG            | BRKEN                 | RWA    | RWAEN  | RWB    | RWBEN  |

| 0x1817            | DBGT          | TRGSEL | BEGIN  | 0              | 0                     | TRG3   | TRG2   | TRG1   | TRG0   |

| 0x1818            | DBGS          | AF     | BF     | ARMF           | 0                     | CNT3   | CNT2   | CNT1   | CNT0   |

| 0x1819–<br>0x181F | Reserved      | _      | _      | _              | _                     |        | _      | _      | _      |

| 0x1820            | FCDIV         | DIVLD  | PRDIV8 | DIV            |                       |        |        |        |        |

| 0x1821            | FOPT          | KEYEN  | FNORED | EPGMOD 0 0 SEC |                       |        |        | C      |        |

| 0x1822            | Reserved      | _      | _      | _              |                       | _      | _      | _      | —      |

| 0x1823            | FCNFG         | 0      | EPGSEL | KEYACC         | Reserved <sup>1</sup> | 0      | 0      | 0      | 1      |

| 0x1824            | FPROT         | EF     | ۶S     |                |                       | FF     | ۶S     |        |        |

| 0x1825            | FSTAT         | FCBEF  | FCCF   | FPVIOL         | FACCERR               | 0      | FBLANK | 0      | 0      |

| 0x1826            | FCMD          |        |        |                | FC                    | MD     |        |        |        |

| 0x1827–<br>0x183F | Reserved      |        | _      | _              | _                     | _      | _      | _      | _      |

| 0x1840            | ΡΤΑΡΕ         | PTAPE7 | PTAPE6 | PTAPE5         | PTAPE4                | PTAPE3 | PTAPE2 | PTAPE1 | PTAPE0 |

| 0x1841            | PTASE         | PTASE7 | PTASE6 | PTASE5         | PTASE4                | PTASE3 | PTASE2 | PTASE1 | PTASE0 |

| 0x1842            | PTADS         | PTADS7 | PTADS6 | PTADS5         | PTADS4                | PTADS3 | PTADS2 | PTADS1 | PTADS0 |

| 0x1843            | Reserved      | _      |        | —              | —                     | _      | —      |        | _      |

| 0x1844            | PTASC         | 0      | 0      | 0              | 0                     | PTAIF  | PTAACK | PTAIE  | PTAMOD |

| 0x1845            | PTAPS         | PTAPS7 | PTAPS6 | PTAPS5         | PTAPS4                | PTAPS3 | PTAPS2 | PTAPS1 | PTAPS0 |

| 0x1846            | PTAES         | PTAES7 | PTAES6 | PTAES5         | PTAES4                | PTAES3 | PTAES2 | PTAES1 | PTAES0 |

| 0x1847            | Reserved      | —      |        | _              | —                     |        | —      |        | _      |

| 0x1848            | PTBPE         | PTBPE7 | PTBPE6 | PTBPE5         | PTBPE4                | PTBPE3 | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x1849            | PTBSE         | PTBSE7 | PTBSE6 | PTBSE5         | PTBSE4                | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x184A            | PTBDS         | PTBDS7 | PTBDS6 | PTBDS5         | PTBDS4                | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |

| 0x184B            | Reserved      | —      |        | —              | —                     | —      | —      |        | —      |

| 0x184C            | PTBSC         | 0      | 0      | 0              | 0                     | PTBIF  | PTBACK | PTBIE  | PTBMOD |

Table 4-3. High-Page Register Summary (Sheet 2 of 3)

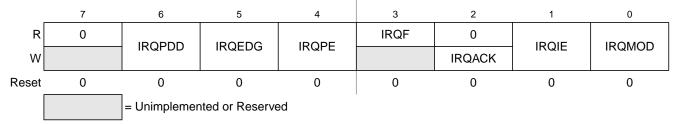

## 5.8.1 Interrupt Pin Request Status and Control Register (IRQSC)

This direct page register includes status and control bits which are used to configure the IRQ function, report status, and acknowledge IRQ events.

#### Figure 5-2. Interrupt Request Status and Control Register (IRQSC)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>IRQPDD | Interrupt Request (IRQ) Pull Device Disable— This read/write control bit is used to disable the internal pull-up/pull-down device when the IRQ pin is enabled (IRQPE = 1) allowing for an external device to be used.<br>0 IRQ pull device enabled if IRQPE = 1.<br>1 IRQ pull device disabled if IRQPE = 1.                                                                                                                                                                                                                                                                                                                                   |

| 5<br>IRQEDG | Interrupt Request (IRQ) Edge Select — This read/write control bit is used to select the polarity of edges or levels on the IRQ pin that cause IRQF to be set. The IRQMOD control bit determines whether the IRQ pin is sensitive to both edges and levels or only edges. When the IRQ pin is enabled as the IRQ input and is configured to detect rising edges, it has a pull-down. When the IRQ pin is enabled as the IRQ input and is configured to detect falling edges, it has a pull-up.         0       IRQ is falling edge or falling edge/low-level sensitive.         1       IRQ is rising edge or rising edge/high-level sensitive. |

| 4<br>IRQPE  | <ul> <li>IRQ Pin Enable — This read/write control bit enables the IRQ pin function. When this bit is set the IRQ pin can be used as an interrupt request.</li> <li>IRQ pin function is disabled.</li> <li>IRQ pin function is enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                              |

| 3<br>IRQF   | <ul> <li>IRQ Flag — This read-only status bit indicates when an interrupt request event has occurred.</li> <li>0 No IRQ request.</li> <li>1 IRQ event detected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2<br>IRQACK | <b>IRQ Acknowledge</b> — This write-only bit is used to acknowledge interrupt request events (write 1 to clear IRQF). Writing 0 has no meaning or effect. Reads always return 0. If edge-and-level detection is selected (IRQMOD = 1), IRQF cannot be cleared while the IRQ pin remains at its asserted level.                                                                                                                                                                                                                                                                                                                                 |

| 1<br>IRQIE  | <ul> <li>IRQ Interrupt Enable — This read/write control bit determines whether IRQ events generate an interrupt request.</li> <li>Interrupt request when IRQF set is disabled (use polling).</li> <li>Interrupt requested whenever IRQF = 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                        |

| 0<br>IRQMOD | <ul> <li>IRQ Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level detection. The IRQEDG control bit determines the polarity of edges and levels that are detected as interrupt request events. See Section 5.5.2.2, "Edge and Level Sensitivity" for more details.</li> <li>IRQ event on falling edges or rising edges only.</li> <li>IRQ event on falling edges and low levels or on rising edges and high levels.</li> </ul>                                                                                                                                                                    |

Chapter 5 Resets, Interrupts, and General System Control

# 5.8.2 System Reset Status Register (SRS)

This high page register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address causes a COP reset when the COP is enabled except the values 0x55 and 0xAA. Writing a 0x55-0xAA sequence to this address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

| _                   | 7   | 6                   | 5                   | 4                   | 3                   | 2            | 1   | 0 |

|---------------------|-----|---------------------|---------------------|---------------------|---------------------|--------------|-----|---|

| R                   | POR | PIN                 | COP                 | ILOP                | ILAD                | LOC          | LVD | 0 |

| W                   |     | Wi                  | iting 0x55, 0xA     | A to SRS addr       | ess clears COI      | vatchdog tim | er. |   |

| POR:                | 1   | 0                   | 0                   | 0                   | 0                   | 0            | 1   | 0 |

| LVD:                | u   | 0                   | 0                   | 0                   | 0                   | 0            | 1   | 0 |

| Any other<br>reset: | 0   | Note <sup>(1)</sup> | Note <sup>(1)</sup> | Note <sup>(1)</sup> | Note <sup>(1)</sup> | 0            | 0   | 0 |

<sup>1</sup> Any of these reset sources that are active at the time of reset entry will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset entry will be cleared.

#### Figure 5-3. System Reset Status (SRS)

#### Table 5-3. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVD) status bit is also set to indicate that the reset occurred while the internal supply was below the LVD threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                      |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                              |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source can be blocked by COPE = 0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                  |

| 4<br>ILOP | Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP<br>instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is<br>considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.0Reset not caused by an illegal opcode.<br>11Reset caused by an illegal opcode. |

| 3<br>ILAD | <ul> <li>Illegal Address — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.</li> <li>0 Reset not caused by an illegal address.</li> <li>1 Reset caused by an illegal address.</li> </ul>                                                                                                                                                         |

### 8.1.2 Modes of Operation

There are nine modes of operation for the MCG:

- FLL Engaged Internal (FEI)

- FLL Engaged External (FEE)

- FLL Bypassed Internal (FBI)

- FLL Bypassed External (FBE)

- PLL Engaged External (PEE)

- PLL Bypassed External (PBE)

- Bypassed Low Power Internal (BLPI)

- Bypassed Low Power External (BLPE)

- Stop

For details see Section 8.4.1, "Operational Modes.

### 8.2 External Signal Description

There are no MCG signals that connect off chip.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

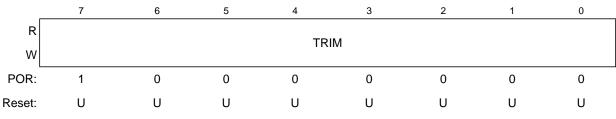

# 8.3.3 MCG Trim Register (MCGTRM)

Figure 8-5. MCG Trim Register (MCGTRM)

| Table 8-3. MCG Trim | <b>Register Field</b> | Descriptions |

|---------------------|-----------------------|--------------|

|---------------------|-----------------------|--------------|

| Field       | Description                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0<br>TRIM | MCG <b>Trim Setting</b> — Controls the internal reference clock frequency by controlling the internal reference clock period. The TRIM bits are binary weighted (i.e., bit 1 will adjust twice as much as bit 0). Increasing the binary value in TRIM will increase the period, and decreasing the value will decrease the period. |  |  |  |  |  |  |

|             | An additional fine trim bit is available in MCGSC as the FTRIM bit.                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|             | If a TRIM[7:0] value stored in nonvolatile memory is to be used, it's the user's responsibility to copy that value from the nonvolatile memory location to this register.                                                                                                                                                          |  |  |  |  |  |  |

## 8.4.3 Bus Frequency Divider

The BDIV bits can be changed at anytime and the actual switch to the new frequency will occur immediately.

### 8.4.4 Low Power Bit Usage

The low power bit (LP) is provided to allow the FLL or PLL to be disabled and thus conserve power when these systems are not being used. However, in some applications it may be desirable to enable the FLL or PLL and allow it to lock for maximum accuracy before switching to an engaged mode. Do this by writing the LP bit to 0.

## 8.4.5 Internal Reference Clock

When IRCLKEN is set the internal reference clock signal will be presented as MCGIRCLK, which can be used as an additional clock source. The MCGIRCLK frequency can be re-targeted by trimming the period of the internal reference clock. This can be done by writing a new value to the TRIM bits in the MCGTRM register. Writing a larger value will decrease the MCGIRCLK frequency, and writing a smaller value to the MCGTRM register will increase the MCGIRCLK frequency. The TRIM bits will effect the MCGOUT frequency if the MCG is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or bypassed low power internal (BLPI) mode. The TRIM and FTRIM value is initialized by POR but is not affected by other resets.

Until MCGIRCLK is trimmed, programming low reference divider (RDIV) factors may result in MCGOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock timing specifications (see the Device Overview chapter).

If IREFSTEN and IRCLKEN bits are both set, the internal reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

# 8.4.6 External Reference Clock

The MCG module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz in FEE and FBE modes, 1 MHz to 16 MHz in PEE and PBE modes, and 0 to 40 MHz in BLPE mode. When ERCLKEN is set, the external reference clock signal will be presented as MCGERCLK, which can be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by the FLL or PLL and will only be used as MCGERCLK. In these modes, the frequency can be equal to the maximum frequency the chip-level timing specifications will support (see the Device Overview chapter).

If EREFSTEN and ERCLKEN bits are both set or the MCG is in FEE, FBE, PEE, PBE or BLPE mode, the external reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

If CME bit is written to 1, the clock monitor is enabled. If the external reference falls below a certain frequency ( $f_{loc\_high}$  or  $f_{loc\_low}$  depending on the RANGE bit in the MCGC2), the MCU will reset. The LOC bit in the System Reset Status (SRS) register will be set to indicate the error.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

# 8.4.7 Fixed Frequency Clock

The MCG presents the divided reference clock as MCGFFCLK for use as an additional clock source. The MCGFFCLK frequency must be no more than 1/4 of the MCGOUT frequency to be valid. Because of this requirement, the MCGFFCLK is not valid in bypass modes for the following combinations of BDIV and RDIV values:

- BDIV=00 (divide by 1), RDIV < 010

- BDIV=01 (divide by 2), RDIV < 011

When MCGFFCLK is valid then MCGFFCLKVALID is set to 1. When MCGFFCLK is not valid then MCGFFCLKVALID is set to 0.

# 8.5 Initialization / Application Information

This section describes how to initialize and configure the MCG module in application. The following sections include examples on how to initialize the MCG and properly switch between the various available modes.

## 8.5.1 MCG Module Initialization Sequence

The MCG comes out of reset configured for FEI mode with the BDIV set for divide-by-2. The internal reference will stabilize in  $t_{irefst}$  microseconds before the FLL can acquire lock. As soon as the internal reference is stable, the FLL will acquire lock in  $t_{fll \ lock}$  milliseconds.

Upon POR, the internal reference will require trimming to guarantee an accurate clock. Freescale recommends using FLASH location 0xFFAE for storing the fine trim bit, FTRIM in the MCGSC register, and 0xFFAF for storing the 8-bit trim value in the MCGTRM register. The MCU will not automatically copy the values in these FLASH locations to the respective registers. Therefore, user code must copy these values from FLASH to the registers.

### NOTE

The BDIV value should not be changed to divide-by-1 without first trimming the internal reference. Failure to do so could result in the MCU running out of specification.

### 8.5.1.1 Initializing the MCG

Because the MCG comes out of reset in FEI mode, the only MCG modes which can be directly switched to upon reset are FEE, FBE, and FBI modes (see Figure 8-8). Reaching any of the other modes requires first configuring the MCG for one of these three initial modes. Care must be taken to check relevant status bits in the MCGSC register reflecting all configuration changes within each mode.

To change from FEI mode to FEE or FBE modes, follow this procedure:

- 1. Enable the external clock source by setting the appropriate bits in MCGC2.

- 2. Write to MCGC1 to select the clock mode.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

- c) MCGC1 = 0x98 (%10011000)

- RDIV (bits 5-3) set to %011, or divide-by-8 because 8 MHz / 8= 1 MHz which is in the 1 MHz to 2 MHz range required by the PLL. In BLPE mode, the configuration of the RDIV does not matter because both the FLL and PLL are disabled. Changing them only sets up the the dividers for PLL usage in PBE mode

- d) MCGC3 = 0x44 (%01000100)

- PLLS (bit 6) set to 1, selects the PLL. In BLPE mode, changing this bit only prepares the MCG for PLL usage in PBE mode

- VDIV (bits 3-0) set to %0100, or multiply-by-16 because 1 MHz reference \* 16 = 16 MHz. In BLPE mode, the configuration of the VDIV bits does not matter because the PLL is disabled. Changing them only sets up the multiply value for PLL usage in PBE mode

- e) Loop until PLLST (bit 5) in MCGSC is set, indicating that the current source for the PLLS clock is the PLL

- 3. Then, BLPE mode transitions into PBE mode:

- a) Clear LP (bit 3) in MCGC2 to 0 here to switch to PBE mode

- b) Then loop until LOCK (bit 6) in MCGSC is set, indicating that the PLL has acquired lock

- 4. Last, PBE mode transitions into PEE mode:

- a) MCGC1 = 0x18 (%00011000)

- CLKS (bits7 and 6) in MCGSC1 set to %00 in order to select the output of the PLL as the system clock source

- b) Loop until CLKST (bits 3 and 2) in MCGSC are %11, indicating that the PLL output is selected to feed MCGOUT in the current clock mode

- Now, With an RDIV of divide-by-8, a BDIV of divide-by-1, and a VDIV of multiply-by-16, MCGOUT = [(8 MHz / 8) \* 16] / 1 = 16 MHz, and the bus frequency is MCGOUT / 2, or 8 MHz

#### Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

| Field         | Description                                                                                                        |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 3:2<br>MODE   | Conversion Mode Selection. MODE bits are used to select between 12-, 10-, or 8-bit operation. See Table 10-8.      |  |  |  |  |  |

| 1:0<br>ADICLK | Input Clock Select. ADICLK bits select the input clock source to generate the internal clock ADCK. See Table 10-9. |  |  |  |  |  |

#### Table 10-6. ADCCFG Register Field Descriptions (continued)

#### Table 10-7. Clock Divide Select

| ADIV | Divide Ratio | Clock Rate      |

|------|--------------|-----------------|

| 00   | 1            | Input clock     |

| 01   | 2            | Input clock ÷ 2 |

| 10   | 4            | Input clock ÷ 4 |

| 11   | 8            | Input clock ÷ 8 |

#### Table 10-8. Conversion Modes

| MODE                        | Mode Description         |  |  |  |

|-----------------------------|--------------------------|--|--|--|

| 00 8-bit conversion (N=8)   |                          |  |  |  |

| 01                          | 12-bit conversion (N=12) |  |  |  |

| 10 10-bit conversion (N=10) |                          |  |  |  |

| 11                          | Reserved                 |  |  |  |

#### Table 10-9. Input Clock Select

| ADICLK                        | Selected Clock Source |  |  |

|-------------------------------|-----------------------|--|--|

| 00 Bus clock                  |                       |  |  |

| 01 Bus clock divided by 2     |                       |  |  |

| 10 Alternate clock (ALTCLK)   |                       |  |  |

| 11 Asynchronous clock (ADACK) |                       |  |  |

### 10.3.8 Pin Control 1 Register (APCTL1)

The pin control registers disable the I/O port control of MCU pins used as analog inputs. APCTL1 is

```

Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

```

ALTCLK for this MCU. Consult the module introduction for information on ALTCLK specific to this MCU.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from wait mode if the ADC interrupt is enabled (AIEN = 1).

# 10.4.7 MCU Stop3 Mode Operation

Stop mode is a low power-consumption standby mode during which most or all clock sources on the MCU are disabled.

## 10.4.7.1 Stop3 Mode With ADACK Disabled

If the asynchronous clock, ADACK, is not selected as the conversion clock, executing a stop instruction aborts the current conversion and places the ADC in its idle state. The contents of ADCRH and ADCRL are unaffected by stop3 mode. After exiting from stop3 mode, a software or hardware trigger is required to resume conversions.

### 10.4.7.2 Stop3 Mode With ADACK Enabled

If ADACK is selected as the conversion clock, the ADC continues operation during stop3 mode. For guaranteed ADC operation, the MCU's voltage regulator must remain active during stop3 mode. Consult the module introduction for configuration information for this MCU.

If a conversion is in progress when the MCU enters stop3 mode, it continues until completion. Conversions can be initiated while the MCU is in stop3 mode by means of the hardware trigger or if continuous conversions are enabled.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from stop3 mode if the ADC interrupt is enabled (AIEN = 1).

### NOTE

The ADC module can wake the system from low-power stop and cause the MCU to begin consuming run-level currents without generating a system level interrupt. To prevent this scenario, software should ensure the data transfer blocking mechanism (discussed in Section 10.4.4.2, "Completing Conversions) is cleared when entering stop3 and continuing ADC conversions.

### 10.4.8 MCU Stop2 Mode Operation

The ADC module is automatically disabled when the MCU enters stop2 mode. All module registers contain their reset values following exit from stop2. Therefore, the module must be re-enabled and re-configured following exit from stop2.

| ICR<br>(hex) | hex) Divider Value |    | SCL Hold<br>(Start)<br>Value | SDA Hold<br>(Stop)<br>Value |  |  |

|--------------|--------------------|----|------------------------------|-----------------------------|--|--|

| 00           | 20                 | 7  | 6                            | 11                          |  |  |

| 01           | 22                 | 7  | 7                            | 12                          |  |  |

| 02           | 24                 | 8  | 8                            | 13                          |  |  |

| 03           | 26                 | 8  | 9                            | 14                          |  |  |

| 04           | 28                 | 9  | 10                           | 15                          |  |  |

| 05           | 30                 | 9  | 11                           | 16                          |  |  |

| 06           | 34                 | 10 | 13                           | 18                          |  |  |

| 07           | 40                 | 10 | 16                           | 21                          |  |  |

| 08           | 28                 | 7  | 10                           | 15                          |  |  |

| 09           | 32                 | 7  | 12                           | 17                          |  |  |

| 0A           | 36                 | 9  | 14                           | 19                          |  |  |

| 0B           | 40                 | 9  | 16                           | 21                          |  |  |

| 0C           | 44                 | 11 | 18                           | 23                          |  |  |

| 0D           | 48                 | 11 | 20                           | 25                          |  |  |

| 0E           | 56                 | 13 | 24                           | 29                          |  |  |

| 0F           | 68                 | 13 | 30                           | 35                          |  |  |

| 10           | 48                 | 9  | 18                           | 25                          |  |  |

| 11           | 56                 | 9  | 22                           | 29                          |  |  |

| 12           | 64                 | 13 | 26                           | 33                          |  |  |

| 13           | 72                 | 13 | 30                           | 37                          |  |  |

| 14           | 80                 | 17 | 34                           | 41                          |  |  |

| 15           | 88                 | 17 | 38                           | 45                          |  |  |

| 16           | 104                | 21 | 46                           | 53                          |  |  |

| 17           | 128                | 21 | 58                           | 65                          |  |  |

| 18           | 80                 | 9  | 38                           | 41                          |  |  |

| 19           | 96                 | 9  | 46                           | 49                          |  |  |

| 1A           | 112                | 17 | 54                           | 57                          |  |  |

| 1B           | 128                | 17 | 62                           | 65                          |  |  |

| 1C           | 144                | 25 | 70                           | 73                          |  |  |

| 1D           | 160                | 25 | 78                           | 81                          |  |  |

| 1E           | 192                | 33 | 94                           | 97                          |  |  |

| 1F           | 240                | 33 | 118                          | 121                         |  |  |

| ICR<br>(hex) | SCL<br>Divider | SDA Hold<br>Value | SCL Hold<br>(Start)<br>Value | SCL Hold<br>(Stop)<br>Value |  |

|--------------|----------------|-------------------|------------------------------|-----------------------------|--|

| 20           | 160            | 17                | 78                           | 81                          |  |

| 21           | 192            | 17                | 94                           | 97                          |  |

| 22           | 224            | 33                | 110                          | 113                         |  |

| 23           | 256            | 33                | 126                          | 129                         |  |

| 24           | 288            | 49                | 142                          | 145                         |  |

| 25           | 320            | 49                | 158                          | 161                         |  |

| 26           | 384            | 65                | 190                          | 193                         |  |

| 27           | 480            | 65                | 238                          | 241                         |  |

| 28           | 320            | 33                | 158                          | 161                         |  |

| 29           | 384            | 33                | 190                          | 193                         |  |

| 2A           | 448            | 65                | 222                          | 225                         |  |

| 2B           | 512            | 65                | 254                          | 257                         |  |

| 2C           | 576            | 97                | 286                          | 289                         |  |

| 2D           | 640            | 97                | 318                          | 321                         |  |

| 2E           | 768            | 129               | 382                          | 385                         |  |

| 2F           | 960            | 129               | 478                          | 481                         |  |

| 30           | 640 65         |                   | 318                          | 321                         |  |

| 31           | 768            | 65                | 382                          | 385                         |  |

| 32           | 896            | 129               | 446                          | 449                         |  |

| 33           | 1024           | 129               | 510                          | 513                         |  |

| 34           | 1152           | 193               | 574                          | 577                         |  |

| 35           | 1280           | 193               | 638                          | 641                         |  |

| 36           | 1536           | 257               | 766                          | 769                         |  |

| 37           | 1920           | 257               | 958                          | 961                         |  |

| 38           | 1280           | 129               | 638                          | 641                         |  |

| 39           | 1536           | 129               | 766                          | 769                         |  |

| 3A           | 1792           | 257               | 894                          | 897                         |  |

| 3B           | 2048           | 257               | 1022                         | 1025                        |  |

| 3C           | 2304           | 385               | 1150                         | 1153                        |  |

| 3D           | 2560           | 385               | 1278                         | 1281                        |  |

| 3E           | 3072           | 513               | 1534                         | 1537                        |  |

| 3F           | 3840           | 513               | 1918                         | 1921                        |  |

#### Table 11-8. IICC2 Field Descriptions

| Field           | Description                                                                                                                                                                                     |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>GCAEN      | <ul> <li>General Call Address Enable. The GCAEN bit enables or disables general call address.</li> <li>0 General call address is disabled</li> <li>1 General call address is enabled</li> </ul> |  |  |  |  |

| 6<br>ADEXT      | <ul> <li>Address Extension. The ADEXT bit controls the number of bits used for the slave address.</li> <li>0 7-bit address scheme</li> <li>1 10-bit address scheme</li> </ul>                   |  |  |  |  |

| 2–0<br>AD[10:8] | Slave Address. The AD[10:8] field contains the upper three bits of the slave address in the 10-bit address scheme. This field is only valid when the ADEXT bit is set.                          |  |  |  |  |

# 11.4 Functional Description

This section provides a complete functional description of the IIC module.

### 11.4.1 IIC Protocol

The IIC bus system uses a serial data line (SDA) and a serial clock line (SCL) for data transfer. All devices connected to it must have open drain or open collector outputs. A logic AND function is exercised on both lines with external pull-up resistors. The value of these resistors is system dependent.

Normally, a standard communication is composed of four parts:

- Start signal

- Slave address transmission

- Data transfer

- Stop signal

The stop signal should not be confused with the CPU stop instruction. The IIC bus system communication is described briefly in the following sections and illustrated in Figure 11-9.

Chapter 13 Serial Communications Interface (S08SCIV4)

# 16.3 On-Chip Debug System (DBG)

Because HCS08 devices do not have external address and data buses, the most important functions of an in-circuit emulator have been built onto the chip with the MCU. The debug system consists of an 8-stage FIFO that can store address or data bus information, and a flexible trigger system to decide when to capture bus information and what information to capture. The system relies on the single-wire background debug system to access debug control registers and to read results out of the eight stage FIFO.

The debug module includes control and status registers that are accessible in the user's memory map. These registers are located in the high register space to avoid using valuable direct page memory space.

Most of the debug module's functions are used during development, and user programs rarely access any of the control and status registers for the debug module. The one exception is that the debug system can provide the means to implement a form of ROM patching. This topic is discussed in greater detail in Section 16.3.6, "Hardware Breakpoints."

### 16.3.1 Comparators A and B

Two 16-bit comparators (A and B) can optionally be qualified with the R/W signal and an opcode tracking circuit. Separate control bits allow you to ignore R/W for each comparator. The opcode tracking circuitry optionally allows you to specify that a trigger will occur only if the opcode at the specified address is actually executed as opposed to only being read from memory into the instruction queue. The comparators are also capable of magnitude comparisons to support the inside range and outside range trigger modes. Comparators are disabled temporarily during all BDC accesses.

The A comparator is always associated with the 16-bit CPU address. The B comparator compares to the CPU address or the 8-bit CPU data bus, depending on the trigger mode selected. Because the CPU data bus is separated into a read data bus and a write data bus, the RWAEN and RWA control bits have an additional purpose, in full address plus data comparisons they are used to decide which of these buses to use in the comparator B data bus comparisons. If RWAEN = 1 (enabled) and RWA = 0 (write), the CPU's write data bus is used. Otherwise, the CPU's read data bus is used.

The currently selected trigger mode determines what the debugger logic does when a comparator detects a qualified match condition. A match can cause:

- Generation of a breakpoint to the CPU

- Storage of data bus values into the FIFO

- Starting to store change-of-flow addresses into the FIFO (begin type trace)

- Stopping the storage of change-of-flow addresses into the FIFO (end type trace)

### 16.3.2 Bus Capture Information and FIFO Operation

The usual way to use the FIFO is to setup the trigger mode and other control options, then arm the debugger. When the FIFO has filled or the debugger has stopped storing data into the FIFO, you would read the information out of it in the order it was stored into the FIFO. Status bits indicate the number of words of valid information that are in the FIFO as data is stored into it. If a trace run is manually halted by writing 0 to ARM before the FIFO is full (CNT = 1:0:0:0), the information is shifted by one position and

# A.6 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

|    | С | Characteristic                                                     | Symbol                               | Condition                            | Min                    | Typ <sup>1</sup> | Max                  | Unit |

|----|---|--------------------------------------------------------------------|--------------------------------------|--------------------------------------|------------------------|------------------|----------------------|------|

| 1  | _ | Operating Voltage                                                  | V <sub>DD</sub>                      |                                      | 2.7                    | _                | 5.5                  | V    |

|    | Ρ | All I/O pins, low-drive strength                                   |                                      | 5 V, I <sub>Load</sub> = -2 mA       | V <sub>DD</sub> – 1.5  | —                | —                    |      |

|    | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = -0.6 mA     | V <sub>DD</sub> – 1.5  | _                | —                    |      |

|    | С | Output high                                                        | V <sub>OH</sub>                      | 5 V, I <sub>Load</sub> = -0.4 mA     | V <sub>DD</sub> – 0.8  | _                | —                    | v    |

| 2  | С | voltage                                                            |                                      | 3 V, I <sub>Load</sub> = -0.24 mA    | V <sub>DD</sub> – 0.8  | _                | —                    |      |

|    | Ρ | All I/O pins, high-drive strength                                  |                                      | 5 V, I <sub>Load</sub> = -10 mA      | V <sub>DD</sub> – 1.5  | _                | —                    |      |

|    | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = -3 mA       | V <sub>DD</sub> – 1.5  | _                | —                    |      |

|    | С |                                                                    |                                      | 5 V, I <sub>Load</sub> = -2 mA       | V <sub>DD</sub> – 0.8  | —                | —                    |      |

|    | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = -0.4 mA     | V <sub>DD</sub> – 0.8  | _                | —                    |      |

| 3  | С | Output Max total I <sub>OH</sub> for all ports                     | I <sub>OHT</sub>                     | 5 V                                  | 0                      | _                | -100                 | mA   |

|    |   | high current                                                       |                                      | 3 V                                  | 0                      | —                | -60                  |      |

|    | Ρ | All I/O pins, low-drive strength                                   |                                      | 5 V, I <sub>Load</sub> = 2 mA        | —                      | —                | 1.5                  |      |

|    | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = 0.6 mA      | —                      | _                | 1.5                  |      |

| -  | С | Output low                                                         |                                      | 5 V, I <sub>Load</sub> = 0.4 mA      | _                      | _                | 0.8                  |      |

| 4  | С | voltage                                                            | V <sub>OL</sub>                      | 3 V, I <sub>Load</sub> = 0.24 mA     | —                      | _                | 0.8                  | V    |

|    | Ρ | All I/O pins, high-drive strength                                  |                                      | 5 V, I <sub>Load</sub> = 10 mA       | —                      | _                | 1.5                  |      |

|    | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = 3 mA        | —                      | _                | 1.5                  |      |

|    | С |                                                                    |                                      | 5 V, I <sub>Load</sub> = 2 mA        | —                      | —                | 0.8                  |      |

|    | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = 0.4 mA      | —                      | _                | 0.8                  |      |

| 5  | С | Output Max total I <sub>OL</sub> for all ports                     | I <sub>OLT</sub>                     | 5 V                                  | 0                      | —                | 100                  | mA   |

|    |   | low current                                                        |                                      | 3 V                                  | 0                      | —                | 60                   |      |

| 6  | С | Input high voltage; all digital inputs                             | $V_{IH}$                             | 5V                                   | 0.65 x V <sub>DD</sub> | —                | —                    |      |

| 7  | С | Input low voltage; all digital inputs                              | $V_{IL}$                             | 5V                                   | —                      | —                | $0.35 \times V_{DD}$ | V    |

| 8  | С | Input hysteresis                                                   | V <sub>hys</sub>                     |                                      | $0.06 \times V_{DD}$   |                  |                      | mV   |

| 9  | Ρ | Input leakage<br>current (Per pin)<br>all input only pins          | I <sub>In</sub>                      | $V_{ln} = V_{DD} \text{ or } V_{SS}$ | —                      | 0.1              | 1                    | μA   |

| 10 | Ρ | Hi-Z (off-state) leakage<br>current (per pin)<br>all input/output  | I <sub>OZ</sub>                      | $V_{In} = V_{DD} \text{ or } V_{SS}$ | —                      | 0.1              | 1                    | μA   |

| 11 | P | Pullup resistors (or Pulldown <sup>2</sup> resistors when enabled) | R <sub>PU</sub> ,<br>R <sub>PD</sub> | 5 V                                  | 20                     | 45               | 65                   | kΩ   |

|    | С |                                                                    |                                      | 3 V                                  | 20                     | 45               | 65                   |      |

| 12 | Т | Input Capacitance, all pins                                        | C <sub>In</sub>                      |                                      | _                      | _                | 8                    | pF   |

| 13 | D | RAM retention voltage                                              | V <sub>RAM</sub>                     |                                      | —                      | 0.6              | 1.0                  | V    |

#### **Table A-6. DC Characteristics**

**Appendix A Electrical Characteristics**

NOTES:

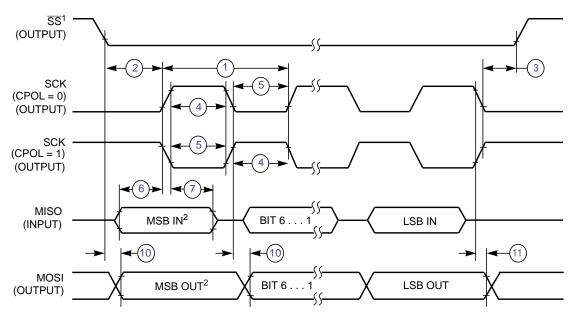

1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

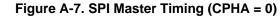

1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

MC9S08DN60 Series Data Sheet, Rev 3

# Appendix B Timer Pulse-Width Modulator (TPMV2)

### NOTE

This chapter refers to S08TPM version 2, which applies to the 3M05C and older mask sets of this device. )M74K and newer mask set devices use S08TPM version 3. If your device uses mask 0M74K or newer, please refer to Chapter 15, "Timer Pulse-Width Modulator (S08TPMV3) for information pertaining to that module.

The TPM uses one input/output (I/O) pin per channel, TPMxCHn where x is the TPM number (for example, 1 or 2) and n is the channel number (for example, 0–4). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information).

### B.0.1 Features

The TPM has the following features:

- Each TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on all channels

- Clock sources independently selectable per TPM (multiple TPMs device)

- Selectable clock sources (device dependent): bus clock, fixed system clock, external pin

- Clock prescaler taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- 16-bit free-running or up/down (CPWM) count operation

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus a terminal count interrupt for each TPM module (multiple TPMs device)

- Channel features:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

### B.0.2 Block Diagram

Figure B-1 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

MC9S08DN60 Series Data Sheet, Rev 3