#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 25                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 1.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 10x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08dn32f2mlc |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

To maintain I/O states for pins that were configured as general-purpose I/O before entering stop2, the user must restore the contents of the I/O port registers, which have been saved in RAM, to the port registers before writing to the PPDACK bit. If the port registers are not restored from RAM before writing to PPDACK, then the pins will switch to their reset states when PPDACK is written.

For pins that were configured as peripheral I/O, the user must reconfigure the peripheral module that interfaces to the pin before writing to the PPDACK bit. If the peripheral module is not enabled before writing to PPDACK, the pins will be controlled by their associated port control registers when the I/O latches are opened.

## 3.6.3 On-Chip Peripheral Modules in Stop Modes

When the MCU enters any stop mode, system clocks to the internal peripheral modules are stopped. Even in the exception case (ENBDM = 1), where clocks to the background debug logic continue to operate, clocks to the peripheral systems are halted to reduce power consumption. Refer to Section 3.6.2, "Stop2 Mode" and Section 3.6.1, "Stop3 Mode" for specific information on system behavior in stop modes.

| Deviational             | Mode                       |                            |  |  |  |

|-------------------------|----------------------------|----------------------------|--|--|--|

| Peripheral              | Stop2                      | Stop3                      |  |  |  |

| CPU                     | Off                        |                            |  |  |  |

| RAM                     | Standby                    | Standby                    |  |  |  |

| Flash/EEPROM            | Off                        | Standby                    |  |  |  |

| Parallel Port Registers | Off                        | Standby                    |  |  |  |

| ACMP                    | Off                        | Off                        |  |  |  |

| ADC                     | Off                        | Optionally On <sup>1</sup> |  |  |  |

| IIC                     | Off                        | Standby                    |  |  |  |

| MCG                     | Off                        | Optionally On <sup>2</sup> |  |  |  |

| RTC                     | Optionally On <sup>3</sup> | Optionally On <sup>3</sup> |  |  |  |

| SCI                     | Off                        | Standby                    |  |  |  |

| SPI                     | Off                        | Standby                    |  |  |  |

| ТРМ                     | Off                        | Standby                    |  |  |  |

| Voltage Regulator       | Off                        | Optionally On <sup>4</sup> |  |  |  |

| XOSC                    | Off Optionally 0           |                            |  |  |  |

| I/O Pins                | States Held                | States Held                |  |  |  |

| BDM                     | Off <sup>6</sup>           | Optionally On              |  |  |  |

| LVD/LVW                 | Off <sup>7</sup>           | Optionally On              |  |  |  |

| Table 3-2. Stop Mode Behavior | Table 3-2 | 2. Stop | Mode | <b>Behavior</b> |

|-------------------------------|-----------|---------|------|-----------------|

|-------------------------------|-----------|---------|------|-----------------|

<sup>1</sup> Requires the asynchronous ADC clock and LVD to be enabled, else in standby.

<sup>2</sup> IRCLKEN and IREFSTEN set in MCGC1, else in standby.

<sup>3</sup> Requires the RTC to be enabled, else in standby.

<sup>4</sup> Requires the LVD or BDC to be enabled.

#### NOTE

The FCBEF flag will not set after launching the sector erase abort command. If an attempt is made to start a new command write sequence with a sector erase abort operation active, the FACCERR flag in the FSTAT register will be set. A new command write sequence may be started after clearing the ACCERR flag, if set.

#### NOTE

The sector erase abort command should be used sparingly since a sector erase operation that is aborted counts as a complete program/erase cycle.

### 4.5.6 Access Errors

An access error occurs whenever the command execution protocol is violated.

Any of the following specific actions will cause the access error flag (FACCERR) in FSTAT to be set. FACCERR must be cleared by writing a 1 to FACCERR in FSTAT before any command can be processed.

- Writing to a Flash address before the internal Flash and EEPROM clock frequency has been set by writing to the FCDIV register.

- Writing to a Flash address while FCBEF is not set. (A new command cannot be started until the command buffer is empty.)

- Writing a second time to a Flash address before launching the previous command. (There is only one write to Flash for every command.)

- Writing a second time to FCMD before launching the previous command. (There is only one write to FCMD for every command.)

- Writing to any Flash control register other than FCMD after writing to a Flash address.

- Writing any command code other than the six allowed codes (0x05, 0x20, 0x25, 0x40, 0x41, or 0x47) to FCMD.

- Writing any Flash control register other than to write to FSTAT (to clear FCBEF and launch the command) after writing the command to FCMD.

- The MCU enters stop mode while a program or erase command is in progress. (The command is aborted.)

- Writing the byte program, burst program, sector erase or sector erase abort command code (0x20, 0x25, 0x40, or 0x47) with a background debug command while the MCU is secured. (The background debug controller can do blank check and mass erase commands only when the MCU is secure.)

- Writing 0 to FCBEF to cancel a partial command.

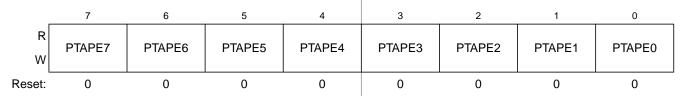

## 6.5.1.3 Port A Pull Enable Register (PTAPE)

Figure 6-5. Internal Pull Enable for Port A Register (PTAPE)

#### Table 6-3. PTAPE Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0        | Internal Pull Enable for Port A Bits — Each of these control bits determines if the internal pull-up or pull-down                                                                                                                                                                                                                      |

| PTAPE[7:0] | <ul> <li>device is enabled for the associated PTA pin. For port A pins that are configured as outputs, these bits have no effect and the internal pull devices are disabled.</li> <li>0 Internal pull-up/pull-down device disabled for port A bit n.</li> <li>1 Internal pull-up/pull-down device enabled for port A bit n.</li> </ul> |

#### NOTE

Pull-down devices only apply when using pin interrupt functions, when corresponding edge select and pin select functions are configured.

### 6.5.1.4 Port A Slew Rate Enable Register (PTASE)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTASE7 | PTASE6 | PTASE5 | PTASE4 | PTASE3 | PTASE2 | PTASE1 | PTASE0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-6. Slew Rate Enable for Port A Register (PTASE)

#### Table 6-4. PTASE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTASE[7:0] | <ul> <li>Output Slew Rate Enable for Port A Bits — Each of these control bits determines if the output slew rate control is enabled for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port A bit n.</li> <li>Output slew rate control enabled for port A bit n.</li> </ul> |

**Note:** Slew rate reset default values may differ between engineering samples and final production parts. Always initialize slew rate control to the desired value to ensure correct operation.

**Chapter 6 Parallel Input/Output Control**

# 6.5.2 Port B Registers

Port B is controlled by the registers listed below.

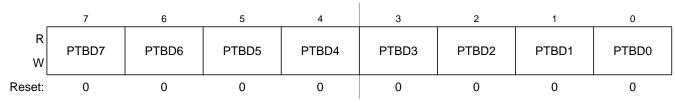

## 6.5.2.1 Port B Data Register (PTBD)

#### Figure 6-11. Port B Data Register (PTBD)

#### Table 6-9. PTBD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups/pull-downs disabled. |

### 6.5.2.2 Port B Data Direction Register (PTBDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-12. Port B Data Direction Register (PTBDD)

#### Table 6-10. PTBDD Register Field Descriptions

| Field | Description                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data Direction for Port B Bits</b> — These read/write bits control the direction of port B pins and what is read for PTBD reads.                                                 |

|       | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn.</li> </ul> |

**Chapter 6 Parallel Input/Output Control**

# 6.5.3 Port C Registers

Port C is controlled by the registers listed below.

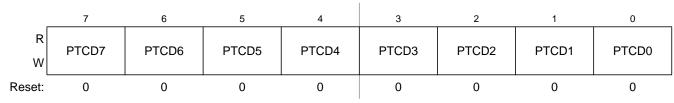

## 6.5.3.1 Port C Data Register (PTCD)

#### Figure 6-19. Port C Data Register (PTCD)

#### Table 6-17. PTCD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCD[7:0] | Port C Data Register Bits — For port C pins that are inputs, reads return the logic level on the pin. For port C pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port C pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTCD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups disabled. |

## 6.5.3.2 Port C Data Direction Register (PTCDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTCDD7 | PTCDD6 | PTCDD5 | PTCDD4 | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-20. Port C Data Direction Register (PTCDD)

#### Table 6-18. PTCDD Register Field Descriptions

| Field             | Description                                                                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCDD[7:0] | <b>Data Direction for Port C Bits</b> — These read/write bits control the direction of port C pins and what is read for PTCD reads.                                             |

|                   | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port C bit n and PTCD reads return the contents of PTCDn.</li> </ol> |

# 7.2.3 Stack Pointer (SP)

This 16-bit address pointer register points at the next available location on the automatic last-in-first-out (LIFO) stack. The stack may be located anywhere in the 64-Kbyte address space that has RAM and can be any size up to the amount of available RAM. The stack is used to automatically save the return address for subroutine calls, the return address and CPU registers during interrupts, and for local variables. The AIS (add immediate to stack pointer) instruction adds an 8-bit signed immediate value to SP. This is most often used to allocate or deallocate space for local variables on the stack.

SP is forced to 0x00FF at reset for compatibility with the earlier M68HC05 Family. HCS08 programs normally change the value in SP to the address of the last location (highest address) in on-chip RAM during reset initialization to free up direct page RAM (from the end of the on-chip registers to 0x00FF).

The RSP (reset stack pointer) instruction was included for compatibility with the M68HC05 Family and is seldom used in new HCS08 programs because it only affects the low-order half of the stack pointer.

# 7.2.4 Program Counter (PC)

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

During normal program execution, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, interrupt, and return operations load the program counter with an address other than that of the next sequential location. This is called a change-of-flow.

During reset, the program counter is loaded with the reset vector that is located at 0xFFFE and 0xFFFF. The vector stored there is the address of the first instruction that will be executed after exiting the reset state.

# 7.2.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask (I) and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code bits in general terms. For a more detailed explanation of how each instruction sets the CCR bits, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMv1.

#### Chapter 11 Inter-Integrated Circuit (S08IICV2)

the transition from master to slave mode does not generate a stop condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

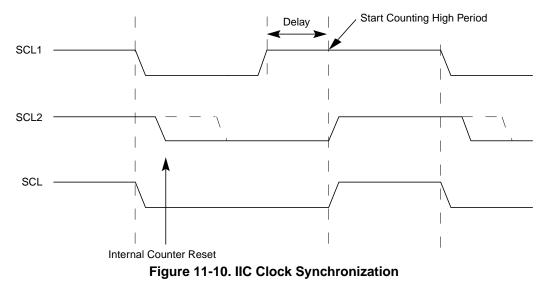

## 11.4.1.7 Clock Synchronization

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 11-10). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

### 11.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such a case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

### 11.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

# Chapter 14 Real-Time Counter (S08RTCV1)

# 14.1 Introduction

The RTC module consists of one 8-bit counter, one 8-bit comparator, several binary-based and decimal-based prescaler dividers, three clock sources, and one programmable periodic interrupt. This module can be used for time-of-day, calendar or any task scheduling functions. It can also serve as a cyclic wake up from low power modes without the need of external components.

All devices in the MC9S08DN60 Series feature the RTC.

# 14.1.1 RTC Clock Signal Names

References to ERCLK and IRCLK in this chapter correspond to signals MCGERCLK and MCGIRCLK, respectively.

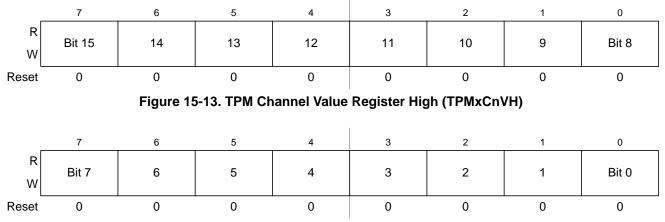

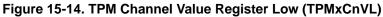

In input capture mode, reading either byte (TPMxCnVH or TPMxCnVL) latches the contents of both bytes into a buffer where they remain latched until the other half is read. This latching mechanism also resets (becomes unlatched) when the TPMxCnSC register is written (whether BDM mode is active or not). Any write to the channel registers will be ignored during the input capture mode.

When BDM is active, the coherency mechanism is frozen (unless reset by writing to TPMxCnSC register) such that the buffer latches remain in the state they were in when the BDM became active, even if one or both halves of the channel register are read while BDM is active. This assures that if the user was in the middle of reading a 16-bit register when BDM became active, it will read the appropriate value from the other half of the 16-bit value after returning to normal execution. The value read from the TPMxCnVH and TPMxCnVL registers in BDM mode is the value of these registers and not the value of their read buffer.

In output compare or PWM modes, writing to either byte (TPMxCnVH or TPMxCnVL) latches the value into a buffer. After both bytes are written, they are transferred as a coherent 16-bit value into the timer-channel registers according to the value of CLKSB:CLKSA bits and the selected mode, so:

- If (CLKSB:CLKSA = 0:0), then the registers are updated when the second byte is written.

- If (CLKSB:CLKSA not = 0:0 and in output compare mode) then the registers are updated after the second byte is written and on the next change of the TPM counter (end of the prescaler counting).

- If (CLKSB:CLKSA not = 0:0 and in EPWM or CPWM modes), then the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter then the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

The latching mechanism may be manually reset by writing to the TPMxCnSC register (whether BDM mode is active or not). This latching mechanism allows coherent 16-bit writes in either big-endian or little-endian order which is friendly to various compiler implementations.

When BDM is active, the coherency mechanism is frozen such that the buffer latches remain in the state they were in when the BDM became active even if one or both halves of the channel register are written while BDM is active. Any write to the channel registers bypasses the buffer latches and directly write to the channel register while BDM is active. The values written to the channel register while BDM is active

# 15.4.1.3 Counting Modes

The main timer counter has two counting modes. When center-aligned PWM is selected (CPWMS=1), the counter operates in up/down counting mode. Otherwise, the counter operates as a simple up counter. As an up counter, the timer counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts up from 0x0000 through its terminal count and then down to 0x0000 where it changes back to up counting. Both 0x0000 and the terminal count value are normal length counts (one timer clock period long). In this mode, the timer overflow flag (TOF) becomes set at the end of the terminal-count period (as the count changes to the next lower count value).

## 15.4.1.4 Manual Counter Reset

The main timer counter can be manually reset at any time by writing any value to either half of TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only half of the counter was read before resetting the count.

# 15.4.2 Channel Mode Selection

Provided CPWMS=0, the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and edge-aligned PWM.

### 15.4.2.1 Input Capture Mode

With the input-capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input-capture channel, the TPM latches the contents of the TPM counter into the channel-value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

In input capture mode, the TPMxCnVH and TPMxCnVL registers are read only.

When either half of the 16-bit capture register is read, the other half is latched into a buffer to support coherent 16-bit accesses in big-endian or little-endian order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An input capture event sets a flag bit (CHnF) which may optionally generate a CPU interrupt request.

While in BDM, the input capture function works as configured by the user. When an external event occurs, the TPM latches the contents of the TPM counter (which is frozen because of the BDM mode) into the channel value registers and sets the flag bit.

# 15.4.2.2 Output Compare Mode

With the output-compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel-value registers of an output-compare channel, the TPM can set, clear, or toggle the channel pin.

Input capture, output compare, and edge-aligned PWM functions do not make sense when the counter is operating in up/down counting mode so this implies that all active channels within a TPM must be used in CPWM mode when CPWMS=1.

The TPM may be used in an 8-bit MCU. The settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers.

In center-aligned PWM mode, the TPMxCnVH:L registers are updated with the value of their write buffer according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter, the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

When TPMxCNTH:TPMxCNTL=TPMxMODH:TPMxMODL, the TPM can optionally generate a TOF interrupt (at the end of this count).

Writing to TPMxSC cancels any values written to TPMxMODH and/or TPMxMODL and resets the coherency mechanism for the modulo registers. Writing to TPMxCnSC cancels any values written to the channel value registers and resets the coherency mechanism for TPMxCnVH:TPMxCnVL.

# 15.5 Reset Overview

## 15.5.1 General

The TPM is reset whenever any MCU reset occurs.

## 15.5.2 Description of Reset Operation

Reset clears the TPMxSC register which disables clocks to the TPM and disables timer overflow interrupts (TOIE=0). CPWMS, MSnB, MSnA, ELSnB, and ELSnA are all cleared which configures all TPM channels for input-capture operation with the associated pins disconnected from I/O pin logic (so all MCU pins related to the TPM revert to general purpose I/O pins).

# 15.6 Interrupts

## 15.6.1 General

The TPM generates an optional interrupt for the main counter overflow and an interrupt for each channel. The meaning of channel interrupts depends on each channel's mode of operation. If the channel is configured for input capture, the interrupt flag is set each time the selected input capture edge is recognized. If the channel is configured for output compare or PWM modes, the interrupt flag is set each time the main timer counter matches the value in the 16-bit channel value register.

#### 15.6.2.1.2 Center-Aligned PWM Case

When CPWMS=1, TOF gets set when the timer counter changes direction from up-counting to down-counting at the end of the terminal count (the value in the modulo register). In this case the TOF corresponds to the end of a PWM period.

### 15.6.2.2 Channel Event Interrupt Description

The meaning of channel interrupts depends on the channel's current mode (input-capture, output-compare, edge-aligned PWM, or center-aligned PWM).

#### 15.6.2.2.1 Input Capture Events

When a channel is configured as an input capture channel, the ELSnB:ELSnA control bits select no edge (off), rising edges, falling edges or any edge as the edge which triggers an input capture event. When the selected edge is detected, the interrupt flag is set. The flag is cleared by the two-step sequence described in Section 15.6.2, "Description of Interrupt Operation."

#### 15.6.2.2.2 Output Compare Events

When a channel is configured as an output compare channel, the interrupt flag is set each time the main timer counter matches the 16-bit value in the channel value register. The flag is cleared by the two-step sequence described Section 15.6.2, "Description of Interrupt Operation."

#### 15.6.2.2.3 PWM End-of-Duty-Cycle Events

For channels configured for PWM operation there are two possibilities. When the channel is configured for edge-aligned PWM, the channel flag gets set when the timer counter matches the channel value register which marks the end of the active duty cycle period. When the channel is configured for center-aligned PWM, the timer count matches the channel value register twice during each PWM cycle. In this CPWM case, the channel flag is set at the start and at the end of the active duty cycle period which are the times when the timer counter matches the channel value register. The flag is cleared by the two-step sequence described Section 15.6.2, "Description of Interrupt Operation."

# 15.7 The Differences from TPM v2 to TPM v3

1. Write to TPMxCNTH:L registers (Section 15.3.2, "TPM-Counter Registers (TPMxCNTH:TPMxCNTL)) [SE110-TPM case 7]

Any write to TPMxCNTH or TPMxCNTL registers in TPM v3 clears the TPM counter (TPMxCNTH:L) and the prescaler counter. Instead, in the TPM v2 only the TPM counter is cleared in this case.

- 2. Read of TPMxCNTH:L registers (Section 15.3.2, "TPM-Counter Registers (TPMxCNTH:TPMxCNTL))

- In TPM v3, any read of TPMxCNTH:L registers during BDM mode returns the value of the TPM counter that is frozen. In TPM v2, if only one byte of the TPMxCNTH:L registers was read before the BDM mode became active, then any read of TPMxCNTH:L registers during

Chapter 15 Timer/PWM Module (S08TPMV3)

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 2<br>WS  | <ul> <li>Wait or Stop Status — When the target CPU is in wait or stop mode, most BDC commands cannot function. However, the BACKGROUND command can be used to force the target CPU out of wait or stop and into active background mode where all BDC commands work. Whenever the host forces the target MCU into active background mode, the host should issue a READ_STATUS command to check that BDMACT = 1 before attempting other BDC commands.</li> <li>0 Target CPU is running user application code or in active background mode (was not in wait or stop mode when background became active)</li> <li>1 Target CPU is in wait or stop mode, or a BACKGROUND command was used to change from wait or stop to active background mode</li> </ul> |  |  |  |  |  |  |

| 1<br>WSF | <ul> <li>Wait or Stop Failure Status — This status bit is set if a memory access command failed due to the target CPU executing a wait or stop instruction at or about the same time. The usual recovery strategy is to issue a BACKGROUND command to get out of wait or stop mode into active background mode, repeat the command that failed, then return to the user program. (Typically, the host would restore CPU registers and stack values and re-execute the wait or stop instruction.)</li> <li>Memory access did not conflict with a wait or stop instruction</li> <li>Memory access command failed because the CPU entered wait or stop mode</li> </ul>                                                                                   |  |  |  |  |  |  |

| 0<br>DVF | Data Valid Failure Status — This status bit is not used in the MC9S08DN60 Series because it does not have any slow access memory.         0 Memory access did not conflict with a slow memory access         1 Memory access command failed because CPU was not finished with a slow memory access                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

#### Table 16-2. BDCSCR Register Field Descriptions (continued)

### 16.4.1.2 BDC Breakpoint Match Register (BDCBKPT)

This 16-bit register holds the address for the hardware breakpoint in the BDC. The BKPTEN and FTS control bits in BDCSCR are used to enable and configure the breakpoint logic. Dedicated serial BDC commands (READ\_BKPT and WRITE\_BKPT) are used to read and write the BDCBKPT register but is not accessible to user programs because it is not located in the normal memory map of the MCU. Breakpoints are normally set while the target MCU is in active background mode before running the user application program. For additional information about setup and use of the hardware breakpoint logic in the BDC, refer to Section 16.2.4, "BDC Hardware Breakpoint."

# 16.4.2 System Background Debug Force Reset Register (SBDFR)

This register contains a single write-only control bit. A serial background mode command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

#### **Appendix A Electrical Characteristics**

| Num | С | Rating                                                                                             | Symbol                        | Min                       | Typical            | Max                                                        | Unit              |

|-----|---|----------------------------------------------------------------------------------------------------|-------------------------------|---------------------------|--------------------|------------------------------------------------------------|-------------------|

| 18  | Т | RMS frequency variation of a single clock cycle measured 625 ns after reference edge. <sup>6</sup> | f <sub>pll_cycjit_625ns</sub> | _                         | 0.566 <sup>4</sup> | _                                                          | %f <sub>pll</sub> |

| 19  | Т | Maximum frequency variation averaged over 625 ns window.                                           | f <sub>pll_maxjit_625ns</sub> | _                         | 0.113              | _                                                          | %f <sub>pll</sub> |

| 20  | D | Lock entry frequency tolerance <sup>7</sup>                                                        | D <sub>lock</sub>             | ± 1.49                    | _                  | ± 2.98                                                     | %                 |

| 21  | D | Lock exit frequency tolerance <sup>8</sup>                                                         | D <sub>unl</sub>              | ± 4.47                    | _                  | ± 5.97                                                     | %                 |

| 22  | D | Lock time - FLL                                                                                    | t <sub>fll_lock</sub>         | _                         | _                  | t <sub>fll_acquire+</sub><br>1075(1/ <sup>f</sup> int_t)   | s                 |

| 23  | D | Lock time - PLL                                                                                    | t <sub>pll_lock</sub>         |                           | _                  | t <sub>pll_acquire+</sub><br>1075(1/ <sup>f</sup> pll_ref) | S                 |

| 24  | D | Loss of external clock minimum frequency -<br>RANGE = 0                                            | f <sub>loc_low</sub>          | (3/5) x f <sub>int</sub>  | _                  | _                                                          | kHz               |

| 25  | D | Loss of external clock minimum frequency -<br>RANGE = 1                                            | f <sub>loc_high</sub>         | (16/5) x f <sub>int</sub> | _                  | _                                                          | kHz               |

#### Table A-12. MCG Frequency Specifications (Temperature Range = -40 to 125°C Ambient) (continued)

<sup>1</sup> TRIM register at default value (0x80) and FTRIM control bit at default value (0x0).

<sup>2</sup> This specification applies to any time the FLL reference source or reference divider is changed, trim value changed or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

<sup>3</sup> This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

<sup>4</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>BUS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval. Jitter measurements are based upon a 40MHz MCGOUT clock frequency.

<sup>5</sup> In some specifications, this value is described as "long term accuracy of PLL output clock (averaged over 2 ms)" with symbol "f<sub>oll litter 2ms</sub>." The parameter is unchanged, but the description has been changed for clarification purposes.

<sup>6</sup> In some specifications, this value is described as "Jitter of PLL output clock measured over 625 ns" with symbol "f<sub>oll litter 625ns</sub>." The parameter is unchanged, but the description has been changed for clarification purposes.

<sup>7</sup> Below D<sub>lock</sub> minimum, the MCG is guaranteed to enter lock. Above D<sub>lock</sub> maximum, the MCG will not enter lock. But if the MCG is already in lock, then the MCG may stay in lock.

<sup>8</sup> Below D<sub>unl</sub> minimum, the MCG will not exit lock if already in lock. Above D<sub>unl</sub> maximum, the MCG is guaranteed to exit lock.

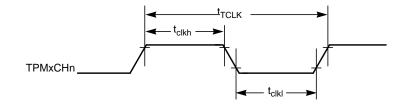

Figure A-5. Timer External Clock

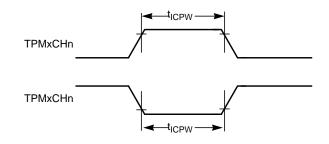

Figure A-6. Timer Input Capture Pulse

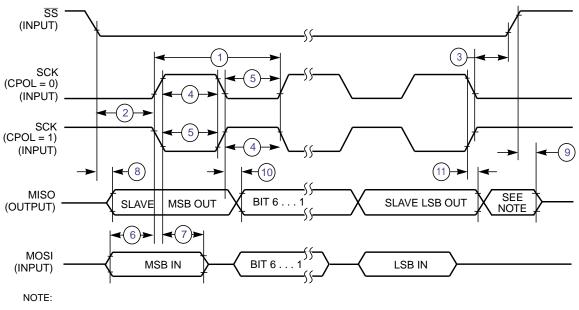

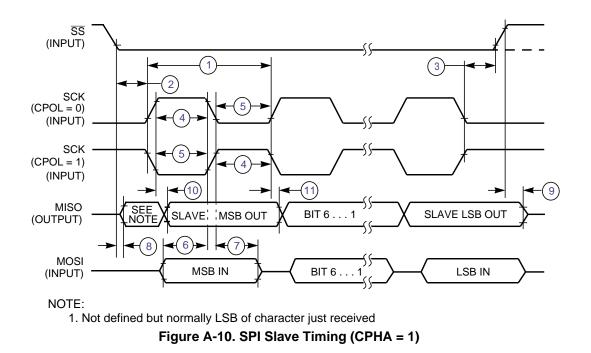

1. Not defined but normally MSB of character just received

MC9S08DN60 Series Data Sheet, Rev 3

#### Appendix B Timer Pulse-Width Modulator (TPMV2)

As an up-counter, the main 16-bit counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts upward from 0x0000 through its terminal count and then counts downward to 0x0000 where it returns to up-counting. Both 0x0000 and the terminal count value (value in TPMxMODH:TPMxMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The 0x0000 count value corresponds to the center of a period.)

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter for read operations. Whenever either byte of the counter is read (TPMxCNTH or TPMxCNTL), both bytes are captured into a buffer so when the other byte is read, the value will represent the other byte of the count at the time the first byte was read. The counter continues to count normally, but no new value can be read from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer count TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only one byte of the counter was read before resetting the count.

# B.3.2 Channel Mode Selection

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

## B.3.2.1 Input Capture Mode

With the input capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter into the channel value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

$\overline{3}$  datums a, b, and d to be determined at datum plane h.

$\overline{/4.}$  dimensions to be determined at seating plane datum c.

<u>/5</u> DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION: 0.07 MM.

<u>6</u> DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

$\overline{/7.}$  exact shape of each corner is optional.

$\overline{/8.}$  These dimensions apply to the flat section of the lead between 0.1 MM and 0.25 MM from the lead tip.

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |        |  |

|---------------------------------------------------------|--------------------|--------------------------|----------------------------|--------|--|

| TITLE:                                                  |                    | DOCUMENT NO: 98ASH70029A |                            | RE∨: D |  |

| LOW PROFILE QUAD FLAT PA                                | ````               | CASE NUMBER              | 19 MAY 2005                |        |  |

| 32 LEAD, 0.8 PITCH (7 X                                 | / X 1.4)           | STANDARD: JE             | DEC MS-026 BBA             |        |  |