Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | HC05                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 4MHz                                                                 |

| Connectivity               | -                                                                    |

| Peripherals                | LED, POR                                                             |

| Number of I/O              | 32                                                                   |

| Program Memory Size        | 3.75KB (3.75K x 8)                                                   |

| Program Memory Type        | OTP                                                                  |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 192 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                            |

| Data Converters            | A/D 4x8b                                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 44-QFP                                                               |

| Supplier Device Package    | 44-QFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc705sr3cfbe |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC05SR3 MC68HC705SR3

# High-density Complementary Metal Oxide Semiconductor (HCMOS) Microcontroller Units

All Trade Marks recognized. This document contains information on new products. Specifications and information herein are subject to change without notice.

All products are sold on Freescale's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Freescale's Terms & Conditions of Supply is available on request.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale was negligent regarding the design or manufacture of the part. Freescale, Inc. is an Equal Opportunity/Affirmative Action Employeer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Freescale office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

### LIST OF FIGURES

| Figure<br>Number | TITLE                                                       | Page<br>Number |

|------------------|-------------------------------------------------------------|----------------|

| 1-1              | MC68HC05SR3/ MC68HC705SR3 Block Diagram                     | 1-3            |

| 2-1              | Oscillator Connections                                      |                |

| 2-2              | Typical Oscillator Frequency for Selected External Resistor | 2-4            |

| 2-3              | Typical Oscillator Frequency for Wire-Strap Connection      |                |

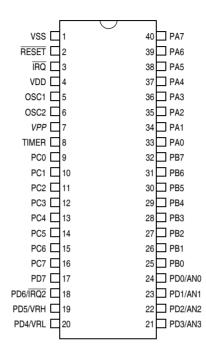

| 2-4              | Pin Assignment for 40-pin PDIP                              |                |

| 2-5              | Pin Assignment for 42-pin SDIP                              |                |

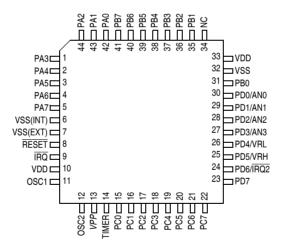

| 2-6              | Pin Assignment for 44-pin QFP                               |                |

| 3-1              | Port I/O Circuitry                                          |                |

| 3-2              | Typical IOL vs VOL @VDD=5V                                  |                |

| 3-3              | Typical IOH vs VOH @VDD=5V                                  |                |

| 3-4              | Typical IOL vs VOL @VDD=3V                                  |                |

| 3-5              | Typical IOL vs VOL @VDD=3V                                  |                |

| 4-1              | MC68HC05SR3/MC68HC705SR3 Memory Map                         |                |

| 5-1              | Interrupt Stacking Order                                    |                |

| 5-2              | Hardware Interrupt Processing Flowchart                     |                |

| 5-3              | External Interrupt                                          |                |

| 5-4              | Keyboard Interrupt Circuitry                                |                |

| 6-1              | Timer Block Diagram                                         |                |

| 7-1              | ADC Converter Block Diagram                                 |                |

| 8-1              | Programming model                                           |                |

| 8-2              | Stacking order                                              |                |

| 9-1              | STOP and WAIT Mode Flowcharts                               |                |

| 10-1             | MC68HC05SR3 Self-Check Circuit                              |                |

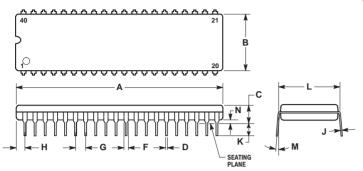

| 12-1             | 40-pin DIP Package                                          |                |

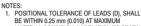

| 12-2             | 42-pin SDIP Package                                         |                |

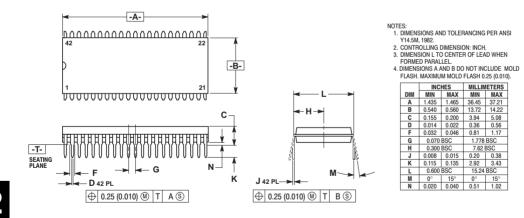

| 12-3             | 44-pin QFP Package                                          | 12-3           |

THIS PAGE LEFT BLANK INTENTIONALLY

# **1** GENERAL DESCRIPTION

The MC68HC05SR3 HCMOS microcontroller is a member of the M68HC05 family of low-cost single-chip microcontrollers. This 8-bit microcontroller unit (MCU) contains on-chip oscillator, CPU, RAM, ROM, I/O, Timer, and Analog-to-Digital Converter. The MC68HC05SR3 is pin compatible with the MC6805R3 and is provided as a low power upgrade path for MC6805R3 applications. The low power advantage of CMOS is combined with the addition of I/O and port modifications which help eliminate external components in cost sensitive applications.

The MC68HC705SR3 is an EPROM version of the MC68HC05SR3; it is available in windowed and OTP packages. All references to the MC68HC05SR3 apply equally to the MC68HC705SR3, unless otherwise stated. *References specific to the MC68HC705SR3 are italicized in the text and also, for quick reference, they are summarized in Appendix A.*

#### 1.1 Features

- Fully static chip design featuring the industry standard 8-bit M68HC05 core

- Pin compatible with the MC6805R3

- Power saving STOP, WAIT, and SLOW modes

- 3840 bytes of user ROM with security feature in MC68HC05SR3 3840 bytes of EPROM with security bit in MC68HC705SR3

- 192 bytes of RAM (64 bytes for stack)

- 32 bidirectional I/O lines

- Keyboard interrupts

- 8-bit count-down timer with programmable 7-bit prescaler

- On-chip crystal oscillator, with built-in capacitor for RC option

- Second software programmable external interrupt line (IRQ2)

- Direct LED drive capability on all ports

- Programmable 20KΩ pull-up resistors integrated into I/O ports

#### **GENERAL DESCRIPTION**

#### 2.3 Pin Assignments

Figure 2-4 Pin Assignment for 40-pin PDIP

Figure 2-5 Pin Assignment for 42-pin SDIP

Figure 2-6 Pin Assignment for 44-pin QFP

#### PCP — Port C Pull-up

- 1 (set) The internal 20K $\Omega$  pull-up resistors are connected to the inputs of Port C.

- 0 (clear) No pull-up resistor is connected to the inputs of Port C.

#### PBP — PB2:PB7 Pull-up

- 1 (set) The internal  $20K\Omega$  pull-up resistors are connected to the inputs of PB2-PB7.

- 0 (clear) No pull-up resistor is connected to the inputs of PB2-PB7.

#### PB1 — PB1 pull-up

- 1 (set) The internal  $20K\Omega$  pull-up resistor is connected to the input of PB1.

- 0 (clear) No pull-up resistor is connected to the input of PB1.

#### PB0 — PB0 pull-up

- 1 (set) The internal  $20K\Omega$  pull-up resistor is connected to the input of PB0.

- 0 (clear) No pull-up resistor is connected to the input of PB0.

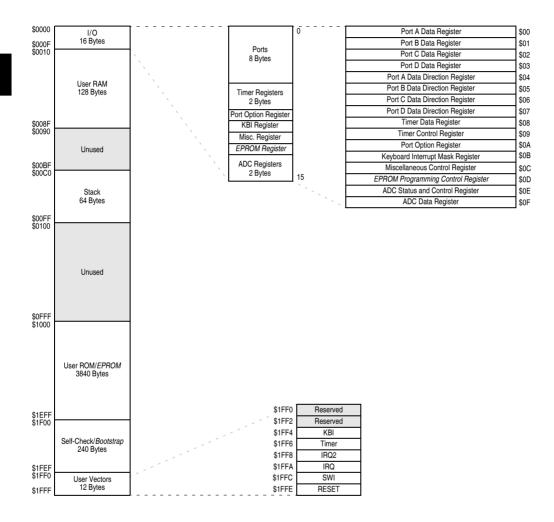

#### 4.4 Memory Map

1

Figure 4-1 shows the memory map for MC68HC05SR3/MC68HC705SR3 device.

Figure 4-1 MC68HC05SR3/MC68HC705SR3 Memory Map

MC68HC05SR3

### 7.1 ADC Operation

As shown in Figure 7-1, the ADC consists of an analog multiplexer, an 8-bit digital to analog capacitor array, a comparator and a successive approximation register (SAR).

There are eight options that can be selected by the multiplexer; the AN0 to AN3 input pins,  $V_{RH}$ ,  $V_{RL}$ ,  $(V_{RH}+V_{RL})/4$ , or  $(V_{RH}+V_{RL})/2$ . Selection is done via the CHx bits in the ADC Status and Control Register. AN0 to AN3 are input points for ADC conversion operations; the others are reference points which can be used for test purposes. The converter uses  $V_{RH}$  and  $V_{RL}$  as reference voltages. An input voltage equal to or greater than  $V_{RH}$  converts to \$FF. An input voltage equal to or less than  $V_{RL}$ , but greater than  $V_{SS}$ , converts to \$00. Maximum and minimum ratings must not be exceeded. Each analog input source should use  $V_{RH}$  as the supply voltage and should be referenced to  $V_{RL}$  for the ratiometric conversions. To maintain full accuracy of the ADC, the following should be noted:

- 1)  $V_{RH}$  should be equal to or less than  $V_{CC}$ ;

- V<sub>RL</sub> should be equal to or greater than V<sub>SS</sub> but less than maximum specifications; and

- 3)  $V_{RH}$  +  $V_{RL}$  should be equal to or greater than 4 Volts.

The ADC reference inputs ( $V_{RH}$  and  $V_{RL}$ ) are applied to a precision internal digital to analog converter. Control logic drives this D/A converter and the analog output is successively compared with the selected analog input sampled at the beginning of the conversion. The conversion is monotonic with no missing codes.

The result of each successive comparison is stored in the successive approximation register (SAR) and, when the conversion is complete, the contents of the SAR are transferred to the read-only ADC Data Register (\$0F), and the conversion complete flag, COCO, is set in the ADC Status and Control Register (\$0E).

Warning: Any write to the ADC Status and Control Register will abort the current conversion, reset the conversion complete flag (COCO) and a new conversion starts on the selected channel.

At power-on or external reset, both the ADRC and ADON bits are cleared, thus the ADC is disabled.

#### Table 8-1 MUL instruction

| Operation          | $X:A \leftarrow X^*A$                                                                                                                                                       |                |  |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|--|--|--|

| Description        | Multiplies the eight bits in the index register by the eight<br>bits in the accumulator and places the 16-bit result in the<br>concatenated accumulator and index register. |                |  |  |  |  |  |  |  |

| Condition<br>codes | H : Cleared<br>I : Not affected<br>N : Not affected<br>Z : Not affected<br>C : Cleared                                                                                      |                |  |  |  |  |  |  |  |

| Source             |                                                                                                                                                                             | MUL            |  |  |  |  |  |  |  |

| Form               | Addressing mode<br>Inherent                                                                                                                                                 | Opcode<br>\$42 |  |  |  |  |  |  |  |

#### Table 8-2 Register/memory instructions

|                                          |          | Addressing modes |                  |          |        |          |          |        |                           |          |        |                              |          |                               |         |          |        |         |          |

|------------------------------------------|----------|------------------|------------------|----------|--------|----------|----------|--------|---------------------------|----------|--------|------------------------------|----------|-------------------------------|---------|----------|--------|---------|----------|

|                                          |          |                  | Immediate Direct |          |        | Extended |          |        | Indexed<br>(no<br>offset) |          |        | Indexed<br>(8-bit<br>offset) |          | Indexed<br>(16-bit<br>offset) |         | t        |        |         |          |

| Function                                 | Mnemonic | Opcode           | # Bytes          | # Cycles | Opcode | # Bytes  | # Cycles | Opcode | # Bytes                   | # Cycles | Opcode | # Bytes                      | # Cycles | Opcode                        | # Bytes | # Cycles | Opcode | # Bytes | # Cycles |

| Load A from memory                       | LDA      | A6               | 2                | 2        | B6     | 2        | 3        | C6     | 3                         | 4        | F6     | 1                            | 3        | E6                            | 2       | 4        | D6     | 3       | 5        |

| Load X from memory                       | LDX      | AE               | 2                | 2        | BE     | 2        | 3        | CE     | 3                         | 4        | FE     | 1                            | 3        | EE                            | 2       | 4        | DE     | 3       | 5        |

| Store A in memory                        | STA      |                  |                  |          | B7     | 2        | 4        | C7     | 3                         | 5        | F7     | 1                            | 4        | E7                            | 2       | 5        | D7     | 3       | 6        |

| Store X in memory                        | STX      |                  |                  |          | BF     | 2        | 4        | CF     | 3                         | 5        | FF     | 1                            | 4        | EF                            | 2       | 5        | DF     | 3       | 6        |

| Add memory to A                          | ADD      | AB               | 2                | 2        | BB     | 2        | 3        | CB     | 3                         | 4        | FB     | 1                            | 3        | EB                            | 2       | 4        | DB     | 3       | 5        |

| Add memory and carry to A                | ADC      | A9               | 2                | 2        | B9     | 2        | 3        | C9     | 3                         | 4        | F9     | 1                            | 3        | E9                            | 2       | 4        | D9     | 3       | 5        |

| Subtract memory                          | SUB      | A0               | 2                | 2        | B0     | 2        | 3        | C0     | 3                         | 4        | F0     | 1                            | 3        | E0                            | 2       | 4        | D0     | 3       | 5        |

| Subtract memory from A with borrow       | SBC      | A2               | 2                | 2        | B2     | 2        | 3        | C2     | 3                         | 4        | F2     | 1                            | 3        | E2                            | 2       | 4        | D2     | 3       | 5        |

| AND memory with A                        | AND      | A4               | 2                | 2        | B4     | 2        | 3        | C4     | 3                         | 4        | F4     | 1                            | 3        | E4                            | 2       | 4        | D4     | 3       | 5        |

| OR memory with A                         | ORA      | AA               | 2                | 2        | BA     | 2        | 3        | CA     | 3                         | 4        | FA     | 1                            | 3        | EA                            | 2       | 4        | DA     | 3       | 5        |

| Exclusive OR memory with A               | EOR      | A8               | 2                | 2        | B8     | 2        | 3        | C8     | 3                         | 4        | F8     | 1                            | 3        | E8                            | 2       | 4        | D8     | 3       | 5        |

| Arithmetic compare A with memory         | CMP      | A1               | 2                | 2        | B1     | 2        | 3        | C1     | 3                         | 4        | F1     | 1                            | 3        | E1                            | 2       | 4        | D1     | 3       | 5        |

| Arithmetic compare X<br>with memory      | CPX      | A3               | 2                | 2        | B3     | 2        | 3        | C3     | 3                         | 4        | F3     | 1                            | 3        | E3                            | 2       | 4        | D3     | 3       | 5        |

| Bit test memory with A (logical compare) | BIT      | A5               | 2                | 2        | B5     | 2        | 3        | C5     | 3                         | 4        | F5     | 1                            | 3        | E5                            | 2       | 4        | D5     | 3       | 5        |

| Jump unconditional                       | JMP      |                  |                  |          | BC     | 2        | 2        | CC     | 3                         | 3        | FC     | 1                            | 2        | EC                            | 2       | 3        | DC     | 3       | 4        |

| Jump to subroutine                       | JSR      |                  |                  |          | BD     | 2        | 5        | CD     | 3                         | 6        | FD     | 1                            | 5        | ED                            | 2       | 6        | DD     | 3       | 7        |

#### 8.3.4 Extended

In the extended addressing mode, the effective address of the argument is contained in the two bytes following the opcode byte. Instructions with extended addressing mode are capable of referencing arguments anywhere in memory with a single three-byte instruction. When using the Freescale assembler, the user need not specify whether an instruction uses direct or extended addressing. The assembler automatically selects the short form of the instruction.

> $EA = (PC+1):(PC+2); PC \leftarrow PC+3$ Address bus high  $\leftarrow$  (PC+1); Address bus low  $\leftarrow$  (PC+2)

#### 8.3.5 Indexed, no offset

In the indexed, no offset addressing mode, the effective address of the argument is contained in the 8-bit index register. This addressing mode can access the first 256 memory locations. These instructions are only one byte long. This mode is often used to move a pointer through a table or to hold the address of a frequently referenced RAM or I/O location.

$$\label{eq:EA} \begin{split} \mathsf{EA} &= \mathsf{X}; \ \mathsf{PC} \leftarrow \mathsf{PC}{+1} \\ \mathsf{Address \ bus \ high} \leftarrow 0; \ \mathsf{Address \ bus \ low} \leftarrow \mathsf{X} \end{split}$$

#### 8.3.6 Indexed, 8-bit offset

In the indexed, 8-bit offset addressing mode, the effective address is the sum of the contents of the unsigned 8-bit index register and the unsigned byte following the opcode. Therefore the operand can be located anywhere within the lowest 511 memory locations. This addressing mode is useful for selecting the mth element in an n element table.

$EA = X+(PC+1); PC \leftarrow PC+2$ Address bus high  $\leftarrow K;$  Address bus low  $\leftarrow X+(PC+1)$ where K = the carry from the addition of X and (PC+1)

#### 8.3.7 Indexed, 16-bit offset

In the indexed, 16-bit offset addressing mode, the effective address is the sum of the contents of the unsigned 8-bit index register and the two unsigned bytes following the opcode. This address mode can be used in a manner similar to indexed, 8-bit offset except that this three-byte instruction allows tables to be anywhere in memory. As with direct and extended addressing, the Freescale assembler determines the shortest form of indexed addressing.

$$\label{eq:expectation} \begin{split} &\mathsf{EA} = \mathsf{X} + [(\mathsf{PC}+1):(\mathsf{PC}+2)]; \,\mathsf{PC} \leftarrow \mathsf{PC}+3 \\ &\mathsf{Address\ bus\ high} \leftarrow (\mathsf{PC}+1) + \mathsf{K}; \,\mathsf{Address\ bus\ low} \leftarrow \mathsf{X} + (\mathsf{PC}+2) \\ & \mathsf{where}\ \mathsf{K} = \mathsf{the\ carry\ from\ the\ addition\ of\ X\ and\ (\mathsf{PC}+2)} \end{split}$$

**CPU CORE AND INSTRUCTION SET**

# 8

### THIS PAGE LEFT BLANK INTENTIONALLY

#### 9.3 SLOW Mode

The SLOW mode function is controlled by the SM bit in the Miscellaneous Control Register. When the SM bit is set, the internal bus clock is divided by 16, resulting to a frequency equal to the oscillator frequency divide by 32. This feature permits a slow down of all the internal operations and thus reduces power consumption — particularly useful while in WAIT mode. The SM bit is automatically cleared while going to STOP mode.

|                                | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |  |

|--------------------------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|--|

| Miscellaneous Control Register | \$0C    | KBIE  | KBIC  | INTO  | INTE  | LVRE  | SM    | IRQ2F | IRQ2E | 0001 0000         |  |

#### SM — Slow Mode

- 1 (set) Slow mode enabled. Internal bus frequency  $f_{OP} = f_{OSC} \div 32$ .

- 0 (clear) Slow mode disabled. Internal bus frequency f<sub>OP</sub>=f<sub>OSC</sub> ÷ 2.

#### 9.4 Data-Retention Mode

If the Low Voltage Reset function is not enabled, the contents of RAM and CPU registers are retained at supply voltages as low as 2Vdc. This is called the data-retention mode where the data is held, but the device is not guaranteed to operate. The RESET pin must be held low during data-retention mode.

The Low Voltage Reset Function is enabled/disabled by the LVRE bit in the Miscellaneous Control Register (\$0C).

|                                | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |

|--------------------------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|

| Miscellaneous Control Register | \$0C    | KBIE  | KBIC  | INTO  | INTE  | LVRE  | SM    | IRQ2F | IRQ2E | 0001 0000         |

#### LVRE — Low Voltage Reset Enable

1 (set) - Low Voltage Reset function enabled.

0 (clear) - Low Voltage Reset function disabled.

| D4      | D3       | D2   | D1 | REMARKS                       |

|---------|----------|------|----|-------------------------------|

|         | Flas     | hing |    | O.K. (self-check is on-going) |

| 1       | 1        | 1    | 1  | Bad port A                    |

| 1       | 1        | 1    | 0  | Bad port B                    |

| 1       | 1        | 0    | 1  | Bad port C                    |

| 1       | 1        | 0    | 0  | Bad port D                    |

| 1       | 0        | 1    | 1  | Bad RAM                       |

| 1       | 0        | 1    | 0  | Bad ROM                       |

| 1       | 0        | 0    | 0  | Bad SWI                       |

| 0       | 1        | 1    | 1  | Bad IRQ                       |

| 1=LED o | n, 0=LED | off  |    |                               |

#### Table 10-2 Self-Check Report

10.3 Bootstrap Mode

The Bootstrap mode is provided in the EPROM part (MC68HC705SR3) as a mean of self-programming its EPROM with minimal circuitry. Bootstrap mode will be entered on the rising edge of  $\overrightarrow{RESET}$  when the V<sub>PP</sub> pin is at V<sub>TST</sub> (2×V<sub>DD</sub>) and PB1 pin is at V<sub>DD</sub>. Once in the bootstrap mode, PB1 can then be used for other purposes. After entering the bootstrap mode, CPU branches to the bootstrap program and carries out the EPROM programming routine. The user EPROM consists of 3840 bytes, from location \$1000 to \$1EFF.

Refer to Appendix A for further details on MC68HC705SR3.

10

THIS PAGE LEFT BLANK INTENTIONALLY

10

- BE WITHIN 0.25 mm (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- 3. DIMENSION B DOES NOT INCLUDE MOLD FLASH. .....

|    |   | MILLIM | ETERS | INCHES    |       |  |  |  |

|----|---|--------|-------|-----------|-------|--|--|--|

| DI | М | MIN    | MAX   | MIN       | MAX   |  |  |  |

| A  |   | 51.69  | 52.45 | 2.035     | 2.065 |  |  |  |

| B  |   | 13.72  | 14.22 | 0.540     | 0.560 |  |  |  |

| C  |   | 3.94   | 5.08  | 0.155     | 0.200 |  |  |  |

| D  | 1 | 0.36   | 0.56  | 0.014     | 0.022 |  |  |  |

| F  |   | 1.02   | 1.52  | 0.040     | 0.060 |  |  |  |

| G  |   | 2.54   | BSC   | 0.100 BSC |       |  |  |  |

| H  |   | 1.65   | 2.16  | 0.065     | 0.085 |  |  |  |

| J  |   | 0.20   | 0.38  | 0.008     | 0.015 |  |  |  |

| K  |   | 2.92   | 3.43  | 0.115     | 0.135 |  |  |  |

| L  |   | 15.24  | BSC   | 0.600     | BSC   |  |  |  |

| N  | 1 | 0°     | 15°   | 0°        | 15°   |  |  |  |

| N  |   | 0.51   | 1.02  | 0.020     | 0.040 |  |  |  |

Figure 12-1 40-pin DIP Package

#### 12.2 42-Pin SDIP Package (Case 858-01)

Figure 12-2 42-pin SDIP Package

Figure 12-3 44-pin QFP Package

| CLR  | PCR      | ;reset PCR                     |  |  |  |  |  |  |

|------|----------|--------------------------------|--|--|--|--|--|--|

| LDX  | #\$00    | ;load index register with 00   |  |  |  |  |  |  |

| BSET | 1,PCR    | ;set ELAT bit                  |  |  |  |  |  |  |

| LDA  | #\$00    | ;load data=00 in to A          |  |  |  |  |  |  |

| STA  | \$1900,X | ;latch data and address        |  |  |  |  |  |  |

| BSET | 0,PCR    | ;program                       |  |  |  |  |  |  |

| JSR  | DELAY    | ;call delay subroutine for 1ms |  |  |  |  |  |  |

| CLR  | PCR      | ;reset PCR                     |  |  |  |  |  |  |

#### A.5 Mask Option Register (MOR)

The Mask Option Register (MOR) contains programmable EPROM bits to control mask options, and cannot be changed in User mode. The erased state are zeros. This register is latched upon reset going away.

|                            | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |

|----------------------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|

| Mask Option Register (MOR) | \$0FFF  |       |       | SMD   | SEC   | TMR2  | TMR1  | TMR0  | RC    | unaffected        |

#### SMD — SLOW Mode at Power-on

When programmed to "1", this bit enables SLOW mode at power-up. Operating frequency,  $f_{OP}=f_{OSC}\div 2\div 16=f_{OSC}\div 32$ .

#### SEC — EPROM Security

When programmed to "1", this bit disables some functions of the Bootstrap mode, preventing external reading of EPROM content.

#### TMR2:TMR0 — Power-on Reset Delay

The amount Power-On Reset delay is set by programming these three bits. The delay is selected as follows:

| TMR2 | TMR1 | TMR0 | Delay (Instruction Cycles) |

|------|------|------|----------------------------|

| 0    | 0    | 0    | 256                        |

| 0    | 0    | 1    | 512                        |

| 0    | 1    | 0    | 1024                       |

| 0    | 1    | 1    | 2048                       |

| 1    | 0    | 0    | 4096                       |

| 1    | 0    | 1    | 8192                       |

| 1    | 1    | 0    | 16384                      |

| 1    | 1    | 1    | 32768                      |

THIS PAGE LEFT BLANK INTENTIONALLY

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Rev. 2.1 MC68HC05SR3D/H 08/2005 RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The ARM POWERED logo is a registered trademark of ARM Limited. ARM7TDMI-S is a trademark of ARM Limited. Java and all other Java-based marks are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries. The Bluetooth trademarks are owned by their proprietor and used by Freescale Semiconductor, Inc. under license.

© Freescale Semiconductor, Inc. 2005. All rights reserved.