#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFL

| Becano                     |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Active                                                                              |

| Core Processor             | ARM® Cortex®-M3                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 48MHz                                                                               |

| Connectivity               | I <sup>2</sup> C, SIO, UART/USART                                                   |

| Peripherals                | DMA, PWM, WDT                                                                       |

| Number of I/O              | 74                                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 64K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x12b                                                                          |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

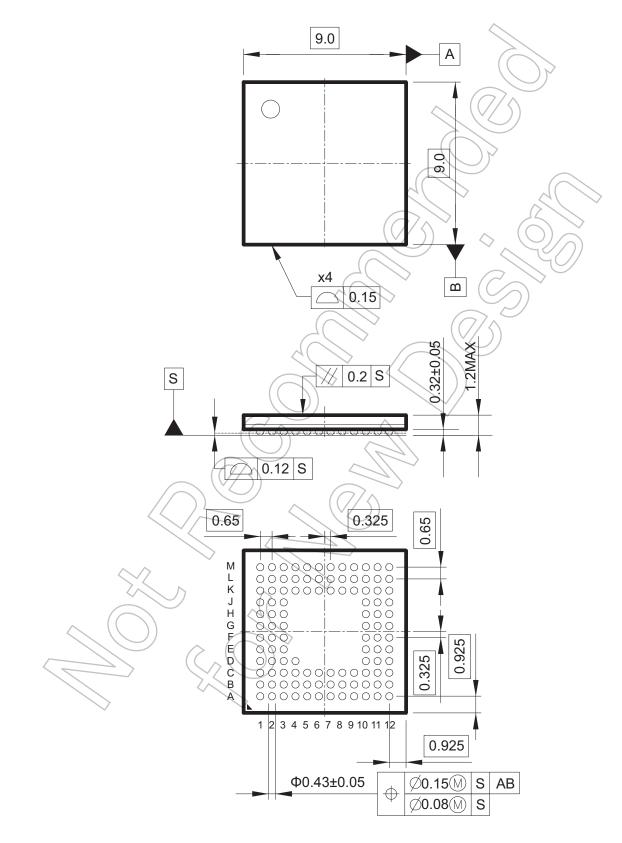

| Package / Case             | 109-TFBGA                                                                           |

| Supplier Device Package    | 109-TFBGA (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/toshiba-semiconductor-and-storage/tmpm366fdxbg |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

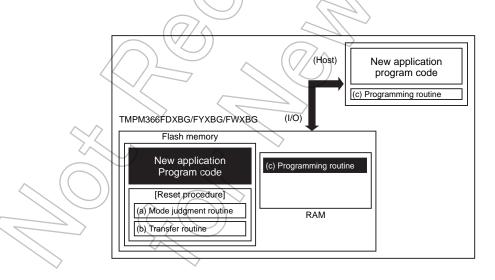

# TMPM366FDXBG/FYXBG/FWXBG

The TMPM366FDXBG/FYXBG/FWXBG is a 32-bit RISC microprocessor series with an ARM Cortex<sup>™</sup>-M3 microprocessor core.

| Product Name | ROM<br>(FLASH) | RAM      | Package                  |

|--------------|----------------|----------|--------------------------|

| TMPM366FDXBG | 512 Kbyte      | 64 Kbyte |                          |

| TMPM366FYXBG | 256 Kbyte      | 48 Kbyte | P-TFBGA109-0909-0.65-002 |

| TMPM366FWXBG | 128 Kbyte      | 32 Kbyte |                          |

Features of the TMPM366FDXBG/FYXBG/FWXBG are as follows:

### 1.1 Features

- 1. ARM Cortex-M3 microprocessor core

- a. Improved code efficiency has been realized through the use of Thumb® -2 instruction.

- · New 16-bit Thumb instructions for improved program flow

- · New 32-bit Thumb instructions for improved performance

- New Thumb mixed 16-/32-bit instruction set can produce faster, more efficient code.

- b. Both high performance and low power consumption have been achieved.

[High performance]

- A 32-bit multiplication  $(32 \times 32 = 32 \text{ bit})$  can be executed with one clock.

- · Division takes between 2 and 12 cycles depending on dividend and devisor

[Low power consumption]

- · Optimized design using a low power consumption library

- Standby function that stops the operation of the micro controller core

- High-speed interrupt response suitable for real-time control

• An interruptible long instruction.

Stack push automatically handled by hardware.

On chip program memory and data memory

- On chip SRAM : 64 Kbyte / 48 Kbyte / 32 Kbyte

- On chip Flash ROM : 512 Kbyte / 256 Kbyte / 128 Kbyte

- 3. External bus interface (EBIF)

- Up to 16Mbytes access area (Program / Data)

- External data bus (Separate / Multiplex): 8 /16bit bus width

- · Chip select / Wait controller: 2 channels

- 4. DMA controller (DMAC) : 2 units 4 channels

The example of warm-up function setup.

Table 8-1 <example> from STOP mode to NORMAL mode transition (internal high-speed oscillator is selected)

| CGOSCCR <wuodr[11:0]> = "0x9C4"</wuodr[11:0]> | : Specify the warm-up time                                                  |

|-----------------------------------------------|-----------------------------------------------------------------------------|

| CGOSCCR <wuodr[11:0]> read</wuodr[11:0]>      | : Confirm warm-up time reflecting<br>Repaet until the read data is "0x9C4". |

| CGOSCCR <xen2> = "1"</xen2>                   | : Internal high-speed oscillator (fosc) enable                              |

| CGOSCCR <wueon> = "1"</wueon>                 | : Start the warm-up timer (WUP)                                             |

| CGOSCCR <wuef> read</wuef>                    | : Wait until the state becomes "0" (warm-up is finished)                    |

- Note 1: It is not required the warm-up time in using the external clock to be stabled.

- Note 2: The warm-up timer operates according to the oscillation clock, and it may contain errors if there is any fluctuation in the oscillation frequency. Therefore, the warm-up time should be taken as approximate time.

- Note 3: After setting warm-up count value to OSCCR<WUDOR>, wait until confirming of the value to be reflected, then change to the standby mode by WFI instruction.

- Note 4: When returning from STOP1/STOP2 mode, related bits CGPLLSEL<PLLSEL<, CGOSCCR<HWUPSEL>, <OS-CSEL>, <XEN2>, <XEN1> and <PLLON> are initialized in order to start internal high-speed oscillator and CGOSCCR<WUDOR[11:0]> is not initialized.

|             | 31  | 30  | 29  | 28  | 27  | 26                              | 25       | 24  |

|-------------|-----|-----|-----|-----|-----|---------------------------------|----------|-----|

| bit symbol  | -   | -   | -   | -   | -   | - >                             |          | -   |

| After reset | 0   | 0   | 0   | 0   | 0   | 0 ((                            | ø        | 0   |

|             | 23  | 22  | 21  | 20  | 19  | 18                              | 17       | 16  |

| bit symbol  | -   | -   | -   | -   | -   | $(\overline{\alpha})$           | <u> </u> | -   |

| After reset | 0   | 0   | 0   | 0   | 0   | 0                               | ) 0      | 0   |

|             | 15  | 14  | 13  | 12  | 11  | 10                              | 9        | 8   |

| bit symbol  | -   | -   | -   | -   | -   | $\left( \left( \right) \right)$ | -        | -   |

| After reset | 0   | 0   | 0   | 0   | 0   |                                 | 0        | 0   |

|             | 7   | 6   | 5   | 4   | 3   | 2                               |          | 0   |

| bit symbol  | PF7 | PF6 | PF5 | PF4 | PE3 | PF2                             | PF1      | PF0 |

| After reset | 0   | 0   | 0   | 0   |     | 0                               | 0        | 0   |

#### 10.2.6.2 PFDATA (Port F data register)

| Bit  | Bit Symbol | Туре |                      | Function |   |

|------|------------|------|----------------------|----------|---|

| 31-8 | -          | R    | Read as "0".         |          | ( |

| 7-0  | PF7-PF0    | R/W  | Port F data register |          |   |

10.2.6.3 PFCR (Port F output control register)

|             |                |              |      |      |                  | $\sim$ |      |      |

|-------------|----------------|--------------|------|------|------------------|--------|------|------|

|             | 31             | 30           | 29   | 28   | 27               | 26     | 25   | 24   |

| bit symbol  | -              | -            |      | - <  | $\sum_{i=1}^{n}$ | -      | -    | -    |

| After reset | 0              | 0            | 0    | 0    | 0                | 0      | 0    | 0    |

|             | 23             | 22           | ))21 | 20   | 19               | 18     | 17   | 16   |

| bit symbol  | - /            |              |      |      | -                | -      | -    | -    |

| After reset | 0              | 0            | 7 0  | 0    | 0                | 0      | 0    | 0    |

|             | 15             | 14           | 13   | 12   | 11               | 10     | 9    | 8    |

| bit symbol  | -              | <u> </u>     | -    |      | -                | -      | -    | -    |

| After reset | 0              | 0            | 0    | 0    | 0                | 0      | 0    | 0    |

|             | 7~             | 5 6          | 5    | 4    | 3                | 2      | 1    | 0    |

| bit symbol  | PF7C           | PF6C         | PF5C | PF4C | PF3C             | PF2C   | PF1C | PF0C |

| After reset | (0)            | 0            | 0    | 0    | 0                | 0      | 0    | 0    |

|             | $\overline{)}$ | $\Diamond$ ( |      |      |                  |        |      |      |

| Bit  | Bit Symbol | Туре | Function     |

|------|------------|------|--------------|

| 31-8 | -          | R    | Read as "0". |

| 7-0  | PF7C-PF0C  | R/W  | Output       |

|      |            |      | 0: Disable   |

|      |            |      | 1: Enable    |

|             | 31    | 30    | 29    | 28    | 27    | 26                              | 25       | 24    |

|-------------|-------|-------|-------|-------|-------|---------------------------------|----------|-------|

| bit symbol  | -     | -     | -     | -     | -     | -                               | -        | -     |

| After reset | 0     | 0     | 0     | 0     | 0     | 0 (                             | Ø        | 0     |

|             | 23    | 22    | 21    | 20    | 19    | 18                              | 17       | 16    |

| bit symbol  | -     | -     | -     | -     | -     | $(-\alpha)$                     | <u> </u> | -     |

| After reset | 0     | 0     | 0     | 0     | o <   | 0                               | ) 0      | 0     |

|             | 15    | 14    | 13    | 12    | 11    | 10                              | 9        | 8     |

| bit symbol  | -     | -     | -     | -     | -     | $\left( \left( \right) \right)$ | -        | -     |

| After reset | 0     | 0     | 0     | 0     | 0     |                                 | 0        | 0     |

|             | 7     | 6     | 5     | 4     | 3     | 2                               |          | 0     |

| bit symbol  | PI7F1 | PI6F1 | PI5F1 | PI4F1 | PI3F1 | PI2F1                           | PI1F1    | PI0F1 |

| After reset | 1     | 1     | 1     | 1     | (7/   | 0                               |          | 0     |

|             |       |       |       | G     |       |                                 | (LA)     |       |

#### 10.2.9.4 PIFR1(Port I function register 1)

| Bit  | Bit Symbol | Туре | Function                 |

|------|------------|------|--------------------------|

| 31-8 | -          | R    | Read as "0".             |

| 7    | PI7F1      | R/W  | 0: PORT<br>1: TRST       |

| 6    | PI6F1      | R/W  | 0: PORT<br>1: TDI        |

| 5    | PI5F1      | R/W  | 0: PORT<br>1: TDO/SWV    |

| 4    | PI4F1      | R/W  | 0: PORT<br>1: TMS/SWDJO  |

| 3    | PI3F1      | R/W  | 0: PORT<br>1: TCK/SWCLK  |

| 2    | PI2F1      | R/W  | 0: PORT<br>1: TRACECLK   |

| 1    | PI1F1      | R/W  | 0: PORT<br>1: TRAGEDATA0 |

| 0    | PI0F1      | R/W  | 0: PORT<br>1: TRACEDATA1 |

### 10.4.7 Port G Setting

#### Table 10-12 Port Setting List (Port G)

| Pin      | Port<br>Type | Function            | After<br>reset | PGCR                              | PGFR1 | PGFR2    | PGFR3 | PGFR4      | PGFR5             | PGOD                          | PGPUP   | PGIE |

|----------|--------------|---------------------|----------------|-----------------------------------|-------|----------|-------|------------|-------------------|-------------------------------|---------|------|

|          | туре         | Input Port          | 10301          | 0                                 | 0     | 0        | 0     | 0          | _0                | $\overrightarrow{\mathbf{x}}$ | x       | 1    |

|          | FT1          | Output Port         |                | 1                                 | 0     | 0        | 0     | 0          |                   | ×                             | x       | 0    |

|          |              | SDA0 (Input/Output) |                | 1                                 | 1     | 0        | 0     | 0          | $\langle \rangle$ | 1                             | x       | 1    |

| PG0      | FT1          | SO0 (Output)        |                | 1                                 | 1     | 0        | 0     | 0          | 0                 | x                             | x       | 0    |

| FGU      | FT9          | A3 (Output)         |                | 1                                 | 0     | 1        | 0     |            |                   | x                             | x       | 0    |

|          | 115          | TX02 (Output)       |                | 1                                 | 0     | 0        | 0     |            | 0                 |                               |         | 0    |

|          | FT1          | IROUT (Output)      |                | 1                                 | 0     | 0        | 0     | 1          | 1                 | ×                             | X       | 0    |

|          |              | ,                   |                |                                   |       |          |       |            |                   | ×                             | ×       |      |

|          | FT1          | Input Port          |                | 0                                 | 0     | 0        |       | >0         | 0                 | ×                             | ×       | 1    |

|          |              | Output Port         |                | 1                                 | 0     | 0        | /0)   | 0          | 0                 | $\langle \mathbf{x} \rangle$  | $\beta$ | 0    |

|          | FT1          | SCL0 (Input/Output) |                | 1                                 | 1     | 0        | 0     | 0          | 0                 | 19                            | ×       | 1    |

| PG1      |              | SI0 (Input)         |                | 0                                 | 1     | 0        | >0    | 0          | 0                 | ×                             | x       | 1    |

| -        | FT9          | A4 (Output)         |                | 1                                 | 0     |          | 0     | 0          | Ø                 | )) x                          | x       | 0    |

|          |              | TB3IN0 (Input)      |                | 0                                 | 0     | 0        | 1     | -0         |                   | x                             | x       | 1    |

|          | FT1          | RX02 (Input)        |                | 0                                 | - 0   | >0       | 0     | 4          | 0)                | х                             | x       | 1    |

|          |              | IRIN (Input)        |                | 0                                 | 0     | 0        | 0     | 0          | _1                | x                             | x       | 1    |

|          | FT1          | Input Port          |                | 0                                 | B     | 0 <      | 0     | 0          | 0                 | х                             | x       | 1    |

|          |              | Output Port         |                | $\left( \left( 1 \right) \right)$ | 0     | 0        | 0     | 0          | 0                 | х                             | x       | 0    |

|          | FT1          | SCK0 (Input)        |                | 0                                 | / 1   | 0        | 0     | <u>\</u> 0 | 0                 | х                             | x       | 1    |

| PG2      |              | SCK0 (Output)       |                | $\langle \gamma \rangle$          | 1     | 0        | 0     | 0          | 0                 | х                             | x       | 0    |

|          | FT9          | A5 (Output)         | $\sim$         | 7                                 | 0     | 1        | 0     | 0          | 0                 | х                             | x       | 0    |

|          | FT1          | TB3IN1 (Input)      | $7/\Lambda$    | 0                                 | 0     | 0        | 1     | 0          | 0                 | х                             | x       | 1    |

|          |              | CTS2 (Input)        | $\bigcirc$     | 0                                 | 0     | 0        | ~ 0   | 1          | 0                 | x                             | x       | 1    |

|          | FT1          | Input Port          | ~              | 0                                 | 0     | <b>)</b> | 0     | 0          | 0                 | х                             | x       | 1    |

|          | FII          | Output Port         |                | 1                                 | ø     | 0        | 0     | 0          | 0                 | х                             | x       | 0    |

| DOD      | FT4          | INT0 (Input)        | 4              | 6                                 | H     | 0        | 0     | 0          | 0                 | х                             | x       | 1    |

| PG3      | FT9          | A6 (Output)         |                | 1                                 | 0     | 1        | 0     | 0          | 0                 | х                             | x       | 0    |

| Í        | FT1          | TB4IN0 (Input)      | ~              | 0                                 | 0     | 0        | 1     | 0          | 0                 | х                             | x       | 1    |

| Í        | FT1          | RIN2 (Input)        |                | 0                                 | 0     | 0        | 0     | 1          | 0                 | х                             | x       | 1    |

| $\frown$ |              | Input Port          |                | 0                                 | 0     | 0        | 0     | 0          | 0                 | х                             | x       | 1    |

|          | Ft1          | Output Port         | $\bigcirc$     | Y                                 | 0     | 0        | 0     | 0          | 0                 | х                             | x       | 0    |

| PG4      | FT9          | A7 (Output)         | $\bigcirc$     | ) 0                               | 0     | 1        | 0     | 0          | 0                 | х                             | x       | 0    |

|          |              | TB4IN1 (Input)      | $\overline{}$  | 0                                 | 0     | 0        | 1     | 0          | 0                 | x                             | x       | 1    |

|          | FT1          | RTS2 (Input)        | $\searrow$     | 1                                 | 0     | 0        | 0     | 1          | 0                 | x                             | x       | 0    |

|          | ~            | Input Port          |                | 0                                 | 0     | 0        | 0     | 0          | 0                 | х                             | х       | 1    |

|          | FT1          | Output Port         |                | 1                                 | 0     | 0        | 0     | 0          | 0                 | x                             | x       | 0    |

| PG5      | FT4          | INT1 (Input)        |                | 0                                 | 1     | 0        | 0     | 0          | 0                 | x                             | x       | 1    |

|          | FT4          | USBPON (Input)      |                | 0                                 | 0     | 0        | 0     | 1          | 0                 | x                             | x       | 1    |

|             | 31 | 30 | 29 | 28  | 27 | 26      | 25   | 24   |

|-------------|----|----|----|-----|----|---------|------|------|

| bit symbol  | C  | SR |    | WRR |    | RDR     |      |      |

| After reset | 0  | 1  | 0  | 0   | 1  | 0 ((    | 0    | 1    |

|             | 23 | 22 | 21 | 20  | 19 | 18      | 17   | 16   |

| bit symbol  | -  | -  | AL | EW  | w  | rs (7/4 | RI   | DS   |

| After reset | 0  | 0  | 0  | 1   | 0  |         | 0    | 1    |

|             | 15 | 14 | 13 | 12  | 11 | 10      | 9    | 8    |

| bit symbol  | -  | -  | -  |     |    | CSIW    | -    |      |

| After reset | 0  | 0  | 0  | 0   | 0  | 0       | 1    | 0    |

|             | 7  | 6  | 5  | 4   | 3  | 2       | ( )  | 0    |

| bit symbol  | -  | -  | -  | -   |    | CS      | sw 2 | CSW0 |

| After reset | 0  | 0  | 0  | 0   |    | 0       |      | 0    |

|             |    |    |    | G   |    |         | YO   | )    |

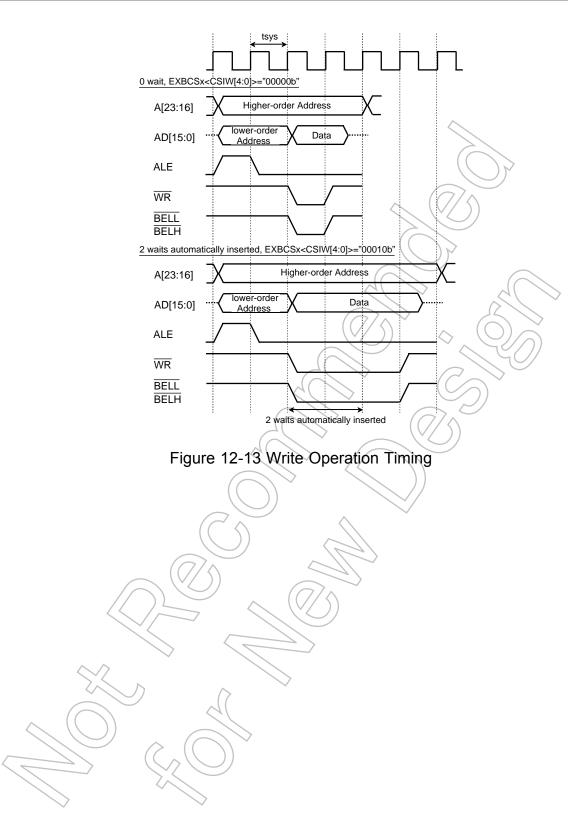

## 12.6.4 EXBCSx (External Bus Chip Select Control Register)

| Bit   | Bit Symbol              | Туре | Function                                                                                                                                                                                                                                                                                               |

|-------|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-30 | CSR[1:0]                | R/W  | Chip select (CSx) Recovery cycle<br>00: None, 01: 1 cycle, 10: 2 cycles, 11: 4 cycles                                                                                                                                                                                                                  |

| 29-27 | WRR[2:0]                | R/W  | Write (WR) Recovery cycle<br>000: None, 001: 1 cycle, 010: 2 cycles, 011: 3 cycles,<br>100: 4 cycles, 101: 5 cycles, 110: 6 cycles, 111: 8 cycles                                                                                                                                                      |

| 26-24 | RDR[2:0]                | R/W  | Read (RD) Recovery cycle<br>000: None, 001: 1 cycle, 010: 2 cycles, 011: 3 cycles,<br>100: 4 cycles, 101: 5 cycles, 110: 6 cycles, 111: 8 cycles                                                                                                                                                       |

| 23-22 | -                       | R    | Read as 0.                                                                                                                                                                                                                                                                                             |

| 21-20 | ALEW[1:0]               | R/W  | ALE wait cycle for multiplex bus<br>000: None, 001: 1 cycle, 010: 2 cycles, 011: 4 cycles                                                                                                                                                                                                              |

| 19-18 | WRS[1:0]                | R/W  | Write (WR) Setup cycle<br>000: None, 001: 1 cycle, 010: 2 cycles, 011: 4 cycles                                                                                                                                                                                                                        |

| 17-16 | RDS[1:0]                | R/W  | Read (RD) Setup cycle<br>000: None, 001: 1 cycle, 010: 2 cycles, 011: 4 cycles                                                                                                                                                                                                                         |

| 15-13 | -                       | R    | Read as 0.                                                                                                                                                                                                                                                                                             |

| 12-8  | CSIW[4:0]               | R/W  | Internal Wait (Automatically insertion)<br>0000: 0 wait, 0001: 1 wait, 0010: 2 waits, 0011: 3 waits,<br>0100: 4 waits, 0101: 5 waits, 0110: 6 waits, 0111: 7 waits,<br>1000: 8 waits, 1001: 9 waits, 1010: 10 waits, 1011: 11 waits,<br>1100: 12 waits, 1101: 13 waits, 1110: 14 waits, 1111: 15 waits |

| 7-4   | $\langle ( ( ) \rangle$ | R    | Read as 0.                                                                                                                                                                                                                                                                                             |

| 3     |                         | R/W  | Always write to "0"                                                                                                                                                                                                                                                                                    |

| 2-1   | CSW[2:1]                | R/W  | Data bus width<br>00: 8-bit, 01: 16-bit, Others: Prohibited                                                                                                                                                                                                                                            |

| 0     | CSWO                    | R/W  | CS Enable<br>0: Disable, 1: Enable                                                                                                                                                                                                                                                                     |

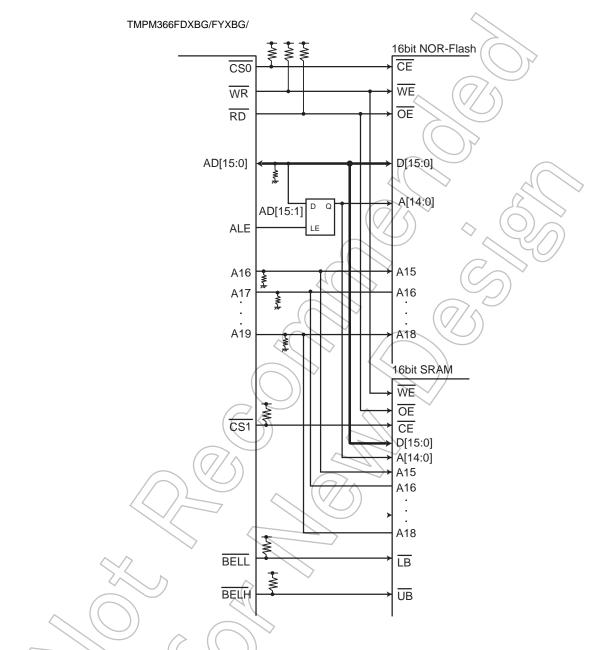

### 12.7.2 Connection Example for external 16-bit SRAM and NOR-Flash (Multiplex bus)

Figure 12-20 Connection Example for external 16-bit SRAM and NOR-Flash (Multiplex bus)

| Select                                         | Clock gear value                   | Select                                                | Prescaler output clock function |                             |                               |  |  |

|------------------------------------------------|------------------------------------|-------------------------------------------------------|---------------------------------|-----------------------------|-------------------------------|--|--|

| peripheral clock<br>CGSYSCR<br><fpsel></fpsel> | CGSYSCR<br><gear[2:0]></gear[2:0]> | prescaler clock<br>CGSYSCR<br><prck[2:0]></prck[2:0]> | φΤ1                             | φΤ4                         | φT16                          |  |  |

|                                                |                                    | 000 (fperiph/1)                                       | fc/21 (0.04 µs)                 | fc/2³ (0.17 µs)             | fc/2⁵ (0.67 µs)               |  |  |

|                                                |                                    | 001 (fperiph/2)                                       | fc/2² (0.08 µs)                 | fc/2⁴ (0.33 µs)             | fc/2 <sup>6</sup> (1.33 μs)   |  |  |

|                                                | 000 (5.)                           | 010 (fperiph/4)                                       | fc/2 <sup>3</sup> (0.17 µs)     | fc/2 <sup>5</sup> (0.67 µs) | fc/2 <sup>7</sup> (2.67 µs)   |  |  |

|                                                | 000 (fc)                           | 011 (fperiph/8)                                       | fc/2⁴ (0.33 µs)                 | fc/2 <sup>6</sup> (1.33 µs) | fc/2 <sup>8</sup> (5.33 µs)   |  |  |

|                                                |                                    | 100 (fperiph/16)                                      | fc/2⁵ (0.67 μs)                 | fc/27 (2.67 µs)             | fc/2 <sup>9</sup> (10.67 μs)  |  |  |

|                                                |                                    | 101 (fperiph/32)                                      | fc/2 <sup>6</sup> (1.33 µs)     | fc/2 <sup>8</sup> (5.33 µs) | fc/2 <sup>10</sup> (21.33 µs) |  |  |

|                                                |                                    | 000 (fperiph/1)                                       | - ((                            | fc/2 <sup>3</sup> (0.17 μs) | fc/2⁵ (0.67 µs)               |  |  |

|                                                |                                    | 001 (fperiph/2)                                       | fc/2² (0.08 µs)                 | fc/2⁴ (0.33 µs)             | fc/2 <sup>6</sup> (1.33 μs)   |  |  |

|                                                | 100 (fa/2)                         | 010 (fperiph/4)                                       | fc/2³ (0.17 µs)                 | fc/2⁵ (0.67 µs)             | fc/2 <sup>7</sup> (2.67 μs)   |  |  |

|                                                | 100 (fc/2)                         | 011 (fperiph/8)                                       | fc/2⁴ (0.33 µs)                 | fc/2 <sup>6</sup> (1.33 µs) | fc/2 <sup>8</sup> (5.33 μs)   |  |  |

|                                                |                                    | 100 (fperiph/16)                                      | fc/2⁵ (0.67 µs)                 | fc/2 <sup>7</sup> (2.67 µs) | fc/2º (10.67 µs)              |  |  |

|                                                |                                    | 101 (fperiph/32)                                      | fc/2 <sup>6</sup> (1.33 µs)     | fc/2 <sup>8</sup> (5.33 µs) | fc/2 <sup>10</sup> (21.33 µs) |  |  |

|                                                | 101 (fc/4)                         | 000 (fperiph/1)                                       |                                 | fc/2 <sup>3</sup> (0.17 µs) | √ fc/2⁵ (0.67 μs)             |  |  |

|                                                |                                    | 001 (fperiph/2)                                       | >-                              | fc/2⁴ (0.33 µs)             | fc/2 <sup>6</sup> (1.33 µs)   |  |  |

| 1 (fp)                                         |                                    | 010 (fperiph/4)                                       | fc/2³ (0.17 μs)                 | fc/2 <sup>5</sup> (0.67 µs) | fc/2 <sup>7</sup> (2.67 µs)   |  |  |

| 1 (fc)                                         |                                    | 011 (fperiph/8)                                       | fc/2⁴ (0.33 µs)                 | fc/2 <sup>6</sup> (1.33 µs) | fc/2 <sup>8</sup> (5.33 µs)   |  |  |

|                                                |                                    | 100 (fperiph/16)                                      | fc/2⁵ (0.67 µs)                 | fc/2 <sup>7</sup> (2.67 μs) | fc/2 <sup>9</sup> (10.67 μs)  |  |  |

|                                                |                                    | 101 (fperiph/32)                                      | fc/2 <sup>6</sup> (1.33 µs)     | fc/2 <sup>8</sup> (5.33 μs) | fc/2 <sup>10</sup> (21.33 µs) |  |  |

|                                                |                                    | 000 (fperiph/1)                                       | -                               |                             | fc/2⁵ (0.67 µs)               |  |  |

|                                                | (                                  | 001 (fperiph/2)                                       | <u> </u>                        | fc/2⁴ (0.33 µs)             | fc/2 <sup>6</sup> (1.33 µs)   |  |  |

|                                                | 110 (5-10)                         | 010 (fperiph/4)                                       | -                               | fc/2⁵ (0.67 µs)             | fc/2 <sup>7</sup> (2.67 µs)   |  |  |

|                                                | 110 (fc/8)                         | 011 (fperiph/8)                                       | fc/2⁴ (0.33 µs)                 | fc/2 <sup>6</sup> (1.33 µs) | fc/2 <sup>8</sup> (5.33 µs)   |  |  |

|                                                | 111 (fc/16)                        | 100 (fperiph/16)                                      | fc/2⁵ (0.67 µs)                 | fc/2 <sup>7</sup> (2.67 µs) | fc/2 <sup>9</sup> (10.67 μs)  |  |  |

|                                                |                                    | 101 (fperiph/32)                                      | fc/2 <sup>6</sup> (1.33 μs)     | fc/2 <sup>8</sup> (5.33 µs) | fc/2 <sup>10</sup> (21.33 µs) |  |  |

| <                                              |                                    | 000 (fperiph/1)                                       | $\left( \right)$                | -                           | fc/2⁵ (0.67 µs)               |  |  |

|                                                |                                    | 001 (fperiph/2)                                       | -                               | -                           | fc/2 <sup>6</sup> (1.33 μs)   |  |  |

|                                                |                                    | 010 (fperiph/4)                                       | -                               | fc/2⁵ (0.67 µs)             | fc/2 <sup>7</sup> (2.67 µs)   |  |  |

|                                                |                                    | 011 (fperiph/8)                                       | -                               | fc/2 <sup>6</sup> (1.33 µs) | fc/2 <sup>8</sup> (5.33 µs)   |  |  |

|                                                |                                    | 100 (fperiph/16)                                      | fc/2⁵ (0.67 µs)                 | fc/2 <sup>7</sup> (2.67 µs) | fc/2 <sup>9</sup> (10.67 μs)  |  |  |

|                                                | _                                  | 101 (fperiph/32)                                      | fc/2 <sup>6</sup> (1.33 μs)     | fc/2 <sup>8</sup> (5.33 µs) | fc/2 <sup>10</sup> (21.33 µs) |  |  |

Note 1: The prescaler output clock  $\phi$ Tn must be selected so that  $\phi$ Tn < fsys is satisfied (so that  $\phi$ Tn is slower than fsys). Note 2: Do not change the clock gear while the timer is operating.

Note 3: "-" denotes a setting prohibited.

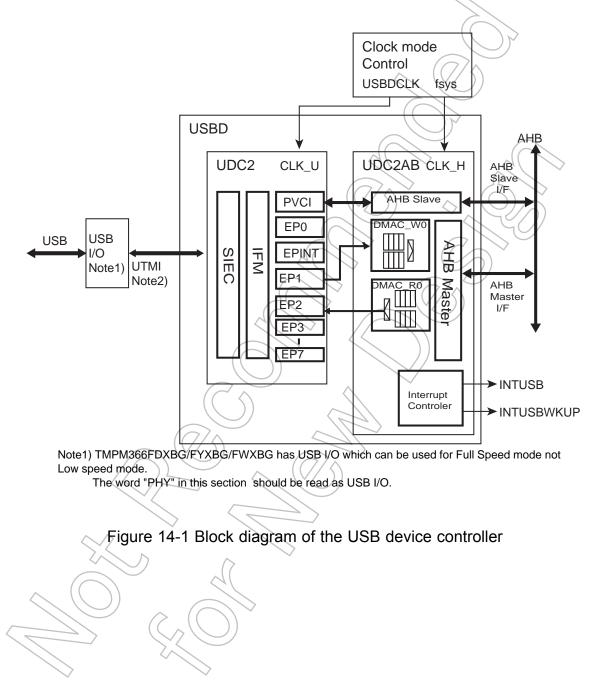

### 14.2 System Structure

The USB device controller consists of the USB-Spec2.0 device controller (hereinafter called UDC2) and the bus bridge (hereinafter called UDC2AB) which connects the UDC2 and the AHB bus.

In this section, "14.2.1 AHB Bus Bridge (UDC2AB)" describes the configuration of the UDC2AB, and "14.2.2 Toshiba USB-Spec2.0 Device Controller (UDC2)" describes that of the UDC2.

- f. By detecting Resume on the USB bus, the WAKEUP output signal will be asserted to 0 asynchronously.By WAKEUP output signal, INTUSBWKUP occurs and the low-power consumption mode is cancelled. Then, supply of CLK\_H starts.

- g. With the supply of CLK\_H, PHYSUSPEND output signal is automatically asserted to "1", and <phy\_suspend> is zero-cleared.

Set CGUSBCTL<USBCLKEN> of the clock/mode control circuit to "1" to activate the CLK\_U.

- h. 2.5 s after the interrupt is asserted (time required for the signal to stabilize when VBUS is disconnected) and check UDFSPWCTL<pw\_detect>. If the UDFSPWCTL<pw\_detect> is "1", WAKEUP is asserted by Resume. If UDFSPWCTL<pw\_detect> is "0", WAKEUP is asserted by disconnection of the VBUS.

- i. To resume, perform the sequences below. To disconnect, perform the sequences of the "14.5.7.3 Resuming from the suspend state (disconnect)".

- j. Clears the interrupt factor and <wakeup\_en> to deassert the WAKEUP output signal. Set <suspend\_resume\_en> to "1".

- k. Resumes from the suspended state.

#### 15.4 Registers Description

### 15.4.12 SCxRST (RX FIFO Status Register)

|             | 31  | 30 | 29 | 28 | 27  | 26    | 25   | 24 |

|-------------|-----|----|----|----|-----|-------|------|----|

| bit symbol  | -   | -  | -  | -  | -   | -     | -    | -  |

| After reset | 0   | 0  | 0  | 0  | 0   | 0     | 0    | 0  |

|             | 23  | 22 | 21 | 20 | 19  | 18    | 17   | 16 |

| bit symbol  | -   | -  | -  | -  | -   | - ((  | 3    | -  |

| After reset | 0   | 0  | 0  | 0  | 0   | 0     | 0    | 0  |

|             | 15  | 14 | 13 | 12 | 11  | (107/ | 9    | 8  |

| bit symbol  | -   | -  | -  | -  |     |       | ) -  | -  |

| After reset | 0   | 0  | 0  | 0  | 0   | 6     | 0    | 0  |

|             | 7   | 6  | 5  | 4  | 3   | 2     | 1    | 0  |

| bit symbol  | ROR | -  | -  | -  | - ( |       | RLVL |    |

| After reset | 0   | 0  | 0  | 0  | Q   | 0     | 0    | 0  |

| Bit  | Bit Symbol | Туре | ( /Function                                                                                             |

|------|------------|------|---------------------------------------------------------------------------------------------------------|

| 31-8 | -          | R    | Read as 0.                                                                                              |

| 7    | ROR        | R    | RX FIFO Overrun (Note)<br>0: Not generated                                                              |

|      |            |      | 1: Generated                                                                                            |

| 6-3  | -          | R    | Read as 0.                                                                                              |

| 2-0  | RLVL[2:0]  | R    | Status of RX FIFO fill level.<br>000: Empty<br>001: 1 byte<br>010: 2 byte<br>011: 3 byte<br>100: 4 byte |

Note: The <ROR> bit is cleared to "0" when receive data is read from the SCxBUF register.

Overview

16.1

(1) UART transmit / receive data format.

| START       DATA<br>(LSB - MSB)       PARITY       STOP         (2)Receive FIFO data format         Bit Number<br>Receive 8-bit data<br>Receive 6-bit data<br>Receive 6-bit data         Receive data format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                             | Transmit / recei | ve data forma             | at            |                  |                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|------------------|---------------------------|---------------|------------------|---------------------------|

| (2)Receive FIFO data format<br>$ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        | START                       |                  | P                         | ARITY         | STOP             |                           |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I                      |                             | (LOD → NIOD)     |                           |               |                  |                           |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (2)Receive FIFO data f | ormat                       |                  |                           |               |                  | 52                        |

| Bit Number         0         1         2         3         4         5         6         7           Receive 8-bit data         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1< |                        | ormat                       |                  |                           | ~             | (7)              |                           |

| Bit Number         0         1         2         3         4         5         6         7           Receive 8-bit data         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1< |                        | F                           | Receive data     | Framing                   | Parity er     | rror Break error | Overrun                   |

| Receive 8-bit data         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0   |                        |                             |                  |                           |               |                  |                           |

| Receive 7-bi data         1         1         1         1         1         1         0           Receive 6-bit data         1         1         1         1         1         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |                             |                  |                           |               | $\bigcirc$       |                           |

| Receive 6-bit data 1 1 1 1 1 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |                             |                  |                           | $\mathcal{A}$ |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  |                           | $\nearrow$    |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  | (()                       | 7/^           | 1                | $\langle \rangle \rangle$ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  |                           | $\bigcirc$    |                  | ZUN)                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  | $ \leq $                  | <u> </u>      |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  |                           | $\checkmark$  | $(C_{\sim})$     | $\sim$                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             | <                | $\langle \ \rangle$       |               |                  | )                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             | $( \ \ )$        | $\searrow$                |               | (7)              |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  | $\searrow$                | $\frown$      | $(\bigcirc)$     |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  | > /                       |               | $\backslash$     |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  | $\langle$                 |               |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             | (())             |                           |               | //               |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  | $\wedge$                  |               |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | (                           | ( )              |                           |               |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  |                           | $\leq$        |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | (7/                         |                  | $\langle \gamma \rangle$  |               |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | $\mathcal{Y}$               | ) (i             | 77^                       | 7             |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  | $\langle \rangle \rangle$ |               |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                             |                  |                           |               |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | $\searrow$                  |                  | $\geq$                    |               |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\sim \sim \sim$       | ÷                           |                  |                           |               |                  |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Z/ N                   |                             | $\sim$           |                           |               |                  |                           |