#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16.5MHz                                                                   |

| Connectivity               | EBI/EMI, UART/USART                                                       |

| Peripherals                | DMA                                                                       |

| Number of I/O              | 56                                                                        |

| Program Memory Size        | -                                                                         |

| Program Memory Type        | ROMIess                                                                   |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 68-LCC (J-Lead)                                                           |

| Supplier Device Package    | 68-PLCC (24.21x24.21)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/ia80c152jb-jdplc68ir1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## LIST OF FIGURES

| Figure 1. | JA/JC Versions Package Diagram                        | 10 |

|-----------|-------------------------------------------------------|----|

| Figure 2. | JB/JD Versions Package Diagram                        | 13 |

| Figure 3. | Package Dimensions                                    | 16 |

| Figure 4. | Functional Block Diagram                              | 22 |

| Figure 5. | Memory Space                                          | 24 |

| Figure 6. | External Program Memory Read Cycle                    | 44 |

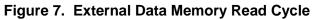

| Figure 7. | External Data Memory Read Cycle                       | 44 |

| Figure 8. | External Data Memory Write Cycle                      | 45 |

| Figure 9. | External Clock Drive Waveform                         | 46 |

| Figure 10 | Shift Register Mode Timing Waveforms                  | 47 |

| Figure 11 | . GSC Receiver Timings (Internal Baud Rate Generator) | 48 |

| Figure 12 | . GSC Transmit Timings (Internal Baud Rate Generator) | 48 |

| -         | . GSC Timings (External Clock)                        |    |

IA211040524-06 UNCONTROLLED WHEN PRINTED OR COPIED Page 5 of 61

- CSMA/CD

- SDLC/HDLC

- User Definable

- Separate Transmit & Receive FIFOs

- Special Protocol Features:

- Up to 2.0625 Mbps Serial Operation

- CSMA and SDLC Frame Formats with CRC Checking

- Manchester, NRZ, & NRZI Data Encoding

- Collision Detection & Resolution in CSMA Mode

- Selectable Full/Half Duplex

# 2. Packaging, Pin Descriptions, and Physical Dimensions

Information on the packages and pin descriptions is provided in this chapter.

## 2.1 Packages and Pinouts

The IA80C152 is available in the following packages:

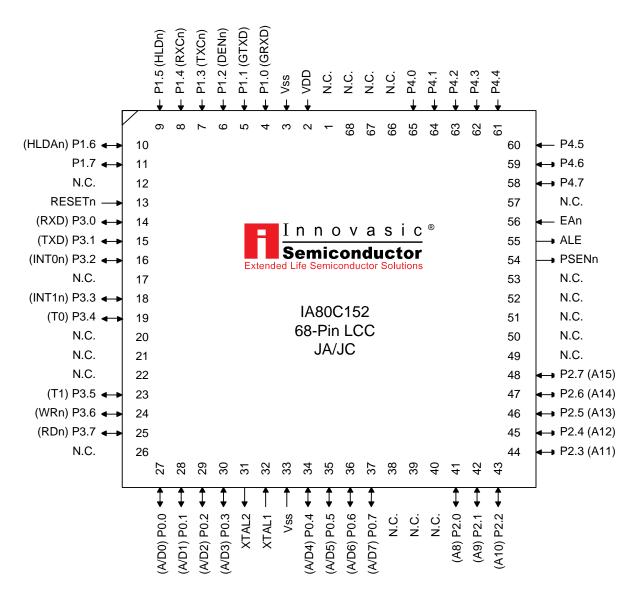

- 68-Pin PLCC pinout JA/JC versions

- 68-Pin PLCC pinout JB/JD versions

### 2.1.1 JA/JC

The pinout for the JA/JC package is as shown in Figure 1. The corresponding numeric and alphabetic pin listings are provided in Tables 2 and 3.

Figure 1. JA/JC Versions Package Diagram

IA211040524-06 UNCONTROLLED WHEN PRINTED OR COPIED Page 10 of 61

nirr-Gitt

÷

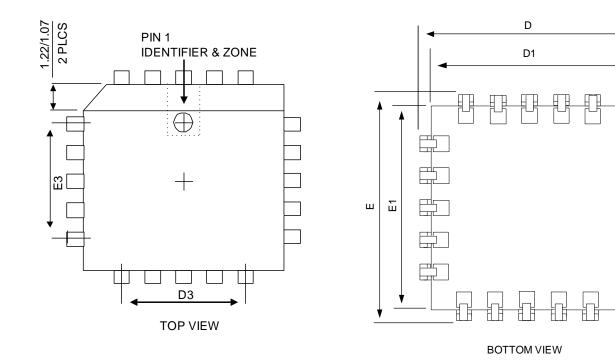

## 2.1.3 Physical Dimensions

The package dimensions are as shown in Figure 3.

| Legend: |                     |       |  |  |  |

|---------|---------------------|-------|--|--|--|

|         | 68 (in Millimeters) |       |  |  |  |

| Symbol  | Min                 | Max   |  |  |  |

| А       | 4.20                | 5.08  |  |  |  |

| A1      | 2.29                | 3.30  |  |  |  |

| D1      | 24.13               | 24.33 |  |  |  |

| D2      | 22.61               | 23.62 |  |  |  |

| D3      | 20.32 BSC           |       |  |  |  |

| E1      | 24.13               | 24.33 |  |  |  |

| E2      | 22.61               | 23.62 |  |  |  |

| E3      | 20.32               | BSC   |  |  |  |

| е       | 1.27                | BSC   |  |  |  |

| D       | 25.02               | 25.27 |  |  |  |

| E       | 25.02               | 25.27 |  |  |  |

## Figure 3. Package Dimensions

IA211040524-06 UNCONTROLLED WHEN PRINTED OR COPIED Page 16 of 61 http://www.Innovasic.com Customer Support: 1-888-824-4184

| Signal Name                        | Description                                                                     |

|------------------------------------|---------------------------------------------------------------------------------|

| P1.0 - GRXD, GSC                   | Port 1—8-bit bi-directional port that is bit addressable. To use a port signal  |

| Receive                            | as an input, write a 1 to the port location. Internal pull-ups pull the input   |

| P1.1 - GTXD, GSC                   | high and source current when the input is driven low. To use a port signal      |

| Transmit                           | as an output, a 1 or 0 written to the port location is presented at the output. |

| P1.2 - DENn, Driver Enable         |                                                                                 |

| P1.3 - TXCn, External              | Port signals in this port also serve as I/O for IA80C152 functions. These I/O   |

| Transmit Clock                     | signals are defined next to the port name.                                      |

| P1.4 - RXCn, External              |                                                                                 |

| Receive Clock                      |                                                                                 |

| P1.5 - HLDn, DMA Hold              |                                                                                 |

| P1.6 - HLDAn, DMA Hold             |                                                                                 |

| Acknowledge                        |                                                                                 |

| P1.7                               |                                                                                 |

| P2.0                               | Port 2—8-bit bi-directional port that is bit addressable. To use a port signal  |

| P2.1                               | as an input, write a 1 to the port location. Internal pull-ups pull the input   |

| P2.2                               | high and source current when the input is driven low. To use a port signal      |

| P2.3                               | as an output, a 1 or 0 written to the port location is presented at the output. |

| P2.4                               |                                                                                 |

| P2.5                               | This port also provides the high-byte of the multiplexed address and data       |

| P2.6                               | bus depending on the state of EBEN.                                             |

| P2.7                               |                                                                                 |

|                                    | Port 3—8-bit bi-directional port that is bit addressable. To use a port signal  |

| P3.1 - TXD, UART                   | as an input, write a 1 to the port location. Internal pull-ups pull the input   |

| Transmit                           | high and source current when the input is driven low. To use a port signal      |

| P3.2 - INT0n, External             | as an output, a 1 or 0 written to the port location is presented at the output. |

| Interrupt 0                        |                                                                                 |

| P3.3 - INT1n, External             | Port signals in this port also serve as I/O for IA80C152 functions. These I/O   |

| Interrupt 1                        | signals are defined next to the port name.                                      |

| P3.4 - T0, Timer 0 External        |                                                                                 |

| Input                              |                                                                                 |

| P3.5 - T1, Timer 1 External        |                                                                                 |

| Input<br>P3.6 - WRn, External Data |                                                                                 |

| Memory Write Strobe                |                                                                                 |

| P3.7 - RDn, External Data          |                                                                                 |

| Memory Read Strobe                 |                                                                                 |

| Internoly Read Strobe              |                                                                                 |

## Table 6. I/O Signal Descriptions (Continued)

| Symbol            | Parameter                                                                  | Min | Тур | Max | Unit | Test Conditions           |

|-------------------|----------------------------------------------------------------------------|-----|-----|-----|------|---------------------------|

| V <sub>CC</sub>   | Supply Voltage                                                             | 4.5 | _   | 5.5 | V    | -                         |

| V <sub>IL</sub>   | Input Low Voltage (All Except XTAL1)                                       | -   | _   | 0.9 | V    | -                         |

| V <sub>IH</sub>   | Input High Voltage (All Except XTAL1)                                      | 2.1 | —   | _   | V    | -                         |

| V <sub>OL</sub>   | Output Low Voltage                                                         | -   | -   | 0.4 | V    | -                         |

| V <sub>OH</sub>   | Output High Voltage (All Except Port 0 in                                  | 3.5 | _   | -   | V    | _                         |

|                   | port mode)                                                                 | -   | —   | -   |      | -                         |

| V <sub>OH1</sub>  | Output High Voltage (Port 0 in External Bus                                | 3.5 | —   | -   | V    | -                         |

|                   | Mode)                                                                      | -   | _   | _   | _    | _                         |

| I <sub>IL</sub>   | Logical 0 Input Current                                                    | -1  | -   | 1   | μA   | No pullup or<br>pulldown  |

| I <sub>IH</sub>   | Logical 1 Input Current                                                    | -1  | -   | 1   | μA   | No pullup or<br>pulldown  |

| l <sub>oz</sub>   | Input Leakage ( Port 0,1,2,3,4,5,6,<br>ALE,PSEN, EPSEN)                    | -10 | -   | 10  | μA   | Tri-state leakage current |

| Rup,<br>Rdn       | Pull-up Resistor, Pull-down Resistor                                       | -   | 50  | -   | kW   | -                         |

| I <sub>DD</sub> a | Power Supply Current: Active (16.5 MHz)<br>Idle (16.5 MHz) Power Down Mode | -   | -   | 50  | mA   | -                         |

|                   |                                                                            |     | _   | -   | mA   | -                         |

|                   |                                                                            |     | _   | _   | μA   | -                         |

## Table 9. DC Parameters

<sup>a</sup>Static Idd current is exclusive of input/output drive requirements and is measured with the clocks stopped and all inputs tied to Vdd or Vss configured to draw minimum current.

IA211040524-06 UNCONTROLLED WHEN PRINTED OR COPIED Page 21 of 61

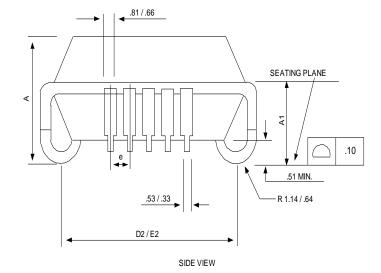

## 4. Device Architecture

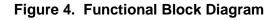

## 4.1 Functional Block Diagram

Figure 4 shows the major functional blocks of the IA80C152. Each version of the IA80C152 function identically to each other with the exception of the 2 additional I/O ports (Port 5 and Port 6) in the JB and JD versions.

I/O for Memory, GSC, DMA, UART, Interrupts, and Timers

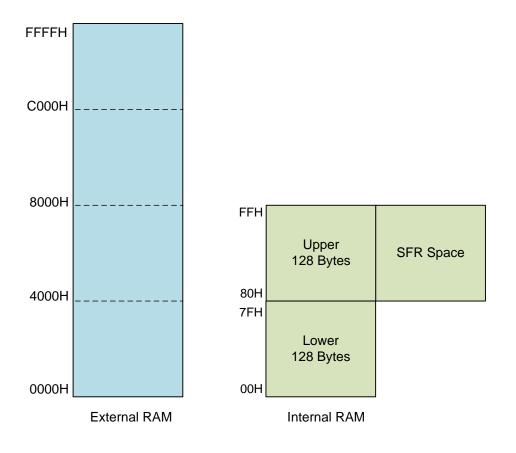

Figure 5. Memory Space

In the Raw Transmit mode the receiver operates as normal and zero bit detection is performed in SDLC mode. The transmit output is internally connected to the receiver input for loopback testing. Data transmitted is done so without a preamble, flag or zero bit insertion and without a CRC.

In the Alternate Backoff mode the backoff is modified so it is delayed until the end of the IFS. Since the IFS time is generally longer than the slot time this should help to prevent collisions.

- Bit [4]—AL → This bit determines the address length used. If set to a 1, the 16-bit addressing is used. If set to a 0, the 8 bit addressing is used.

- Bit [3]—CT → This bit determines the CRC type used. If set to a 1, the 32-bit AUTODIN II-32 is used. If set to a 0, the 16 bit CRC-CCITT is used.

- Bits [2-1]—PL0, PL1  $\rightarrow$  Preamble length:

| PL1 | PL0 | Preamble length in bits |

|-----|-----|-------------------------|

| 0   | 0   | 0                       |

| 0   | 1   | 8                       |

| 1   | 0   | 32                      |

| 1   | 1   | 64                      |

The length noted in the table includes the two-bit BOF in CSMA/CD mode but not the SDLC flag. Zero length preamble is not compatible with CSMA/CD mode.

• Bit [0]—PR → If set to a 1, the GSC is in SDLC mode. If set to a 0, the GSC is in CSMA/CD mode.

## 5.2.14 IE\* (0A8h)

The Interrupt Enable register allows the software to select which interrupts are enabled as shown in Table 15. If a bit is 0, the interrupt is disabled. If a bit is 1, the interrupt is enabled.

## Table 15. IE\* Register

| 7  | 6        | 5        | 4  | 3   | 2   | 1   | 0   |

|----|----------|----------|----|-----|-----|-----|-----|

| EA | Reserved | Reserved | ES | ET1 | EX1 | ET0 | EX0 |

- Bit [7]—EA  $\rightarrow$  Enable All interrupts. This bit globally enables or disables all interrupts regardless of the state of the individual bits.

- Bit [6]—Reserved.

- Bit [5]—Reserved.

- Bit [4]—ES  $\rightarrow$  Enable or disable serial port interrupt.

- Bit [3]—ET1  $\rightarrow$  Enable or disable Timer 1 overflow interrupt.

- Bit [2]—EX1  $\rightarrow$  Enable or disable External Interrupt 1.

- Bit [1]—ET0  $\rightarrow$  Enable or disable Timer 0 overflow interrupt.

- Bit [0]—EX0  $\rightarrow$  Enable or disable External Interrupt 0.

## 5.2.15 IEN1\* (0C8h)

The Interrupt Enable Number 1 register allows the software to select which interrupts are enabled as shown in Table 16. If a bit is 0, the interrupt is disabled. If a bit is 1, the interrupt is enabled.

### Table 16. IEN1\* Register

| ĺ | 7        | 6        | 5     | 4     | 3     | 2     | 1     | 0     |

|---|----------|----------|-------|-------|-------|-------|-------|-------|

|   | Reserved | Reserved | EGSTE | EDMA1 | EGSTV | EDMA0 | EGSRE | EGSRV |

- Bit [7]—Reserved.

- Bit [6]—Reserved.

- Bit [5]—EGSTE  $\rightarrow$  Enable or disable GSC Transmit Error interrupt.

- Bit [4]—EDMA1  $\rightarrow$  Enable or disable DMA channel 1 interrupt.

- Bit [3]—EGSTV  $\rightarrow$  Enable or disable GSC Transmit Valid interrupt.

- Bit [2]—EDMA0  $\rightarrow$  Enable or disable DMA channel 0 interrupt.

- Bit [1]—EGSRE  $\rightarrow$  Enable or disable GSC Receive Error interrupt.

- Bit [0]—EGSRV  $\rightarrow$  Enable or disable GSC Receive Valid interrupt.

## 5.2.16 IFS (0A4h)

The Interframe Spacing register determines the number of bit times between transmitted frames in both CSMA/CD and SDLC. Only even bit times can be used. The number written to this register is divided by two and loaded into the seven most significant bits. An interframe space is created by counting down this seven bit number twice. The value read from this register is the current count value in the upper seven bits and the first or second count down in the LSB. A 1 indicates the first count down and a 0 indicates the second count down. The value may not be valid because the register is clocked asynchronously to the CPU.

|    | Port        | Bit 7   | Bit 6        | Bit 5     | Bit 4    | Bit 3   | Bit 2 | Bit 1 | Bit 0 |  |

|----|-------------|---------|--------------|-----------|----------|---------|-------|-------|-------|--|

| P0 | Function    | Multipl | exed Addı    | ress/Data | a        |         |       |       |       |  |

|    | Bit Address | 087h    | 086h         | 085h      | 084h     | 083h    | 082h  | 081h  | 080h  |  |

| P1 | Function    | _       | HLDAn        | HLDn      | RXCn     | TXCn    | DENn  | GTXD  | GRXD  |  |

|    | Bit Address | 097h    | 096h         | 095h      | 094h     | 093h    | 092h  | 091h  | 090h  |  |

| P2 | Function    |         |              | Add       | ress and | User De | fined |       |       |  |

|    | Bit Address | 0A7h    | 0A6h         | 0A5h      | 0A4h     | 0A3h    | 0A2h  | 0A1h  | 0A0h  |  |

| P3 | Function    | RDn     | WRn          | T1        | T0       | INT1n   | INT0n | TXD   | RXD   |  |

|    | Bit Address | 0B7h    | 0B6h         | 0B5h      | 0B4h     | 0B3h    | 0B2h  | 0B1h  | 0B0h  |  |

| P4 | Function    |         |              |           | User [   | Defined |       |       |       |  |

|    | Bit Address | 0C7h    | 0C6h         | 0C5h      | 0C4h     | 0C3h    | 0C2h  | 0C1h  | 0C0h  |  |

| P5 | Function    |         |              |           | User [   | Defined |       |       |       |  |

|    | Bit Address |         | 091h         |           |          |         |       |       |       |  |

| P6 | Function    |         | User Defined |           |          |         |       |       |       |  |

|    | Address     |         |              |           | 0A       | \1h     |       |       |       |  |

### Table 20. P0\*, P1\*, P2\*, P3\*, P4\*, P5, P6 Register

### 5.2.21 PCON (087h)

The Power Control register controls the power down and idle states of the IA80C152 as well as various UART, GSC, and DMA functions as defined in Table 21.

#### Table 21. PCON Register

| 7    | 6   | 5   | 4     | 3     | 2     | 1  | 0   |

|------|-----|-----|-------|-------|-------|----|-----|

| SMOD | ARB | REQ | GAREN | XRCLK | GFIEN | PD | IDL |

- Bit [7]—SMOD  $\rightarrow$  Doubles the baud rate of the UART if the bit is set to 1.

- Bit [6]—ARB  $\rightarrow$  The DMA (both channels) is put into Arbiter mode if the bit is set to 1.

- Bit [5]—REQ → The DMA (both channels) is put into Requester mode if the bit is set to 1.

- Bit [4]—GAREN → The GSC Auxiliary Receive Enable allows the GSC to receive back-to-back SDLC frames by setting the bit to 1. This bit has no effect in CSMA mode.

- Bit [3]—XRCLK → Setting this bit enables the External Receive Clock to be used by the receiver portion of the GSC.

- Bit [2]—GFIEN → The GSC Flag Idle Enable bit generates idle flags between transmitted SDLC frames when this bit is set to a 1. This bit has no effect in CSMA mode.

#### Table 25. TCON\* Register

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

- Bit [7]—TF1 → Timer overFlow 1 interrupt flag set by hardware when timer 1 overflows. Hardware clears this flag when the processor vectors to the interrupt service routine.

- Bit [6]—TR1 → Timer Run 1 flag set by software to turn on timer 1 and cleared by software to turn off timer 1.

- Bit [5]—TF0 → Timer overFlow 0 interrupt flag set by hardware when timer 0 overflows. Hardware clears this flag when the processor vectors to the interrupt service routine.

- Bit [4]—TR0  $\rightarrow$  Timer Run 0 flag set by software to turn on timer 0 and cleared by software to turn off timer 0.

- Bit [3]—IE1 → Interrupt External 1 flag set by hardware when an edge is detected on External Interrupt 1. Hardware clears this flag when the processor vectors to the interrupt service routine.

- Bit [2]—IT1 → Interrupt Type 1 flag is set by software to specify a falling edge triggered interrupt for External Interrupt 1. The flag is cleared by software to specify a low level triggered interrupt for External Interrupt 1.

- Bit [1]—IE0 → Interrupt External 0 flag set by hardware when an edge is detected on External Interrupt 0. Hardware clears this flag when the processor vectors to the interrupt service routine.

- Bit [0]—IT0 → Interrupt Type 0 flag is set by software to specify a falling edge triggered interrupt for External Interrupt 0. The flag is cleared by software to specify a low level triggered interrupt for External Interrupt 0.

## 5.2.34 TFIFO (085h)

This is the 3 byte buffer used for storing GSC transmit data. If TEN is set to a 1 transmission begins as soon as data is written to TFIFO.

## 5.2.35 TH0, TL0 (08Ch, 08Ah)

These registers provide the high byte (TH0) and low byte (TL0) values for Timer 0. These registers may be used together or separately depending on Timer 0 mode bits.

Power Down Mode is entered through software control of the PCON register. Power Down disables the oscillator causing all functions to stop. RAM data is maintained because power is not removed from the device. The only way to exit power down mode is to invoke a hardware reset.

|       | Program             |     |       |                     | Port  | Port | Port  | Port | Port | Port           | Port           |

|-------|---------------------|-----|-------|---------------------|-------|------|-------|------|------|----------------|----------------|

| Mode  | Fetch               | ALE | PSENn | EPSENn <sup>a</sup> | 0     | 1    | 2     | 3    | 4    | 5 <sup>a</sup> | 6 <sup>a</sup> |

| Idle  | P0, P2              | 1   | 1     | 1                   | Float | Data | Addr. | Data | Data | Data           | Data           |

|       | P5, P6 <sup>a</sup> | 1   | 1     | 1                   | Data  | Data | Data  | Data | Data | 0FFh           | Addr.          |

| Power | P0, P2              | 0   | 0     | 1                   | Float | Data | Data  | Data | Data | Data           | Data           |

| Down  | P5, P6 <sup>a</sup> | 0   | 1     | 0                   | Data  | Data | Data  | Data | Data | 0FFh           | 0FFh           |

## Table 28. Power Conservation Modes

<sup>a</sup>JB and JD versions only.

## 5.4 Oscillator Pins

There are 2 methods for providing a clock to the IA80C152. One method is to provide a crystal oscillator and the other method is to provide an external clock source. When providing a crystal oscillator, the XTAL1 pin is the input and XTAL2 is the output. The min and max crystal frequencies are 3.5 and 16.5 MHz, respectively.

When providing an external clock source, XTAL1 is the input and XTAL2 has no connection. Duty cycle does not matter to the device, however, the external clock source requires a minimum pulse width of 20 ns.

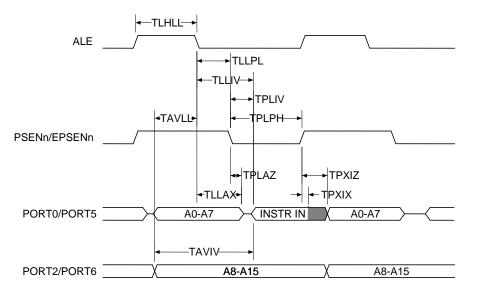

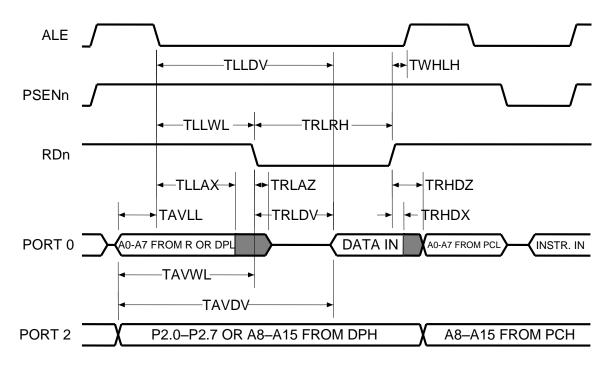

Figures 6 through 13 present the external program memory read cycle, the external data memory read cycle, the external data memory write cycle, the external clock drive waveform, the shift register mode timing waveforms, the GSC receiver timings (internal baud rate generator), the GSC transmit timings (internal baud rate generator), the GSC timings (external clock) respectively. Tables 29 through 32 present the external clock drive, the local serial channel timing—shift register mode, the global serial port timing—internal baud rate generator, and the global serial port timing—external clock, respectively.

IA211040524-06 UNCONTROLLED WHEN PRINTED OR COPIED Page 43 of 61

Figure 6. External Program Memory Read Cycle

# 6. Instruction Set Summary Table

Table 33 provides a summary of the instruction set organized by hexadecimal opcode. Please refer to the original Intel Data Book for individual instruction set details.

Table 33. Instruction Set Summary

| Ornerale |                    |

|----------|--------------------|

| Opcode   | Mnemonic           |

| 00 H     | NOP                |

| 01 H     | AJMP addr11        |

| 02 H     | LJMP addr16        |

| 03 H     | RR A               |

| 04 H     | INC A              |

| 05 H     | INC direct         |

| 06 H     | INC @R0<br>INC @R1 |

| 07 H     | INC @R1            |

| 08 H     | INC R0             |

| 09 H     | INC R1             |

| 0A H     | INC R2             |

| 0B H     | INC R3             |

| 0C H     | INC R4             |

| 0D H     | INC R5             |

| 0E H     | INC R6<br>INC R7   |

| 0F H     | INC R7             |

| 10 H     | JBC bit,rel        |

| 11 H     | ACALL addr11       |

| 12 H     | LCALL addr16       |

| 13 H     | RRC A              |

| 14 H     | DEC A              |

| 15 H     | DEC direct         |

| 16 H     | DEC @R0            |

| 17 H     | DEC @R1            |

| 18 H     | DEC R0             |

| 19 H     | DEC R1<br>DEC R2   |

| 1A H     | DEC R2             |

| 1B H     | DEC R3             |

| 1C H     | DEC R4             |

| 1D H     | DEC R5<br>DEC R6   |

| 1E H     | DEC R6             |

| 1F H     | DEC R7             |

| 20 H     | JB bit.rel         |

| 21 H     | AJMP addr11        |

| 22 H     | RET                |

| 23 H     | RL A               |

| 24 H     | ADD A,#data        |

| 25 H     | ADD A, direct      |

| 26 H     | ADD A,@R0          |

| 27 H     | ADD A,@R1          |

| 28 H     | ADD A,R0           |

IA211040524-06 UNCONTROLLED WHEN PRINTED OR COPIED Page 50 of 61

| Opcode       | Mnemonic                                                                                                                                  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 29 H         | ADD A,R1                                                                                                                                  |

| 2A H         | ADD A,R2                                                                                                                                  |

| 2B H         | ADD A,R3                                                                                                                                  |

| 2C H         | ADD A,R4                                                                                                                                  |

| 2D H         | ADD A,R5                                                                                                                                  |

| 2E H         | ADD A,R6                                                                                                                                  |

| 2F H         | ADD A,R7                                                                                                                                  |

| 2F H<br>30 H | JNB bit.rel                                                                                                                               |

| 31 H         | ACALL addr11                                                                                                                              |

| 32 H         | RETI                                                                                                                                      |

| 33 H         | RLC A                                                                                                                                     |

| 34 H         | ADDC A,#data                                                                                                                              |

| 35 H         | ADDC A, direct                                                                                                                            |

| 36 H         | ADDC A,@R0                                                                                                                                |

| 37 H         | ADDC A,@R1                                                                                                                                |

| 38 H         | ADDC A,R0                                                                                                                                 |

| 39 H         | ADDC A,R1                                                                                                                                 |

| 3A H         | ADDC A,R2                                                                                                                                 |

| 3B H         | ADDC A,R3                                                                                                                                 |

| 3C H         | ADDC A,R4                                                                                                                                 |

| 3D H         | ADDC A,R5                                                                                                                                 |

| 3E H         | ADDC A,R6                                                                                                                                 |

| 3F H         | RLC AADDC A,#dataADDC A,directADDC A,@R0ADDC A,@R1ADDC A,R0ADDC A,R1ADDC A,R2ADDC A,R2ADDC A,R3ADDC A,R4ADDC A,R5ADDC A,R6ADDC A,R7JC rel |

| 3F H<br>40 H |                                                                                                                                           |

| 41 H         | AJMP addr11                                                                                                                               |

| 42 H         | ORL direct,A                                                                                                                              |

| 43 H         | ORL direct,#data                                                                                                                          |

| 44 H         | ORL A,#data                                                                                                                               |

| 45 H         | ORL A, direct                                                                                                                             |

| 46 H         | ORL A,@R0                                                                                                                                 |

| 47 H         | ORL A,@R1                                                                                                                                 |

| 48 H         | ORL A,R0                                                                                                                                  |

| 49 H         | ORL A,R1                                                                                                                                  |

| 4A H         | ORL A,R2                                                                                                                                  |

| 4B H         | ORL A,R3                                                                                                                                  |

| 4C H         | ORL A,R4                                                                                                                                  |

| 4D H         | ORL A,R5                                                                                                                                  |

| 4E H         | ORL A,R6                                                                                                                                  |

| 4F H<br>50 H | ORL A,R7                                                                                                                                  |

| 50 H         | JNC rel                                                                                                                                   |

| 51 H         | ACALL addr11                                                                                                                              |

| 52 H         | ANL direct,A                                                                                                                              |

| 53 H         | ANL direct,#data                                                                                                                          |

| 54 H         | ANL A,#data                                                                                                                               |

| 55 H         | ANL A, direct                                                                                                                             |

| 56 H         | ANL A,@R0                                                                                                                                 |

## Table 33. Instruction Set Summary (Continued)

| Opcode | Mnemonic            |  |  |  |

|--------|---------------------|--|--|--|

| B3 H   | CPL C               |  |  |  |

| B4 H   | CJNE A,#data,rel    |  |  |  |

| B5 H   | CJNE A, direct, rel |  |  |  |

| B6 H   | CJNE                |  |  |  |

|        | @R0,#data,rel       |  |  |  |

| B7 H   | CJNE                |  |  |  |

|        | @R1,#data,rel       |  |  |  |

| B8 H   | CJNE R0,#data,rel   |  |  |  |

| B9 H   | CJNE R1,#data,rel   |  |  |  |

| BA H   | CJNE R2,#data,rel   |  |  |  |

| BB H   | CJNE R3,#data,rel   |  |  |  |

| BC H   | CJNE R4,#data,rel   |  |  |  |

| BD H   | CJNE R5,#data,rel   |  |  |  |

| BE H   | CJNE R6,#data,rel   |  |  |  |

| BF H   | CJNE R7,#data,rel   |  |  |  |

| C0 H   | PUSH direct         |  |  |  |

| C1 H   | AJMP addr11         |  |  |  |

| C2 H   | CLR bit             |  |  |  |

| C3 H   | CLR C               |  |  |  |

| C4 H   | SWAP A              |  |  |  |

| C5 H   | XCH A, direct       |  |  |  |

| C6 H   | XCH A,@R0           |  |  |  |

| C7 H   | XCH A,@R1           |  |  |  |

| C8 H   | XCH A,R0            |  |  |  |

| C9 H   | XCH A,R1            |  |  |  |

| CAH    | XCH A,R2            |  |  |  |

| CB H   | XCH A,R3            |  |  |  |

| CC H   | XCH A,R4            |  |  |  |

| CD H   | XCH A,R5            |  |  |  |

| CE H   | XCH A,R6            |  |  |  |

| CF H   | XCH A,R7            |  |  |  |

| D0 H   | POP direct          |  |  |  |

| D1 H   | ACALL addr11        |  |  |  |

| D2 H   | SETB bit            |  |  |  |

| D3 H   | SETB C              |  |  |  |

| D4 H   | DA A                |  |  |  |

| D5 H   | DJNZ direct,rel     |  |  |  |

| D6 H   | XCHD A,@R0          |  |  |  |

| D7 H   | XCHD A,@R1          |  |  |  |

| D8 H   | DJNZ R0,rel         |  |  |  |

| D9 H   | DJNZ R1,rel         |  |  |  |

| DA H   | DJNZ R2,rel         |  |  |  |

| DB H   | DJNZ R3,rel         |  |  |  |

| DC H   | DJNZ R4,rel         |  |  |  |

| DD H   | DJNZ R5,rel         |  |  |  |

| DE H   | DJNZ R6,rel         |  |  |  |

## Table 33. Instruction Set Summary (Continued)

| Opcode | Mnemonic      |  |  |

|--------|---------------|--|--|

| DF H   | DJNZ R7,rel   |  |  |

| E0 H   | MOVX A,@DPTR  |  |  |

| E1 H   | AJMP addr11   |  |  |

| E2 H   | MOVX A,@R0    |  |  |

| E3 H   | MOVX A,@R1    |  |  |

| E4 H   | CLR A         |  |  |

| E5 H   | MOV A, direct |  |  |

| E6 H   | MOV A,@R0     |  |  |

| E7 H   | MOV A,@R1     |  |  |

| E8 H   | MOV A,R0      |  |  |

| E9 H   | MOV A,R1      |  |  |

| EAH    | MOV A,R2      |  |  |

| EB H   | MOV A,R3      |  |  |

| EC H   | MOV A,R4      |  |  |

| ED H   | MOV A,R5      |  |  |

| EE H   | MOV A,R6      |  |  |

| EFH    | MOV A,R7      |  |  |

| F0 H   | MOVX @DPTR,A  |  |  |

| F1 H   | ACALL addr11  |  |  |

| F2 H   | MOVX @R0,A    |  |  |

| F3 H   | MOVX @R1,A    |  |  |

| F4 H   | CPL A         |  |  |

| F5 H   | MOV direct,A  |  |  |

| F6 H   | MOV @R0,A     |  |  |

| F7 H   | MOV @R1,A     |  |  |

| F8 H   | MOV R0,A      |  |  |

| F9 H   | MOV R1,A      |  |  |

| FA H   | MOV R2,A      |  |  |

| FB H   | MOV R3,A      |  |  |

| FC H   | MOV R4,A      |  |  |

| FD H   | MOV R5,A      |  |  |

| FE H   | MOV R6,A      |  |  |

| FF H   | MOV R7,A      |  |  |

## Table 33. Instruction Set Summary (Continued)

IA211040524-06 UNCONTROLLED WHEN PRINTED OR COPIED Page 55 of 61 http://www.Innovasic.com Customer Support: 1-888-824-4184

## 9. Errata

The following errata are associated with all versions of the IA80C152. A workaround to the identified problem has been provided where possible.

## 9.1 Errata Summary

Table 36 presents a summary of errata.

## Table 36. Summary of Errata

| Errata<br>No. | Problem                                                                                                                                                                                                                                                                 | Rev.<br>01 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1             | Under certain circumstances, the DMA arbiter will "lock up" in alternate cycles mode. This problem occurs when one DMA channel has finished performing a transfer and another DMA initiates a transfer with the byte Count Register having been set to 0001 by the CPU. | Exists     |

| 2             | Original Intel device has a linear resistor as the pullup on input RESET.                                                                                                                                                                                               | Exists     |

| 3             | DMA can interfere with processing of interrupts of different priority.                                                                                                                                                                                                  | Exists     |

| 4             | Corruption of read data may occur if Port 0 bit written to 0.                                                                                                                                                                                                           | Exists     |

## 9.2 Errata Detail

## Errata No. 1

**Problem:** Under certain circumstances, the DMA arbiter will "lock up" in alternate cycles mode. This problem occurs when one DMA channel has finished performing a transfer and another DMA initiates a transfer with the byte Count Register having been set to 0001 by the CPU.

**Workaround:** Avoid using the alternate cycles DMA mode in conjunction with a byte count of one.

## Errata No. 2

**Problem:** Original Intel device has a linear resistor as the pullup on input RESET.

**Workaround:** None. A non-linear resistor is on the Innovasic device. This may affect operation of certain R/C reset circuits.

IA211040524-06 UNCONTROLLED WHEN PRINTED OR COPIED Page 58 of 61

# **Revision History**

Table 37 presents the sequence of revisions to document IA211040524.

## Table 37. Revision History

| Date            | Revision | Description                                                                                                                                                                                                 | Page(s)       |

|-----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| August 17, 2005 | 1        | Edition released.                                                                                                                                                                                           | NA            |

| July 27, 2007   | 2        | Renamed data sheet for clarity                                                                                                                                                                              | NA            |

| August 31, 2007 | 3        | Updated Errata and RoHS information                                                                                                                                                                         | 57, 58        |

| June 18, 2009   | 4        | Document reformatted to meet publication<br>standards. Added Conventions, Acronyms<br>and Abbreviations, and Summary of Errata<br>table. Added new errata and added range for<br>supply voltage in Table 9. | All           |

| August 17, 2009 | 5        | Added a note regarding recommendations<br>for using the JB/JD version of the device in<br>JA/JC applications. Revised Tables 2, 3 and<br>5.                                                                 | 7, 11, 12, 15 |

| July 29, 2010   | 6        | Errata 3 and 4 added.                                                                                                                                                                                       | 58, 59        |

IA211040524-06 UNCONTROLLED WHEN PRINTED OR COPIED Page 60 of 61