Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 684                                                           |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | -                                                             |

| Number of I/O                  | 104                                                           |

| Number of Gates                | 4000                                                          |

| Voltage - Supply               | 4.5V ~ 5.5V                                                   |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 70°C (TA)                                               |

| Package / Case                 | 144-BQFP                                                      |

| Supplier Device Package        | 144-PQFP (28x28)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a1240a-1pq144c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Microsemi.

ACT 2 Family FPGAs

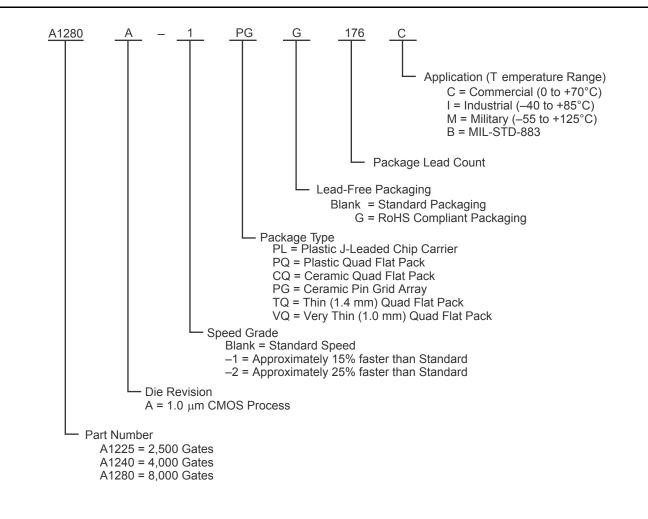

# **Ordering Information**

# **Product Plan**

|                                           | S      | peed Grad | e <sup>1</sup> | Application <sup>1</sup> |          |   |   |  |

|-------------------------------------------|--------|-----------|----------------|--------------------------|----------|---|---|--|

| Device/Package                            | Std.   | -1        | -2             | С                        | I        | М | В |  |

| A1225A Device                             |        |           |                | •                        |          | • |   |  |

| 84-Pin Plastic Leaded Chip Carrier (PL)   | 1      | 1         | ✓              | 1                        | 1        | - | - |  |

| 100-Pin Plastic Quad Flatpack (PQ)        | 1      | 1         | ✓              | 1                        | 1        | - | - |  |

| 100-Pin Very Thin Quad Flatpack (VQ)      | 1      | ~         | ✓              | 1                        | _        | - | _ |  |

| 100-Pin Ceramic Pin Grid Array (PG)       | 1      | 1         | 1              | 1                        | -        | - | _ |  |

| A1240A Device                             |        |           |                |                          |          |   |   |  |

| 84-Pin Plastic Leaded Chip Carrier (PL)   | 1      | ~         | ✓              | 1                        | 1        | - | - |  |

| 132-Pin Ceramic Pin Grid Array (PG)       | 1      | 1         | <i>✓</i>       | 1                        | _        | 1 | 1 |  |

| 144-Pin Plastic Quad Flat Pack (PQ)       | 1      | 1         | ✓              | 1                        | 1        | - | - |  |

| 176-Pin Thin (1.4 mm) Quad Flat Pack (TQ) | 1      | 1         | 1              | 1                        | -        | - | _ |  |

| A1280A Device                             |        |           |                |                          |          |   |   |  |

| 160-Pin Plastic Quad Flatpack (PQ)        | 1      | 1         | ✓              | 1                        | 1        | - | - |  |

| 172-Pin Ceramic Quad Flatpack (CQ)        | 1      | ~         | ✓              | 1                        | _        | 1 | 1 |  |

| 176-Pin Ceramic Pin Grid Array (PG)       | 1      | 1         | 1              | 1                        | _        | 1 | 1 |  |

| 176-Pin Thin (1.4 mm) Quad Flat Pack (TQ) | 1      | 1         | 1              | 1                        | _        | - | - |  |

| Notes:                                    | Availa | hility:   | 1              | Sneed                    | d Grade: | 1 |   |  |

1. Applications: C = Commercial I = Industrial M = Military B = MIL-STD-883 Availability:  $\checkmark = Available$  P = Planned- = Not planned Speed Grade: -1 = Approx. 15% faster than Std.

-2 = Approx. 25% faster than Std.

2. Contact your Microsemi SoC Products Group sales representative for product availability.

# **Device Resources**

| Device | Logic   |       |       | User I/Os |       |       |       |       |      |       |       |       |

|--------|---------|-------|-------|-----------|-------|-------|-------|-------|------|-------|-------|-------|

| Series | Modules | Gates | PG176 | PG132     | PG100 | PQ160 | PQ144 | PQ100 | PL84 | CQ172 | TQ176 | VQ100 |

| A1225A | 451     | 2,500 | -     | -         | 83    | -     | _     | 83    | 72   | -     | -     | 83    |

| A1240A | 684     | 4,000 | -     | 104       | -     | -     | 104   | -     | 72   | -     | 104   | _     |

| A1280A | 1,232   | 8,000 | 140   | _         | -     | 125   | _     | -     | 72   | 140   | 140   | -     |

Contact your local Microsemi SoC Products Group representative for device availability: http://www.microsemi.com/soc/contact/default.aspx.

# 1 – ACT 2 Family Overview

# **General Description**

The ACT 2 family represents Actel's second generation of field programmable gate arrays (FPGAs). The ACT 2 family presents a two-module architecture, consisting of C-modules and S-modules. These modules are optimized for both combinatorial and sequential designs. Based on Actel's patented channeled array architecture, the ACT 2 family provides significant enhancements to gate density and performance while maintaining downward compatibility with the ACT 1 design environment and upward compatibility with the ACT 3 design environment. The devices are implemented in silicon gate, 1.0- $\mu$ m, two-level metal CMOS, and employ Actel's PLICE® antifuse technology. This revolutionary architecture offers gate array design flexibility, high performance, and fast time-to-production with user programming. The ACT 2 family is supported by the Designer and Designer Advantage Systems, which offers automatic pin assignment, validation of electrical and design rules, automatic placement and routing, timing analysis, user programming, and diagnostic probe capabilities. The systems are supported on the following platforms: 386/486<sup>TM</sup> PC, Sun<sup>TM</sup>, and HP<sup>TM</sup> workstations. The systems provide CAE interfaces to the following design environments: Cadence, Viewlogic<sup>®</sup>, Mentor Graphics<sup>®</sup>, and OrCAD<sup>TM</sup>.

# **Operating Conditions**

#### Table 2-1 • Absolute Maximum Ratings<sup>1</sup>

| Symbol           | Parameter                            | Limits            | Units |

|------------------|--------------------------------------|-------------------|-------|

| VCC              | DC supply voltage                    | –0.5 to +7.0      | V     |

| VI               | Input voltage                        | -0.5 to VCC + 0.5 | V     |

| VO               | Output voltage                       | -0.5 to VCC + 0.5 | V     |

| IIO              | I/O source sink current <sup>2</sup> | ±20               | mA    |

| T <sub>STG</sub> | Storage temperature                  | -65 to +150       | °C    |

Notes:

1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Device should not be operated outside the recommended operating conditions.

2. Device inputs are normally high impedance and draw extremely low current. However, when input voltage is greater than VCC + 0.5 V for less than GND –0.5 V, the internal protection diodes will be forward biased and can draw excessive current.

#### Table 2-2 • Recommended Operating Conditions

| Parameter              | Commercial | Industrial | Military    | Units |

|------------------------|------------|------------|-------------|-------|

| Temperature range*     | 0 to +70   | -40 to +85 | –55 to +125 | °C    |

| Power supply tolerance | ±5         | ±10        | ±10         | %VCC  |

Note: \*Ambient temperature  $(T_A)$  is used for commercial and industrial; case temperature  $(T_C)$  is used for military.

#### Table 2-3 • Electrical Specifications

|                                                                                                 |                                                          | Con        | nmercial     | Industrial |           | Military |           |       |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------|--------------|------------|-----------|----------|-----------|-------|

| Symbol                                                                                          | Parameter                                                | Min.       | Max.         | Min.       | Max.      | Min.     | Max.      | Units |

| VOH <sup>1</sup>                                                                                | $(IOH = -10 \text{ mA})^2$                               | 2.4        | -            | _          | _         | _        | -         | V     |

| VOH <sup>1</sup><br>VOL <sup>1</sup><br>VIL<br>VIH<br>Input Transit<br>C <sub>IO</sub> I/O capa | (IOH = –6 mA)                                            | 3.84       | -            | _          | _         | _        | -         | V     |

|                                                                                                 | (IOH = -4 mA)                                            | -          | -            | 3.7        | _         | 3.7      | -         | V     |

| VOL <sup>1</sup>                                                                                | (IOL = 10 mA) <sup>2</sup>                               | -          | 0.5          | _          | -         | _        | -         | V     |

|                                                                                                 | (IOL = 6 mA)                                             | -          | 0.33         | _          | 0.40      | _        | 0.40      | V     |

| VIL                                                                                             |                                                          | -0.3       | 0.8          | -0.3       | 0.8       | -0.3     | 0.8       | V     |

| VIH                                                                                             |                                                          | 2.0        | VCC + 0.3    | 2.0        | VCC + 0.3 | 2.0      | VCC + 0.3 | V     |

| Input Tran                                                                                      | sition Time t <sub>R</sub> , t <sub>F</sub> <sup>2</sup> | -          | 500          | _          | 500       | -        | 500       | ns    |

| C <sub>IO</sub> I/O caj                                                                         | pacitance <sup>2,3</sup>                                 | -          | 10           | _          | 10        | -        | 10        | pF    |

| Standby Current, ICC <sup>4</sup> (typical = 1 mA)                                              |                                                          | -          | 2            | _          | 10        | _        | 20        | mA    |

| Leakage C                                                                                       | Current <sup>5</sup>                                     | -10        | +10          | -10        | +10       | -10      | +10       | μA    |

| ICC(D)                                                                                          | Dynamic VCC supply curren                                | t. See the | Power Dissip | ation see  | ction.    |          | 1         | 1     |

Notes:

1. Only one output tested at a time. VCC = minimum.

2. Not tested, for information only.

3. Includes worst-case PG176 package capacitance. VOUT = 0 V, f = 1 MHz

4. All outputs unloaded. All inputs = VCC or GND, typical ICC = 1 mA. ICC limit includes IPP and ISV during normal operations.

5. VOUT, VIN = VCC or GND.

## **Static Power Component**

Microsemi FPGAs have small static power components that result in lower power dissipation than PALs or PLDs. By integrating multiple PALs/PLDs into one FPGA, an even greater reduction in board-level power dissipation can be achieved.

The power due to standby current is typically a small component of the overall power. Standby power is calculated in Table 2-5 for commercial, worst case conditions.

#### Table 2-5 • Standby Power Calculation

| ICC  | VCC    | Power   |

|------|--------|---------|

| 2 mA | 5.25 V | 10.5 mW |

The static power dissipated by TTL loads depends on the number of outputs driving high or low and the DC load current. Again, this value is typically small. For instance, a 32-bit bus sinking 4 mA at 0.33 V will generate 42 mW with all outputs driving low, and 140 mW with all outputs driving high. The actual dissipation will average somewhere between as I/Os switch states with time.

### **Active Power Component**

Power dissipation in CMOS devices is usually dominated by the active (dynamic) power dissipation. This component is frequency dependent, a function of the logic and the external I/O. Active power dissipation results from charging internal chip capacitances of the interconnect, unprogrammed antifuses, module inputs, and module outputs, plus external capacitance due to PC board traces and load device inputs.

An additional component of the active power dissipation is the totem-pole current in CMOS transistor pairs. The net effect can be associated with an equivalent capacitance that can be combined with frequency and voltage to represent active power dissipation.

EQ 3

### **Equivalent Capacitance**

The power dissipated by a CMOS circuit can be expressed by EQ 3.

Power ( $\mu$ W) = C<sub>EQ</sub> \* VCC<sup>2</sup> \* F

Where:

C<sub>EQ</sub> is the equivalent capacitance expressed in pF.

VCC is the power supply in volts.

F is the switching frequency in MHz.

Equivalent capacitance is calculated by measuring ICC active at a specified frequency and voltage for each circuit component of interest. Measurements have been made over a range of frequencies at a fixed value of VCC. Equivalent capacitance is frequency independent so that the results may be used over a wide range of operating conditions. Equivalent capacitance values are shown in Table 2-6.

Table 2-6 • CEQ Values for Microsemi FPGAs

| Item                                                 | CEQ Value |

|------------------------------------------------------|-----------|

| Modules (C <sub>EQM</sub> )                          | 5.8       |

| Input Buffers (C <sub>EQI</sub> )                    | 12.9      |

| Output Buffers (C <sub>EQO</sub> )                   | 23.8      |

| Routed Array Clock Buffer Loads (C <sub>EQCR</sub> ) | 3.9       |

2-5

To calculate the active power dissipated from the complete design, the switching frequency of each part of the logic must be known. EQ 4 shows a piece-wise linear summation over all components.

Power =VCC<sup>2</sup> \* [(m \* C<sub>EQM</sub> \*  $f_m$ )<sub>modules</sub> + (n \* C<sub>EQI</sub> \*  $f_n$ )<sub>inputs</sub>

+ (p \* ( $C_{EQO}$ +  $C_L$ ) \* fp)outputs

+ 0.5 \* (q1 \* C<sub>EQCR</sub> \* f<sub>q1</sub>)<sub>routed\_Clk1</sub> + (r1 \* f<sub>q1</sub>)<sub>routed\_Clk1</sub>

+ 0.5 \* (q2 \* C<sub>EQCR</sub> \* f<sub>q2</sub>)<sub>routed Clk2</sub> + (r<sub>2</sub> \* f<sub>q2</sub>)<sub>routed Clk2</sub>

#### Where:

m = Number of logic modules switching at fm

n = Number of input buffers switching at fn

p = Number of output buffers switching at f<sub>p</sub>

q1 = Number of clock loads on the first routed array clock

q2 = Number of clock loads on the second routed array clock

r<sub>1</sub> = Fixed capacitance due to first routed array clock

r<sub>2</sub> = Fixed capacitance due to second routed array clock

C<sub>EOM</sub> = Equivalent capacitance of logic modules in pF

C<sub>EOI</sub> = Equivalent capacitance of input buffers in pF

C<sub>FOO</sub> = Equivalent capacitance of output buffers in pF

C<sub>EQCR</sub> = Equivalent capacitance of routed array clock in pF

C<sub>1</sub> = Output lead capacitance in pF

f<sub>m</sub> = Average logic module switching rate in MHz

fn = Average input buffer switching rate in MHz

fp = Average output buffer switching rate in MHz

$f_{q1}$  = Average first routed array clock rate in MHz

f<sub>g2</sub> = Average second routed array clock rate in MHz

#### Table 2-7 • Fixed Capacitance Values for Microsemi FPGAs

| Device Type | r1, routed_Clk1 | r2, routed_Clk2 |

|-------------|-----------------|-----------------|

| A1225A      | 106             | 106.0           |

| A1240A      | 134             | 134.2           |

| A1280A      | 168             | 167.8           |

EQ 4

# **Determining Average Switching Frequency**

To determine the switching frequency for a design, you must have a detailed understanding of the data input values to the circuit. The following guidelines are meant to represent worst-case scenarios so that they can be generally used to predict the upper limits of power dissipation. These guidelines are given in Table 2-8.

| Table 2-8 • Guidelines for Predicting Power Dissipation | or Predicting Power Dissipation | Table 2-8 • Guidelines for |

|---------------------------------------------------------|---------------------------------|----------------------------|

|---------------------------------------------------------|---------------------------------|----------------------------|

| Data                                                      | Value                     |

|-----------------------------------------------------------|---------------------------|

| Logic Modules (m)                                         | 80% of modules            |

| Inputs switching (n)                                      | # inputs/4                |

| Outputs switching (p)                                     | # output/4                |

| First routed array clock loads (q1)                       | 40% of sequential modules |

| Second routed array clock loads (q2)                      | 40% of sequential modules |

| Load capacitance (CL)                                     | 35 pF                     |

| Average logic module switching rate (f <sub>m</sub> )     | F/10                      |

| Average input switching rate (f <sub>n</sub> )            | F/5                       |

| Average output switching rate (fp)                        | F/10                      |

| Average first routed array clock rate (f <sub>q1</sub> )  | F                         |

| Average second routed array clock rate (f <sub>q2</sub> ) | F/2                       |

### A1225A Timing Characteristics (continued)

#### Table 2-13 • A1225A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

| I/O Mod            | ule Input Propagation Delays      |                  | -2 S | peed  | –1 S | peed  | Std. | Units |    |

|--------------------|-----------------------------------|------------------|------|-------|------|-------|------|-------|----|

| Parame             | ter/Description                   |                  | Min. | Max.  | Min. | Max.  | Min. | Max.  |    |

| t <sub>INYH</sub>  | Pad to Y High                     |                  |      | 2.9   |      | 3.3   |      | 3.8   | ns |

| t <sub>INYL</sub>  | Pad to Y Low                      |                  |      | 2.6   |      | 3.0   |      | 3.5   | ns |

| t <sub>INGH</sub>  | G to Y High                       |                  |      | 5.0   |      | 5.7   |      | 6.6   | ns |

| t <sub>INGL</sub>  | G to Y Low                        |                  |      | 4.7   |      | 5.4   |      | 6.3   | ns |

| Input M            | odule Predicted Input Routing Del | ays <sup>*</sup> |      |       |      |       |      |       |    |

| t <sub>IRD1</sub>  | FO = 1 Routing Delay              |                  |      | 4.1   |      | 4.6   |      | 5.4   | ns |

| t <sub>IRD2</sub>  | FO = 2 Routing Delay              |                  |      | 4.6   |      | 5.2   |      | 6.1   | ns |

| t <sub>IRD3</sub>  | FO = 3 Routing Delay              |                  |      | 5.3   |      | 6.0   |      | 7.1   | ns |

| t <sub>IRD4</sub>  | FO = 4 Routing Delay              |                  |      | 5.7   |      | 6.4   |      | 7.6   | ns |

| t <sub>IRD8</sub>  | FO = 8 Routing Delay              |                  |      | 7.4   |      | 8.3   |      | 9.8   | ns |

| Global (           | Clock Network                     |                  |      |       |      |       | -    | -     |    |

| t <sub>скн</sub>   | Input Low to High                 | FO = 32          |      | 10.2  |      | 11.0  |      | 12.8  | ns |

|                    |                                   | FO = 256         |      | 11.8  |      | 13.0  |      | 15.7  |    |

| t <sub>CKL</sub>   | Input High to Low                 | FO = 32          |      | 10.2  |      | 11.0  |      | 12.8  | ns |

|                    |                                   | FO = 256         |      | 12.0  |      | 13.2  |      | 15.9  |    |

| t <sub>PWH</sub>   | Minimum Pulse Width High          | FO = 32          | 3.4  |       | 4.1  |       | 4.5  |       | ns |

|                    |                                   | FO = 256         | 3.8  |       | 4.5  |       | 5.0  |       |    |

| t <sub>PWL</sub>   | Minimum Pulse Width Low           | FO = 32          | 3.4  |       | 4.1  |       | 4.5  |       | ns |

|                    |                                   | FO = 256         | 3.8  |       | 4.5  |       | 5.0  |       |    |

| t <sub>CKSW</sub>  | Maximum Skew                      | FO = 32          |      | 0.7   |      | 0.7   |      | 0.7   | ns |

|                    |                                   | FO = 256         |      | 3.5   |      | 3.5   |      | 3.5   |    |

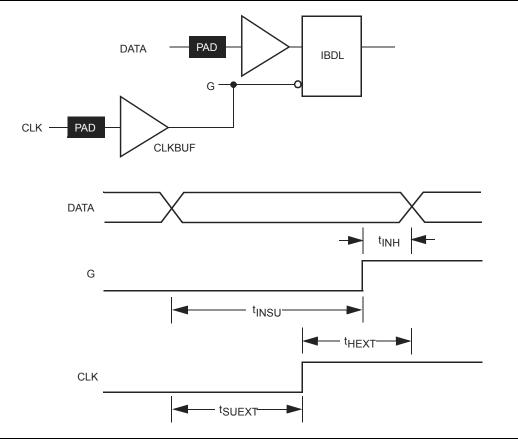

| t <sub>SUEXT</sub> | Input Latch External Setup        | FO = 32          | 0.0  |       | 0.0  |       | 0.0  |       | ns |

|                    |                                   | FO = 256         | 0.0  |       | 0.0  |       | 0.0  |       |    |

| t <sub>HEXT</sub>  | Input Latch External Hold         | FO = 32          | 7.0  |       | 7.0  |       | 7.0  |       | ns |

|                    |                                   | FO = 256         | 11.2 |       | 11.2 |       | 11.2 |       |    |

| t <sub>P</sub>     | Minimum Period                    | FO = 32          | 7.7  |       | 8.3  |       | 9.1  |       | ns |

|                    |                                   | FO = 256         | 8.1  |       | 8.8  |       | 10.0 |       |    |

| f <sub>MAX</sub>   | Maximum Frequency                 | FO = 32          |      | 130.0 |      | 120.0 |      | 110.0 | ns |

|                    |                                   | FO = 256         |      | 125.0 |      | 115.0 |      | 100.0 | ]  |

Note: \*These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

### A1240A Timing Characteristics (continued)

Table 2-16 • A1240A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

| I/O Module Input Propagation Delays Parameter/Description |                                   | -2 Speed         |      | -1 Speed |      | Std. Speed |      | Units |    |

|-----------------------------------------------------------|-----------------------------------|------------------|------|----------|------|------------|------|-------|----|

|                                                           |                                   | Min.             | Max. | Min.     | Max. | Min.       | Max. | 1     |    |

| t <sub>INYH</sub>                                         | Pad to Y High                     |                  |      | 2.9      |      | 3.3        |      | 3.8   | ns |

| t <sub>INYL</sub>                                         | Pad to Y Low                      |                  |      | 2.6      |      | 3.0        |      | 3.5   | ns |

| t <sub>INGH</sub>                                         | G to Y High                       |                  |      | 5.0      |      | 5.7        |      | 6.6   | ns |

| t <sub>INGL</sub>                                         | G to Y Low                        |                  |      | 4.7      |      | 5.4        |      | 6.3   | ns |

| Input Mo                                                  | odule Predicted Input Routing Del | ays <sup>*</sup> |      |          |      |            | -    |       |    |

| t <sub>IRD1</sub>                                         | FO = 1 Routing Delay              |                  |      | 4.2      |      | 4.8        |      | 5.6   | ns |

| t <sub>IRD2</sub>                                         | FO = 2 Routing Delay              |                  |      | 4.8      |      | 5.4        |      | 6.4   | ns |

| t <sub>IRD3</sub>                                         | FO = 3 Routing Delay              |                  |      | 5.4      |      | 6.1        |      | 7.2   | ns |

| t <sub>IRD4</sub>                                         | FO = 4 Routing Delay              |                  |      | 5.9      |      | 6.7        |      | 7.9   | ns |

| t <sub>IRD8</sub>                                         | FO = 8 Routing Delay              |                  |      | 7.9      |      | 8.9        |      | 10.5  | ns |

| Global (                                                  | Clock Network                     |                  | -    |          |      |            | -    |       |    |

| t <sub>СКН</sub>                                          | Input Low to High                 | FO = 32          |      | 10.2     |      | 11.0       |      | 12.8  | ns |

|                                                           |                                   | FO = 256         |      | 11.8     |      | 13.0       |      | 15.7  | 1  |

| t <sub>CKL</sub>                                          | Input High to Low                 | FO = 32          |      | 10.2     |      | 11.0       |      | 12.8  | ns |

|                                                           |                                   | FO = 256         |      | 12.0     |      | 13.2       |      | 15.9  |    |

| t <sub>PWH</sub>                                          | Minimum Pulse Width High          | FO = 32          | 3.8  |          | 4.5  |            | 5.5  |       | ns |

|                                                           |                                   | FO = 256         | 4.1  |          | 5.0  |            | 5.8  |       |    |

| t <sub>PWL</sub>                                          | Minimum Pulse Width Low           | FO = 32          | 3.8  |          | 4.5  |            | 5.5  |       | ns |

|                                                           |                                   | FO = 256         | 4.1  |          | 5.0  |            | 5.8  |       |    |

| t <sub>CKSW</sub>                                         | Maximum Skew                      | FO = 32          |      | 0.5      |      | 0.5        |      | 0.5   | ns |

|                                                           |                                   | FO = 256         |      | 2.5      |      | 2.5        |      | 2.5   |    |

| t <sub>SUEXT</sub>                                        | Input Latch External Setup        | FO = 32          | 0.0  |          | 0.0  |            | 0.0  |       | ns |

|                                                           |                                   | FO = 256         | 0.0  |          | 0.0  |            | 0.0  |       |    |

| t <sub>HEXT</sub>                                         | Input Latch External Hold         | FO = 32          | 7.0  |          | 7.0  |            | 7.0  |       | ns |

|                                                           |                                   | FO = 256         | 11.2 |          | 11.2 |            | 11.2 |       |    |

| t <sub>P</sub>                                            | Minimum Period                    | FO = 32          | 8.1  |          | 9.1  |            | 11.1 |       | ns |

|                                                           |                                   | FO = 256         | 8.8  |          | 10.0 |            | 11.7 |       | 1  |

| f <sub>MAX</sub>                                          | Maximum Frequency                 | FO = 32          | 1    | 125.0    |      | 110.0      |      | 90.0  | ns |

|                                                           |                                   | FO = 256         |      | 115.0    |      | 100.0      |      | 85.0  | 1  |

Note: \*These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

| TTL Output Module Timing <sup>1</sup><br>Parameter/Description |                                   | –2 S | -2 Speed |      | -1 Speed |      | Std. Speed |       |

|----------------------------------------------------------------|-----------------------------------|------|----------|------|----------|------|------------|-------|

|                                                                |                                   | Min. | Max.     | Min. | Max.     | Min. | Max.       |       |

| t <sub>DLH</sub>                                               | Data to Pad High                  |      | 8.1      |      | 9.0      |      | 10.6       | ns    |

| t <sub>DHL</sub>                                               | Data to Pad Low                   |      | 10.2     |      | 11.4     |      | 13.4       | ns    |

| t <sub>ENZH</sub>                                              | Enable Pad Z to High              |      | 9.0      |      | 10.0     |      | 11.8       | ns    |

| t <sub>ENZL</sub>                                              | Enable Pad Z to Low               |      | 11.8     |      | 13.2     |      | 15.5       | ns    |

| t <sub>ENHZ</sub>                                              | Enable Pad High to Z              |      | 7.1      |      | 8.0      |      | 9.4        | ns    |

| t <sub>ENLZ</sub>                                              | Enable Pad Low to Z               |      | 8.4      |      | 9.5      |      | 11.1       | ns    |

| t <sub>GLH</sub>                                               | G to Pad High                     |      | 9.0      |      | 10.2     |      | 11.9       | ns    |

| t <sub>GHL</sub>                                               | G to Pad Low                      |      | 11.3     |      | 12.7     |      | 14.9       | ns    |

| d <sub>TLH</sub>                                               | Delta Low to High                 |      | 0.07     |      | 0.08     |      | 0.09       | ns/pF |

| d <sub>THL</sub>                                               | Delta High to Low                 |      | 0.12     |      | 0.13     |      | 0.16       | ns/pF |

| CMOS                                                           | Output Module Timing <sup>1</sup> | ·    |          |      |          |      |            |       |

| t <sub>DLH</sub>                                               | Data to Pad High                  |      | 10.3     |      | 11.5     |      | 13.5       | ns    |

| t <sub>DHL</sub>                                               | Data to Pad Low                   |      | 8.5      |      | 9.6      |      | 11.2       | ns    |

| t <sub>ENZH</sub>                                              | Enable Pad Z to High              |      | 9.0      |      | 10.0     |      | 11.8       | ns    |

| t <sub>ENZL</sub>                                              | Enable Pad Z to Low               |      | 11.8     |      | 13.2     |      | 15.5       | ns    |

| t <sub>ENHZ</sub>                                              | Enable Pad High to Z              |      | 7.1      |      | 8.0      |      | 9.4        | ns    |

| t <sub>ENLZ</sub>                                              | Enable Pad Low to Z               |      | 8.4      |      | 9.5      |      | 11.1       | ns    |

| t <sub>GLH</sub>                                               | G to Pad High                     |      | 9.0      |      | 10.2     |      | 11.9       | ns    |

| t <sub>GHL</sub>                                               | G to Pad Low                      |      | 11.3     |      | 12.7     |      | 14.9       | ns    |

| d <sub>TLH</sub>                                               | Delta Low to High                 |      | 0.12     |      | 0.13     |      | 0.16       | ns/pF |

| d <sub>THL</sub>                                               | Delta High to Low                 |      | 0.09     |      | 0.10     |      | 0.12       | ns/pF |

#### Table 2-20 • A1280A Worst-Case Commercial Conditions, VCC = 4.75 V, $T_J = 70^{\circ}C$

Notes:

1. Delays based on 50 pF loading.

2. SSO information can be found at www.microsemi.com/soc/techdocs/appnotes/board\_consideration.aspx.

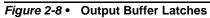

# PQ100

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

|            | PQ144           | PQ144      |                 |  |  |

|------------|-----------------|------------|-----------------|--|--|

| Pin Number | A1240A Function | Pin Number | A1240A Function |  |  |

| 2          | MODE            | 89         | VCC             |  |  |

| 9          | GND             | 90         | VCC             |  |  |

| 10         | GND             | 91         | VCC             |  |  |

| 11         | GND             | 92         | VCC             |  |  |

| 18         | VCC             | 93         | VCC             |  |  |

| 19         | VCC             | 100        | GND             |  |  |

| 20         | VCC             | 101        | GND             |  |  |

| 21         | VCC             | 102        | GND             |  |  |

| 28         | GND             | 110        | SDI, I/O        |  |  |

| 29         | GND             | 116        | GND             |  |  |

| 30         | GND             | 117        | GND             |  |  |

| 44         | GND             | 118        | GND             |  |  |

| 45         | GND             | 123        | PRA, I/O        |  |  |

| 46         | GND             | 125        | CLKA, I/O       |  |  |

| 54         | VCC             | 126        | VCC             |  |  |

| 55         | VCC             | 127        | VCC             |  |  |

| 56         | VCC             | 128        | VCC             |  |  |

| 64         | GND             | 130        | CLKB, I/O       |  |  |

| 65         | GND             | 132        | PRB, I/O        |  |  |

| 71         | SDO             | 136        | GND             |  |  |

| 79         | GND             | 137        | GND             |  |  |

| 80         | GND             | 138        | GND             |  |  |

| 81         | GND             | 144        | DCLK, I/O       |  |  |

| 88         | GND             |            |                 |  |  |

Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

|            | TQ176           |                 | TQ176      |                 |                 |  |  |

|------------|-----------------|-----------------|------------|-----------------|-----------------|--|--|

| Pin Number | A1240A Function | A1280A Function | Pin Number | A1240A Function | A1280A Function |  |  |

| 1          | GND             | GND             | 82         | NC              | VCC             |  |  |

| 2          | MODE            | MODE            | 86         | NC              | I/O             |  |  |

| 8          | NC              | NC              | 87         | SDO             | SDO             |  |  |

| 10         | NC              | I/O             | 89         | GND             | GND             |  |  |

| 11         | NC              | I/O             | 96         | NC              | I/O             |  |  |

| 13         | NC              | VCC             | 97         | NC              | I/O             |  |  |

| 18         | GND             | GND             | 101        | NC              | NC              |  |  |

| 19         | NC              | I/O             | 103        | NC              | I/O             |  |  |

| 20         | NC              | I/O             | 106        | GND             | GND             |  |  |

| 22         | NC              | I/O             | 107        | NC              | I/O             |  |  |

| 23         | GND             | GND             | 108        | NC              | I/O             |  |  |

| 24         | NC              | VCC             | 109        | GND             | GND             |  |  |

| 25         | VCC             | VCC             | 110        | VCC             | VCC             |  |  |

| 26         | NC              | I/O             | 111        | GND             | GND             |  |  |

| 27         | NC              | I/O             | 112        | VCC             | VCC             |  |  |

| 28         | VCC             | VCC             | 113        | VCC             | VCC             |  |  |

| 29         | NC              | I/O             | 114        | NC              | I/O             |  |  |

| 33         | NC              | NC              | 115        | NC              | I/O             |  |  |

| 37         | NC              | I/O             | 116        | NC              | VCC             |  |  |

| 38         | NC              | NC              | 121        | NC              | NC              |  |  |

| 45         | GND             | GND             | 124        | NC              | I/O             |  |  |

| 52         | NC              | VCC             | 125        | NC              | I/O             |  |  |

| 54         | NC              | I/O             | 126        | NC              | NC              |  |  |

| 55         | NC              | I/O             | 133        | GND             | GND             |  |  |

| 57         | NC              | NC              | 135        | SDI, I/O        | SDI, I/O        |  |  |

| 61         | NC              | I/O             | 136        | NC              | I/O             |  |  |

| 64         | NC              | I/O             | 140        | NC              | VCC             |  |  |

| 66         | NC              | I/O             | 143        | NC              | I/O             |  |  |

| 67         | GND             | GND             | 144        | NC              | I/O             |  |  |

| 68         | VCC             | VCC             | 145        | NC              | NC              |  |  |

| 74         | NC              | I/O             | 147        | NC              | I/O             |  |  |

| 77         | NC              | NC              | 151        | NC              | I/O             |  |  |

| 78         | NC              | I/O             | 152        | PRA, I/O        | PRA, I/O        |  |  |

| 80         | NC              | I/O             | 154        | CLKA, I/O       | CLKA, I/O       |  |  |

| TQ176      |                 |                 |  |  |  |  |

|------------|-----------------|-----------------|--|--|--|--|

| Pin Number | A1240A Function | A1280A Function |  |  |  |  |

| 155        | VCC             | VCC             |  |  |  |  |

| 156        | GND             | GND             |  |  |  |  |

| 158        | CLKB, I/O       | CLKB, I/O       |  |  |  |  |

| 160        | PRB, I/O        | PRB, I/O        |  |  |  |  |

| 161        | NC              | I/O             |  |  |  |  |

| 165        | NC              | NC              |  |  |  |  |

| 166        | NC              | I/O             |  |  |  |  |

| 168        | NC              | I/O             |  |  |  |  |

| 170        | NC              | VCC             |  |  |  |  |

| 173        | NC              | I/O             |  |  |  |  |

| 175        | DCLK, I/O       | DCLK, I/O       |  |  |  |  |

Notes:

- 1. NC denotes no connection.

- 2. All unlisted pin numbers are user I/Os.

- 3. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

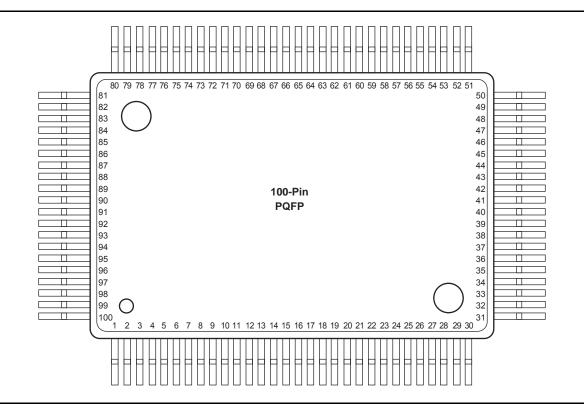

# PG100

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

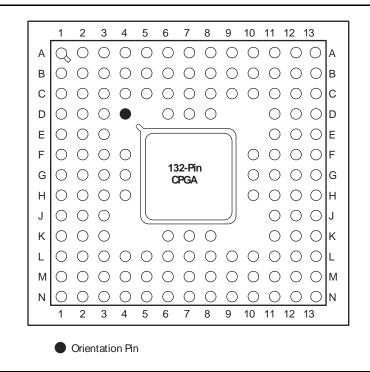

# PG132

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

# 4 – Datasheet Information

# **List of Changes**

The following table lists critical changes that were made in each version of the datasheet.

| Revision                      | Changes                                                                                                                                                                                                  | Page |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 8<br>(January 2012)  | The ACT 2 datasheet was formatted newly in the style used for current datasheets. The same information is present (other than noted in the list of changes for this revision) but divided into chapters. | N/A  |

|                               | Package names used in Table 1 • ACT 2 Product Family Profile and throughout the document were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                        |      |

|                               | The description for SDO pins had earlier been removed from the datasheet and has now been included again, in the "Pin Descriptions" section (SAR 35819).                                                 | 2-21 |

|                               | SDO pin numbers had earlier been removed from package pin assignment tables in the datasheet, and have now been restored to the pin tables (SAR 35819).                                                  | 3-2  |

| Revision 7<br>(June 2006)     | The "Ordering Information" section was revised to include RoHS information.                                                                                                                              | II   |

| Revision 6<br>(December 2000) | In the "PG176" package, pin A3 was incorrectly assigned as CLKA, I/O. A3 is a user I/O. Pin A9 is CLKA, I/O.                                                                                             | 3-21 |

Datasheet Information

# **Datasheet Categories**

### Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

### Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

### Production

This version contains information that is considered to be final.

### **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.