Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 684                                                           |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | -                                                             |

| Number of I/O                  | 104                                                           |

| Number of Gates                | 4000                                                          |

| Voltage - Supply               | 4.5V ~ 5.5V                                                   |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 70°C (TA)                                               |

| Package / Case                 | 144-BQFP                                                      |

| Supplier Device Package        | 144-PQFP (28x28)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a1240a-pqg144c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Product Plan**

|                                           | s    | Application <sup>1</sup> |    |   |   |   |   |

|-------------------------------------------|------|--------------------------|----|---|---|---|---|

| Device/Package                            | Std. | -1                       | -2 | С | I | М | В |

| A1225A Device                             | •    | •                        | •  |   | • | • |   |

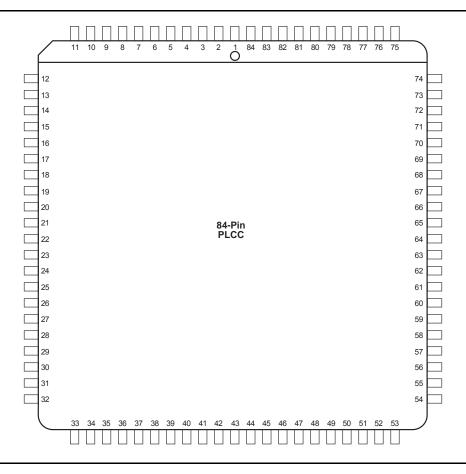

| 84-Pin Plastic Leaded Chip Carrier (PL)   | ✓    | 1                        | 1  | 1 | 1 | _ | _ |

| 100-Pin Plastic Quad Flatpack (PQ)        | 1    | 1                        | 1  | 1 | 1 | _ | _ |

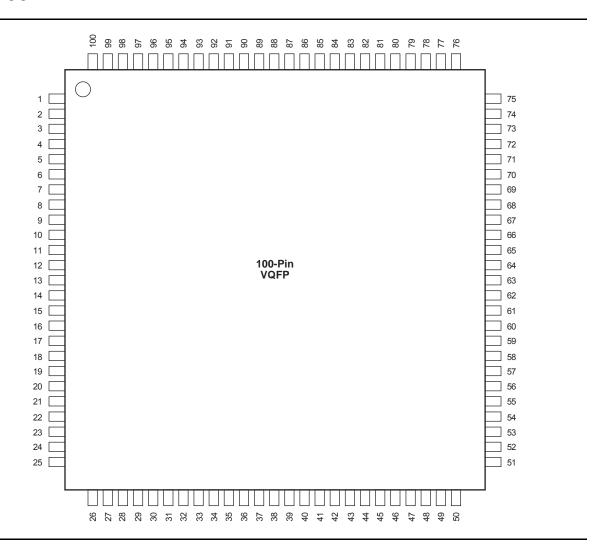

| 100-Pin Very Thin Quad Flatpack (VQ)      | 1    | ✓                        | 1  | 1 | _ | _ | _ |

| 100-Pin Ceramic Pin Grid Array (PG)       | 1    | 1                        | 1  | 1 | _ | _ | _ |

| A1240A Device                             | I    |                          |    |   | ı | ı |   |

| 84-Pin Plastic Leaded Chip Carrier (PL)   | ✓    | 1                        | ✓  | 1 | 1 | _ | _ |

| 132-Pin Ceramic Pin Grid Array (PG)       | 1    | 1                        | 1  | 1 | _ | 1 | ✓ |

| 144-Pin Plastic Quad Flat Pack (PQ)       | 1    | 1                        | 1  | 1 | 1 | _ | _ |

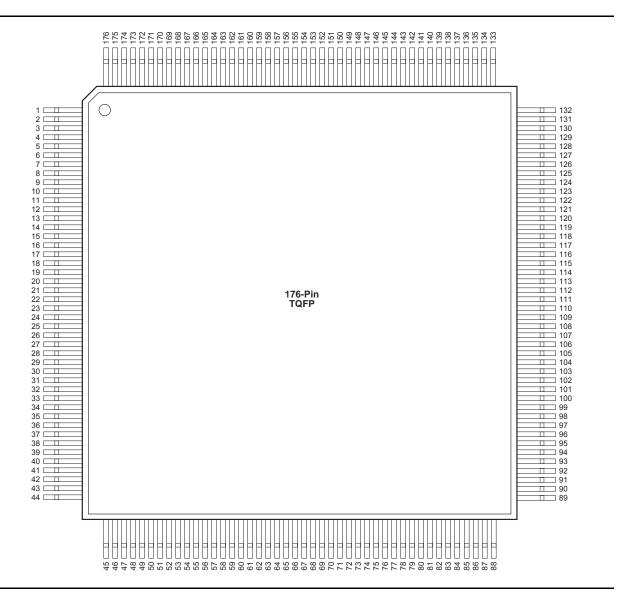

| 176-Pin Thin (1.4 mm) Quad Flat Pack (TQ) | 1    | 1                        | 1  | 1 | _ | _ | _ |

| A1280A Device                             | I    |                          |    |   | ı | ı |   |

| 160-Pin Plastic Quad Flatpack (PQ)        | ✓    | 1                        | ✓  | 1 | 1 | _ | _ |

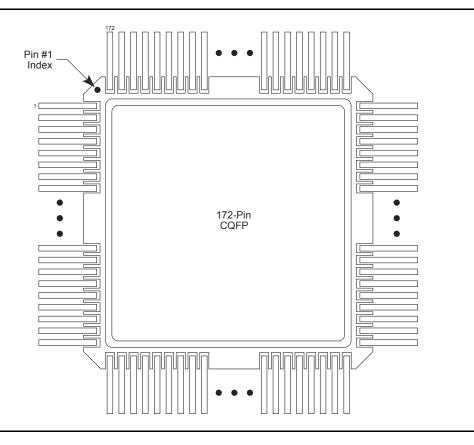

| 172-Pin Ceramic Quad Flatpack (CQ)        | 1    | ✓                        | ✓  | ✓ | _ | 1 | ✓ |

| 176-Pin Ceramic Pin Grid Array (PG)       | /    | ✓                        | ✓  | 1 | _ | 1 | ✓ |

| 176-Pin Thin (1.4 mm) Quad Flat Pack (TQ) | 1    | 1                        | 1  | 1 | _ | _ | _ |

| • • •                                     |      | •                        |    | • | _ | - | _ |

Notes:

Applications:

C = Commercial

I = Industrial

M = Military

B = MIL-STD-883

Availability: ✓ = Available P = Planned – = Not planned

Speed Grade:

-1 = Approx. 15% faster than Std. -2 = Approx. 25% faster than Std.

2. Contact your Microsemi SoC Products Group sales representative for product availability.

## **Device Resources**

| Device | Logic   |       |       | User I/Os |       |       |       |       |      |       |       |       |

|--------|---------|-------|-------|-----------|-------|-------|-------|-------|------|-------|-------|-------|

| Series | Modules | Gates | PG176 | PG132     | PG100 | PQ160 | PQ144 | PQ100 | PL84 | CQ172 | TQ176 | VQ100 |

| A1225A | 451     | 2,500 | _     | _         | 83    | _     | _     | 83    | 72   | _     | _     | 83    |

| A1240A | 684     | 4,000 | _     | 104       | _     | _     | 104   | _     | 72   | _     | 104   | _     |

| A1280A | 1,232   | 8,000 | 140   | -         | _     | 125   | ı     | -     | 72   | 140   | 140   | _     |

Contact your local Microsemi SoC Products Group representative for device availability: http://www.microsemi.com/soc/contact/default.aspx.

Revision 8 III

## **Package Thermal Characteristics**

The device junction to case thermal characteristic is  $\theta$ jc, and the junction to ambient air characteristic is  $\theta$ ja. The thermal characteristics for  $\theta$ ja are shown with two different air flow rates.

Maximum junction temperature is 150°C.

A sample calculation of the absolute maximum power dissipation allowed for a PQ160 package at commercial temperature and still air is as follows:

$$\frac{\text{Max. junction temp. (°C)} - \text{Max. ambient temp. (°C)}}{\theta_{\text{ia}}\text{°C/W}} = \frac{150\text{°C} - 70\text{°C}}{33\text{°C/W}} = 2.4 \text{ W}$$

EQ 1

Table 2-4 • Package Thermal Characteristics

| Package Type*                      | Pin Count | $\theta$ jc | θ <sub>ja</sub><br>Still Air | $_{ m ja}^{ m 	heta_{ m ja}}$ 300 ft./min. | Units |

|------------------------------------|-----------|-------------|------------------------------|--------------------------------------------|-------|

| Ceramic Pin Grid Array             | 100       | 5           | 35                           | 17                                         | °C/W  |

|                                    | 132       | 5           | 30                           | 15                                         | °C/W  |

|                                    | 176       | 8           | 23                           | 12                                         | °C/W  |

| Ceramic Quad Flatpack              | 172       | 8           | 25                           | 15                                         | °C/W  |

| Plastic Quad Flatpack <sup>1</sup> | 100       | 13          | 48                           | 40                                         | °C/W  |

|                                    | 144       | 15          | 40                           | 32                                         | °C/W  |

|                                    | 160       | 15          | 38                           | 30                                         | °C/W  |

| Plastic Leaded Chip Carrier        | 84        | 12          | 37                           | 28                                         | °C/W  |

| Very Thin Quad Flatpack            | 100       | 12          | 43                           | 35                                         | °C/W  |

| Thin Quad Flatpack                 | 176       | 15          | 32                           | 25                                         | °C/W  |

Notes: (Maximum Power in Still Air)

- Maximum power dissipation values for PQFP packages are 1.9 W (PQ100), 2.3 W (PQ144), and 2.4 W (PQ160).

- 2. Maximum power dissipation for PLCC packages is 2.7 W.

- 3. Maximum power dissipation for VQFP packages is 2.3 W.

- 4. Maximum power dissipation for TQFP packages is 3.1 W.

## **Power Dissipation**

P = [ICC standby + ICCactive] \* VCC + IOL \* VOL \* N + IOH\* (VCC - VOH) \* M

EQ2

where:

ICC standby is the current flowing when no inputs or outputs are changing

ICCactive is the current flowing due to CMOS switching.

IOL and IOH are TTL sink/source currents.

VOL and VOH are TTL level output voltages.

N is the number of outputs driving TTL loads to VOL.

M is the number of outputs driving TTL loads to VOH.

An accurate determination of N and M is problematical because their values depend on the family type, design details, and on the system I/O. The power can be divided into two components: static and active.

## **Determining Average Switching Frequency**

To determine the switching frequency for a design, you must have a detailed understanding of the data input values to the circuit. The following guidelines are meant to represent worst-case scenarios so that they can be generally used to predict the upper limits of power dissipation. These guidelines are given in Table 2-8.

Table 2-8 • Guidelines for Predicting Power Dissipation

| Data                                                      | Value                     |

|-----------------------------------------------------------|---------------------------|

| Logic Modules (m)                                         | 80% of modules            |

| Inputs switching (n)                                      | # inputs/4                |

| Outputs switching (p)                                     | # output/4                |

| First routed array clock loads (q1)                       | 40% of sequential modules |

| Second routed array clock loads (q2)                      | 40% of sequential modules |

| Load capacitance (C <sub>L</sub> )                        | 35 pF                     |

| Average logic module switching rate (f <sub>m</sub> )     | F/10                      |

| Average input switching rate (f <sub>n</sub> )            | F/5                       |

| Average output switching rate (f <sub>p</sub> )           | F/10                      |

| Average first routed array clock rate (f <sub>q1</sub> )  | F                         |

| Average second routed array clock rate (f <sub>q2</sub> ) | F/2                       |

2-6 Revision 8

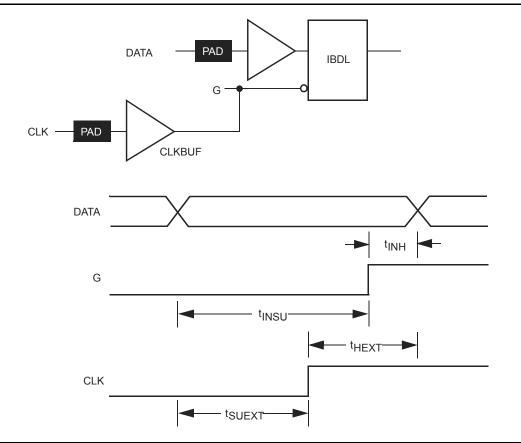

Figure 2-7 • Input Buffer Latches

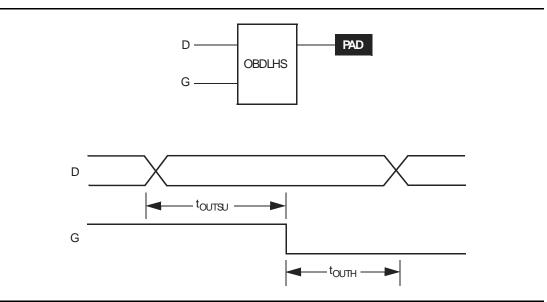

Figure 2-8 • Output Buffer Latches

2-10 Revision 8

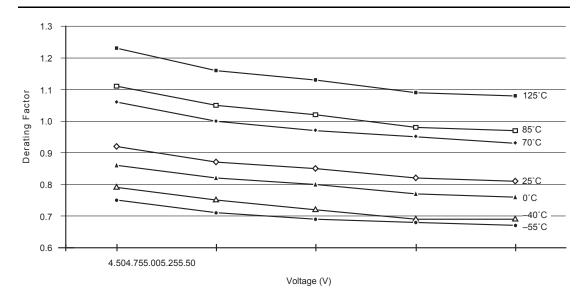

## **Timing Derating Factor (Temperature and Voltage)**

Table 2-9 • Timing Derating Factor (Temperature and Voltage)

| (Commercial Minimum/Maximum Specification) x | Indus | strial | Military |      |

|----------------------------------------------|-------|--------|----------|------|

|                                              | Min.  | Max.   | Min.     | Max. |

|                                              | 0.69  | 1.11   | 0.67     | 1.23 |

Table 2-10 • Timing Derating Factor for Designs at Typical Temperature ( $T_J = 25^{\circ}C$ ) and Voltage (5.0 V)

| (Commercial Maximum Specification) x | 0.85 |

|--------------------------------------|------|

|--------------------------------------|------|

Table 2-11 • Temperature and Voltage Derating Factors (normalized to Worst-Case Commercial, TJ = 4.75 V, 70°C)

|      | <b>-55</b> | -40  | 0    | 25   | 70   | 85   | 125  |

|------|------------|------|------|------|------|------|------|

| 4.50 | 0.75       | 0.79 | 0.86 | 0.92 | 1.06 | 1.11 | 1.23 |

| 4.75 | 0.71       | 0.75 | 0.82 | 0.87 | 1.00 | 1.05 | 1.13 |

| 5.00 | 0.69       | 0.72 | 0.80 | 0.85 | 0.97 | 1.02 | 1.13 |

| 5.25 | 0.68       | 0.69 | 0.77 | 0.82 | 0.95 | 0.98 | 1.09 |

| 5.50 | 0.67       | 0.69 | 0.76 | 0.81 | 0.93 | 0.97 | 1.08 |

Note: This derating factor applies to all routing and propagation delays.

Figure 2-9 • Junction Temperature and Voltage Derating Curves (normalized to Worst-Case Commercial, T<sub>J</sub> = 4.75 V, 70°C)

## A1225A Timing Characteristics (continued)

Table 2-13 • A1225A Worst-Case Commercial Conditions, VCC = 4.75 V,  $T_J = 70^{\circ}$ C

| I/O Mod                | ule Input Propagation Delays      |                  | -2 S | peed  | -1 S | peed  | Std. Speed |       | Units |

|------------------------|-----------------------------------|------------------|------|-------|------|-------|------------|-------|-------|

| Paramet                | ter/Description                   |                  | Min. | Max.  | Min. | Max.  | Min.       | Max.  |       |

| t <sub>INYH</sub>      | Pad to Y High                     |                  |      | 2.9   |      | 3.3   |            | 3.8   | ns    |

| t <sub>INYL</sub>      | Pad to Y Low                      |                  |      | 2.6   |      | 3.0   |            | 3.5   | ns    |

| t <sub>INGH</sub>      | G to Y High                       |                  |      | 5.0   |      | 5.7   |            | 6.6   | ns    |

| t <sub>INGL</sub>      | G to Y Low                        |                  |      | 4.7   |      | 5.4   |            | 6.3   | ns    |

| Input Mo               | odule Predicted Input Routing Del | ays <sup>*</sup> |      |       |      |       |            |       |       |

| t <sub>IRD1</sub>      | FO = 1 Routing Delay              |                  |      | 4.1   |      | 4.6   |            | 5.4   | ns    |

| t <sub>IRD2</sub>      | FO = 2 Routing Delay              |                  |      | 4.6   |      | 5.2   |            | 6.1   | ns    |

| t <sub>IRD3</sub>      | FO = 3 Routing Delay              |                  |      | 5.3   |      | 6.0   |            | 7.1   | ns    |

| t <sub>IRD4</sub>      | FO = 4 Routing Delay              |                  |      | 5.7   |      | 6.4   |            | 7.6   | ns    |

| t <sub>IRD8</sub>      | FO = 8 Routing Delay              |                  |      | 7.4   |      | 8.3   |            | 9.8   | ns    |

| Global (               | Clock Network                     |                  |      |       |      |       |            |       |       |

| t <sub>CKH</sub>       | Input Low to High                 | FO = 32          |      | 10.2  |      | 11.0  |            | 12.8  | ns    |

|                        |                                   | FO = 256         |      | 11.8  |      | 13.0  |            | 15.7  |       |

| t <sub>CKL</sub> Input | Input High to Low                 | FO = 32          |      | 10.2  |      | 11.0  |            | 12.8  | ns    |

|                        |                                   | FO = 256         |      | 12.0  |      | 13.2  |            | 15.9  |       |

| t <sub>PWH</sub>       | Minimum Pulse Width High          | FO = 32          | 3.4  |       | 4.1  |       | 4.5        |       | ns    |

|                        |                                   | FO = 256         | 3.8  |       | 4.5  |       | 5.0        |       |       |

| t <sub>PWL</sub>       | Minimum Pulse Width Low           | FO = 32          | 3.4  |       | 4.1  |       | 4.5        |       | ns    |

|                        |                                   | FO = 256         | 3.8  |       | 4.5  |       | 5.0        |       |       |

| t <sub>CKSW</sub>      | Maximum Skew                      | FO = 32          |      | 0.7   |      | 0.7   |            | 0.7   | ns    |

|                        |                                   | FO = 256         |      | 3.5   |      | 3.5   |            | 3.5   |       |

| t <sub>SUEXT</sub>     | Input Latch External Setup        | FO = 32          | 0.0  |       | 0.0  |       | 0.0        |       | ns    |

|                        |                                   | FO = 256         | 0.0  |       | 0.0  |       | 0.0        |       |       |

| t <sub>HEXT</sub>      | Input Latch External Hold         | FO = 32          | 7.0  |       | 7.0  |       | 7.0        |       | ns    |

|                        |                                   | FO = 256         | 11.2 |       | 11.2 |       | 11.2       |       |       |

| t <sub>P</sub>         | Minimum Period                    | FO = 32          | 7.7  |       | 8.3  |       | 9.1        |       | ns    |

|                        |                                   | FO = 256         | 8.1  |       | 8.8  |       | 10.0       |       |       |

| f <sub>MAX</sub>       | Maximum Frequency                 | FO = 32          |      | 130.0 |      | 120.0 |            | 110.0 | ns    |

|                        |                                   | FO = 256         |      | 125.0 |      | 115.0 |            | 100.0 | ]     |

Note: \*These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

**Detailed Specifications**

## A1240A Timing Characteristics (continued)

Table 2-16 • A1240A Worst-Case Commercial Conditions, VCC = 4.75 V,  $T_J$  = 70°C

| I/O Mod                        | ule Input Propagation Delays      |                  | -2 S | peed  | -1 Speed |       | Std. Speed |      | Units |

|--------------------------------|-----------------------------------|------------------|------|-------|----------|-------|------------|------|-------|

| Paramet                        | ter/Description                   |                  | Min. | Max.  | Min.     | Max.  | Min.       | Max. |       |

| t <sub>INYH</sub>              | Pad to Y High                     |                  |      | 2.9   |          | 3.3   |            | 3.8  | ns    |

| t <sub>INYL</sub>              | Pad to Y Low                      |                  |      | 2.6   |          | 3.0   |            | 3.5  | ns    |

| t <sub>INGH</sub>              | G to Y High                       |                  |      | 5.0   |          | 5.7   |            | 6.6  | ns    |

| t <sub>INGL</sub>              | G to Y Low                        |                  |      | 4.7   |          | 5.4   |            | 6.3  | ns    |

| Input Mo                       | odule Predicted Input Routing Del | ays <sup>*</sup> |      | .1.   |          |       |            |      |       |

| t <sub>IRD1</sub>              | FO = 1 Routing Delay              |                  |      | 4.2   |          | 4.8   |            | 5.6  | ns    |

| t <sub>IRD2</sub>              | FO = 2 Routing Delay              |                  |      | 4.8   |          | 5.4   |            | 6.4  | ns    |

| t <sub>IRD3</sub>              | FO = 3 Routing Delay              |                  |      | 5.4   |          | 6.1   |            | 7.2  | ns    |

| t <sub>IRD4</sub>              | FO = 4 Routing Delay              |                  |      | 5.9   |          | 6.7   |            | 7.9  | ns    |

| t <sub>IRD8</sub>              | FO = 8 Routing Delay              |                  |      | 7.9   |          | 8.9   |            | 10.5 | ns    |

| Global (                       | Clock Network                     |                  | •    | •     |          | •     |            | •    | •     |

| t <sub>CKH</sub>               | Input Low to High                 | FO = 32          |      | 10.2  |          | 11.0  |            | 12.8 | ns    |

|                                |                                   | FO = 256         |      | 11.8  |          | 13.0  |            | 15.7 |       |

| t <sub>CKL</sub> Input High to | Input High to Low                 | FO = 32          |      | 10.2  |          | 11.0  |            | 12.8 | ns    |

|                                |                                   | FO = 256         |      | 12.0  |          | 13.2  |            | 15.9 |       |

| t <sub>PWH</sub>               | Minimum Pulse Width High          | FO = 32          | 3.8  |       | 4.5      |       | 5.5        |      | ns    |

|                                |                                   | FO = 256         | 4.1  |       | 5.0      |       | 5.8        |      |       |

| t <sub>PWL</sub>               | Minimum Pulse Width Low           | FO = 32          | 3.8  |       | 4.5      |       | 5.5        |      | ns    |

|                                |                                   | FO = 256         | 4.1  |       | 5.0      |       | 5.8        |      |       |

| t <sub>CKSW</sub>              | Maximum Skew                      | FO = 32          |      | 0.5   |          | 0.5   |            | 0.5  | ns    |

|                                |                                   | FO = 256         |      | 2.5   |          | 2.5   |            | 2.5  |       |

| t <sub>SUEXT</sub>             | Input Latch External Setup        | FO = 32          | 0.0  |       | 0.0      |       | 0.0        |      | ns    |

|                                |                                   | FO = 256         | 0.0  |       | 0.0      |       | 0.0        |      |       |

| t <sub>HEXT</sub>              | Input Latch External Hold         | FO = 32          | 7.0  |       | 7.0      |       | 7.0        |      | ns    |

|                                |                                   | FO = 256         | 11.2 |       | 11.2     |       | 11.2       |      | 1     |

| t <sub>P</sub>                 | Minimum Period                    | FO = 32          | 8.1  |       | 9.1      |       | 11.1       |      | ns    |

|                                |                                   | FO = 256         | 8.8  |       | 10.0     |       | 11.7       |      | 1     |

| f <sub>MAX</sub>               | Maximum Frequency                 | FO = 32          |      | 125.0 |          | 110.0 |            | 90.0 | ns    |

|                                |                                   | FO = 256         |      | 115.0 |          | 100.0 |            | 85.0 | 1     |

Note: \*These parameters should be used for estimating device performance. Optimization techniques may further reduce delays by 0 to 4 ns. Routing delays are for typical designs across worst-case operating conditions. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

2-16 Revision 8

## A1240A Timing Characteristics (continued)

Table 2-17 • A1240A Worst-Case Commercial Conditions, VCC = 4.75 V,  $T_J$  = 70°C

| TTL Out           | put Module Timing <sup>1</sup>    | -2 S | peed | -1 Speed |      | Std. Speed |      | Units |

|-------------------|-----------------------------------|------|------|----------|------|------------|------|-------|

| Parame            | ter/Description                   | Min. | Max. | Min.     | Max. | Min.       | Max. |       |

| t <sub>DLH</sub>  | Data to Pad High                  |      | 8.0  |          | 9.0  |            | 10.6 | ns    |

| t <sub>DHL</sub>  | Data to Pad Low                   |      | 10.1 |          | 11.4 |            | 13.4 | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to High              |      | 8.9  |          | 10.0 |            | 11.8 | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to Low               |      | 11.7 |          | 13.2 |            | 15.5 | ns    |

| t <sub>ENHZ</sub> | Enable Pad High to Z              |      | 7.1  |          | 8.0  |            | 9.4  | ns    |

| t <sub>ENLZ</sub> | Enable Pad Low to Z               |      | 8.4  |          | 9.5  |            | 11.1 | ns    |

| t <sub>GLH</sub>  | G to Pad High                     |      | 9.0  |          | 10.2 |            | 11.9 | ns    |

| t <sub>GHL</sub>  | G to Pad Low                      |      | 11.2 |          | 12.7 |            | 14.9 | ns    |

| $d_{TLH}$         | Delta Low to High                 |      | 0.07 |          | 0.08 |            | 0.09 | ns/pF |

| $d_{THL}$         | Delta High to Low                 |      | 0.12 |          | 0.13 |            | 0.16 | ns/pF |

| CMOS (            | Output Module Timing <sup>1</sup> | •    |      |          |      |            |      |       |

| t <sub>DLH</sub>  | Data to Pad High                  |      | 10.2 |          | 11.5 |            | 13.5 | ns    |

| t <sub>DHL</sub>  | Data to Pad Low                   |      | 8.4  |          | 9.6  |            | 11.2 | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to High              |      | 8.9  |          | 10.0 |            | 11.8 | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to Low               |      | 11.7 |          | 13.2 |            | 15.5 | ns    |

| t <sub>ENHZ</sub> | Enable Pad High to Z              |      | 7.1  |          | 8.0  |            | 9.4  | ns    |

| t <sub>ENLZ</sub> | Enable Pad Low to Z               |      | 8.4  |          | 9.5  |            | 11.1 | ns    |

| t <sub>GLH</sub>  | G to Pad High                     |      | 9.0  |          | 10.2 |            | 11.9 | ns    |

| t <sub>GHL</sub>  | G to Pad Low                      |      | 11.2 |          | 12.7 |            | 14.9 | ns    |

| d <sub>TLH</sub>  | Delta Low to High                 |      | 0.12 |          | 0.13 |            | 0.16 | ns/pF |

| d <sub>THL</sub>  | Delta High to Low                 |      | 0.09 |          | 0.10 |            | 0.12 | ns/pF |

#### Notes:

- 1. Delays based on 50 pF loading.

- 2. SSO information can be found at www.microsemi.com/soc/techdocs/appnotes/board\_consideration.aspx.

## **PL84**

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

| PL84       |                 |                 |                 |

|------------|-----------------|-----------------|-----------------|

| Pin Number | A1225A Function | A1240A Function | A1280A Function |

| 2          | CLKB, I/O       | CLKB, I/O       | CLKB, I/O       |

| 4          | PRB, I/O        | PRB, I/O        | PRB, I/O        |

| 6          | GND             | GND             | GND             |

| 10         | DCLK, I/O       | DCLK, I/O       | DCLK, I/O       |

| 12         | MODE            | MODE            | MODE            |

| 22         | VCC             | VCC             | VCC             |

| 23         | VCC             | VCC             | VCC             |

| 28         | GND             | GND             | GND             |

| 43         | VCC             | VCC             | VCC             |

| 49         | GND             | GND             | GND             |

| 52         | SDO             | SDO             | SDO             |

| 63         | GND             | GND             | GND             |

| 64         | VCC             | VCC             | VCC             |

| 65         | VCC             | VCC             | VCC             |

| 70         | GND             | GND             | GND             |

| 76         | SDI, I/O        | SDI, I/O        | SDI, I/O        |

| 81         | PRA, I/O        | PRA, I/O        | PRA, I/O        |

| 83         | CLKA, I/O       | CLKA, I/O       | CLKA, I/O       |

| 84         | VCC             | VCC             | VCC             |

#### Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

3-2 Revision 8

| PQ160      |                 |         |

|------------|-----------------|---------|

| Pin Number | A1280A Function | Pin Nur |

| 2          | DCLK, I/O       | 69      |

| 6          | VCC             | 80      |

| 11         | GND             | 82      |

| 16         | PRB, I/O        | 86      |

| 18         | CLKB, I/O       | 89      |

| 20         | VCC             | 98      |

| 21         | CLKA, I/O       | 99      |

| 23         | PRA, I/O        | 109     |

| 30         | GND             | 114     |

| 35         | VCC             | 120     |

| 38         | SDI, I/O        | 125     |

| 40         | GND             | 130     |

| 44         | GND             | 135     |

| 49         | GND             | 138     |

| 54         | VCC             | 139     |

| 57         | VCC             | 140     |

| 58         | VCC             | 145     |

| 59         | GND             | 150     |

| 60         | VCC             | 155     |

| 61         | GND             | 159     |

| 64         | GND             | 160     |

|            |                 |         |

| PQ160      |                 |  |

|------------|-----------------|--|

| Pin Number | A1280A Function |  |

| 69         | GND             |  |

| 80         | GND             |  |

| 82         | SDO             |  |

| 86         | VCC             |  |

| 89         | GN              |  |

| 98         | GND             |  |

| 99         | GND             |  |

| 109        | GND             |  |

| 114        | VCC             |  |

| 120        | GND             |  |

| 125        | GND             |  |

| 130        | GND             |  |

| 135        | VCC             |  |

| 138        | VCC             |  |

| 139        | VCC             |  |

| 140        | GND             |  |

| 145        | GND             |  |

| 150        | VCC             |  |

| 155        | GND             |  |

| 159        | MODE            |  |

| 160        | GND             |  |

#### Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

3-8 Revision 8

## **VQ100**

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

| VQ100      |                 |  |

|------------|-----------------|--|

| Pin Number | A1225A Function |  |

| 2          | MODE            |  |

| 7          | GND             |  |

| 14         | VCC             |  |

| 15         | VCC             |  |

| 20         | GND             |  |

| 32         | GND             |  |

| 38         | VCC             |  |

| 44         | GND             |  |

| 50         | SDO             |  |

| 55         | GND             |  |

| 62         | GND             |  |

| 63         | VCC             |  |

| VQ100      |                 |  |

|------------|-----------------|--|

| Pin Number | A1225A Function |  |

| 64         | VCC             |  |

| 65         | VCC             |  |

| 70         | GND             |  |

| 77         | SDI, I/O        |  |

| 82         | GND             |  |

| 85         | PRA, I/O        |  |

| 87         | CLKA, I/O       |  |

| 88         | VCC             |  |

| 90         | CLKB, I/O       |  |

| 92         | PRB, I/O        |  |

| 94         | GND             |  |

| 100        | DCLK, I/O       |  |

#### Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

3-10 Revision 8

## **TQ176**

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

## **CQ172**

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

3-14 Revision 8

| CQ172      |                 |  |

|------------|-----------------|--|

| Pin Number | A1280A Function |  |

| 1          | MODE            |  |

| 7          | GND             |  |

| 12         | VCC             |  |

| 17         | GND             |  |

| 22         | GND             |  |

| 23         | VCC             |  |

| 24         | VCC             |  |

| 27         | VCC             |  |

| 32         | GND             |  |

| 37         | GND             |  |

| 50         | VCC             |  |

| 55         | GND             |  |

| 65         | GND             |  |

| 66         | VCC             |  |

| 75         | GND             |  |

| 80         | VCC             |  |

| 85         | SDO             |  |

| 98         | GND             |  |

| 103        | GND             |  |

| 106        | GND             |  |

| CQ172      |                 |  |

|------------|-----------------|--|

| Pin Number | A1280A Function |  |

| 107        | VCC             |  |

| 108        | GND             |  |

| 109        | VCC             |  |

| 110        | VCC             |  |

| 113        | VCC             |  |

| 118        | GND             |  |

| 123        | GND             |  |

| 131        | SDI, I/O        |  |

| 136        | VCC             |  |

| 141        | GND             |  |

| 148        | PRA, I/O        |  |

| 150        | CLKA, I/O       |  |

| 151        | VCC             |  |

| 152        | GND             |  |

| 154        | CLKB, I/O       |  |

| 156        | PRB, I/O        |  |

| 161        | GND             |  |

| 166        | VCC             |  |

| 171        | DCLK, I/O       |  |

#### Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

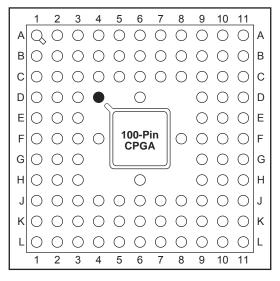

## **PG100**

Orientation Pin

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

3-16 Revision 8

| PG132      |                 |  |

|------------|-----------------|--|

| Pin Number | A1240A Function |  |

| A1         | MODE            |  |

| B5         | GND             |  |

| B6         | CLKB, I/O       |  |

| B7         | CLKA, I/O       |  |

| B8         | PRA, I/O        |  |

| B9         | GND             |  |

| B12        | SDI, I/O        |  |

| C3         | DCLK, I/O       |  |

| C5         | GND             |  |

| C6         | PRB, I/O        |  |

| C7         | VCC             |  |

| C9         | GND             |  |

| D7         | VCC             |  |

| E3         | GND             |  |

| E11        | GND             |  |

| E12        | GND             |  |

| F4         | GND             |  |

| G2         | VCC             |  |

| PG132      |                 |  |

|------------|-----------------|--|

| Pin Number | A1240A Function |  |

| G3         | VCC             |  |

| G4         | VCC             |  |

| G10        | VCC             |  |

| G11        | VCC             |  |

| G12        | VCC             |  |

| G13        | VCC             |  |

| H13        | GND             |  |

| J2         | GND             |  |

| J3         | GND             |  |

| J11        | GND             |  |

| K7         | VCC             |  |

| K12        | GND             |  |

| L5         | GND             |  |

| L7         | VCC             |  |

| L9         | GND             |  |

| M9         | GND             |  |

| N12        | SDO             |  |

#### Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

| PG176      |                 |  |

|------------|-----------------|--|

| Pin Number | A1280A Function |  |

| A9         | CLKA, I/O       |  |

| В3         | DCLK, I/O       |  |

| B8         | CLKB, I/O       |  |

| B14        | SDI, I/O        |  |

| C3         | MODE            |  |

| C8         | GND             |  |

| C9         | PRA, I/O        |  |

| D4         | GND             |  |

| D5         | VCC             |  |

| D6         | GND             |  |

| D7         | PRB, I/O        |  |

| D8         | VCC             |  |

| D10        | GND             |  |

| D11        | VCC             |  |

| D12        | GND             |  |

| E4         | GND             |  |

| E12        | GND             |  |

| F4         | VCC             |  |

| F12        | GND             |  |

| G4         | GND             |  |

| G12        | VCC             |  |

| H2         | VCC             |  |

| PG176      |                 |  |

|------------|-----------------|--|

| Pin Number | A1280A Function |  |

| H3         | VCC             |  |

| H4         | GND             |  |

| H12        | GND             |  |

| H13        | VCC             |  |

| H14        | VCC             |  |

| J4         | VCC             |  |

| J12        | GND             |  |

| J13        | GND             |  |

| J14        | VCC             |  |

| K4         | GND             |  |

| K12        | GND             |  |

| L4         | GND             |  |

| M4         | GND             |  |

| M5         | VCC             |  |

| M6         | GND             |  |

| M8         | GND             |  |

| M10        | GND             |  |

| M11        | VCC             |  |

| M12        | GND             |  |

| N8         | VCC             |  |

| P13        | SDO             |  |

#### Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.