Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 1232                                                          |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | -                                                             |

| Number of I/O                  | 140                                                           |

| Number of Gates                | 8000                                                          |

| Voltage - Supply               | 4.5V ~ 5.5V                                                   |

| Mounting Type                  | Through Hole                                                  |

| Operating Temperature          | 0°C ~ 70°C (TA)                                               |

| Package / Case                 | 176-BCPGA                                                     |

| Supplier Device Package        | 176-CPGA (39.88x39.88)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a1280a-1pg176c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Product Plan**

|                                           | s    | peed Grad | e <sup>1</sup> | Application <sup>1</sup> |   |   |   |

|-------------------------------------------|------|-----------|----------------|--------------------------|---|---|---|

| Device/Package                            | Std. | -1        | -2             | С                        | I | М | В |

| A1225A Device                             | •    | •         | •              | •                        | • | • |   |

| 84-Pin Plastic Leaded Chip Carrier (PL)   | ✓    | 1         | 1              | 1                        | 1 | _ | _ |

| 100-Pin Plastic Quad Flatpack (PQ)        | 1    | 1         | 1              | 1                        | 1 | _ | _ |

| 100-Pin Very Thin Quad Flatpack (VQ)      | 1    | ✓         | 1              | 1                        | _ | _ | _ |

| 100-Pin Ceramic Pin Grid Array (PG)       | 1    | 1         | 1              | 1                        | _ | _ | _ |

| A1240A Device                             | I    |           |                |                          | ı | ı |   |

| 84-Pin Plastic Leaded Chip Carrier (PL)   | ✓    | 1         | ✓              | 1                        | 1 | _ | _ |

| 132-Pin Ceramic Pin Grid Array (PG)       | 1    | 1         | 1              | 1                        | _ | 1 | ✓ |

| 144-Pin Plastic Quad Flat Pack (PQ)       | 1    | 1         | 1              | 1                        | 1 | _ | _ |

| 176-Pin Thin (1.4 mm) Quad Flat Pack (TQ) | 1    | 1         | 1              | 1                        | _ | _ | _ |

| A1280A Device                             | I    |           |                |                          | ı | ı |   |

| 160-Pin Plastic Quad Flatpack (PQ)        | ✓    | 1         | ✓              | 1                        | 1 | _ | _ |

| 172-Pin Ceramic Quad Flatpack (CQ)        | 1    | ✓         | ✓              | ✓                        | _ | 1 | ✓ |

| 176-Pin Ceramic Pin Grid Array (PG)       | /    | ✓         | ✓              | 1                        | _ | 1 | ✓ |

| 176-Pin Thin (1.4 mm) Quad Flat Pack (TQ) | 1    | 1         | 1              | 1                        | _ | _ | _ |

| • • •                                     |      | •         |                | •                        | _ | - | _ |

Notes:

Applications:

C = Commercial

I = Industrial

M = Military

B = MIL-STD-883

Availability: ✓ = Available P = Planned – = Not planned

Speed Grade:

-1 = Approx. 15% faster than Std. -2 = Approx. 25% faster than Std.

2. Contact your Microsemi SoC Products Group sales representative for product availability.

### **Device Resources**

| Device | Logic   |       |       |       |       |       | User  | I/Os  |      |       |       |       |

|--------|---------|-------|-------|-------|-------|-------|-------|-------|------|-------|-------|-------|

| Series | Modules | Gates | PG176 | PG132 | PG100 | PQ160 | PQ144 | PQ100 | PL84 | CQ172 | TQ176 | VQ100 |

| A1225A | 451     | 2,500 | _     | _     | 83    | _     | _     | 83    | 72   | _     | _     | 83    |

| A1240A | 684     | 4,000 | _     | 104   | _     | _     | 104   | _     | 72   | _     | 104   | _     |

| A1280A | 1,232   | 8,000 | 140   | -     | -     | 125   | ı     | -     | 72   | 140   | 140   | _     |

Contact your local Microsemi SoC Products Group representative for device availability: http://www.microsemi.com/soc/contact/default.aspx.

Revision 8 III

# 1 - ACT 2 Family Overview

### **General Description**

The ACT 2 family represents Actel's second generation of field programmable gate arrays (FPGAs). The ACT 2 family presents a two-module architecture, consisting of C-modules and S-modules. These modules are optimized for both combinatorial and sequential designs. Based on Actel's patented channeled array architecture, the ACT 2 family provides significant enhancements to gate density and performance while maintaining downward compatibility with the ACT 1 design environment and upward compatibility with the ACT 3 design environment. The devices are implemented in silicon gate, 1.0-μm, two-level metal CMOS, and employ Actel's PLICE® antifuse technology. This revolutionary architecture offers gate array design flexibility, high performance, and fast time-to-production with user programming. The ACT 2 family is supported by the Designer and Designer Advantage Systems, which offers automatic pin assignment, validation of electrical and design rules, automatic placement and routing, timing analysis, user programming, and diagnostic probe capabilities. The systems are supported on the following platforms: 386/486™ PC, Sun™, and HP™ workstations. The systems provide CAE interfaces to the following design environments: Cadence, Viewlogic®, Mentor Graphics®, and OrCAD™.

**Detailed Specifications**

Table 2-3 • Electrical Specifications

|                                                    |                                                        | Con                                                                   | nmercial  | In   | dustrial  | M    | lilitary  |       |

|----------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------|-----------|------|-----------|------|-----------|-------|

| Symbol                                             | Parameter                                              | Min.                                                                  | Max.      | Min. | Max.      | Min. | Max.      | Units |

| VOH <sup>1</sup>                                   | $(IOH = -10 \text{ mA})^2$                             | 2.4                                                                   | -         | -    | _         | -    | -         | V     |

|                                                    | (IOH = -6 mA)                                          | 3.84                                                                  | -         | -    | -         | -    | _         | V     |

|                                                    | (IOH = -4 mA)                                          | -                                                                     | -         | 3.7  | -         | 3.7  | _         | V     |

| VOL <sup>1</sup>                                   | $(IOL = 10 \text{ mA})^2$                              | -                                                                     | 0.5       | -    | _         | -    | _         | V     |

|                                                    | (IOL = 6 mA)                                           | _                                                                     | 0.33      | -    | 0.40      | -    | 0.40      | V     |

| VIL                                                |                                                        | -0.3                                                                  | 0.8       | -0.3 | 0.8       | -0.3 | 0.8       | V     |

| VIH                                                |                                                        | 2.0                                                                   | VCC + 0.3 | 2.0  | VCC + 0.3 | 2.0  | VCC + 0.3 | V     |

| Input Transi                                       | tion Time t <sub>R</sub> , t <sub>F</sub> <sup>2</sup> | _                                                                     | 500       | -    | 500       | -    | 500       | ns    |

| C <sub>IO</sub> I/O capa                           | acitance <sup>2,3</sup>                                | _                                                                     | 10        | -    | 10        | -    | 10        | pF    |

| Standby Current, ICC <sup>4</sup> (typical = 1 mA) |                                                        | _                                                                     | 2         | -    | 10        | -    | 20        | mA    |

| Leakage Current <sup>5</sup>                       |                                                        | -10                                                                   | +10       | -10  | +10       | -10  | +10       | μA    |

| ICC(D)                                             | Dynamic VCC supply current                             | ICC(D) Dynamic VCC supply current. See the Power Dissipation section. |           |      |           |      | •         |       |

#### Notes:

- 1. Only one output tested at a time. VCC = minimum.

- 2. Not tested, for information only.

- 3. Includes worst-case PG176 package capacitance. VOUT = 0 V, f = 1 MHz

- 4. All outputs unloaded. All inputs = VCC or GND, typical ICC = 1 mA. ICC limit includes IPP and ISV during normal operations.

- 5. VOUT, VIN = VCC or GND.

2-2 Revision 8

### **Parameter Measurement**

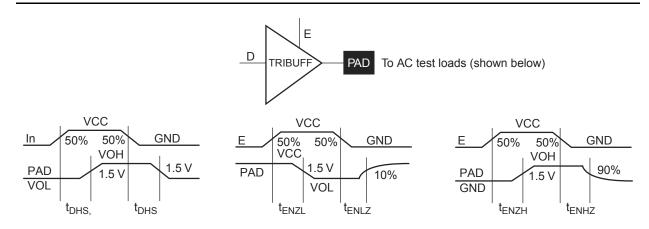

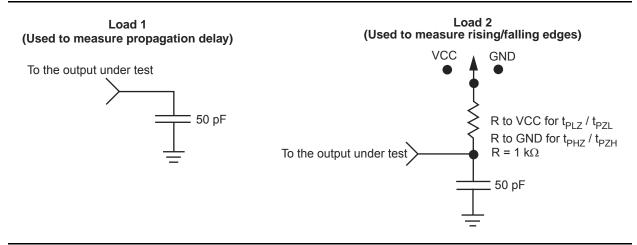

Figure 2-2 • Output Buffer Delays

Figure 2-3 • AC Test Loads

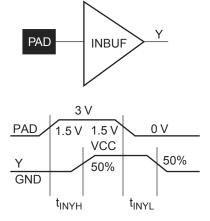

Figure 2-4 • Input Buffer Delays

2-8 Revision 8

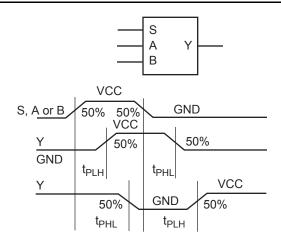

Figure 2-5 • Module Delays

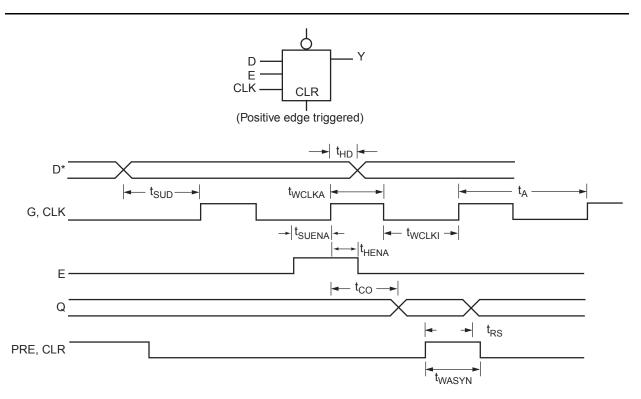

### **Sequential Module Timing Characteristics**

Note: D represents all data functions involving A, B, and S for multiplexed flip-flops.

Figure 2-6 • Flip-Flops and Latches

### A1240A Timing Characteristics (continued)

Table 2-17 • A1240A Worst-Case Commercial Conditions, VCC = 4.75 V,  $T_J$  = 70°C

| TTL Output Module Timing <sup>1</sup> |                                   | -2 S | peed | -1 Speed |      | Std. Speed |      | Units |

|---------------------------------------|-----------------------------------|------|------|----------|------|------------|------|-------|

| Parame                                | ter/Description                   | Min. | Max. | Min.     | Max. | Min.       | Max. |       |

| t <sub>DLH</sub>                      | Data to Pad High                  |      | 8.0  |          | 9.0  |            | 10.6 | ns    |

| t <sub>DHL</sub>                      | Data to Pad Low                   |      | 10.1 |          | 11.4 |            | 13.4 | ns    |

| t <sub>ENZH</sub>                     | Enable Pad Z to High              |      | 8.9  |          | 10.0 |            | 11.8 | ns    |

| t <sub>ENZL</sub>                     | Enable Pad Z to Low               |      | 11.7 |          | 13.2 |            | 15.5 | ns    |

| t <sub>ENHZ</sub>                     | Enable Pad High to Z              |      | 7.1  |          | 8.0  |            | 9.4  | ns    |

| t <sub>ENLZ</sub>                     | Enable Pad Low to Z               |      | 8.4  |          | 9.5  |            | 11.1 | ns    |

| t <sub>GLH</sub>                      | G to Pad High                     |      | 9.0  |          | 10.2 |            | 11.9 | ns    |

| t <sub>GHL</sub>                      | G to Pad Low                      |      | 11.2 |          | 12.7 |            | 14.9 | ns    |

| $d_{TLH}$                             | Delta Low to High                 |      | 0.07 |          | 0.08 |            | 0.09 | ns/pF |

| $d_{THL}$                             | Delta High to Low                 |      | 0.12 |          | 0.13 |            | 0.16 | ns/pF |

| CMOS (                                | Output Module Timing <sup>1</sup> | -    |      |          |      |            |      |       |

| t <sub>DLH</sub>                      | Data to Pad High                  |      | 10.2 |          | 11.5 |            | 13.5 | ns    |

| t <sub>DHL</sub>                      | Data to Pad Low                   |      | 8.4  |          | 9.6  |            | 11.2 | ns    |

| t <sub>ENZH</sub>                     | Enable Pad Z to High              |      | 8.9  |          | 10.0 |            | 11.8 | ns    |

| t <sub>ENZL</sub>                     | Enable Pad Z to Low               |      | 11.7 |          | 13.2 |            | 15.5 | ns    |

| t <sub>ENHZ</sub>                     | Enable Pad High to Z              |      | 7.1  |          | 8.0  |            | 9.4  | ns    |

| t <sub>ENLZ</sub>                     | Enable Pad Low to Z               |      | 8.4  |          | 9.5  |            | 11.1 | ns    |

| t <sub>GLH</sub>                      | G to Pad High                     |      | 9.0  |          | 10.2 |            | 11.9 | ns    |

| t <sub>GHL</sub>                      | G to Pad Low                      |      | 11.2 |          | 12.7 |            | 14.9 | ns    |

| d <sub>TLH</sub>                      | Delta Low to High                 |      | 0.12 |          | 0.13 |            | 0.16 | ns/pF |

| d <sub>THL</sub>                      | Delta High to Low                 |      | 0.09 |          | 0.10 |            | 0.12 | ns/pF |

#### Notes:

- 1. Delays based on 50 pF loading.

- 2. SSO information can be found at www.microsemi.com/soc/techdocs/appnotes/board\_consideration.aspx.

### **Pin Descriptions**

#### CLKA Clock A (Input)

TTL Clock input for clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

#### CLKB Clock B (Input)

TTL Clock input for clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

#### DCLK Diagnostic Clock (Input)

TTL Clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is High. This pin functions as an I/O when the MODE pin is Low.

#### GND Ground

Low supply voltage.

#### I/O Input/Output (Input, Output)

The I/O pin functions as an input, output, three-state, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/O pins are automatically driven Low by the ALS software.

#### MODE Mode (Input)

The MODE pin controls the use of multifunction pins (DCLK, PRA, PRB, SDI). When the MODE pin is High, the special functions are active. When the MODE pin is Low, the pins function as I/Os. To provide Actionprobe capability, the MODE pin should be terminated to GND through a 10K resistor so that the MODE pin can be pulled High when required.

#### NC No Connection

This pin is not connected to circuitry within the device.

#### PRA Probe A (Output)

The Probe A pin is used to output data from any user-defined design node within the device. This independent diagnostic pin can be used in conjunction with the Probe B pin to allow real-time diagnostic output of any signal path within the device. The Probe A pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRA is active when the MODE pin is High. This pin functions as an I/O when the MODE pin is Low.

#### PRB Probe B (Output)

The Probe B pin is used to output data from any user-defined design node within the device. This independent diagnostic pin can be used in conjunction with the Probe A pin to allow real-time diagnostic output of any signal path within the device. The Probe B pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRB is active when the MODE pin is High. This pin functions as an I/O when the MODE pin is Low.

#### SDI Serial Data Input (Input)

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is High. This pin functions as an I/O when the MODE pin is Low.

#### SDO Serial Data Output (Output)

Serial data output for diagnostic probe. SDO is active when the MODE pin is High. This pin functions as an I/O when the MODE pin is Low.

#### VCC 5.0 V Supply Voltage

High supply voltage.

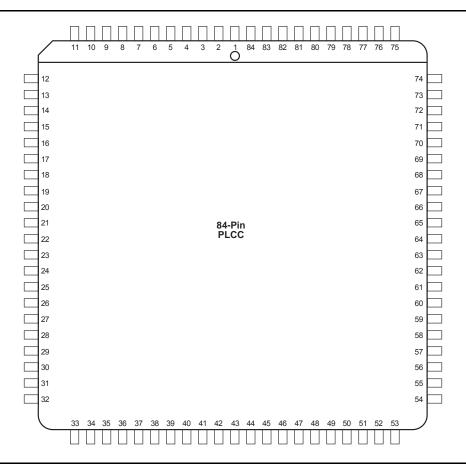

### **PL84**

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

|            | PQ160           |         |  |  |  |

|------------|-----------------|---------|--|--|--|

| Pin Number | A1280A Function | Pin Nur |  |  |  |

| 2          | DCLK, I/O       | 69      |  |  |  |

| 6          | VCC             | 80      |  |  |  |

| 11         | GND             | 82      |  |  |  |

| 16         | PRB, I/O        | 86      |  |  |  |

| 18         | CLKB, I/O       | 89      |  |  |  |

| 20         | VCC             | 98      |  |  |  |

| 21         | CLKA, I/O       | 99      |  |  |  |

| 23         | PRA, I/O        | 109     |  |  |  |

| 30         | GND             | 114     |  |  |  |

| 35         | VCC             | 120     |  |  |  |

| 38         | SDI, I/O        | 125     |  |  |  |

| 40         | GND             | 130     |  |  |  |

| 44         | GND             | 135     |  |  |  |

| 49         | GND             | 138     |  |  |  |

| 54         | VCC             | 139     |  |  |  |

| 57         | VCC             | 140     |  |  |  |

| 58         | VCC             | 145     |  |  |  |

| 59         | GND             | 150     |  |  |  |

| 60         | VCC             | 155     |  |  |  |

| 61         | GND             | 159     |  |  |  |

| 64         | GND             | 160     |  |  |  |

|            |                 |         |  |  |  |

| PQ160      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A1280A Function |  |  |  |

| 69         | GND             |  |  |  |

| 80         | GND             |  |  |  |

| 82         | SDO             |  |  |  |

| 86         | VCC             |  |  |  |

| 89         | GN              |  |  |  |

| 98         | GND             |  |  |  |

| 99         | GND             |  |  |  |

| 109        | GND             |  |  |  |

| 114        | VCC             |  |  |  |

| 120        | GND             |  |  |  |

| 125        | GND             |  |  |  |

| 130        | GND             |  |  |  |

| 135        | VCC             |  |  |  |

| 138        | VCC             |  |  |  |

| 139        | VCC             |  |  |  |

| 140        | GND             |  |  |  |

| 145        | GND             |  |  |  |

| 150        | VCC             |  |  |  |

| 155        | GND             |  |  |  |

| 159        | MODE            |  |  |  |

| 160        | GND             |  |  |  |

#### Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

3-8 Revision 8

|            | TQ176           |                 |  |  |

|------------|-----------------|-----------------|--|--|

| Pin Number | A1240A Function | A1280A Function |  |  |

| 1          | GND             | GND             |  |  |

| 2          | MODE            | MODE            |  |  |

| 8          | NC              | NC              |  |  |

| 10         | NC              | I/O             |  |  |

| 11         | NC              | I/O             |  |  |

| 13         | NC              | VCC             |  |  |

| 18         | GND             | GND             |  |  |

| 19         | NC              | I/O             |  |  |

| 20         | NC              | I/O             |  |  |

| 22         | NC              | I/O             |  |  |

| 23         | GND             | GND             |  |  |

| 24         | NC              | VCC             |  |  |

| 25         | VCC             | VCC             |  |  |

| 26         | NC              | I/O             |  |  |

| 27         | NC              | I/O             |  |  |

| 28         | VCC             | VCC             |  |  |

| 29         | NC              | I/O             |  |  |

| 33         | NC              | NC              |  |  |

| 37         | NC              | I/O             |  |  |

| 38         | NC              | NC              |  |  |

| 45         | GND             | GND             |  |  |

| 52         | NC              | VCC             |  |  |

| 54         | NC              | I/O             |  |  |

| 55         | NC              | I/O             |  |  |

| 57         | NC              | NC              |  |  |

| 61         | NC              | I/O             |  |  |

| 64         | NC              | I/O             |  |  |

| 66         | NC              | I/O             |  |  |

| 67         | GND             | GND             |  |  |

| 68         | VCC             | VCC             |  |  |

| 74         | NC              | I/O             |  |  |

| 77         | NC              | NC              |  |  |

| 78         | NC              | I/O             |  |  |

| 80         | NC              | I/O             |  |  |

|            | TQ176           |                 |  |  |

|------------|-----------------|-----------------|--|--|

| Pin Number | A1240A Function | A1280A Function |  |  |

| 82         | NC              | VCC             |  |  |

| 86         | NC              | I/O             |  |  |

| 87         | SDO             | SDO             |  |  |

| 89         | GND             | GND             |  |  |

| 96         | NC              | I/O             |  |  |

| 97         | NC              | I/O             |  |  |

| 101        | NC              | NC              |  |  |

| 103        | NC              | I/O             |  |  |

| 106        | GND             | GND             |  |  |

| 107        | NC              | I/O             |  |  |

| 108        | NC              | I/O             |  |  |

| 109        | GND             | GND             |  |  |

| 110        | VCC             | VCC             |  |  |

| 111        | GND             | GND             |  |  |

| 112        | VCC             | VCC             |  |  |

| 113        | VCC             | VCC             |  |  |

| 114        | NC              | I/O             |  |  |

| 115        | NC              | I/O             |  |  |

| 116        | NC              | VCC             |  |  |

| 121        | NC              | NC              |  |  |

| 124        | NC              | I/O             |  |  |

| 125        | NC              | I/O             |  |  |

| 126        | NC              | NC              |  |  |

| 133        | GND             | GND             |  |  |

| 135        | SDI, I/O        | SDI, I/O        |  |  |

| 136        | NC              | I/O             |  |  |

| 140        | NC              | VCC             |  |  |

| 143        | NC              | I/O             |  |  |

| 144        | NC              | I/O             |  |  |

| 145        | NC              | NC              |  |  |

| 147        | NC              | I/O             |  |  |

| 151        | NC              | I/O             |  |  |

| 152        | PRA, I/O        | PRA, I/O        |  |  |

| 154        | CLKA, I/O       | CLKA, I/O       |  |  |

3-12 Revision 8

|            | CQ172           |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A1280A Function |  |  |  |

| 1          | MODE            |  |  |  |

| 7          | GND             |  |  |  |

| 12         | VCC             |  |  |  |

| 17         | GND             |  |  |  |

| 22         | GND             |  |  |  |

| 23         | VCC             |  |  |  |

| 24         | VCC             |  |  |  |

| 27         | VCC             |  |  |  |

| 32         | GND             |  |  |  |

| 37         | GND             |  |  |  |

| 50         | VCC             |  |  |  |

| 55         | GND             |  |  |  |

| 65         | GND             |  |  |  |

| 66         | VCC             |  |  |  |

| 75         | GND             |  |  |  |

| 80         | VCC             |  |  |  |

| 85         | SDO             |  |  |  |

| 98         | GND             |  |  |  |

| 103        | GND             |  |  |  |

| 106        | GND             |  |  |  |

| CQ172      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | A1280A Function |  |  |

| 107        | VCC             |  |  |

| 108        | GND             |  |  |

| 109        | VCC             |  |  |

| 110        | VCC             |  |  |

| 113        | VCC             |  |  |

| 118        | GND             |  |  |

| 123        | GND             |  |  |

| 131        | SDI, I/O        |  |  |

| 136        | VCC             |  |  |

| 141        | GND             |  |  |

| 148        | PRA, I/O        |  |  |

| 150        | CLKA, I/O       |  |  |

| 151        | VCC             |  |  |

| 152        | GND             |  |  |

| 154        | CLKB, I/O       |  |  |

| 156        | PRB, I/O        |  |  |

| 161        | GND             |  |  |

| 166        | VCC             |  |  |

| 171        | DCLK, I/O       |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

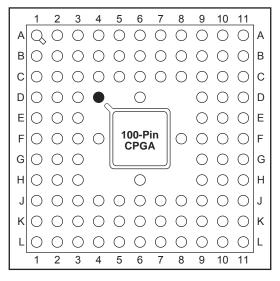

### **PG100**

Orientation Pin

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

3-16 Revision 8

| PG100      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | A1225A Function |  |  |

| A4         | PRB, I/O        |  |  |

| A7         | PRA, I/O        |  |  |

| B6         | VCC             |  |  |

| C2         | MODE            |  |  |

| C3         | DCLK, I/O       |  |  |

| C5         | GND             |  |  |

| C6         | CLKA, I/O       |  |  |

| C7         | GND             |  |  |

| C8         | SDI, I/O        |  |  |

| D6         | CLKB, I/O       |  |  |

| D10        | GND             |  |  |

| E3         | GND             |  |  |

| PG100      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | A1225A Function |  |  |

| E11        | VCC             |  |  |

| F3         | VCC             |  |  |

| F9         | VCC             |  |  |

| F10        | VCC             |  |  |

| F11        | GND             |  |  |

| G1         | VCC             |  |  |

| G3         | GND             |  |  |

| G9         | GND             |  |  |

| J5         | GND             |  |  |

| J7         | GND             |  |  |

| J9         | SDO             |  |  |

| K6         | VCC             |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

| PG132      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | A1240A Function |  |  |

| A1         | MODE            |  |  |

| B5         | GND             |  |  |

| B6         | CLKB, I/O       |  |  |

| B7         | CLKA, I/O       |  |  |

| B8         | PRA, I/O        |  |  |

| B9         | GND             |  |  |

| B12        | SDI, I/O        |  |  |

| C3         | DCLK, I/O       |  |  |

| C5         | GND             |  |  |

| C6         | PRB, I/O        |  |  |

| C7         | VCC             |  |  |

| C9         | GND             |  |  |

| D7         | VCC             |  |  |

| E3         | GND             |  |  |

| E11        | GND             |  |  |

| E12        | GND             |  |  |

| F4         | GND             |  |  |

| G2         | VCC             |  |  |

| PG132      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | A1240A Function |  |  |

| G3         | VCC             |  |  |

| G4         | VCC             |  |  |

| G10        | VCC             |  |  |

| G11        | VCC             |  |  |

| G12        | VCC             |  |  |

| G13        | VCC             |  |  |

| H13        | GND             |  |  |

| J2         | GND             |  |  |

| J3         | GND             |  |  |

| J11        | GND             |  |  |

| K7         | VCC             |  |  |

| K12        | GND             |  |  |

| L5         | GND             |  |  |

| L7         | VCC             |  |  |

| L9         | GND             |  |  |

| M9         | GND             |  |  |

| N12        | SDO             |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

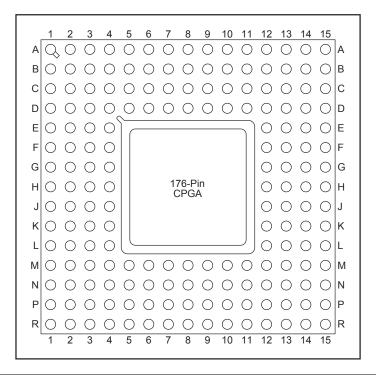

### **PG176**

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

3-20 Revision 8

| PG176      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | A1280A Function |  |  |

| A9         | CLKA, I/O       |  |  |

| В3         | DCLK, I/O       |  |  |

| B8         | CLKB, I/O       |  |  |

| B14        | SDI, I/O        |  |  |

| C3         | MODE            |  |  |

| C8         | GND             |  |  |

| C9         | PRA, I/O        |  |  |

| D4         | GND             |  |  |

| D5         | VCC             |  |  |

| D6         | GND             |  |  |

| D7         | PRB, I/O        |  |  |

| D8         | VCC             |  |  |

| D10        | GND             |  |  |

| D11        | VCC             |  |  |

| D12        | GND             |  |  |

| E4         | GND             |  |  |

| E12        | GND             |  |  |

| F4         | VCC             |  |  |

| F12        | GND             |  |  |

| G4         | GND             |  |  |

| G12        | VCC             |  |  |

| H2         | VCC             |  |  |

| PG176      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | A1280A Function |  |  |

| H3         | VCC             |  |  |

| H4         | GND             |  |  |

| H12        | GND             |  |  |

| H13        | VCC             |  |  |

| H14        | VCC             |  |  |

| J4         | VCC             |  |  |

| J12        | GND             |  |  |

| J13        | GND             |  |  |

| J14        | VCC             |  |  |

| K4         | GND             |  |  |

| K12        | GND             |  |  |

| L4         | GND             |  |  |

| M4         | GND             |  |  |

| M5         | VCC             |  |  |

| M6         | GND             |  |  |

| M8         | GND             |  |  |

| M10        | GND             |  |  |

| M11        | VCC             |  |  |

| M12        | GND             |  |  |

| N8         | VCC             |  |  |

| P13        | SDO             |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. MODE pin should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.