# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 6                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1571-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

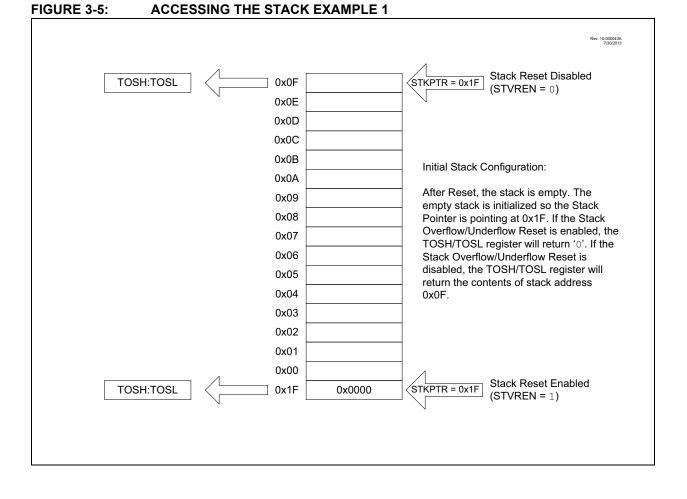

#### 3.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-5 through 3-8). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW OR RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an overflow/underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 3.5.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. The TOSH:TOSL register pair points to the top of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. The STKPTR is 5 bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and interrupts will increment STKPTR while RETLW, RETURN and RETFIE will decrement STKPTR. At any time, the STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement the STKPTR.

Reference Figure 3-5 through Figure 3-8 for examples of accessing the stack.

#### 4.7 Register Definitions: Device ID

| REGISTER 4-3. |   | ICEID. DEVICI |      | <b>_</b> N` ' |       |   |       |

|---------------|---|---------------|------|---------------|-------|---|-------|

|               |   | R             | R    | R             | R     | R | R     |

|               |   |               |      | DEV<          | 13:8> |   |       |

|               |   | bit 13        |      |               |       |   | bit 8 |

| R             | R | R             | R    | R             | R     | R | R     |

|               |   |               | DEV< | :7:0>         |       |   |       |

| bit 7         |   |               |      |               |       |   | bit 0 |

|               |   |               |      |               |       |   |       |

#### REGISTER 4-3: DEVICEID: DEVICE ID REGISTER<sup>(1)</sup>

#### Legend:

| R   | t = Readable bit   |                  |                    |

|-----|--------------------|------------------|--------------------|

| '0' | ' = Bit is cleared | '1' = Bit is set | x = Bit is unknown |

bit 13-0 **DEV<13:0>:** Device ID bits

Refer to Table 4-1 to determine what these bits will read on which device. A value of 3FFFh is invalid.

**Note 1:** This location cannot be written.

#### REGISTER 4-4: REVISIONID: REVISION ID REGISTER<sup>(1)</sup>

|       |   | R      | R    | R     | R     | R | R     |

|-------|---|--------|------|-------|-------|---|-------|

|       |   |        |      | REV<  | 13:8> |   |       |

|       |   | bit 13 |      |       |       |   | bit 8 |

|       |   |        |      |       |       |   |       |

| R     | R | R      | R    | R     | R     | R | R     |

|       |   |        | REV< | <7:0> |       |   |       |

| bit 7 |   |        |      |       |       |   | bit 0 |

| -   |       |

|-----|-------|

| Leq | and   |

| LEY | ciiu. |

| R = Readable bit     |                  |

|----------------------|------------------|

| '0' = Bit is cleared | '1' = Bit is set |

x = Bit is unknown

bit 13-0 **REV<13:0>:** Revision ID bits

These bits are used to identify the device revision.

**Note 1:** This location cannot be written.

#### TABLE 4-1: DEVICE ID VALUES

| DEVICE      | Device ID | Revision ID |

|-------------|-----------|-------------|

| PIC12F1571  | 3051h     | 2xxxh       |

| PIC12LF1571 | 3053h     | 2xxxh       |

| PIC12F1572  | 3050h     | 2xxxh       |

| PIC12LF1572 | 3052h     | 2xxxh       |

<sup>© 2013-2015</sup> Microchip Technology Inc.

#### 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run time. See **Section 5.3 "Clock Switching**" for more information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in the Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Locked Loop, HFPLL, that can produce one of three internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Locked Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 2. The **MFINTOSC** (Medium Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

#### 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.8 "Internal Oscillator Clock Switch Timing"** for more information.

The HFINTOSC is enabled by:

- Configuring the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- Setting FOSC<1:0> = 00, or

- Setting the System Clock Source x (SCSx) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

#### 5.2.2.2 MFINTOSC

The Medium Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.8 "Internal Oscillator Clock Switch Timing"** for more information.

The MFINTOSC is enabled by:

- Configuring the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- Setting FOSC<1:0> = 00, or

- Setting the System Clock Source x (SCSx) bits of the OSCCON register to '1x'

The Medium Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

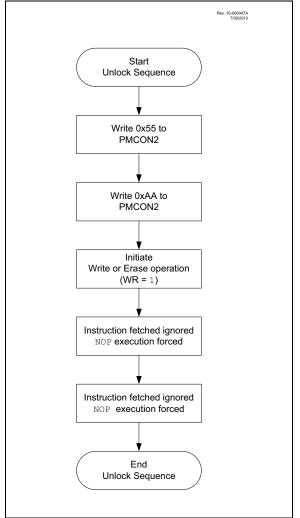

#### 10.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash program memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an erase row or program row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

#### FIGURE 10-3: F

#### FLASH PROGRAM MEMORY UNLOCK SEQUENCE FLOWCHART

#### 12.0 INTERRUPT-ON-CHANGE

The PORTA and PORTB pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The Interrupt-On-Change module has the following features:

- Interrupt-On-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 12-1 is a block diagram of the IOC module.

#### 12.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 12.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

#### 12.3 Interrupt Flags

The IOCAFx and IOCBFx bits located in the IOCAF and IOCBF registers, respectively, are status flags that correspond to the Interrupt-On-Change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx and IOCBFx bits.

#### 12.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx and IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 12-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

#### 12.5 Operation in Sleep

The Interrupt-On-Change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

#### 12.6 Register Definitions: Interrupt-On-Change Control

#### REGISTER 12-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0              | U-0                                                                            | R/W-0/0          | R/W-0/0                                                                  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|------------------|--------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------|---------|---------|---------|---------|

|                  |                                                                                |                  |                                                                          | IOCA    | P<5:0>  |         |         |

| bit 7            |                                                                                |                  |                                                                          |         |         |         | bit 0   |

|                  |                                                                                |                  |                                                                          |         |         |         |         |

| Legend:          |                                                                                |                  |                                                                          |         |         |         |         |

| R = Readable I   | bit                                                                            | W = Writable     | bit                                                                      |         |         |         |         |

| u = Bit is uncha | u = Bit is unchanged $x = Bit$ is unknown $U = Unimplemented bit, read as '0'$ |                  |                                                                          |         |         |         |         |

| '1' = Bit is set |                                                                                | '0' = Bit is cle | '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Rese |         |         |         |         |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCAP<5:0>: Interrupt-On-Change PORTA Positive Edge Enable bits

- 1 = Interrupt-On-Change is enabled on the pin for a positive going edge; IOCAFx bit and IOCIF flag will be set upon detecting an edge

- 0 = Interrupt-On-Change is disabled for the associated pin

#### REGISTER 12-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | IOCA    | N<5:0>  |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

IOCAN<5:0>: Interrupt-On-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-On-Change is enabled on the pin for a negative going edge; IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-On-Change is disabled for the associated pin

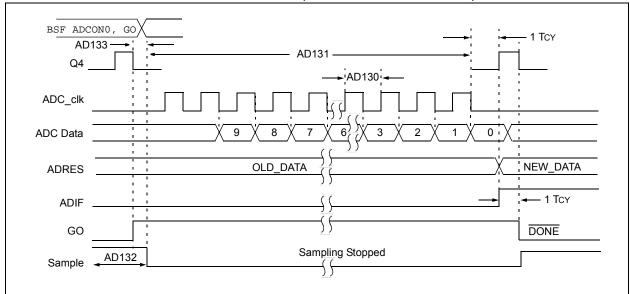

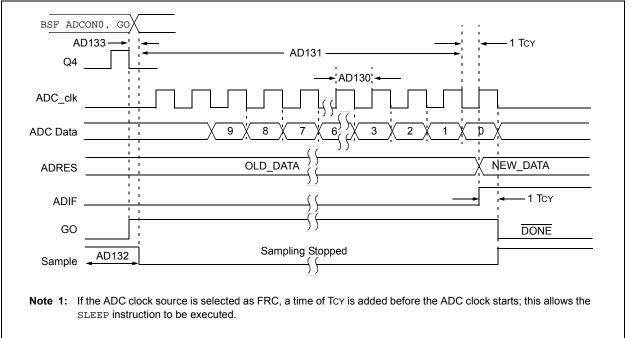

#### 15.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of                                     |

|---------|------------------------------------------------------------------------------|

|         | every conversion, regardless of whether or not the ADC interrupt is enabled. |

|         |                                                                              |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set, and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

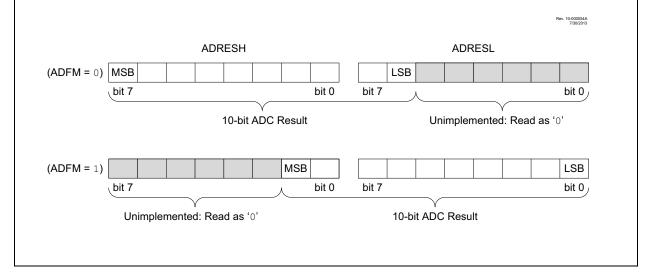

#### 15.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 15-3 shows the two output formats.

#### FIGURE 15-3: 10-BIT ADC CONVERSION RESULT FORMAT

#### 15.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure port:

- Disable pin output driver (refer to the TRISx register)

- Configure pin as analog (refer to the ANSELx register)

- Disable weak pull-ups either globally (refer to the OPTION\_REG register) or individually (refer to the appropriate WPUx register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time.<sup>(2)</sup>

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

Note 1: The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 15.4 "ADC Acquisition Requirements".

#### EXAMPLE 15-1: ADC CONVERSION

```

; This code block configures the ADC

; for polling, Vdd and Vss references, FRC

;oscillator and AN0 input.

;Conversion start & polling for completion

; are included.

BANKSEL ADCON1

;

B'11110000' ;Right justify, FRC

MOVIW

;oscillator

MOVWF

ADCON1

;Vdd and Vss Vref+

BANKSEL TRISA

BSF

TRISA,0

;Set RA0 to input

BANKSEL

ANSEL

;

BSF

ANSEL,0

;Set RA0 to analog

BANKSEL

WPUA

BCF

WPUA,0

;Disable weak

;pull-up on RA0

BANKSEL

ADCON0

;

B'00000001' ;Select channel ANO

MOVLW

MOVWF

ADCON0

;Turn ADC On

SampleTime ;Acquisiton delay

CALL

ADCON0, ADGO ; Start conversion

BSF

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

$-1

;No, test again

BANKSEL ADRESH

;

ADRESH,W ;Read upper 2 bits

MOVE

MOVWF

RESULTHI ;store in GPR space

BANKSEL

ADRESL

;

;Read lower 8 bits

MOVF

ADRESL,W

MOVWF

RESULTLO

;Store in GPR space

```

### 17.8 Register Definitions: Comparator Control

#### REGISTER 17-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0              | R-0/0                                                                                                | R/W-0/0                                                                                                                  | R/W-0/0                                                              | U-0          | R/W-0/0        | R/W-0/0       | R/W-0/0       |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------|----------------|---------------|---------------|--|--|--|

| CxON                 | CxOUT                                                                                                | CxOE                                                                                                                     | CxPOL                                                                | —            | CxSP           | CxHYS         | CxSYNC        |  |  |  |

| bit 7                |                                                                                                      |                                                                                                                          |                                                                      |              |                |               | bit 0         |  |  |  |

| • • • • • •          |                                                                                                      |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

| Legend:              | - 1-:4                                                                                               |                                                                                                                          | L :4                                                                 |              |                |               |               |  |  |  |

| R = Readable         |                                                                                                      |                                                                                                                          | W = Writable bitx = Bit is unknownU = Unimplemented bit, read as '0' |              |                |               |               |  |  |  |

| u = Bit is unchanged |                                                                                                      | x = Bit is unkr                                                                                                          |                                                                      | -            |                |               |               |  |  |  |

| '1' = Bit is set     | t                                                                                                    | $0^{\circ} = Bit is cle$                                                                                                 | '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all oth    |              |                |               |               |  |  |  |

| bit 7                | CxON: Com                                                                                            | parator Enable                                                                                                           | bit                                                                  |              |                |               |               |  |  |  |

|                      | 1 = Compara                                                                                          | ator is enabled                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      | 0 = Compara                                                                                          | Comparator is disabled and consumes no active power                                                                      |                                                                      |              |                |               |               |  |  |  |

| bit 6                | CxOUT: Cor                                                                                           | mparator Output                                                                                                          | bit                                                                  |              |                |               |               |  |  |  |

|                      | If CxPOL = 1 (inverted polarity):                                                                    |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      | 1 = CxVP < CxVN $0 = CxVP > CxVN$                                                                    |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      |                                                                                                      |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      | If CxPOL = 0 (non-inverted polarity):<br>1 = CxVP > CxVN                                             |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      | 0 = CxVP <                                                                                           | CxVN                                                                                                                     |                                                                      |              |                |               |               |  |  |  |

| bit 5                | CxOE: Comparator Output Enable bit                                                                   |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      | 1 = CxOUT is present on the CxOUT pin; requires that the associated TRISx bit be cleared to actually |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      |                                                                                                      | drive the pin, not affected by CxON<br>0 = CxOUT is internal only                                                        |                                                                      |              |                |               |               |  |  |  |

| L:1 4                |                                                                                                      | -                                                                                                                        |                                                                      |              |                |               |               |  |  |  |

| bit 4                | CxPOL: Comparator Output Polarity Select bit                                                         |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      | <ol> <li>Comparator output is inverted</li> <li>Comparator output is not inverted</li> </ol>         |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

| bit 3                | -                                                                                                    | nted: Read as '                                                                                                          |                                                                      |              |                |               |               |  |  |  |

| bit 2                | CxSP: Comparator Speed/Power Select bit                                                              |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      | 1 = Comparator mode is in Normal Power, Higher Speed mode                                            |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      | 0 = Comparator mode is in Low-Power, Low-Speed mode                                                  |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

| bit 1                | CxHYS: Cor                                                                                           | mparator Hyster                                                                                                          | esis Enable bit                                                      |              |                |               |               |  |  |  |

|                      | 1 = Comparator hysteresis is enabled                                                                 |                                                                                                                          |                                                                      |              |                |               |               |  |  |  |

|                      | 0 = Compar                                                                                           | ator hysteresis                                                                                                          | is disabled                                                          |              |                |               |               |  |  |  |

| bit 0                |                                                                                                      | omparator Outp                                                                                                           |                                                                      |              |                |               |               |  |  |  |

|                      |                                                                                                      |                                                                                                                          |                                                                      |              | ronous to chan | ges on Timer1 | clock source; |  |  |  |

|                      |                                                                                                      | output updated on the falling edge of Timer1 clock source<br>0 = Comparator output to Timer1 and I/O pin is asynchronous |                                                                      |              |                |               |               |  |  |  |

|                      |                                                                                                      |                                                                                                                          |                                                                      | an is asynom | 01000          |               |               |  |  |  |

#### 19.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit Timer/Counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- · 2-bit prescaler

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- ADC auto-conversion trigger(s)

- Selectable gate source polarity

- Gate Toggle mode

- · Gate Single-Pulse mode

- Gate value status

- Gate event interrupt

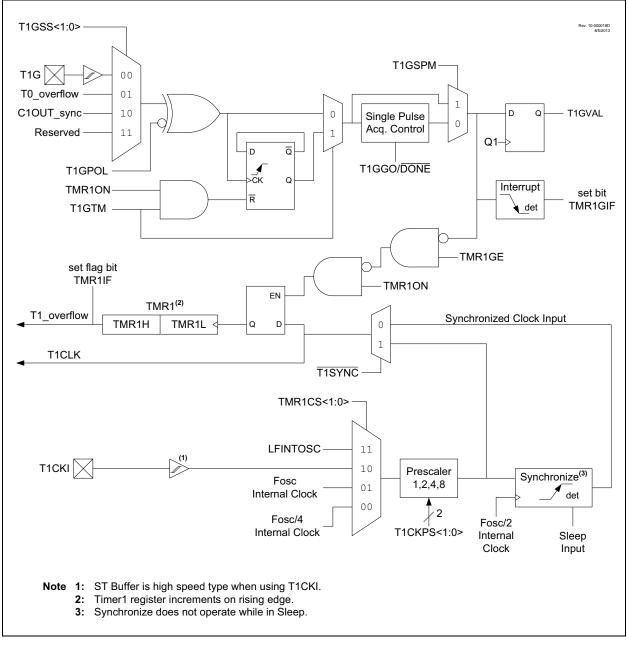

- Figure 19-1 is a block diagram of the Timer1 module.

#### FIGURE 19-1: TIMER1 BLOCK DIAGRAM

#### 21.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 21-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 21.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSELx bit must be cleared for the receiver to function.

#### 21.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds, then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character; otherwise, the framing error is cleared for this character. See Section 21.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

Note: If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See Section 21.1.2.5 "Receive Overrun Error" for more information on overrun errors.

#### 21.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 21.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character, the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two-character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |

|-------|--------------------------------------------|

|       | the corresponding ANSELx bit must be       |

|       | cleared for the receiver to function.      |

#### 21.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSELx bit must be cleared.

#### 21.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens, the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear, then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set, then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 21.5.1.8 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9 bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 21.5.1.9 Synchronous Master Reception Setup

- 1. Initialize the SPBRGH/SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSELx bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 4. Ensure bits, CREN and SREN, are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register, and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit, RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit, RCIF, will be set when reception of a character is complete. An interrupt will be generated if the enable bit, RCIE, was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

### PIC12(L)F1571/2

| U-0                                                 | U-0               | U-0                                 | U-0            | R/W/HS-0/0     | R/W/HS-0/0       | R/W/HS-0/0       | R/W/HS-0/0   |  |

|-----------------------------------------------------|-------------------|-------------------------------------|----------------|----------------|------------------|------------------|--------------|--|

| _                                                   | —                 | —                                   | —              | OFIF           | PHIF             | DCIF             | PRIF         |  |

| bit 7                                               |                   |                                     |                |                |                  |                  | bit 0        |  |

|                                                     |                   |                                     |                |                |                  |                  |              |  |

| Legend:                                             |                   |                                     |                |                |                  |                  |              |  |

| HC = Hardwa                                         | are Clearable bit | HS = Hardwar                        | e Settable bit |                |                  |                  |              |  |

| R = Readabl                                         | le bit            | W = Writable                        | bit            | U = Unimplem   | nented bit, read | l as '0'         |              |  |

| '1' = Bit is se                                     | et                | '0' = Bit is clea                   | ared           | -n/n = Value a | t POR and BO     | R/Value at all o | other Resets |  |

|                                                     |                   |                                     |                |                |                  |                  |              |  |

| bit 7-4                                             | Unimplement       | ted: Read as '0                     | 3              |                |                  |                  |              |  |

| bit 3                                               | OFIF: Offset I    | nterrupt Flag bit                   | (1)            |                |                  |                  |              |  |

|                                                     |                   | atch event occu                     |                |                |                  |                  |              |  |

|                                                     |                   | atch event did n                    |                |                |                  |                  |              |  |

| bit 2 PHIF: Phase Interrupt Flag bit <sup>(1)</sup> |                   |                                     |                |                |                  |                  |              |  |

|                                                     |                   | atch event occu<br>atch event did n |                |                |                  |                  |              |  |

| bit 1                                               |                   | ycle Interrupt Fl                   |                |                |                  |                  |              |  |

|                                                     |                   | e match event of                    |                |                |                  |                  |              |  |

|                                                     |                   | e match event of                    |                | r              |                  |                  |              |  |

| bit 0                                               |                   |                                     |                |                |                  |                  |              |  |

|                                                     |                   | atch event occu                     |                |                |                  |                  |              |  |

|                                                     | 0 = Period ma     | atch event did n                    | ot occur       |                |                  |                  |              |  |

|                                                     |                   |                                     |                |                |                  |                  |              |  |

#### REGISTER 22-3: PWMxINTF: PWMx INTERRUPT REQUEST REGISTER

Note 1: Bit is forced clear by hardware while module is disabled (EN = 0).

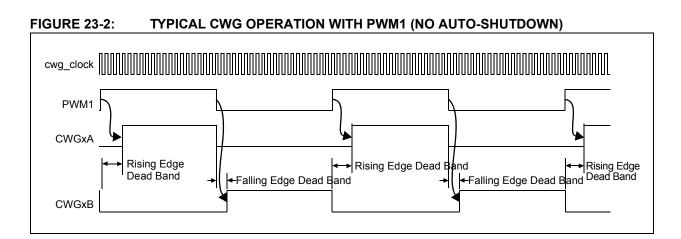

#### 23.5 Dead-Band Control

Dead-band control provides for non-overlapping output signals to prevent shoot-through current in power switches. The CWG contains two 6-bit dead-band counters. One dead-band counter is used for the rising edge of the input source control. The other is used for the falling edge of the input source control.

Dead band is timed by counting CWG clock periods from zero, up to the value in the rising or falling Dead-Band Counter registers. See the CWGxDBR and CWGxDBF registers (Register 23-4 and Register 23-5, respectively).

#### 23.6 Rising Edge Dead Band

The rising edge dead band delays the turn-on of the CWGxA output from when the CWGxB output is turned off. The rising edge dead-band time starts when the rising edge of the input source signal goes true. When this happens, the CWGxB output is immediately turned off and the rising edge dead-band delay time starts. When the rising edge dead-band delay time is reached, the CWGxA output is turned on.

The CWGxDBR register sets the duration of the deadband interval on the rising edge of the input source signal. This duration is from 0 to 64 counts of dead band.

Dead band is always counted off the edge on the input source signal. A count of 0 (zero), indicates that no dead band is present.

If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

#### 23.7 Falling Edge Dead Band

The falling edge dead band delays the turn-on of the CWGxB output from when the CWGxA output is turned off. The falling edge dead-band time starts when the falling edge of the input source goes true. When this happens, the CWGxA output is immediately turned off and the falling edge dead-band delay time starts. When the falling edge dead-band delay time is reached, the CWGxB output is turned on.

The CWGxDBF register sets the duration of the deadband interval on the falling edge of the input source signal. This duration is from 0 to 64 counts of dead band.

Dead band is always counted off the edge on the input source signal. A count of 0 (zero), indicates that no dead band is present.

If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

Refer to Figure 23-3 and Figure 23-4 for examples.

#### 23.12 Register Definitions: CWG Control

#### REGISTER 23-1: CWGxCON0: CWGx CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                                                                                                                      | R/W-0/0                                                                                    | R/W-0/0 | R/W-0/0        | U-0              | U-0            | R/W-0/0      |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|----------------|------------------|----------------|--------------|--|--|--|

| GxEN             | GxOEB                                                                                                                        | GxOEA                                                                                      | GxPOLB  | GxPOLA         | —                | _              | GxCS0        |  |  |  |

| bit 7            | •                                                                                                                            | •                                                                                          |         | •              |                  | •              | bit 0        |  |  |  |

|                  |                                                                                                                              |                                                                                            |         |                |                  |                |              |  |  |  |

| Legend:          |                                                                                                                              |                                                                                            |         |                |                  |                |              |  |  |  |

| R = Readable     | e bit                                                                                                                        | W = Writable                                                                               | bit     |                |                  |                |              |  |  |  |

| u = Bit is uncl  | hanged                                                                                                                       | x = Bit is unkr                                                                            | nown    | U = Unimpler   | mented bit, read | as '0'         |              |  |  |  |

| '1' = Bit is set |                                                                                                                              | '0' = Bit is cle                                                                           | ared    | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |  |  |  |

|                  |                                                                                                                              |                                                                                            |         |                |                  |                |              |  |  |  |

| bit 7            | GxEN: CWG                                                                                                                    | x Enable bit                                                                               |         |                |                  |                |              |  |  |  |

|                  | 1 = Module i                                                                                                                 | 1 = Module is enabled                                                                      |         |                |                  |                |              |  |  |  |

|                  | 0 = Module i                                                                                                                 | 0 = Module is disabled                                                                     |         |                |                  |                |              |  |  |  |

| bit 6            | GxOEB: CWGxB Output Enable bit                                                                                               |                                                                                            |         |                |                  |                |              |  |  |  |

|                  | 1 = CWGxB is available on appropriate I/O pin                                                                                |                                                                                            |         |                |                  |                |              |  |  |  |

|                  | 0 = CWGxB                                                                                                                    | 0 = CWGxB is not available on appropriate I/O pin                                          |         |                |                  |                |              |  |  |  |

| bit 5            | GxOEA: CWGxA Output Enable bit                                                                                               |                                                                                            |         |                |                  |                |              |  |  |  |

|                  | <ul> <li>1 = CWGxA is available on appropriate I/O pin</li> <li>0 = CWGxA is not available on appropriate I/O pin</li> </ul> |                                                                                            |         |                |                  |                |              |  |  |  |

| L:1 4            |                                                                                                                              |                                                                                            |         | te i/O pin     |                  |                |              |  |  |  |

| bit 4            |                                                                                                                              | NGxB Output F                                                                              | •       |                |                  |                |              |  |  |  |

|                  |                                                                                                                              | <ul> <li>1 = Output is inverted polarity</li> <li>0 = Output is normal polarity</li> </ul> |         |                |                  |                |              |  |  |  |

| bit 3            | •                                                                                                                            |                                                                                            | •       |                |                  |                |              |  |  |  |

| bit 5            |                                                                                                                              | <b>GxPOLA:</b> CWGxA Output Polarity bit<br>1 = Output is inverted polarity                |         |                |                  |                |              |  |  |  |

|                  | •                                                                                                                            | 0 = Output is normal polarity                                                              |         |                |                  |                |              |  |  |  |

| bit 2-1          | •                                                                                                                            | ted: Read as '                                                                             |         |                |                  |                |              |  |  |  |

| bit 0            | •                                                                                                                            | Gx Clock Source                                                                            |         |                |                  |                |              |  |  |  |

|                  | 1 = HFINTO                                                                                                                   |                                                                                            |         |                |                  |                |              |  |  |  |

|                  | 0 = Fosc                                                                                                                     | ~~                                                                                         |         |                |                  |                |              |  |  |  |

## PIC12(L)F1571/2

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                            |  |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                               |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                               |  |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                          |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |  |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                        |  |  |  |  |

| Operands:        | None                                                                                                                                                  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                  |  |  |  |  |

| Status Affected: | None                                                                                                                                                  |  |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the Program Counter.<br>This is a 2-cycle instruction. |  |  |  |  |

| RETLW            | Return with literal in W                                                                                                                                                      | RLF              | Rotate Left f through Carry                                                                                                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |

| Operands:        | $0 \le k \le 255$                                                                                                                                                             | Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                               |

| Operation:       | $k \rightarrow (W);$                                                                                                                                                          |                  | $d \in [0,1]$                                                                                                                                                                                                     |

|                  | $TOS \rightarrow PC$                                                                                                                                                          | Operation:       | See description below                                                                                                                                                                                             |

| Status Affected: | None                                                                                                                                                                          | Status Affected: | С                                                                                                                                                                                                                 |

| Description:     | The W register is loaded with the 8-bit<br>literal 'k'. The Program Counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| Words:           | 1                                                                                                                                                                             |                  | ← C ← Register f ←                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                             | Words:           | 1                                                                                                                                                                                                                 |

| Example:         | CALL TABLE;W contains table                                                                                                                                                   |                  |                                                                                                                                                                                                                   |

|                  | ; offset value                                                                                                                                                                | Cycles:          | 1                                                                                                                                                                                                                 |

| TABLE            | <ul> <li>;W now has table value</li> </ul>                                                                                                                                    | Example:         | RLF REG1,0                                                                                                                                                                                                        |

|                  | •                                                                                                                                                                             |                  | Before Instruction                                                                                                                                                                                                |

|                  | ADDWF PC ;W = offset                                                                                                                                                          |                  | REG1 = 1110 0110                                                                                                                                                                                                  |

|                  | RETLW k1 ;Begin table                                                                                                                                                         |                  | C = 0<br>After Instruction                                                                                                                                                                                        |

|                  | RETLW k2 ;                                                                                                                                                                    |                  | REG1 = 1110 0110                                                                                                                                                                                                  |

|                  | •                                                                                                                                                                             |                  | W = 1100 1100                                                                                                                                                                                                     |

|                  | •                                                                                                                                                                             |                  | C = 1                                                                                                                                                                                                             |

|                  | RETLW kn ; End of table                                                                                                                                                       |                  |                                                                                                                                                                                                                   |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                                                                        |                  |                                                                                                                                                                                                                   |

#### TABLE 26-4: I/O PORTS

| Standard      | d Operati | ing Conditions (unless otherwi       | se stated)      |        |          |       |                                                                            |

|---------------|-----------|--------------------------------------|-----------------|--------|----------|-------|----------------------------------------------------------------------------|

| Param.<br>No. | Sym.      | Characteristic                       | Min.            | Тур†   | Max.     | Units | Conditions                                                                 |

|               | VIL       | Input Low Voltage                    |                 |        |          |       |                                                                            |

|               |           | I/O Ports:                           |                 |        |          |       |                                                                            |

| D030          |           | with TTL Buffer                      | —               | _      | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |

| D030A         |           |                                      | —               | _      | 0.15 VDD | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |