Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 6                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1571-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

# 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory, 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a Software Reset. See **Section 3.5 "Stack"** for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

# 2.4 Instruction Set

There are 49 instructions for the enhanced midrange CPU to support the features of the CPU. See **Section 25.0 "Instruction Set Summary"** for more details.

| Addr              | Name            | Bit 7        | Bit 6         | Bit 5          | Bit 4         | Bit 3        | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>Resets |

|-------------------|-----------------|--------------|---------------|----------------|---------------|--------------|--------|---------|--------|----------------------|---------------------------------|

| Bank              | 31              |              |               |                |               |              |        |         |        |                      |                                 |

| F8Ch<br>—<br>FE3h | _               | Unimpleme    | nted          |                |               |              |        |         |        | -                    | _                               |

| FE4h              | STATUS_<br>SHAD | _            | -             | _              | -             | -            | Z_SHAD | DC_SHAD | C_SHAD | xxx                  | uuu                             |

| FE5h              | WREG_<br>SHAD   | Working Re   | egister Shado | w              |               |              |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FE6h              | BSR_<br>SHAD    | _            | _             | _              | Bank Select   | Register Sha | dow    |         |        | x xxxx               | u uuuu                          |

| FE7h              | PCLATH_<br>SHAD | -            | Program Co    | ounter Latch H | ligh Register | Shadow       |        |         |        | -xxx xxxx            | uuuu uuuu                       |

| FE8h              | FSR0L_<br>SHAD  | Indirect Dat | a Memory Ad   | dress 0 Low    | Pointer Shade | OW           |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| FE9h              | FSR0H_<br>SHAD  | Indirect Dat | a Memory Ad   | ddress 0 High  | Pointer Shad  | low          |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEAh              | FSR1L_<br>SHAD  | Indirect Dat | a Memory Ad   | dress 1 Low    | Pointer Shade | OW           |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| FEBh              | FSR1H_<br>SHAD  | Indirect Dat | a Memory Ad   | ldress 1 High  | Pointer Shad  | low          |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| FECh              | —               | Unimpleme    | nted          |                |               |              |        |         |        | —                    | _                               |

| FEDh              | STKPTR          | _            | —             | _              | Current Stac  | k Pointer    |        |         |        | 1 1111               | 1 1111                          |

| FEEh              | TOSL            | Top-of-Stac  | k Low Byte    |                |               |              |        |         |        | XXXX XXXX            | uuuu uuuu                       |

SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-10**:

FEFh TOSH Top-of-Stack High Byte \_

Legend: x = unknown; u = unchanged; q = value depends on condition; — = unimplemented; r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: PIC12F1571/2 only. 2: PIC12(L)F1572 only.

3: Unimplemented, read as '1'.

-xxx xxxx -uuu uuuu

#### 4.2 **Register Definitions: Configuration Words**

#### U-1 U-1 R/P-1 **R/P-1** U-1 R/P-1 **CLKOUTEN** BOREN<1:0>(1) bit 13 bit 8 R/P-1 R/P-1 R/P-1 R/P-1 U-1 R/P-1 R/P-1 R/P-1 $\overline{CP}^{(2)}$ MCLRE PWRTF<sup>(1)</sup> WDTE<1:0> FOSC<1:0> bit 7 bit 0 Legend: R = Readable bit U = Unimplemented bit, read as '1' P = Programmable bit 0' = Bit is cleared n = Value when blank or after bulk erase '1' = Bit is set bit 13-12 Unimplemented: Read as '1' **CLKOUTEN:** Clock Out Enable bit bit 11 1 = Off – CLKOUT function is disabled; I/O or oscillator function on CLKOUT pin 0 = On - CLKOUT function is enabled on CLKOUT pin BOREN<1:0>: Brown-out Reset Enable bits(1) bit 10-9 11 = On- Brown-out Reset is enabled; the SBOREN bit is ignored - Brown-out Reset is enabled while running and disabled in Sleep; the SBOREN bit is ignored 10 = Sleep01 = SBODEN - Brown-out Reset is controlled by the SBOREN bit in the BORCON register - Brown-out Reset is disabled; the SBOREN bit is ignored 00 = OffUnimplemented: Read as '1' bit 8 CP: Flash Program Memory Code Protection bit<sup>(2)</sup> bit 7 1 = Off - Code protection is off; program memory can be read and written 0 = On – Code protection is on; program memory cannot be read or written externally bit 6 MCLRE: MCLR/VPP Pin Function Select bit If LVP bit = 1 (On): This bit is ignored. MCLR/VPP pin function is MCLR; weak pull-up is enabled. If LVP bit = 0 (Off): $1 = On - \overline{MCLR}/VPP$ pin function is $\overline{MCLR}$ ; weak pull-up is enabled 0 = Off - MCLR/VPP pin function is a digital input, MCLR is internally disabled; weak pull-up is under control of pin's WPU control bit **PWRTE:** Power-up Timer Enable bit<sup>(1)</sup> bit 5 1 = Off - PWRT is disabled 0 = On - PWRT is enabled bit 4-3 WDTE<1:0>: Watchdog Timer Enable bits - WDT is enabled; SWDTEN is ignored 11 = On10 = Sleep WDT is enabled while running and disabled in Sleep; SWDTEN is ignored 01 = SWDTEN – WDT is controlled by the SWDTEN bit in the WDTCON register WDT is disabled; SWDTEN is ignored 00 = Offbit 2 Unimplemented: Read as '1' bit 1-0 FOSC<1:0>: Oscillator Selection bits 11 = ECH - External Clock, High-Power mode: CLKI on CLKI - External Clock, Medium Power mode: CLKI on CLKI 10 = ECM - External Clock, Low-Power mode: CLKI on CLKI 01 = ECL 00 = INTOSC - I/O function on CLKI Note 1: Enabling Brown-out Reset does not automatically enable the Power-up Timer.

#### **REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1**

Once enabled, code-protect can only be disabled by bulk erasing the device. 2:

# 10.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat Steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 10-5 (row writes to program memory with 16 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper 11 bits of PMADRH:PMADRL (PMADRH<6:0>:PMADRL<7:4>), with the lower 4 bits of PMADRL (PMADRL<3:0>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF.

The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

Note: The special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. If the unlock sequence is interrupted, writing to the latches or program memory will not be initiated.

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- 6. Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat Steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- 11. Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- **Note:** The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 10-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using Indirect Addressing.

| ADC Clock              | Period (TAD) |            | Device Frequency (Fosc) |            |            |            |  |  |  |  |

|------------------------|--------------|------------|-------------------------|------------|------------|------------|--|--|--|--|

| ADC<br>Clock<br>Source | ADCS<2:0>    | 20 MHz     | 16 MHz                  | 8 MHz      | 4 MHz      | 1 MHz      |  |  |  |  |

| Fosc/2                 | 000          | 100 ns     | 125 ns                  | 250 ns     | 500 ns     | 2.0 μs     |  |  |  |  |

| Fosc/4                 | 100          | 200 ns     | 250 ns                  | 500 ns     | 1.0 μs     | 4.0 μs     |  |  |  |  |

| Fosc/8                 | 001          | 400 ns     | 500 ns                  | 1.0 μs     | 2.0 μs     | 8.0 μs     |  |  |  |  |

| Fosc/16                | 101          | 800 ns     | 1.0 μs                  | 2.0 μs     | 4.0 μs     | 16.0 μs    |  |  |  |  |

| Fosc/32                | 010          | 1.6 μs     | 2.0 μs                  | 4.0 μs     | 8.0 μs     | 32.0 μs    |  |  |  |  |

| Fosc/64                | 110          | 3.2 μs     | 4.0 μs                  | 8.0 μs     | 16.0 μs    | 64.0 μs    |  |  |  |  |

| FRC                    | x11          | 1.0-6.0 μs | 1.0-6.0 μs              | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs |  |  |  |  |

## TABLE 15-1: ADC CLOCK PERIOD (TAD) VS. DEVICE OPERATING FREQUENCIES

**Legend:** Shaded cells are outside of recommended range.

**Note:** The TAD period when using the FRC clock source can fall within a specified range (see TAD parameter). The TAD period when using the FOSC-based clock source can be configured for a more precise TAD period. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

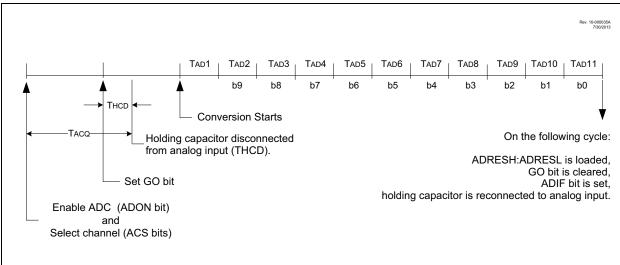

#### FIGURE 15-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

| Name   | Bit 7    | Bit 6                    | Bit 5               | Bit 4               | Bit 3 | Bit 2   | Bit 1         | Bit 0  | Register<br>on Page |

|--------|----------|--------------------------|---------------------|---------------------|-------|---------|---------------|--------|---------------------|

| ADCON0 |          |                          |                     | CHS<4:0>            |       |         | GO/DONE       | ADON   | 135                 |

| ADCON1 | ADFM     |                          | ADCS<2:0>           | >                   | —     | —       | — ADPREF<1:0> |        |                     |

| ADCON2 |          | TRIGSE                   | EL<3:0>             |                     | —     | —       | _             | _      | 137                 |

| ADRESH | ADC Resu | ADC Result Register High |                     |                     |       |         |               |        |                     |

| ADRESL | ADC Resu | lt Register I            | _OW                 |                     |       |         |               |        | 138, 139            |

| ANSELA |          | _                        | _                   | ANSA4               | _     |         | ANSA<2:0>     | 114    |                     |

| INTCON | GIE      | PEIE                     | TMR0IE              | INTE                | IOCIE | TMR0IF  | INTF          | IOCIF  | 74                  |

| PIE1   | TMR1GIE  | ADIE                     | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | —     | —       | TMR2IE        | TMR1IE | 75                  |

| PIR1   | TMR1GIF  | ADIF                     | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | _     | _       | TMR2IF        | TMR1IF | 78                  |

| TRISA  | _        | _                        | TRISA5              | TRISA4              | _(1)  |         | TRISA<2:0>    | •      | 113                 |

| FVRCON | FVREN    | FVRRDY                   | TSEN                | TSRNG               | CDAFV | /R<1:0> | ADFVF         | R<1:0> | 125                 |

|        |          |                          |                     |                     |       |         |               |        |                     |

## TABLE 15-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: — = unimplemented, read as '0'. Shaded cells are not used for the ADC module.

**Note 1:** Unimplemented, read as '1'.

2: PIC12(L)F1572 only.

# 19.8 Register Definitions: Timer1 Control

# REGISTER 19-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | U-0 | R/W-0/u | U-0 | R/W-0/u |

|---------|---------|---------|---------|-----|---------|-----|---------|

| TMR1C   | S<1:0>  | T1CKP   | 'S<1:0> |     | T1SYNC  | _   | TMR10N  |

| bit 7   |         |         |         |     |         |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

| bit 7-6 | <b>TMR1CS&lt;1:0&gt;:</b> Timer1 Clock Source Select bits<br>11 = Timer1 clock source is the LFINTOSC<br>10 = Timer1 clock source is the T1CKI pin (on the rising edge) |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 01 = Timer1 clock source is the system clock (Fosc)<br>00 = Timer1 clock source is the instruction clock (Fosc/4)                                                       |

| bit 5-4 | <b>T1CKPS&lt;1:0&gt;:</b> Timer1 Input Clock Prescale Select bits                                                                                                       |

|         | <ul> <li>11 = 1:8 Prescale value</li> <li>10 = 1:4 Prescale value</li> <li>01 = 1:2 Prescale value</li> <li>00 = 1:1 Prescale value</li> </ul>                          |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                              |

| bit 2   | T1SYNC: Timer1 Synchronization Control bit                                                                                                                              |

|         | <ul> <li>1 = Does not synchronize the asynchronous clock input</li> <li>0 = Synchronizes the asynchronous clock input with the system clock (Fosc)</li> </ul>           |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                              |

| bit 0   | TMR1ON: Timer1 On bit<br>1 = Enables Timer1<br>0 = Stops Timer1 and clears Timer1 gate flip-flop                                                                        |

NOTES:

|                         | R/W-0/0                                                                                                                                                                         | R/W-0/0                                                                                                                                                                                            | R/W-0/0                                                                                                       | R/W-0/0         | R-0/0                                | R-0/0          | R-0/0    |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------|----------------|----------|--|--|--|--|

| SPEN                    | RX9                                                                                                                                                                             | SREN                                                                                                                                                                                               | CREN                                                                                                          | ADDEN           | FERR                                 | OERR           | RX9D     |  |  |  |  |

| bit 7                   | •                                                                                                                                                                               |                                                                                                                                                                                                    | •                                                                                                             |                 |                                      |                | bit (    |  |  |  |  |

|                         |                                                                                                                                                                                 |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

| Legend:                 |                                                                                                                                                                                 |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

| R = Readable            | bit                                                                                                                                                                             | W = Writable                                                                                                                                                                                       | bit                                                                                                           |                 |                                      |                |          |  |  |  |  |

| u = Bit is unch         | nanged                                                                                                                                                                          | x = Bit is unkr                                                                                                                                                                                    | nown                                                                                                          | U = Unimplen    | nented bit, read                     | as '0'         |          |  |  |  |  |

| '1' = Bit is set        |                                                                                                                                                                                 | '0' = Bit is cle                                                                                                                                                                                   | '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all oth                                             |                 |                                      |                |          |  |  |  |  |

| <b>h</b> # 7            |                                                                                                                                                                                 | l Dant Enable bi                                                                                                                                                                                   |                                                                                                               |                 |                                      |                |          |  |  |  |  |

| bit 7                   |                                                                                                                                                                                 | <ul> <li>PEN: Serial Port Enable bit</li> <li>Serial port is enabled (configures RX/DT and TX/CK pins as serial port pins)</li> </ul>                                                              |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         |                                                                                                                                                                                 | ort is disabled (I                                                                                                                                                                                 |                                                                                                               |                 | pins as senai p                      | ort pins)      |          |  |  |  |  |

| bit 6                   | <b>RX9:</b> 9-Bit R                                                                                                                                                             | eceive Enable I                                                                                                                                                                                    | pit                                                                                                           |                 |                                      |                |          |  |  |  |  |

|                         |                                                                                                                                                                                 | 9-bit reception<br>8-bit reception                                                                                                                                                                 |                                                                                                               |                 |                                      |                |          |  |  |  |  |

| bit 5                   | SREN: Single Receive Enable bit                                                                                                                                                 |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         | Asynchronous mode:<br>Don't care.                                                                                                                                               |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         | Synchronous mode – Master:                                                                                                                                                      |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         | <ul> <li>1 = Enables single receive</li> <li>0 = Disables single receive</li> </ul>                                                                                             |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         |                                                                                                                                                                                 | This bit is cleared after reception is complete.                                                                                                                                                   |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         |                                                                                                                                                                                 | hronous mode – Slave:                                                                                                                                                                              |                                                                                                               |                 |                                      |                |          |  |  |  |  |

| bit 4                   | CREN: Continuous Receive Enable bit                                                                                                                                             |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         | Asynchronou                                                                                                                                                                     |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         | 1 = Enables                                                                                                                                                                     | 1 = Enables receiver                                                                                                                                                                               |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         | 0 = Disables                                                                                                                                                                    |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         | Synchronous mode:                                                                                                                                                               |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul>                              |                                                                                                                                                                                                    |                                                                                                               |                 |                                      |                |          |  |  |  |  |

|                         | 0 = Disables                                                                                                                                                                    | s continuous red                                                                                                                                                                                   | eive                                                                                                          |                 |                                      |                |          |  |  |  |  |

| bit 3                   |                                                                                                                                                                                 | s continuous rec<br>dress Detect En                                                                                                                                                                |                                                                                                               |                 |                                      |                |          |  |  |  |  |

| bit 3                   | ADDEN: Add                                                                                                                                                                      |                                                                                                                                                                                                    | able bit                                                                                                      |                 |                                      |                |          |  |  |  |  |

| bit 3                   | ADDEN: Add<br>Asynchronou<br>1 = Enables                                                                                                                                        | dress Detect En<br><u>is mode 9-bit (F</u><br>address detect                                                                                                                                       | able bit<br>2 <u>X9 = 1):</u><br>ion, enables ir                                                              | •               |                                      |                |          |  |  |  |  |

| bit 3                   | ADDEN: Add<br>Asynchronou<br>1 = Enables<br>0 = Disables                                                                                                                        | dress Detect En<br><u>is mode 9-bit (F</u><br>address detect<br>address detect                                                                                                                     | able bit<br>2 <u>X9 = 1):</u><br>ion, enables ir<br>tion, all bytes                                           | •               |                                      |                |          |  |  |  |  |

| bit 3                   | ADDEN: Add<br>Asynchronou<br>1 = Enables<br>0 = Disables<br>Asynchronou                                                                                                         | dress Detect En<br><u>is mode 9-bit (F</u><br>address detect                                                                                                                                       | able bit<br>2 <u>X9 = 1):</u><br>ion, enables ir<br>tion, all bytes                                           | •               |                                      |                |          |  |  |  |  |

|                         | ADDEN: Add<br>Asynchronou<br>1 = Enables<br>0 = Disables<br>Asynchronou<br>Don't care.                                                                                          | dress Detect En<br>is mode 9-bit (F<br>address detect<br>address detec<br>is mode 8-bit (F                                                                                                         | able bit<br>2 <u>X9 = 1):</u><br>ion, enables ir<br>tion, all bytes                                           | •               |                                      |                |          |  |  |  |  |

|                         | ADDEN: Add<br>Asynchronou<br>1 = Enables<br>0 = Disables<br>Asynchronou<br>Don't care.<br>FERR: Fram                                                                            | dress Detect En<br>is mode 9-bit (F<br>address detect<br>address detect<br>is mode 8-bit (F<br>ing Error bit                                                                                       | able bit<br>(X9 = 1):<br>ion, enables in<br>tion, all bytes<br>(X9 = 0):                                      | are received ar | nd ninth bit can                     | be used as par | rity bit |  |  |  |  |

|                         | ADDEN: Add<br>Asynchronou<br>1 = Enables<br>0 = Disables<br>Asynchronou<br>Don't care.<br>FERR: Fram                                                                            | dress Detect En<br><u>is mode 9-bit (F</u><br>address detect<br>address detect<br>address detect<br><u>is mode 8-bit (F</u><br>ing Error bit<br>error (can be u                                    | able bit<br>(X9 = 1):<br>ion, enables in<br>tion, all bytes<br>(X9 = 0):                                      | are received ar | nd ninth bit can                     | be used as par | rity bit |  |  |  |  |

| bit 3<br>bit 2<br>bit 1 | ADDEN: Add<br>Asynchronou<br>1 = Enables<br>0 = Disables<br>Asynchronou<br>Don't care.<br>FERR: Fram<br>1 = Framing                                                             | dress Detect En<br><u>is mode 9-bit (F</u><br>address detect<br>address detect<br><u>is mode 8-bit (F</u><br>ing Error bit<br>error (can be u<br>ing error                                         | able bit<br>(X9 = 1):<br>ion, enables in<br>tion, all bytes<br>(X9 = 0):                                      | are received ar | nd ninth bit can                     | be used as par | rity bit |  |  |  |  |

| bit 2                   | ADDEN: Add<br>Asynchronou<br>1 = Enables<br>0 = Disables<br>Asynchronou<br>Don't care.<br>FERR: Fram<br>1 = Framing<br>0 = No frami<br>OERR: Over<br>1 = Overrun                | dress Detect En<br>is mode 9-bit (F<br>address detect<br>address detect<br>address detect<br>is mode 8-bit (F<br>ing Error bit<br>error (can be u<br>ing error<br>run Error bit<br>error (can be c | able bit<br>(X9 = 1):<br>ion, enables in<br>tion, all bytes<br>(X9 = 0):<br>pdated by rea                     | are received ar | nd ninth bit can<br>egister and rece | be used as par | rity bit |  |  |  |  |

| bit 2                   | ADDEN: Add<br>Asynchronou<br>1 = Enables<br>0 = Disables<br>Asynchronou<br>Don't care.<br>FERR: Fram<br>1 = Framing<br>0 = No frami<br>OERR: Over<br>1 = Overrun<br>0 = No over | dress Detect En<br>is mode 9-bit (F<br>address detect<br>address detect<br>address detect<br>is mode 8-bit (F<br>ing Error bit<br>error (can be u<br>ing error<br>run Error bit<br>error (can be c | able bit<br>(2X9 = 1):<br>ion, enables in<br>tion, all bytes<br>(2X9 = 0):<br>pdated by rea<br>leared by clea | are received ar | nd ninth bit can<br>egister and rece | be used as par | rity bit |  |  |  |  |

# REGISTER 21-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

# 21.4.2 AUTO-BAUD OVERFLOW

During the course of Automatic Baud Detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRGL register pair. The overflow condition will set the RCIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge, at which time, the RDICL bit will set. If the RCREG is read after the overflow occurs, but before the fifth rising edge, the fifth rising edge will set the RCIF again.

Terminating the auto-baud process early to clear an overflow condition will prevent proper detection of the Sync character fifth rising edge. If any falling edges of the Sync character have not yet occurred when the ABDEN bit is cleared, then those will be falsely detected as Start bits. The following steps are recommended to clear the overflow condition:

- 1. Read RCREG to clear RCIF.

- 2. If RCIDL is zero, then wait for RCIF and repeat Step 1.

- 3. Clear the ABDOVF bit.

## 21.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 21-7), and asynchronously if the device is in Sleep mode (Figure 21-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 21.4.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled, the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times; 13-bit times are recommended for LIN bus or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

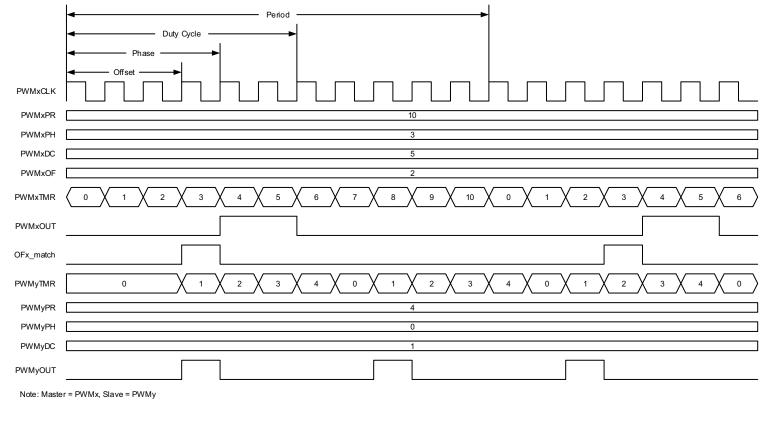

#### Rev. 10-000 146B 7/8/201 5 Period Duty Cycle Phase Offset PWMxCLK PWMxPR 10 PWMxPH 3 PWMxDC 5 PWMxOF 2 PWMxTMR 2 3 5 6 8 9 10 0 2 3 4 5 6 0 4 7 1 PWMxOUT OFx\_match PHx\_match DCx\_match PRx\_match PWMyTMR 3 0 3 2 0 2 0 2 4 2 0 3 4 1 4 1 1 PWMyPR 4 PWMyPH PWMyDC 1 PWMyOUT Note: PWMx = Master, PWMy = Slave

#### **FIGURE 22-8:**

#### INDEPENDENT RUN MODE TIMING DIAGRAM

PIC12(L )F1571,

# SLAVE RUN MODE WITH SYNC START TIMING DIAGRAM FIGURE 22-9: Rev. 10-000 147B 7/8/201 5 Period Duty Cycle Phase Offset

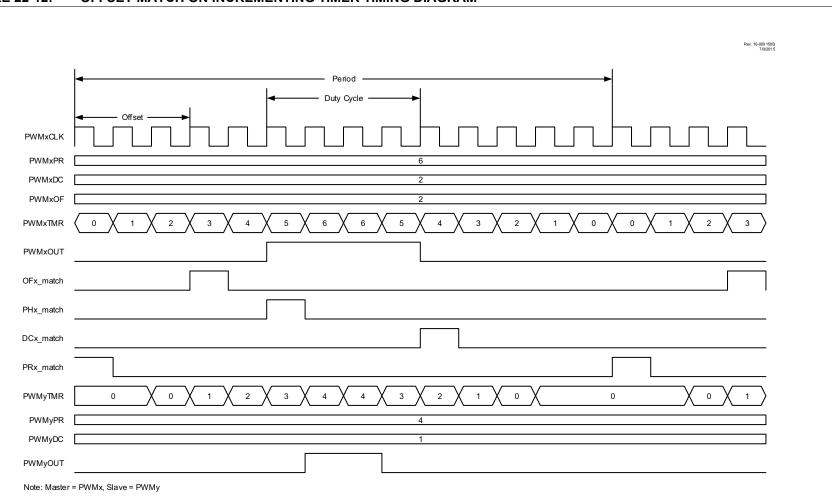

## FIGURE 22-12: OFFSET MATCH ON INCREMENTING TIMER TIMING DIAGRAM

PIC12(L)F1571/2

# REGISTER 22-7: PWMxPHH: PWMx PHASE COUNT HIGH REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | PH<     | 15:8>          |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable      | bit     |                |                  |                |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | U = Unimpler   | mented bit, read | d as '0'       |              |

| '1' = Bit is set |         | '0' = Bit is clea | ared    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

|                  |         |                   |         |                |                  |                |              |

bit 7-0 **PH<15:8>**: PWMx Phase High bits Upper eight bits of PWM phase count.

## REGISTER 22-8: PWMxPHL: PWMx PHASE COUNT LOW REGISTER

| bit 7   |         |         |         |         |         |         | bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PH<     | 7:0>    |         |         |         |

| R/W-x/u |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-0 **PH<7:0>**: PWMx Phase Low bits Lower eight bits of PWM phase count.

PIC12(L)F1571/;

| Mnen   | nonic, | Description                                   | Cycles |     | 14-Bit | Opcode | Ð    | Status   | Notes |

|--------|--------|-----------------------------------------------|--------|-----|--------|--------|------|----------|-------|

| Ореі   | rands  | Description                                   | Cycles | MSb |        |        | LSb  | Affected | Notes |

|        |        | CONTROL OPERA                                 | TIONS  |     |        |        |      |          |       |

| BRA    | k      | Relative Branch                               | 2      | 11  | 001k   | kkkk   | kkkk |          |       |

| BRW    | -      | Relative Branch with W                        | 2      | 00  | 0000   | 0000   | 1011 |          |       |

| CALL   | k      | Call Subroutine                               | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CALLW  | -      | Call Subroutine with W                        | 2      | 00  | 0000   | 0000   | 1010 |          |       |

| GOTO   | k      | Go to address                                 | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| RETFIE | k      | Return from interrupt                         | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW  | k      | Return with literal in W                      | 2      | 11  | 0100   | kkkk   | kkkk |          |       |

| RETURN | -      | Return from Subroutine                        | 2      | 00  | 0000   | 0000   | 1000 |          |       |

|        |        | INHERENT OPERA                                | ATIONS |     |        |        |      |          |       |

| CLRWDT | _      | Clear Watchdog Timer                          | 1      | 00  | 0000   | 0110   | 0100 | TO, PD   |       |

| NOP    | _      | No Operation                                  | 1      | 00  | 0000   | 0000   | 0000 |          |       |

| OPTION | _      | Load OPTION_REG register with W               | 1      | 00  | 0000   | 0110   | 0010 |          |       |

| RESET  | _      | Software device Reset                         | 1      | 00  | 0000   | 0000   | 0001 |          |       |

| SLEEP  | -      | Go into Standby mode                          | 1      | 00  | 0000   | 0110   | 0011 | TO, PD   |       |

| TRIS   | f      | Load TRIS register with W                     | 1      | 00  | 0000   | 0110   | Offf |          |       |

|        |        | C COMPILER OPT                                | IMIZED |     |        |        |      |          |       |

| ADDFSR | n, k   | Add Literal k to FSRn                         | 1      | 11  | 0001   | 0nkk   | kkkk |          |       |

| MOVIW  | n mm   | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 0nmm | Z        | 2, 3  |

|        |        | modifier, mm                                  |        |     |        |        | kkkk |          |       |

|        | k[n]   | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111   | 0nkk   | 1nmm | Z        | 2     |

| MOVWI  | n mm   | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000   | 0001   | kkkk |          | 2, 3  |

|        |        | modifier, mm                                  |        |     |        |        |      |          |       |

|        | k[n]   | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111   | 1nkk   |      |          | 2     |

# TABLE 25-3: ENHANCED MID-RANGE INSTRUCTION SET (CONTINUED)

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

3: See the table in the MOVIW and MOVWI instruction descriptions.

# PIC12(L)F1571/2

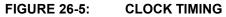

## TABLE 26-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Stanuaru      |      |                                         |      |      |      |       |                      |  |  |

|---------------|------|-----------------------------------------|------|------|------|-------|----------------------|--|--|

| Param.<br>No. | Sym. | Characteristic                          | Min. | Тур† | Max. | Units | Conditions           |  |  |

| OS01          | Fosc | External CLKIN Frequency <sup>(1)</sup> | DC   | _    | 0.5  | MHz   | External Clock (ECL) |  |  |

|               |      |                                         | DC   | —    | 4    | MHz   | External Clock (ECM) |  |  |

|               |      |                                         | DC   | —    | 20   | MHz   | External Clock (ECH) |  |  |

| OS02          | Tosc | External CLKIN Period <sup>(1)</sup>    | 50   | _    | ×    | ns    | External Clock (EC)  |  |  |

| OS03          | Тсү  | Instruction Cycle Time <sup>(1)</sup>   | 200  | Тсү  | DC   | ns    | Tcy = 4/Fosc         |  |  |

Standard Operating Conditions (unless otherwise stated)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

# TABLE 26-15: COMPARATOR SPECIFICATIONS<sup>(1)</sup>

| Param.<br>No. | Sym.     | Characteristics                           | Min. | Тур. | Max. | Units | Comments                  |

|---------------|----------|-------------------------------------------|------|------|------|-------|---------------------------|

| CM01          | VIOFF    | Input Offset Voltage                      | _    | ±7.5 | ±60  | mV    | CxSP = 1,<br>VICM = VDD/2 |

| CM02          | VICM     | Input Common-Mode Voltage                 | 0    |      | Vdd  | V     |                           |

| CM03          | CMRR     | Common-Mode Rejection Ration              |      | 50   |      | dB    |                           |

| CM04A         | TRESP(2) | Response Time Rising Edge                 |      | 400  | 800  | ns    | CxSP = 1                  |

| CM04B         |          | Response Time Falling Edge                | _    | 200  | 400  | ns    | CxSP = 1                  |

| CM04C         |          | Response Time Rising Edge                 |      | 1200 |      | ns    | CxSP = 0                  |

| CM04D         |          | Response Time Falling Edge                | _    | 550  | _    | ns    | CxSP = 0                  |

| CM05*         | Тмс2о∨   | Comparator Mode Change to<br>Output Valid | _    | —    | 10   | μs    |                           |

| CM06          | CHYSTER  | Comparator Hysteresis                     | _    | 25   | _    | mV    | CxHYS = 1,<br>CxSP = 1    |

\* These parameters are characterized but not tested.

Note 1: See Section 27.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

Response time measured with one comparator input at VDD/2, while the other input transitions from 2: Vss to VDD.

# TABLE 26-16: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS<sup>(1)</sup>

| Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = +25°C |      |                              |      |        |       |       |          |

|--------------------------------------------------------------------------|------|------------------------------|------|--------|-------|-------|----------|

| Param.<br>No.                                                            | Sym. | Characteristics              | Min. | Тур.   | Max.  | Units | Comments |

| DAC01*                                                                   | CLSB | Step Size                    | _    | VDD/32 |       | V     |          |

| DAC02*                                                                   | CACC | Absolute Accuracy            | _    | _      | ± 1/2 | LSb   |          |

| DAC03*                                                                   | CR   | Unit Resistor Value (R)      | _    | 5K     | _     | Ω     |          |

| DAC04*                                                                   | CST  | Settling Time <sup>(2)</sup> | _    |        | 10    | μS    |          |

These parameters are characterized but not tested.

Note 1: See Section 27.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

2: Settling time measured while DACR<4:0> transitions from '0000' to '1111'.

# 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |     |      |  |  |

|--------------------------|-------------|----------|-----|------|--|--|

| Dimensio                 | n Limits    | MIN      | NOM | MAX  |  |  |

| Number of Pins           | N           | 8        |     |      |  |  |

| Pitch                    | е           | 1.27 BSC |     |      |  |  |

| Overall Height           | Α           | -        | -   | 1.75 |  |  |

| Molded Package Thickness | A2          | 1.25     | -   | -    |  |  |

| Standoff §               | A1          | 0.10     | -   | 0.25 |  |  |

| Overall Width            | Е           | 6.00 BSC |     |      |  |  |

| Molded Package Width     | E1          | 3.90 BSC |     |      |  |  |

| Overall Length           | D           | 4.90 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25     | -   | 0.50 |  |  |

| Foot Length              | L           | 0.40     | -   | 1.27 |  |  |

| Footprint                | L1          | 1.04 REF |     |      |  |  |

| Foot Angle               | φ           | 0°       | -   | 8°   |  |  |

| Lead Thickness           | С           | 0.17     | -   | 0.25 |  |  |

| Lead Width               | b           | 0.31     | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°       | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -   | 15°  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-057C Sheet 2 of 2

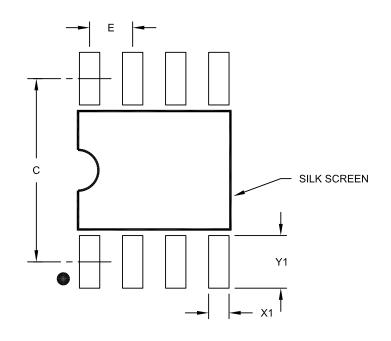

# 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | MILLIMETERS |          |      |      |

|-------------------------|-------------|----------|------|------|

| Dimension               | MIN         | NOM      | MAX  |      |

| Contact Pitch           | E           | 1.27 BSC |      |      |

| Contact Pad Spacing     | С           |          | 5.40 |      |

| Contact Pad Width (X8)  | X1          |          |      | 0.60 |

| Contact Pad Length (X8) | Y1          |          |      | 1.55 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A