Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 6                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                    |

| Supplier Device Package    | 8-MSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1572-e-ms |

## **Analog Peripherals:**

- 10-Bit Analog-to-Digital Converter (ADC):

- Up to four external channels

- Conversion available during Sleep

- Comparator:

- Low-Power/High-Speed modes

- Fixed Voltage Reference at (non)inverting input(s)

- Comparator outputs externally accessible

- Synchronization with Timer1 clock source

- Software hysteresis enable

- 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive reference selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- · Voltage Reference:

- Fixed voltage reference with 1.024V, 2.048V and 4.096V output levels

# **Clocking Structure:**

- · Precision Internal Oscillator:

- Factory calibrated ±1%, typical

- Software-selectable clock speeds from 31 kHz to 32 MHz

- · External Oscillator Block with:

- Resonator modes up to 20 MHz

- Two External Clock modes up to 32 MHz

- · Fail-Safe Clock Monitor

- · Digital Oscillator Input Available

# PIC12(L)F1571/2 FAMILY TYPES

| Device        | Data Sheet Index | Program Memory Flash<br>(K words) | Data SRAM (bytes) | High-Endurance<br>Flash (bytes) | I/O Pins | 8-Bit/16-Bit Timers | Comparators | 16-Bit PWM | 10-Bit ADC (ch) | 5-Bit DAC | CWG | EUSART | Debug <sup>(1)</sup> | XLP |

|---------------|------------------|-----------------------------------|-------------------|---------------------------------|----------|---------------------|-------------|------------|-----------------|-----------|-----|--------|----------------------|-----|

| PIC12(L)F1571 | Α                | 1                                 | 128               | 128                             | 6        | 2/4 <sup>(2)</sup>  | 1           | 3          | 4               | 1         | 1   | 0      | I                    | Υ   |

| PIC12(L)F1572 | Α                | 2                                 | 256               | 128                             | 6        | 2/4 <sup>(2)</sup>  | 1           | 3          | 4               | 1         | 1   | 1      | ı                    | Υ   |

Note 1: I – Debugging integrated on chip.

Data Sheet Index: (Unshaded devices are described in this document.)

A DS40001723 PIC12(L)F1571/2 Data Sheet, 8-Pin Flash, 8-Bit MCU with High-Precision 16-Bit PWM.

<sup>2:</sup> Three additional 16-bit timers available when not using the 16-bit PWM outputs.

### 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 Core Registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of Common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.6 "Indirect Addressing"** for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the bank address and the lower seven bits select the registers/RAM in that bank.

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses: x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-9.

TABLE 3-2: CORE REGISTERS

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| x0Bh or x8Bh | INTCON |

# 5.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 5-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator, a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depends on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT) and peripherals, are *not* affected by the change in frequency.

#### 5.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See Section 5.2.2.8 "Internal Oscillator Clock Switch Timing" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> (OSCCON<6:3>) = 0000) as the system clock source (SCS<1:0> (OSCCON<1:0>) = 1x) or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- Set FOSC<1:0> = 00, or

- Set the System Clock Source x (SCSx) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running.

#### 5.2.2.5 FRC

The FRC clock is an uncalibrated, nominal 600 kHz peripheral clock source.

The FRC is automatically turned on by the peripherals requesting the FRC clock.

The FRC clock will continue to run during Sleep.

# 5.2.2.6 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The postscaler outputs of the 16 MHz HFINTOSC, 500 kHz MFINTOSC and 31 kHz LFINTOSC output connect to a multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits, IRCF<3:0> of the OSCCON register, select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- · 32 MHz (requires 4x PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

Note:

• 31 kHz (LFINTOSC)

Following any Reset, the IRCF<3:0> bits of the OSCCON register are set to '0111' and the frequency selection is set to 500 kHz. The user can modify the IRCFx bits to select a different frequency.

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

#### **REGISTER 7-2:** PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0             | R/W-0/0             | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------------------|---------------------|-----|-----|---------|---------|

| TMR1GIE | ADIE    | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | _   | _   | TMR2IE  | TMR1IE  |

| bit 7   |         |                     |                     |     |     |         | bit 0   |

Legend:

bit 0

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7 TMR1GIE: Timer1 Gate Interrupt Enable bit

1 = Enables the Timer1 gate acquisition interrupt

0 = Disables the Timer1 gate acquisition interrupt

bit 6 ADIE: Analog-to-Digital Converter (ADC) Interrupt Enable bit

1 = Enables the ADC interrupt

0 = Disables the ADC interrupt

**RCIE:** USART Receive Interrupt Enable bit<sup>(1)</sup> bit 5

1 = Enables the USART receive interrupt

0 = Disables the USART receive interrupt

bit 4 **TXIE:** USART Transmit Interrupt Enable bit<sup>(1)</sup>

1 = Enables the USART transmit interrupt

0 = Disables the USART transmit interrupt

bit 3-2 Unimplemented: Read as '0'

bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

> 1 = Enables the Timer2 to PR2 match interrupt 0 = Disables the Timer2 to PR2 match interrupt

TMR1IE: Timer1 Overflow Interrupt Enable bit

1 = Enables the Timer1 overflow interrupt 0 = Disables the Timer1 overflow interrupt

Note 1: PIC12(L)F1572 only.

Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

Note: Bit PEIE of the INTCON register must be

set to enable any peripheral interrupt.

# 9.6 Register Definitions: Watchdog Control

Legend:

R = Readable bit

u = Bit is unchanged

#### REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

W = Writable bit

x = Bit is unknown

| U-0   | U-0 | R/W-0/0 | R/W-1/1 | R/W-0/0    | R/W-1/1 | R/W-1/1 | R/W-0/0 |

|-------|-----|---------|---------|------------|---------|---------|---------|

| _     | _   |         |         | WDTPS<4:0> | >       |         | SWDTEN  |

| bit 7 |     |         |         |            |         |         | bit 0   |

U = Unimplemented bit, read as '0'

'1' = Bit is set -n/n = Value at POR and BOR/Value at all other Resets '0' = Bit is cleared bit 7-6 Unimplemented: Read as '0' bit 5-1 WDTPS<4:0>: Watchdog Timer Period Select bits(1) Bit Value = Prescale Rate 11111 = Reserved; results in minimum interval (1:32) 10011 = Reserved; results in minimum interval (1:32) 10011 - Reserved, results in minimum interval (1 10010 = 1:8388608 ( $2^{23}$ ) (Interval 256s nominal) 10001 = 1:4194304 ( $2^{22}$ ) (Interval 128s nominal) 10000 = 1:2097152 ( $2^{21}$ ) (Interval 64s nominal) 01111 = 1:1048576 ( $2^{20}$ ) (Interval 32s nominal) 01110 = 1:524288 ( $2^{19}$ ) (Interval 16s nominal) 01101 = 1:262144 ( $2^{18}$ ) (Interval 8s nominal)  $01100 = 1:131072 (2^{17}) (Interval 4s nominal)$ 01011 = 1:65536 (Interval 2s nominal) (Reset value) 01010 = 1:32768 (Interval 1s nominal) 01001 = 1:16384 (Interval 512 ms nominal) 01000 = 1:8192 (Interval 256 ms nominal) 00111 = 1:4096 (Interval 128 ms nominal) 00110 = 1:2048 (Interval 64 ms nominal) 00101 = 1:1024 (Interval 32 ms nominal) 00100 = 1:512 (Interval 16 ms nominal) 00011 = 1:256 (Interval 8 ms nominal) 00010 = 1:128 (Interval 4 ms nominal) 00001 = 1:64 (Interval 2 ms nominal) 00000 = 1:32 (Interval 1 ms nominal) bit 0 **SWDTEN:** Software Enable/Disable for Watchdog Timer bit If WDTE<1:0> = 1x: This bit is ignored. If WDTE<1:0> = 01: 1 = WDT is turned on 0 = WDT is turned off If WDTE<1:0> = 00: This bit is ignored.

Note 1: Times are approximate. WDT time is based on 31 kHz LFINTOSC.

#### **EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY**

```

; This row erase routine assumes the following:

; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)

BCF

INTCON, GIE

; Disable ints so required sequences will execute properly

BANKSEL

PMADRL

MOVF

ADDRL,W

; Load lower 8 bits of erase address boundary

MOVWF

PMADRL

MOVF

ADDRH,W

; Load upper 6 bits of erase address boundary

MOVWF

PMADRH

PMCON1,CFGS

BCF

; Not configuration space

; Specify an erase operation

PMCON1,FREE

BSF

PMCON1, WREN

; Enable writes

BSF

MOVLW

55h

; Start of required sequence to initiate erase

MOVWF

PMCON2

; Write 55h

MOVLW

0AAh

MOVWF

PMCON2

; Write AAh

BSF

PMCON1,WR

; Set WR bit to begin erase

NOP

; NOP instructions are forced as processor starts

NOP

; row erase of program memory.

; The processor stalls until the erase process is complete

; after erase processor continues with 3rd instruction

PMCON1,WREN

; Disable writes

BCF

INTCON, GIE

; Enable interrupts

BSF

```

| PIC12 |  | )F157 | 1/2 |

|-------|--|-------|-----|

|-------|--|-------|-----|

NOTES:

#### 12.0 INTERRUPT-ON-CHANGE

The PORTA and PORTB pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The Interrupt-On-Change module has the following features:

- · Interrupt-On-Change enable (Master Switch)

- · Individual pin configuration

- · Rising and falling edge detection

- · Individual pin interrupt flags

Figure 12-1 is a block diagram of the IOC module.

# 12.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

### 12.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

## 12.3 Interrupt Flags

The IOCAFx and IOCBFx bits located in the IOCAF and IOCBF registers, respectively, are status flags that correspond to the Interrupt-On-Change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx and IOCBFx bits.

# 12.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx and IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

# EXAMPLE 12-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

```

MOVLW 0xff

XORWF IOCAF, W

ANDWF IOCAF, F

```

# 12.5 Operation in Sleep

The Interrupt-On-Change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

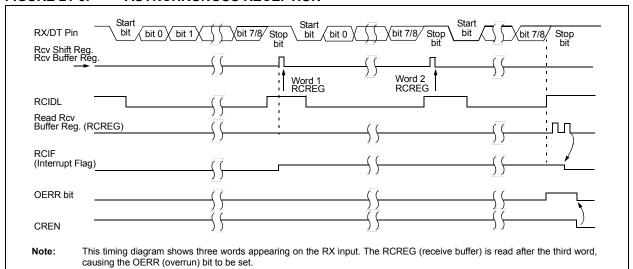

#### 21.1.2.8 Asynchronous Reception Setup

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 21.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSELx bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register, and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 21.1.2.9 9-Bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH/SPBRGL register pair, and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 21.4 "EUSART Baud Rate Generator (BRG)").

- Clear the ANSELx bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit.

The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register, and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

#### FIGURE 21-5: ASYNCHRONOUS RECEPTION

# TABLE 22-2: SUMMARY OF REGISTERS ASSOCIATED WITH PWM (CONTINUED)

| Name       | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register on Page |

|------------|-------|-------|---------|-------|-------|-------|-------|-------|------------------|

| PWM3INTE   | _     | _     | _       | _     | OFIE  | PHIE  | DCIE  | PRIE  | 217              |

| PWM3INTF   | _     | _     | _       | _     | OFIF  | PHIF  | DCIF  | PRIF  | 218              |

| PWM3CLKCON | _     |       | PS<2:0> |       | _     | _     | CS<   | :1:0> | 219              |

| PWM3LDCON  | LDA   | LDT   | 1       | ı     | _     | _     | LDS   | <1:0> | 220              |

| PWM3OFCON  | _     | OFM•  | <1:0>   | OFO   | _     | _     | OFS   | <1:0> | 221              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the PWM.

### TABLE 22-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|------------------|

| CONFICA | 13:8 | _       | _       | _        | _        | CLKOUTEN | BORE     | N<1:0>  | _       | 40               |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | E<1:0>   | _        | FOSC    | <1:0>   | 42               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

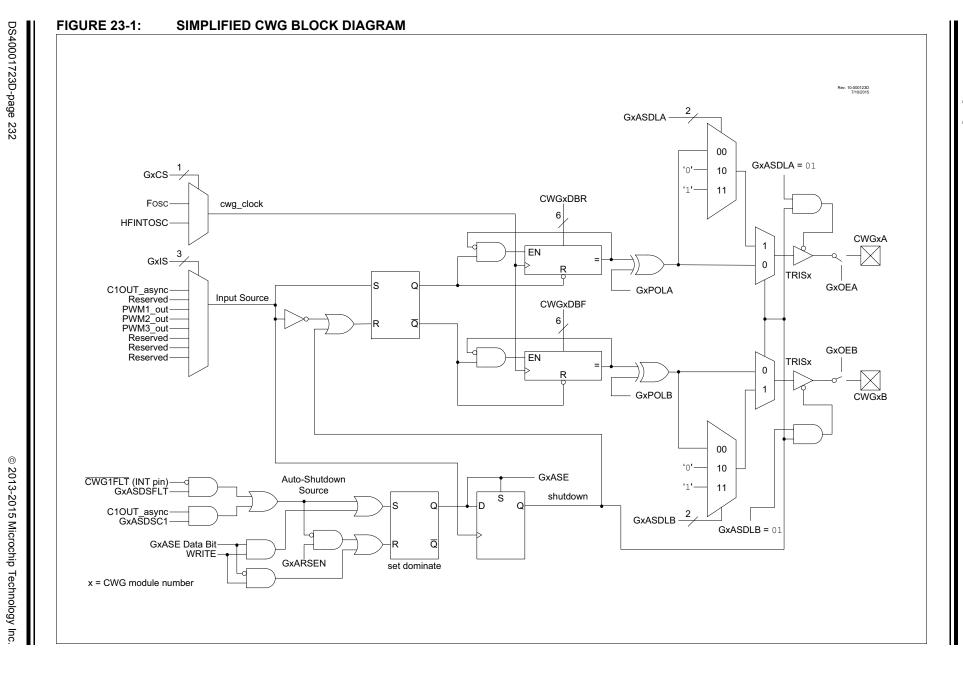

# REGISTER 23-4: CWGxDBR: CWGx COMPLEMENTARY WAVEFORM GENERATOR RISING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | CWGxD   | BR<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7-6 Unimplemented: Read as '0'

bit 5-0 CWGxDBR<5:0>: Complementary Waveform Generator (CWGx) Rising Counts bits

11 1111 = 63-64 counts of dead band

11 1110 = 62-63 counts of dead band

.

.

00 0010 = 2-3 counts of dead band

00 0001 = 1-2 counts of dead band

00 0000 = 0 counts of dead band

# REGISTER 23-5: CWGxDBF: CWGx COMPLEMENTARY WAVEFORM GENERATOR FALLING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | CWGxD   | BF<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 CWGxDBF<5:0>: Complementary Waveform Generator (CWGx) Falling Counts bits

11 1111 = 63-64 counts of dead band

11 1110 = 62-63 counts of dead band

•

•

00 0010 = 2-3 counts of dead band

00 0001 = 1-2 counts of dead band

00 0000 = 0 counts of dead band; dead-band generation is bypassed

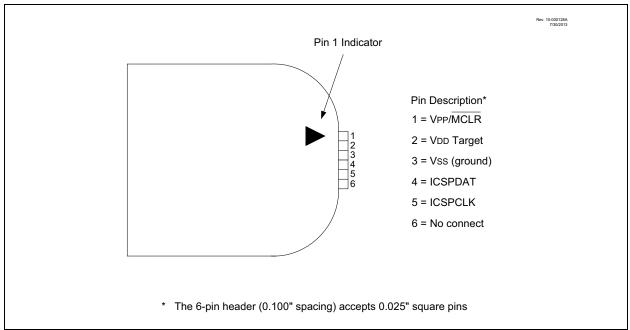

FIGURE 24-2: PICkit™ PROGRAMMER STYLE CONNECTOR INTERFACE

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

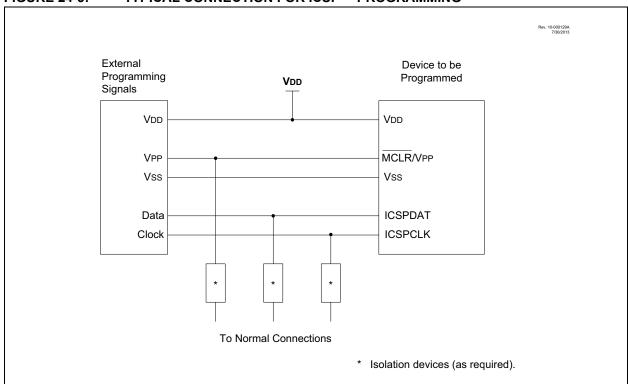

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices, such as resistors, diodes or even jumpers. See Figure 24-3 for more information.

FIGURE 24-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

# 25.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                                 |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                                    |

| Operation:       | $FSR(n) + k \to FSR(n)$                                                                                  |

| Status Affected: | None                                                                                                     |

| Description:     | The signed 6-bit literal 'k' is added to the contents of the FSRnH:FSRnL register pair.                  |

|                  | FSRn is limited to the range 0000h - FFFFh. Moving beyond these bounds will cause the FSR to wraparound. |

| ANDLW            | AND literal with W                                                                                        |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ANDLW k                                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                                       |

| Operation:       | (W) .AND. $(k) \rightarrow (W)$                                                                           |

| Status Affected: | Z                                                                                                         |

| Description:     | The contents of W register are AND'ed with the 8-bit literal 'k'. The result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                             |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] ADDLW k                                                                                             |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |  |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                     |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                      |  |  |  |  |  |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                           |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                    |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                     |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                      |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                            |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                    |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                     |  |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                  |  |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                               |  |  |  |  |  |  |  |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |  |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                               |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] ASRF f {,d}                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Operation:       | $(f<7>)\rightarrow dest<7>$<br>$(f<7:1>)\rightarrow dest<6:0>,$<br>$(f<0>)\rightarrow C,$                                                                                                                            |  |  |  |  |  |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are shifted one bit to the right through the Carry flag. The MSb remains unchanged. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |  |  |

|                  | register f C                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| ADDWFC           | ADD W and CARRY bit to f                                                                                                                                       |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                        |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |  |  |  |  |  |  |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                             |  |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                       |  |  |  |  |  |  |  |

| Description:     | Add W, the Carry flag and data memory location 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed in data memory location 'f'. |  |  |  |  |  |  |  |

### RRF Rotate Right f through Carry

Syntax: [ label ] RRF f,d

Operands:  $0 \le f \le 127 \\ d \in [0,1]$

Operation: See description below

Status Affected: C

Description: The contents of register 'f' are rotated one bit to the right through the Carry

flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.

C Register f

#### SUBLW Subtract W from literal

Syntax: [label] SUBLW k

Operands:  $0 \le k \le 255$ Operation:  $k - (W) \rightarrow (W)$ Status Affected: C, DC, Z

Description: The W register is subtracted (2's com-

plement method) from the 8-bit literal 'k'. The result is placed in the W regis-

ter.

| C = 0  | W > k           |

|--------|-----------------|

| C = 1  | $W \leq k $     |

| DC = 0 | W<3:0> > k<3:0> |

| DC = 1 | W<3:0> ≤ k<3:0> |

### SLEEP Enter Sleep mode

Syntax: [ label ] SLEEP

Operands: None

Operation:  $00h \rightarrow WDT$ ,

$0 \rightarrow WDT$  prescaler,

$\begin{array}{c} 1 \to \overline{\mathsf{TO}}, \\ 0 \to \overline{\mathsf{PD}} \end{array}$

Status Affected: TO, PD

Description: The power-down Status bit,  $\overline{PD}$  is

cleared. Time-out Status bit,  $\overline{\text{TO}}$  is set. Watchdog Timer and its pres-

caler are cleared.

The processor is put into Sleep mode

with the oscillator stopped.

### SUBWF Subtract W from f

Syntax: [label] SUBWF f,d

Operands:  $0 \le f \le 127$   $d \in [0,1]$

Operation: (f) - (W)  $\rightarrow$  (destination)

Status Affected: C, DC, Z

Description: Subtract (2's complement method) W

register from register 'f'. If 'd' is '0', the

result is stored in the W

register. If 'd' is '1', the result is stored

back in register 'f.

| C = 0  | W > f           |

|--------|-----------------|

| C = 1  | $W \leq f$      |

| DC = 0 | W<3:0> > f<3:0> |

| DC = 1 | W<3:0> ≤ f<3:0> |

#### SUBWFB Subtract W from f with Borrow

Syntax: SUBWFB  $f \{,d\}$

Operands:  $0 \le f \le 127$

$d \in [0,1]$

Operation:  $(f) - (W) - (\overline{B}) \rightarrow dest$

Status Affected: C, DC, Z

Description: Subtract W and the BORROW flag

(CARRY) from register 'f' (2's complement method). If 'd' is '0', the result is stored in W. If 'd' is '1', the result is

stored back in register 'f'.

# TABLE 26-13: ANALOG-TO-DIGITAL CONVERTER (ADC) CHARACTERISTICS<sup>(1,2,3)</sup>

| Operating Conditions (unless otherwise stated) VDD = 3.0V, TA = +25°C |      |                                                   |      |      |      |       |                                                                           |

|-----------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------------|

| Param.<br>No.                                                         | Sym. | Characteristic                                    | Min. | Typ† | Max. | Units | Conditions                                                                |

| AD01                                                                  | NR   | Resolution                                        | _    | _    | 10   | bit   |                                                                           |

| AD02                                                                  | EIL  | Integral Error                                    | _    | ±1   | ±1.7 | LSb   | VREF = 3.0V                                                               |

| AD03                                                                  | EDL  | Differential Error                                | _    | ±1   | ±1   | LSb   | No missing codes, VREF = 3.0V                                             |

| AD04                                                                  | Eoff | Offset Error                                      | _    | ±1   | ±2.5 | LSb   | VREF = 3.0V                                                               |

| AD05                                                                  | Egn  | Gain Error                                        | _    | ±1   | ±2.0 | LSb   | VREF = 3.0V                                                               |

| AD06                                                                  | VREF | Reference Voltage                                 | 1.8  | _    | Vdd  | V     | VREF = (VRPOS - VRNEG) (Note 4)                                           |

| AD07                                                                  | Vain | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                           |

| AD08                                                                  | ZAIN | Recommended Impedance of<br>Analog Voltage Source | _    | _    | 10   | kΩ    | Can go higher if external 0.01 $\mu F$ capacitor is present on input pin. |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Total absolute error includes integral, differential, offset and gain errors.

- 2: The ADC conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: See Section 27.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

- 4: ADC VREF is selected by the ADPREF<0> bit.

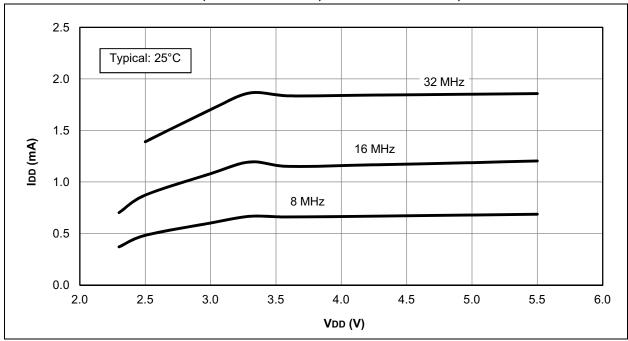

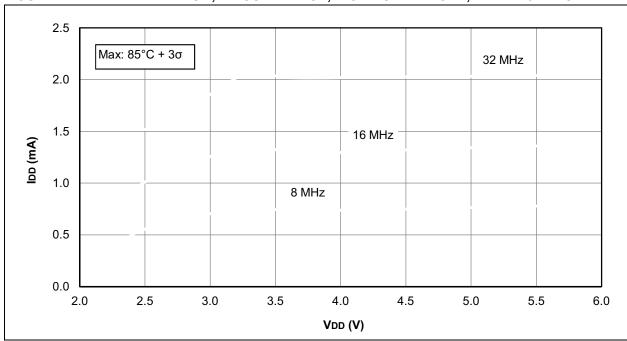

FIGURE 27-12: IDD MAXIMUM, EC OSCILLATOR, HIGH-POWER MODE, PIC12F1571/2 ONLY

# 28.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoq® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 28.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

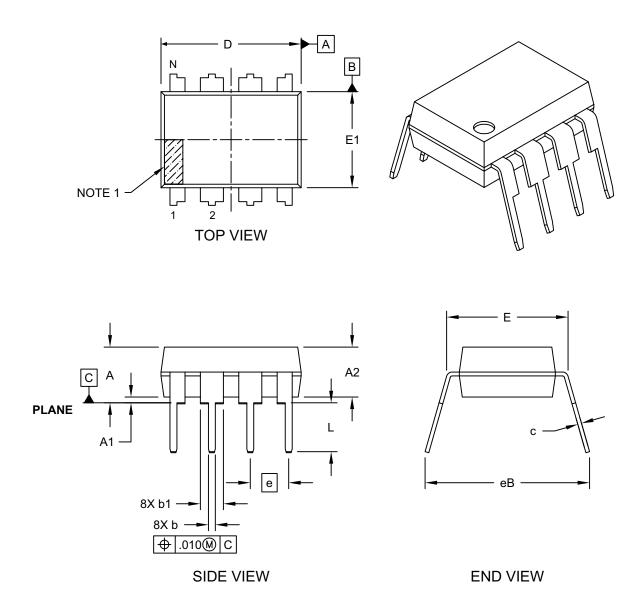

# 29.2 Package Details

The following sections give the technical details of the packages.

# 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-018D Sheet 1 of 2

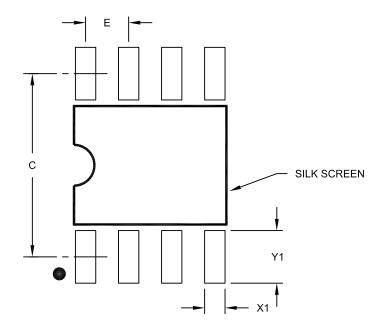

# 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | MILLIMETERS |     |          |      |

|-------------------------|-------------|-----|----------|------|

| Dimension Limits        |             | MIN | NOM      | MAX  |

| Contact Pitch           | E           |     | 1.27 BSC |      |

| Contact Pad Spacing     | С           |     | 5.40     |      |

| Contact Pad Width (X8)  | X1          |     |          | 0.60 |

| Contact Pad Length (X8) | Y1          |     |          | 1.55 |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A