Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Data lla                   |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-VDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-DFN (3x3)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1572t-i-mf |

| PIC12 |  | )F157 | 1/2 |

|-------|--|-------|-----|

|-------|--|-------|-----|

NOTES:

### 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral, thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C, the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

#### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

```

COG1CON0bits.MD = 0x5;

```

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name, MD2, and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

#### Example 1:

```

MOVLW ~(1<<G1MD1)

ANDWF COG1CON0,F

MOVLW 1<<G1MD2 | 1<<G1MD0

IORWF COG1CON0,F

```

### Example 2:

```

BSF COG1CON0,G1MD2

BCF COG1CON0,G1MD1

BSF COG1CON0,G1MD0

```

# 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

### 1.1.3.1 Status, Interrupt and Mirror Bits

Status, interrupt enables, interrupt flags and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

## 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

TABLE 1-2: PIC12(L)F1571/2 PINOUT DESCRIPTION

| Name                                                             | Function | Input<br>Type | Output<br>Type | Description                                   |

|------------------------------------------------------------------|----------|---------------|----------------|-----------------------------------------------|

| RA0/AN0/C1IN+/DACOUT/                                            | RA0      |               |                | General purpose I/O.                          |

| TX <sup>(2)</sup> /CK <sup>(2)</sup> /CWG1B/PWM2/                | AN0      |               |                | ADC channel input.                            |

| ICSPDAT/ICDDAT                                                   | C1IN+    |               |                | Comparator positive input.                    |

|                                                                  | DACOUT   |               |                | Digital-to-Analog Converter output.           |

|                                                                  | TX       | (3)           | (4)            | USART asynchronous transmit.                  |

|                                                                  | CK       | (-)           | (-,            | USART synchronous clock.                      |

|                                                                  | CWG1B    |               |                | CWG complementary output.                     |

|                                                                  | PWM2     |               |                | PWM output.                                   |

|                                                                  | ICSPDAT  |               |                | ICSP™ data I/O.                               |

|                                                                  | ICDDAT   |               |                | In-circuit debug data.                        |

| RA1/AN1/VREF+/C1IN0-/RX <sup>(2)</sup> /                         | RA1      |               |                | General purpose I/O.                          |

| DT <sup>(2)</sup> /PWM1/ICSPCLK/ICDCLK                           | AN1      |               |                | ADC channel input.                            |

|                                                                  | VREF+    |               |                | ADC Voltage Reference input.                  |

|                                                                  | C1IN0-   |               |                | Comparator negative input.                    |

|                                                                  | RX       | (3)           | (4)            | USART asynchronous input.                     |

|                                                                  | DT       |               |                | USART synchronous data.                       |

|                                                                  | PWM1     |               |                | PWM output.                                   |

|                                                                  | ICSPCLK  |               |                | ICSP programming clock.                       |

|                                                                  | ICDCLK   |               |                | In-circuit debug clock.                       |

| RA2/AN2/C1OUT/T0CKI/                                             | RA2      |               |                | General purpose I/O.                          |

| CWG1FLT/CWG1A/PWM3/INT                                           | AN2      | (3)           | (4)            | ADC channel input.                            |

|                                                                  | C1OUT    |               |                | Comparator output.                            |

|                                                                  | T0CKI    |               |                | Timer0 clock input.                           |

|                                                                  | CWG1FLT  |               |                | Complementary Waveform Generator Fault input. |

|                                                                  | CWG1A    |               |                | CWG complementary output.                     |

|                                                                  | PWM3     |               |                | PWM output.                                   |

|                                                                  | INT      |               |                | External interrupt.                           |

| RA3/VPP/T1G <sup>(1)</sup> /MCLR                                 | RA3      |               |                | General purpose input with IOC and WPU.       |

|                                                                  | VPP      | (2)           | (4)            | Programming voltage.                          |

|                                                                  | T1G      | (3)           | (4)            | Timer1 gate input.                            |

|                                                                  | MCLR     |               |                | Master Clear with internal pull-up.           |

| RA4/AN3/C1IN1-/T1G/TX <sup>(1,2)</sup> /                         | RA4      |               |                | General purpose I/O.                          |

| CK <sup>(1,2)</sup> /CWG1B <sup>(1)</sup> /PWM2 <sup>(1)</sup> / | AN3      |               |                | ADC channel input.                            |

| CLKOUT                                                           | C1IN1-   |               |                | Comparator negative input.                    |

|                                                                  | T1G      |               |                | Timer1 gate input.                            |

|                                                                  | TX       | (3)           | (4)            | USART asynchronous transmit.                  |

|                                                                  | CK       |               |                | USART synchronous clock.                      |

|                                                                  | CWG1B    |               |                | CWG complementary output.                     |

|                                                                  | PWM2     |               |                | PWM output.                                   |

|                                                                  | CLKOUT   |               |                | Fosc/4 output.                                |

|                                                                  | 02.1001  |               | l .            | . 555 Salpati                                 |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$  HV = High Voltage XTAL = Crystal levels

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

- 2: PIC12(L)F1572 only.

- 3: Input type is selected by the port.

- **4:** Output type is selected by the port.

**TABLE 1-2:** PIC12(L)F1571/2 PINOUT DESCRIPTION (CONTINUED)

| Name                                                 | Function | Input<br>Type | Output<br>Type | Description                     |

|------------------------------------------------------|----------|---------------|----------------|---------------------------------|

| RA5/T1CKI/RX <sup>(1,2)</sup> /DT <sup>(1,2)</sup> / | RA5      |               |                | General purpose I/O.            |

| CWG1A <sup>(1)</sup> /PWM1 <sup>(1)</sup> /CLKIN     | T1CKI    |               |                | Timer1 clock input.             |

|                                                      | RX       |               | (4)            | USART asynchronous input.       |

|                                                      | DT       | (3)           |                | USART synchronous data.         |

|                                                      | CWG1A    |               |                | CWG complementary output.       |

|                                                      | PWM1     |               |                | PWM output.                     |

|                                                      | CLKIN    |               |                | External Clock input (EC mode). |

| VDD                                                  | VDD      | Power         | _              | Positive supply.                |

| Vss                                                  | Vss      | Power         | _              | Ground reference.               |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

$I^2C$  = Schmitt Trigger input with  $I^2C$ levels

HV = High Voltage XTAL = Crystal Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

2: PIC12(L)F1572 only.

**3:** Input type is selected by the port.

4: Output type is selected by the port.

# TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                                     |          |               |               |       |         |        | (55.1      |           |       |                      |                                 |

|-------------------------------------|----------|---------------|---------------|-------|---------|--------|------------|-----------|-------|----------------------|---------------------------------|

| Addr                                | Name     | Bit 7         | Bit 6         | Bit 5 | Bit 4   | Bit 3  | Bit 2      | Bit 1     | Bit 0 | Value on<br>POR, BOR | Value on<br>All Other<br>Resets |

| Bank                                | 10       |               |               |       |         |        |            |           |       |                      |                                 |

| 50Ch<br>to<br>51Fh                  | _        | Unimplemented |               |       |         |        |            |           |       |                      |                                 |

| Bank                                | 11       |               |               |       |         |        |            |           |       |                      |                                 |

| 58Ch<br>to<br>59Fh                  | _        | Unimpleme     | Jnimplemented |       |         |        |            |           |       |                      |                                 |

| Bank                                | 12       |               |               |       |         |        |            |           |       |                      |                                 |

| 60Ch<br>to<br>61Fh                  | _        | Unimpleme     | Unimplemented |       |         |        |            |           |       |                      | _                               |

| Bank                                | 13       |               |               |       |         |        |            |           |       |                      |                                 |

| 68Ch<br>to<br>690h                  | _        | Unimpleme     | nted          |       |         |        |            |           |       | _                    |                                 |

| 691h                                | CWG1DBR  | _             | _             |       |         | CWC    | S1DBR<5:0> |           |       | 00 0000              | 00 0000                         |

| 692h                                | CWG1DBF  | _             | _             |       |         | CWC    | 91DBF<5:0> |           |       | xx xxxx              | xx xxxx                         |

| 693h                                | CWG1CON0 | G1EN          | G10EB         | G10EA | G1POLB  | G1POLA | _          | _         | G1CS0 | 0000 00              | 0000 00                         |

| 694h                                | CWG1CON1 | G1ASD         | LB<1:0>       | G1ASD | LA<1:0> | _      |            | G1IS<2:0> |       | 0000 -000            | 0000 -000                       |

| 695h                                | CWG1CON2 | G1ASE         | G1ARSEN       | _     | _       | _      | G1ASDSC1   | G1ASDSFLT | _     | 0000-                | 0000-                           |

| 696h<br>to<br>69Fh                  | _        | Unimplemented |               |       |         |        |            |           |       | _                    | _                               |

| Banks                               | s 14-26  |               |               |       |         |        |            |           |       |                      |                                 |

| x0Ch/<br>x8Ch<br>—<br>x1Fh/<br>x9Fh | _        | Unimpleme     | nted          |       |         |        |            |           |       | _                    | _                               |

Legend: x = unknown; u = unchanged; q = value depends on condition; — = unimplemented; r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: PIC12F1571/2 only. 2: PIC12(L)F1572 only.

3: Unimplemented, read as '1'.

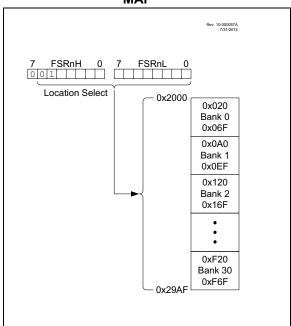

#### 3.6.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address, 0x2000, to FSR address, 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

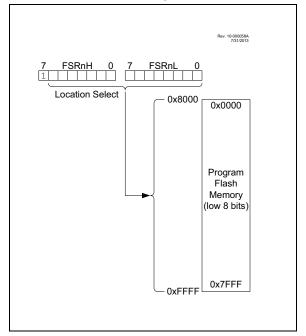

#### 3.6.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire Program Flash Memory is mapped to the upper half of the FSR address space. When the MSb of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location are accessible via INDF. Writing to the Program Flash Memory cannot be accomplished via the FSR/INDF interface. All instructions that access Program Flash Memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

## 5.0 OSCILLATOR MODULE

## 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications, while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources

The oscillator module can be configured in one of the following clock modes:

- ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- ECM External Clock Medium Power mode (0.5 MHz to 4 MHz)

- ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. INTOSC Internal Oscillator (31 kHz to 32 MHz)

Clock Source modes are selected by the FOSC<1:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The ECH, ECM, and ECL Clock modes rely on an external logic level signal as the device clock source.

The INTOSC internal oscillator block produces low, medium and high-frequency clock sources, designated as LFINTOSC, MFINTOSC and HFINTOSC (see Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these three clock sources.

# 5.5 Register Definitions: Oscillator Control

#### REGISTER 5-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0/0 | R/W-0/0   | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|-----------|---------|---------|---------|-----|---------|---------|

| SPLLEN  | IRCF<3:0> |         |         |         | _   | SCS-    | <1:0>   |

| bit 7   |           |         |         |         |     |         | bit 0   |

Legend:R = Readable bitW = Writable bitu = Bit is unchangedx = Bit is unknownU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is cleared-n/n = Value at POR and BOR/Value at all other Resets

bit 7 SPLLEN: Software PLL Enable bit

If PLLEN in Configuration Words = 1:

SPLLEN bit is ignored. 4x PLL is always enabled (subject to oscillator requirements).

If PLLEN in Configuration Words = 0:

1 = 4x PLL is enabled 0 = 4x PLL is disabled

bit 6-3 IRCF<3:0>: Internal Oscillator Frequency Select bits

1111 = 16 MHz HF

1110 = 8 MHz or 32 MHz HF (see **Section 5.2.2.1 "HFINTOSC"**)

1101 = 4 MHz HF 1100 = 2 MHz HF 1011 = 1 MHz HF 1010 = 500 kHz HF<sup>(1)</sup>

1001 = 250 kHz HF<sup>(1)</sup> 1000 = 125 kHz HF<sup>(1)</sup>

0111 = 500 kHz MF (default upon Reset)

0110 = 250 kHz MF 0101 = 125 kHz MF 0100 = 62.5 kHz MF 0011 = 31.25 kHz HF<sup>(1)</sup> 0010 = 31.25 kHz MF 000x = 31 kHz LF

bit 2 Unimplemented: Read as '0'

bit 1-0 SCS<1:0>: System Clock Select bits

1x = Internal oscillator block

01 = Timer1 oscillator

00 = Clock determined by FOSC<1:0> in Configuration Words

**Note 1:** Duplicate frequency derived from HFINTOSC.

### 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the interrupt enable bit of the interrupt event is contained in the PIE1, PIE2 and PIE3 registers)

The INTCON, PIR1, PIR2 and PIR3 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector, 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

# 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5               | Bit 4               | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|------------|---------|--------|---------------------|---------------------|-------|--------|--------|--------|------------------|

| INTCON     | GIE     | PEIE   | TMR0IE              | INTE                | IOCIE | TMR0IF | INTF   | IOCIF  | 74               |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS              | TMR0SE              | PSA   |        | 157    |        |                  |

| PIE1       | TMR1GIE | ADIE   | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | _     | _      | TMR2IE | TMR1IE | 75               |

| PIE2       | _       | _      | C1IE                | _                   | _     | _      | _      | _      | 76               |

| PIE3       | _       | PWM3IE | PWM2IE              | PWM1IE              | _     | _      | _      | _      | 77               |

| PIR1       | TMR1GIF | ADIF   | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | _     | _      | TMR2IF | TMR1IF | 78               |

| PIR2       | _       | _      | C1IF                | _                   | _     | _      | _      | _      | 79               |

| PIR3       | _       | PWM3IF | PWM2IF              | PWM1IF              | _     | _      | _      | _      | 80               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

**Note 1:** PIC12(L)F1572 only.

#### REGISTER 15-3: ADCON2: ADC CONTROL REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0               | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----------------------|---------|-----|-----|-----|-------|

|         | TRIGSEL | .<3:0> <sup>(1)</sup> |         | _   | _   | _   | _     |

| bit 7   |         |                       |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7-4 TRIGSEL<3:0>: Auto-Conversion Trigger Selection bits<sup>(1)</sup>

0000 = No auto-conversion trigger selected

0001 = PWM1 – PWM1 interrupt

0010 = PWM2 – PWM2\_interrupt

$0011 = Timer0 - T0_overflow^{(2)}$

0100 = Timer1 – T1\_overflow<sup>(2)</sup>

0101 = Timer2 – T2\_match

0110 = Comparator C1 - C1OUT\_sync

0111 = PWM3 - PWM3 interrupt

1000 = PWM1 – PWM1\_OF1\_match

1001 =  $PWM2 - PWM2\_OF2\_match$

1010 = PWM3 - PWM3\_OF3\_match

1011 = Reserved

1100 = Reserved

1101 = Reserved

1110 = Reserved

1111 = Reserved

bit 3-0 **Unimplemented:** Read as '0'

Note 1: This is a rising edge sensitive input for all sources.

2: Signal also sets its corresponding interrupt flag.

NOTES:

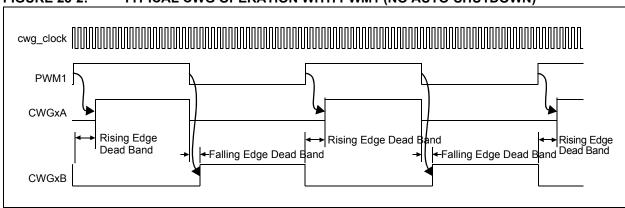

FIGURE 23-2: TYPICAL CWG OPERATION WITH PWM1 (NO AUTO-SHUTDOWN)

#### 23.5 Dead-Band Control

Dead-band control provides for non-overlapping output signals to prevent shoot-through current in power switches. The CWG contains two 6-bit dead-band counters. One dead-band counter is used for the rising edge of the input source control. The other is used for the falling edge of the input source control.

Dead band is timed by counting CWG clock periods from zero, up to the value in the rising or falling Dead-Band Counter registers. See the CWGxDBR and CWGxDBF registers (Register 23-4 and Register 23-5, respectively).

## 23.6 Rising Edge Dead Band

The rising edge dead band delays the turn-on of the CWGxA output from when the CWGxB output is turned off. The rising edge dead-band time starts when the rising edge of the input source signal goes true. When this happens, the CWGxB output is immediately turned off and the rising edge dead-band delay time starts. When the rising edge dead-band delay time is reached, the CWGxA output is turned on.

The CWGxDBR register sets the duration of the deadband interval on the rising edge of the input source signal. This duration is from 0 to 64 counts of dead band.

Dead band is always counted off the edge on the input source signal. A count of 0 (zero), indicates that no dead band is present.

If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

## 23.7 Falling Edge Dead Band

The falling edge dead band delays the turn-on of the CWGxB output from when the CWGxA output is turned off. The falling edge dead-band time starts when the falling edge of the input source goes true. When this happens, the CWGxA output is immediately turned off and the falling edge dead-band delay time starts. When the falling edge dead-band delay time is reached, the CWGxB output is turned on.

The CWGxDBF register sets the duration of the deadband interval on the falling edge of the input source signal. This duration is from 0 to 64 counts of dead band.

Dead band is always counted off the edge on the input source signal. A count of 0 (zero), indicates that no dead band is present.

If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

Refer to Figure 23-3 and Figure 23-4 for examples.

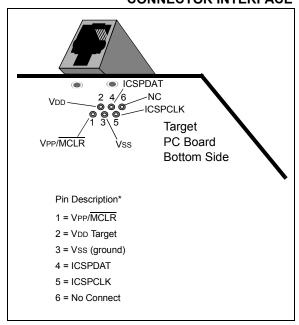

# 24.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>TM</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>TM</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode, the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP $^{\text{TM}}$ , refer to the "PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification" (DS41573).

# 24.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low, then raising the voltage on MCLR/VPP to VIHH.

# 24.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC® MCUs (Flash) to be programmed using VDD only, without high voltage. When the LVP bit of the Configuration Words is set to '1', the ICSP Low-Voltage Programming Entry mode is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- A 32-bit key sequence is presented on ICSPDAT while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at V<sub>IL</sub> for as long as Program/Verify mode is to be maintained.

If Low-Voltage Programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5** "**MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

## 24.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP™ header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 24-1.

FIGURE 24-1: ICD RJ-11 STYLE CONNECTOR INTERFACE

Another connector often found in use with the PICkit™ programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 24-2.

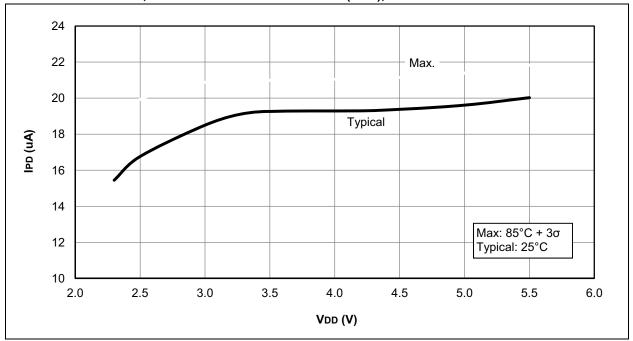

TABLE 26-3: POWER-DOWN CURRENTS (IPD)(1,2) (CONTINUED)

| PIC12LF1571/2 |                                      | Operating Conditions (unless otherwise stated) Low-Power Sleep Mode |            |          |        |             |            |                                 |  |  |  |

|---------------|--------------------------------------|---------------------------------------------------------------------|------------|----------|--------|-------------|------------|---------------------------------|--|--|--|

| PIC12F157     | 71/2                                 | Low-Po                                                              | wer Sle    | ep Mode, | VREGPM | = 1         |            |                                 |  |  |  |

| Param.        |                                      |                                                                     | <b>T</b> 1 | Max.     | Max.   | 1114        | Conditions |                                 |  |  |  |

| No.           | No. Device Characteristics Min. Typ† | Тур†                                                                | PT +85°C   | +125°C   | Units  | <b>V</b> DD | Note       |                                 |  |  |  |

| D027          |                                      | _                                                                   | 4          | 7        | 9      | μА          | 1.8        | Comparator,                     |  |  |  |

|               |                                      | _                                                                   | 4.2        | 8        | 10     | μА          | 3.0        | CxSP = 0                        |  |  |  |

| D027          |                                      | _                                                                   | 13         | 20       | 21     | μА          | 2.3        | Comparator,                     |  |  |  |

|               |                                      | _                                                                   | 14         | 23       | 25     | μΑ          | 3.0        | CxSP = 0                        |  |  |  |

|               |                                      | _                                                                   | 16         | 24       | 26     | μΑ          | 5.0        |                                 |  |  |  |

| D028A         |                                      | _                                                                   | 20         | 35       | 36     | μΑ          | 1.8        | Comparator,                     |  |  |  |

|               |                                      | _                                                                   | 21         | 36       | 38     | μА          | 3.0        | Normal Power, CxSP = 1 (Note 1) |  |  |  |

| D028A         |                                      | _                                                                   | 28         | 47       | 48     | μΑ          | 2.3        | Comparator,                     |  |  |  |

|               |                                      | _                                                                   | 29         | 51       | 52     | μА          | 3.0        | Normal Power, CxSP = 1,         |  |  |  |

|               |                                      | _                                                                   | 31         | 52       | 53     | μΑ          | 5.0        | VREGPM = 1 (Note 1)             |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: The peripheral  $\Delta$  current can be determined by subtracting the base IPD current from this limit. Max. values should be used when calculating total current consumption.

<sup>†</sup> Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

<sup>3:</sup> ADC clock source is FRC.

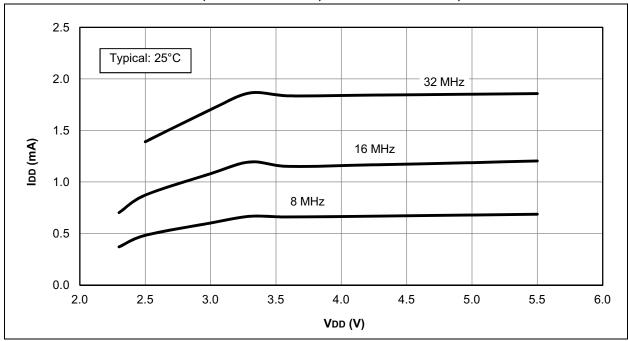

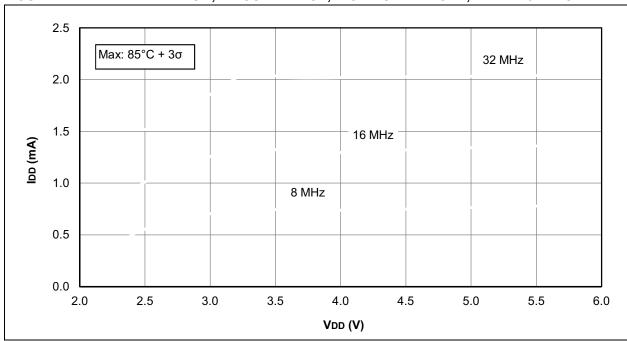

FIGURE 27-12: IDD MAXIMUM, EC OSCILLATOR, HIGH-POWER MODE, PIC12F1571/2 ONLY

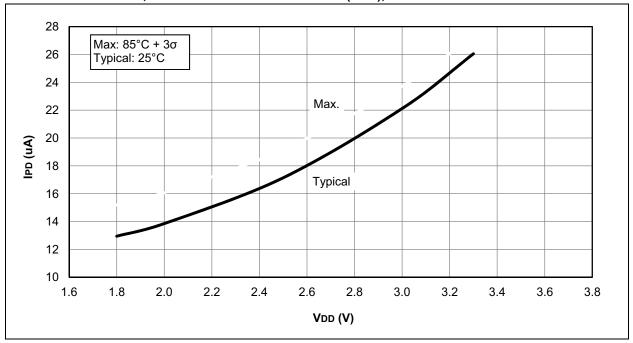

FIGURE 27-25: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC12LF1571/2 ONLY

FIGURE 27-26: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC12F1571/2 ONLY

#### 28.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 28.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 28.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 28.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

## 28.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

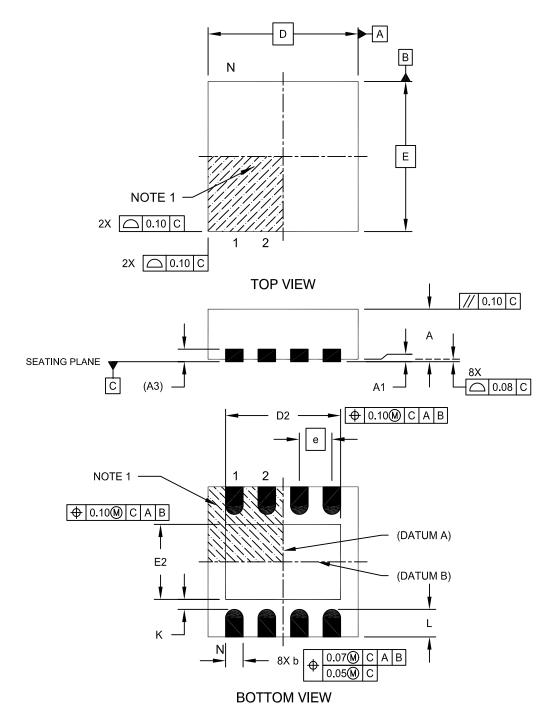

# 8-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-062C Sheet 1 of 2

## 8-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS      |          |          |      |  |

|------------------------|------------------|----------|----------|------|--|

| Dimension              | Dimension Limits |          |          |      |  |

| Number of Pins         | Ν                |          | 8        |      |  |

| Pitch                  | е                |          | 0.65 BSC |      |  |

| Overall Height         | Α                | 0.80     | 0.90     | 1.00 |  |

| Standoff               | A1               | 0.00     | 0.02     | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF |          |      |  |

| Overall Length         | D                |          | 3.00 BSC |      |  |

| Exposed Pad Width      | E2               | 1.34     | -        | 1.60 |  |

| Overall Width          | Е                |          | 3.00 BSC |      |  |

| Exposed Pad Length     | D2               | 1.60     | -        | 2.40 |  |

| Contact Width          | b                | 0.25     | 0.30     | 0.35 |  |

| Contact Length         | L                | 0.20     | 0.30     | 0.55 |  |

| Contact-to-Exposed Pad | K                | 0.20     | 1        | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-062C Sheet 2 of 2