Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-UDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-UDFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1572t-i-rf |

# 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral, thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C, the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

#### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

```

COG1CON0bits.MD = 0x5;

```

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name, MD2, and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

### Example 1:

```

MOVLW ~(1<<G1MD1)

ANDWF COG1CON0,F

MOVLW 1<<G1MD2 | 1<<G1MD0

IORWF COG1CON0,F

```

# Example 2:

```

BSF COG1CON0,G1MD2

BCF COG1CON0,G1MD1

BSF COG1CON0,G1MD0

```

# 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

# 1.1.3.1 Status, Interrupt and Mirror Bits

Status, interrupt enables, interrupt flags and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

# 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

**TABLE 3-10:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr               | Name    | Bit 7     | Bit 6         | Bit 5 | Bit 4  | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on POR, BOR | Value on<br>All Other |  |

|--------------------|---------|-----------|---------------|-------|--------|-------|-----------|-----------|-------|-------------------|-----------------------|--|

|                    |         |           |               |       |        |       |           |           |       | FOR, BOR          | Resets                |  |

| Bank               |         |           |               |       |        |       |           |           |       | 1                 |                       |  |

| 20Ch               | WPUA    | _         | _             |       |        | W     | PUA<5:0>  |           |       | 11 1111           | 11 1111               |  |

| 20Dh               | _       | Unimpleme | nted          |       |        |       |           |           |       | _                 | _                     |  |

| 20Eh<br>to<br>21Fh | _       | Unimpleme | nted          |       | _      | _     |           |           |       |                   |                       |  |

| Bank               | 5       |           |               |       |        |       |           |           |       |                   |                       |  |

| 28Ch               | ODCONA  | _         | _             | ODA   | <5:4>  | _     |           | ODA<2:0>  |       | 11 -111           | 11 -111               |  |

| 28Dh<br>to<br>29Fh | _       | Unimpleme | Jnimplemented |       |        |       |           |           |       |                   |                       |  |

| Bank               | 6       |           |               |       |        |       |           |           |       |                   |                       |  |

| 30Ch               | SLRCONA | _         | _             | SLRA  | ·<5:4> | _     |           | SLRA<2:0> |       | 11 -111           | 11 -111               |  |

| 30Dh<br>to<br>31Fh | _       | Unimpleme | Inimplemented |       |        |       |           |           |       |                   |                       |  |

| Bank               | 7       |           |               |       |        |       |           |           |       |                   |                       |  |

| 38Ch               | INLVLA  | _         | _             |       |        | INI   | .VLA<5:0> |           |       | 11 1111           | 11 1111               |  |

| 38Dh<br>to<br>390h | _       | Unimpleme | nted          |       |        |       |           |           |       | _                 | _                     |  |

| 391h               | IOCAP   | _         | _             |       |        | Ю     | CAP<5:0>  |           |       | 00 0000           | 00 0000               |  |

| 392h               | IOCAN   | _         |               |       |        | IO    | CAN<5:0>  |           |       | 00 0000           | 00 0000               |  |

| 393h               | IOCAF   | _         | _             |       |        | Ю     | CAF<5:0>  |           |       | 00 0000           | 00 0000               |  |

| 394h<br>to<br>39Fh | _       | Unimpleme | nted          |       |        |       |           |           |       | _                 | _                     |  |

| Bank               | 8       |           |               |       |        |       |           |           |       |                   |                       |  |

| 40Ch<br>to<br>41Fh | _       | Unimpleme | nted          |       |        |       |           |           |       | _                 | _                     |  |

| Bank               | 9       |           |               |       |        |       |           |           |       |                   |                       |  |

| 48Ch<br>to<br>49Fh | _       | Unimpleme | nted          |       |        |       |           |           |       | _                 | _                     |  |

**Legend:** x = unknown; u = unchanged; q = value depends on condition; — = unimplemented; r = reserved. Shaded locations are unimplemented, read as '0'. **Note 1:** PIC12F1571/2 only.

2: PIC12(L)F1572 only.

3: Unimplemented, read as '1'.

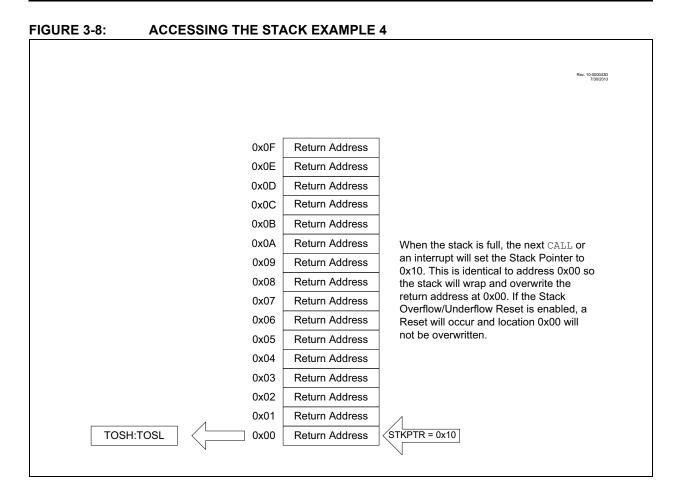

## 3.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in the Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

# 3.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair, FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- · Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

#### **REGISTER 7-2:** PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0             | R/W-0/0             | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------------------|---------------------|-----|-----|---------|---------|

| TMR1GIE | ADIE    | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | _   | _   | TMR2IE  | TMR1IE  |

| bit 7   |         |                     |                     |     |     |         | bit 0   |

Legend:

bit 0

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7 TMR1GIE: Timer1 Gate Interrupt Enable bit

1 = Enables the Timer1 gate acquisition interrupt

0 = Disables the Timer1 gate acquisition interrupt

bit 6 ADIE: Analog-to-Digital Converter (ADC) Interrupt Enable bit

1 = Enables the ADC interrupt

0 = Disables the ADC interrupt

**RCIE:** USART Receive Interrupt Enable bit<sup>(1)</sup> bit 5

1 = Enables the USART receive interrupt

0 = Disables the USART receive interrupt

bit 4 **TXIE:** USART Transmit Interrupt Enable bit<sup>(1)</sup>

1 = Enables the USART transmit interrupt

0 = Disables the USART transmit interrupt

bit 3-2 Unimplemented: Read as '0'

bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

> 1 = Enables the Timer2 to PR2 match interrupt 0 = Disables the Timer2 to PR2 match interrupt

TMR1IE: Timer1 Overflow Interrupt Enable bit

1 = Enables the Timer1 overflow interrupt 0 = Disables the Timer1 overflow interrupt

Note 1: PIC12(L)F1572 only.

Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

Note: Bit PEIE of the INTCON register must be

set to enable any peripheral interrupt.

### REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0 | R/W-0/0 | R-0/0               | R/W-0/0             | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------------------|---------------------|-----|-----|---------|---------|

| TMR1GIF | ADIF    | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | _   | _   | TMR2IF  | TMR1IF  |

| bit 7   |         |                     |                     |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7 TMR1GIF: Timer1 Gate Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 6 ADIF: ADC Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 5 RCIF: USART Receive Interrupt Flag bit<sup>(1)</sup>

1 = Interrupt is pending0 = Interrupt is not pending

bit 4 **TXIF:** USART Transmit Interrupt Flag bit<sup>(1)</sup>

1 = Interrupt is pending0 = Interrupt is not pending

bit 3-2 **Unimplemented:** Read as '0'

bit 1 TMR2IF: Timer2 to PR2 Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 0 TMR1IF: Timer1 Overflow Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

Note 1: PIC12(L)F1572 only.

Note:

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# 8.3 Register Definitions: Voltage Regulator Control

# REGISTER 8-1: VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1  |

|-------|-----|-----|-----|-----|-----|---------|----------|

| _     | _   | _   | _   | _   | _   | VREGPM  | Reserved |

| bit 7 |     |     |     |     |     |         | bit 0    |

Legend:

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7-2 **Unimplemented:** Read as '0'

bit 1 VREGPM: Voltage Regulator Power Mode Selection bit

1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

Draws lowest current in Sleep, slower wake-up.

0 = Normal power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up.

bit 0 Reserved: Read as '1', maintain this bit set

Note 1: PIC12F1571/2 only.

2: See Section 26.0 "Electrical Specifications"

TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name   | Bit 7   | Bit 6  | Bit 5               | Bit 4               | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|--------|---------|--------|---------------------|---------------------|-----------|--------|--------|--------|------------------|

| INTCON | GIE     | PEIE   | TMR0IE              | INTE                | IOCIE     | TMR0IF | INTF   | IOCIF  | 74               |

| IOCAF  | _       | _      | IOCAF5              | IOCAF4              | IOCAF3    | IOCAF2 | IOCAF1 | IOCAF0 | 122              |

| IOCAN  | _       | _      | IOCAN5              | IOCAN4              | IOCAN3    | IOCAN2 | IOCAN1 | IOCAN0 | 121              |

| IOCAP  | _       | _      | IOCAP5              | IOCAP4              | IOCAP3    | IOCAP2 | IOCAP1 | IOCAP0 | 121              |

| PIE1   | TMR1GIE | ADIE   | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | _         | _      | TMR2IE | TMR1IE | 75               |

| PIE2   | _       | _      | C1IE                | _                   | _         | _      | _      | _      | 76               |

| PIE3   | _       | PWM3IE | PWM2IE              | PWM1IE              | _         | _      | _      | _      | 77               |

| PIR1   | TMR1GIF | ADIF   | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | _         | _      | TMR2IF | TMR1IF | 78               |

| PIR2   | _       | _      | C1IF                | _                   | _         | _      | _      | _      | 79               |

| PIR3   | _       | PWM3IF | PWM2IF              | PWM1IF              | _         | _      | _      | _      | 80               |

| STATUS | _       |        |                     | TO                  | PD        | Z      | DC     | С      | 19               |

| WDTCON | _       | _      |                     | V                   | VDTPS<4:0 | >      |        | SWDTEN | 89               |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

Note 1: PIC12(L)F1572 only.

# 11.3 PORTA Registers

#### 11.3.1 DATA REGISTER

PORTA is a 6-bit wide, bidirectional port. The corresponding Data Direction register is TRISA (Register 11-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input-only and its TRISA bit will always read as '1'. Example 11-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 11-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are Read-Modify-Write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the Port Data Latch (LATA).

#### 11.3.2 DIRECTION CONTROL

The TRISA register (Register 11-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.3.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-7) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

## 11.3.4 SLEW RATE CONTROL

The SLRCONA register (Register 11-8) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, the corresponding port pin drive slews at the maximum rate possible.

#### 11.3.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 11-9) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an Interrupt-On-Change occurs, if that feature is enabled. See **Section 26.3 "DC Characteristics"** for more information on threshold levels.

Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 11.3.6 ANALOG CONTROL

Note:

The ANSELA register (Register 11-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSELA set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing Read-Modify-Write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSELA bits must be initialized to '0' by user software.

### **EXAMPLE 11-1: INITIALIZING PORTA**

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

|         | FORTA       |                        |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | digital I/0            |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

# REGISTER 15-4: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |  |  |

|---------|------------|---------|---------|---------|---------|---------|---------|--|--|--|--|--|

|         | ADRES<9:2> |         |         |         |         |         |         |  |  |  |  |  |

| bit 7   |            |         |         |         |         |         | bit 0   |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7-0 ADRES<9:2>: ADC Result Register bits

Upper eight bits of 10-bit conversion result.

# REGISTER 15-5: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADRES<1:0> |         | _       | _       | _       | _       | _       | _       |

| bit 7      |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7-6 **ADRES<1:0>**: ADC Result Register bits

Lower two bits of 10-bit conversion result.

bit 5-0 **Reserved**: Do not use

TABLE 15-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

| Name   | Bit 7    | Bit 6         | Bit 5                           | Bit 4               | Bit 3 | Bit 2   | Bit 1     | Bit 0  | Register on Page |

|--------|----------|---------------|---------------------------------|---------------------|-------|---------|-----------|--------|------------------|

| ADCON0 | _        |               |                                 | CHS<4:0>            |       |         | GO/DONE   | ADON   | 135              |

| ADCON1 | ADFM     |               | ADCS<2:0>                       | •                   | _     | _       | ADPRE     | F<1:0> | 136              |

| ADCON2 |          | TRIGSE        | EL<3:0>                         |                     | _     | _       | _         | _      | 137              |

| ADRESH | ADC Resu | It Register I | High                            |                     |       |         |           |        | 138, 139         |

| ADRESL | ADC Resu | It Register I | _OW                             |                     |       |         |           |        | 138, 139         |

| ANSELA | _        | _             | _                               | ANSA4               | _     |         | ANSA<2:0> |        | 114              |

| INTCON | GIE      | PEIE          | TMR0IE                          | INTE                | IOCIE | TMR0IF  | INTF      | IOCIF  | 74               |

| PIE1   | TMR1GIE  | ADIE          | RCIE <sup>(2)</sup>             | TXIE <sup>(2)</sup> | _     | _       | TMR2IE    | TMR1IE | 75               |

| PIR1   | TMR1GIF  | ADIF          | RCIF <sup>(2)</sup>             | TXIF <sup>(2)</sup> | _     | _       | TMR2IF    | TMR1IF | 78               |

| TRISA  | _        | _             | — TRISA5 TRISA4 —(1) TRISA<2:0> |                     |       |         |           |        | 113              |

| FVRCON | FVREN    | FVRRDY        | TSEN                            | TSRNG               | CDAFV | 'R<1:0> | ADFVF     | R<1:0> | 125              |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for the ADC module.

Note 1: Unimplemented, read as '1'.

2: PIC12(L)F1572 only.

TABLE 21-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                |            |                             |                | SYNC       | = 0, BRG                    | l = 1, BRC     | <b>316 =</b> 0 |                             |                |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc           | = 3.686        | 4 MHz                       | Fos            | c = 1.000  | ) MHz                       |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>Value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>Value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>Value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>Value<br>(decimal) |

| 300    | _              | _          | _                           | _              | _          | _                           |                | _              | _                           | 300            | 0.16       | 207                         |

| 1200   | _              | _          | _                           | 1202           | 0.16       | 207                         | 1200           | 0.00           | 191                         | 1202           | 0.16       | 51                          |

| 2400   | 2404           | 0.16       | 207                         | 2404           | 0.16       | 103                         | 2400           | 0.00           | 95                          | 2404           | 0.16       | 25                          |

| 9600   | 9615           | 0.16       | 51                          | 9615           | 0.16       | 25                          | 9600           | 0.00           | 23                          | _              | _          | _                           |

| 10417  | 10417          | 0.00       | 47                          | 10417          | 0.00       | 23                          | 10473          | 0.53           | 21                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19231          | 0.16       | 25                          | 19.23k         | 0.16       | 12                          | 19.2k          | 0.00           | 11                          | _              | _          | _                           |

| 57.6k  | 55556          | -3.55      | 8                           | _              | _          | _                           | 57.60k         | 0.00           | 3                           | _              | _          | _                           |

| 115.2k | _              | _          |                             | _              | _          | _                           | 115.2k         | 0.00           | 1                           | _              | _          | _                           |

|        |                |            |                             |                | SYNC       | = 0, BRG                    | H = 0, BRG     | 616 = 1    |                             |                |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc           | = 20.00    | 0 MHz                       | Fosc           | = 18.43    | 2 MHz                       | Fosc           | = 16.00    | 0 MHz                       | Fosc           | = 11.059   | 92 MHz                      |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>Value<br>(decimal) |

| 300    | 300.0          | -0.01      | 4166                        | 300.0          | 0.00       | 3839                        | 300.03         | 0.01       | 3332                        | 300.0          | 0.00       | 2303                        |

| 1200   | 1200           | -0.03      | 1041                        | 1200           | 0.00       | 959                         | 1200.5         | 0.04       | 832                         | 1200           | 0.00       | 575                         |

| 2400   | 2399           | -0.03      | 520                         | 2400           | 0.00       | 479                         | 2398           | -0.08      | 416                         | 2400           | 0.00       | 287                         |

| 9600   | 9615           | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9615           | 0.16       | 103                         | 9600           | 0.00       | 71                          |

| 10417  | 10417          | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10417          | 0.00       | 95                          | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k         | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 56.818         | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 58.82k         | 2.12       | 16                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 113.636        | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 111.11k        | -3.55      | 8                           | 115.2k         | 0.00       | 5                           |

|              | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                  |            |                             |                |            |                             |                |            |                             |

|--------------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

|              | Actual<br>Rate                | %<br>Error | SPBRG<br>Value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>Value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>Value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>Value<br>(decimal) |

| 300          | 299.9                         | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0          | 0.00       | 767                         | 300.5          | 0.16       | 207                         |

| 1200         | 1199                          | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202           | 0.16       | 51                          |

| 2400         | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404           | 0.16       | 25                          |

| 9600         | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | _              | _          | _                           |

| 10417        | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417          | 0.00       | 5                           |

| 19.2k        | 19.23k                        | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k         | 0.00       | 11                          | _              | _          | _                           |

| 57.6k        | 55556                         | -3.55      | 8                           | _                | _          | _                           | 57.60k         | 0.00       | 3                           | _              | _          | _                           |

| 115.2k       | _                             | _          | _                           | _                | _          | _                           | 115.2k         | 0.00       | 1                           | _              | _          | _                           |

DS40001723D-page 206

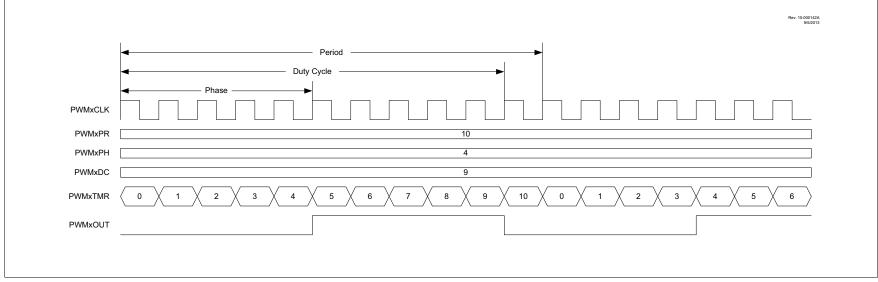

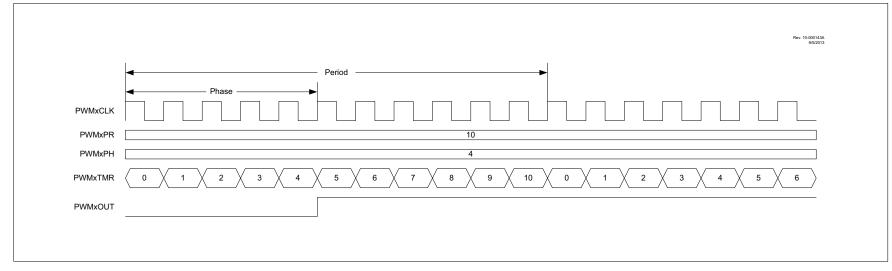

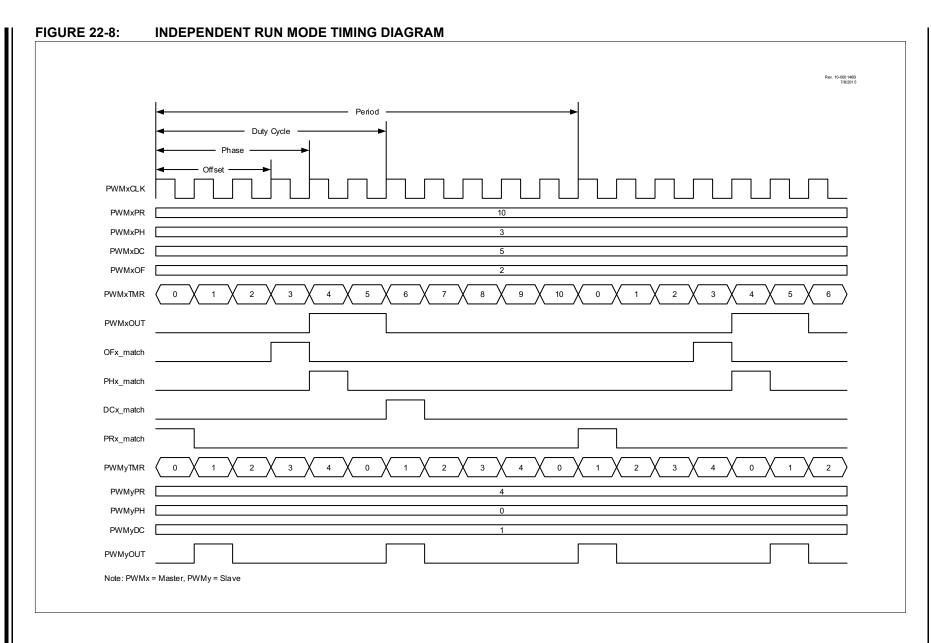

# 22.4 Reload Operation

Four of the PWM module control register pairs and one control bit are double-buffered so that all can be updated simultaneously. These include:

- · PWMxPHH:PWMxPHL register pair

- PWMxDCH:PWMxDCL register pair

- PWMxPRH:PWMxPRL register pair

- PWMxOFH:PWMxOFL register pair

- · OFO control bit

When written to, these registers do not immediately affect the operation of the PWM. By default, writes to these registers will not be loaded into the PWM Operating Buffer registers until after the arming conditions are met. The arming control has two methods of operation:

- · Immediate

- · Triggered

The LDT bit of the PWMxLDCON register controls the arming method. Both methods require the LDA bit to be set. All four buffer pairs will load simultaneously at the loading event.

#### 22.4.1 IMMEDIATE RELOAD

When the LDT bit is clear, then the immediate mode is selected and the buffers will be loaded at the first period event after the LDA bit is set. Immediate reloading is used when a PWM module is operating stand-alone or when the PWM module is operating as a master to other slave PWM modules.

#### 22.4.2 TRIGGERED RELOAD

When the LDT bit is set, then the Triggered mode is selected and a trigger event is required for the LDA bit to take effect. The trigger source is the buffer load event of one of the other PWM modules in the device. The triggering source is selected by the LDS<1:0> bits of the PWMxLDCON register. The buffers will be loaded at the first period event following the trigger event. Triggered reloading is used when a PWM module is operating as a slave to another PWM and it is necessary to synchronize the buffer reloads in both modules.

- Note 1: The buffer load operation clears the LDA bit.

- 2: If the LDA bit is set at the same time as PWMxTMR = PWMxPR, the LDA bit is ignored until the next period event. Such is the case when triggered reload is selected and the triggering event occurs simultaneously with the target's period event.

# 22.5 Operation in Sleep Mode

Each PWM module will continue to operate in Sleep mode when either the HFINTOSC or LFINTOSC is selected as the clock source by PWMxCLKCON<1:0>.

# 22.6 Interrupts

Each PWM module has four independent interrupts based on the phase, duty cycle, period and offset match events. The interrupt flag is set on the rising edge of each of these signals. Refer to Figures 22-12 and 22-13 for detailed timing diagrams of the match signals.

# 23.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces a complementary waveform with dead-band delay from a selection of input sources.

The CWG module has the following features:

- · Selectable dead-band clock source control

- · Selectable input sources

- · Output enable control

- · Output polarity control

- Dead-band control with independent 6-bit rising and falling edge dead-band counters

- · Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

# 23.1 Fundamental Operation

The CWG generates two output waveforms from the selected input source.

The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time delay immediately where neither output is driven. This is referred to as dead time and is covered in **Section 23.5 "Dead-Band Control"**. A typical operating waveform with dead band, generated from a single input signal, is shown in Figure 23-2.

It may be necessary to guard against the possibility of circuit Faults or a feedback event arriving too late, or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 23.9 "Auto-Shutdown Control"**.

# 23.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the G1CS0 bit of the CWGxCON0 register (Register 23-1).

# 23.3 Selectable Input Sources

The CWG generates the output waveforms from the input sources in Table 23-1.

TABLE 23-1: SELECTABLE INPUT SOURCES

| Source Peripheral | Signal Name |  |  |

|-------------------|-------------|--|--|

| Comparator C1     | C1OUT_sync  |  |  |

| PWM1              | PWM1_output |  |  |

| PWM2              | PWM2_output |  |  |

| PWM3              | PWM3_output |  |  |

The input sources are selected using the GxIS<2:0> bits in the CWGxCON1 register (Register 23-2).

# 23.4 Output Control

Immediately after the CWG module is enabled, the complementary drive is configured with both CWGxA and CWGxB drives cleared.

#### 23.4.1 OUTPUT ENABLES

Each CWG output pin has individual output enable control. Output enables are selected with the GxOEA and GxOEB bits of the CWGxCON0 register. When an output enable control is cleared, the module asserts no control over the pin. When an output enable is set, the override value or active PWM waveform is applied to the pin per the port priority selection. The output pin enables are dependent on the module enable bit, GxEN. When GxEN is cleared, CWG output enables and CWG drive levels have no effect.

# 23.4.2 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the GxPOLA and GxPOLB bits of the CWGxCON0 register.

| BCF              | Bit Clear f                         |  |  |  |

|------------------|-------------------------------------|--|--|--|

| Syntax:          | [ label ] BCF f,b                   |  |  |  |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$   |  |  |  |

| Operation:       | $0 \rightarrow (f < b >)$           |  |  |  |

| Status Affected: | None                                |  |  |  |

| Description:     | Bit 'b' in register 'f' is cleared. |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                       |

| Operands:        | $\begin{aligned} 0 &\leq f \leq 127 \\ 0 &\leq b \leq 7 \end{aligned}$                                                                                                                                                    |

| Operation:       | skip if (f < b >) = 0                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                      |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed. If bit 'b', in register 'f', is '0', the next instruction is discarded, and a $\mathtt{NOP}$ is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BRA label<br>[ <i>label</i> ] BRA \$+k                                                                                                                                                                       |

| Operands:        | -256 ≤ label - PC + 1 ≤ 255<br>-256 ≤ k ≤ 255                                                                                                                                                                                 |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| perands:         | $-256 \le label - PC + 1 \le 255$<br>$-256 \le k \le 255$                                                                                                                                                                     |

| peration:        | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |

| status Affected: | None                                                                                                                                                                                                                          |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |

| BRW              | Relative Branch with W                                                                                                                                                                         |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] BRW                                                                                                                                                                                  |  |  |  |

| Operands:        | None                                                                                                                                                                                           |  |  |  |

| Operation:       | $(PC) + (W) \rightarrow PC$                                                                                                                                                                    |  |  |  |

| Status Affected: | None                                                                                                                                                                                           |  |  |  |

| Description:     | Add the contents of W (unsigned) to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + (W). This instruction is a 2-cycle instruction. |  |  |  |

| BSF              | Bit Set f                                                              |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [ label ] BSF f,b                                                      |

| Operands:        | $\begin{aligned} 0 &\leq f \leq 127 \\ 0 &\leq b \leq 7 \end{aligned}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                              |

| Status Affected: | None                                                                   |

| Description:     | Bit 'b' in register 'f' is set.                                        |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.  If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2-cycle instruction. |

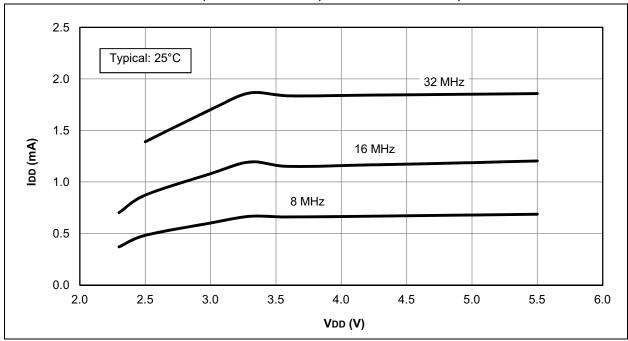

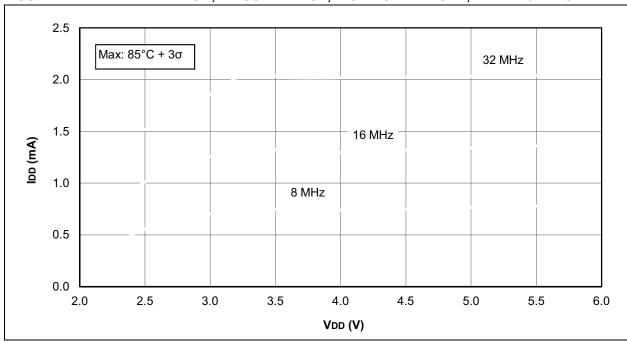

FIGURE 27-12: IDD MAXIMUM, EC OSCILLATOR, HIGH-POWER MODE, PIC12F1571/2 ONLY

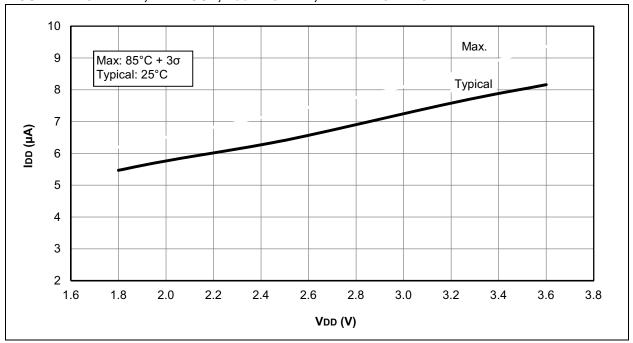

FIGURE 27-13: IDD, LFINTOSC, Fosc = 31 kHz, PIC12LF1571/2 ONLY

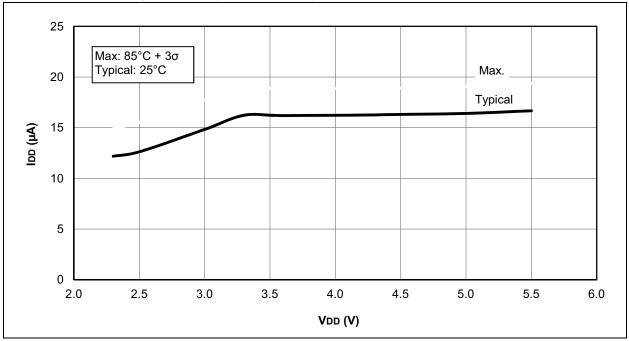

FIGURE 27-14: IDD, LFINTOSC, Fosc = 31 kHz, PIC12F1571/2 ONLY

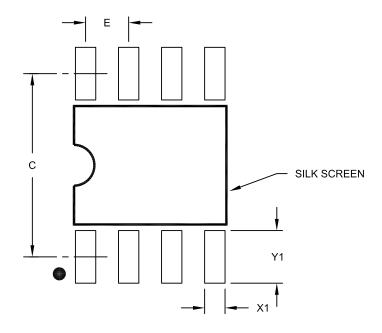

# 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | MILLIMETERS |     |          |      |

|-------------------------|-------------|-----|----------|------|

| Dimension               | MIN         | NOM | MAX      |      |

| Contact Pitch           | E           |     | 1.27 BSC |      |

| Contact Pad Spacing     | С           |     | 5.40     |      |

| Contact Pad Width (X8)  | X1          |     |          | 0.60 |

| Contact Pad Length (X8) | Y1          |     |          | 1.55 |

# Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A