Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-UDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-UDFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1571-e-rf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

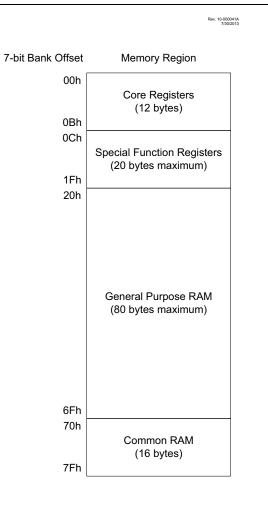

## 3.3.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses: x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

## 3.3.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses: x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.3.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2 "Linear Data Memory"** for more information.

#### 3.3.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### 3.3.5 DEVICE MEMORY MAPS

The memory maps for PIC12(L)F1571/2 are as shown in Table 3-3 through Table 3-8.

#### FIGURE 3-3: BANKED MEMORY PARTITIONING

## TABLE 3-6: PIC12(L)F1571/2 MEMORY MAP, BANK 24-31

|      | BANK 24                       |      | BANK 25                       |      | BANK 26                       |      | BANK 27                               |      | BANK 28                       |                                       | BANK 29                       |      | BANK 30                       |      | BANK 31                       |      |   |                                       |   |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|---------------------------------------|------|-------------------------------|---------------------------------------|-------------------------------|------|-------------------------------|------|-------------------------------|------|---|---------------------------------------|---|

| C00h | Core Registers<br>(Table 3-2) | C80h | Core Registers<br>(Table 3-2) | D00h | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2)         | E00h | Core Registers<br>(Table 3-2) | E80h                                  | Core Registers<br>(Table 3-2) | F00h | Core Registers<br>(Table 3-2) | F80h | Core Registers<br>(Table 3-2) |      |   |                                       |   |

| C0Bh | ( /                           | C8Bh | ( ,                           | D0Bh | ( /                           | D8Bh | ( /                                   | E0Bh | ( /                           | E8Bh                                  | ( /                           | F0Bh | ( /                           | F8Bh | ( /                           |      |   |                                       |   |

| C0Ch | _                             | C8Ch | _                             | D0Ch | _                             | D8Ch |                                       | E0Ch | —                             | E8Ch                                  | —                             | F0Ch | —                             | F8Ch |                               |      |   |                                       |   |

| C0Dh | _                             | C8Dh | _                             | D0Dh | _                             |      |                                       | E0Dh | —                             | E8Dh                                  | —                             | F0Dh | —                             |      |                               |      |   |                                       |   |

| C0Eh | _                             | C8Eh | _                             | D0Eh | _                             |      |                                       | E0Eh | _                             | E8Eh                                  | _                             | F0Eh | _                             |      |                               |      |   |                                       |   |

| C0Fh |                               | C8Fh | _                             | D0Fh | _                             |      |                                       | E0Fh |                               | E8Fh                                  |                               | F0Fh |                               |      |                               |      |   |                                       |   |

| C10h | _                             | C90h | _                             | D10h | _                             |      |                                       | E10h | —                             | E90h                                  | —                             | F10h | —                             |      |                               |      |   |                                       |   |

| C11h | _                             | C91h | _                             | D11h | _                             |      |                                       | E11h | —                             | E91h                                  | —                             | F11h | —                             |      |                               |      |   |                                       |   |

| C12h | _                             | C92h | _                             | D12h | _                             |      |                                       | E12h | —                             | E92h                                  | —                             | F12h | —                             |      |                               |      |   |                                       |   |

| C13h | _                             | C93h | _                             | D13h | _                             |      |                                       | E13h | —                             | E93h                                  | —                             | F13h | —                             |      |                               |      |   |                                       |   |

| C14h | _                             | C94h | _                             | D14h | —                             |      |                                       | E14h | _                             | E94h                                  |                               | F14h | _                             |      |                               |      |   |                                       |   |

| C15h | -                             | C95h | -                             | D15h |                               |      |                                       | E15h | —                             | E95h                                  | —                             | F15h | —                             |      |                               |      |   |                                       |   |

| C16h | _                             | C96h | _                             | D16h | _                             |      |                                       | E16h | —                             | E96h                                  | —                             | F16h | —                             |      |                               |      |   |                                       |   |

| C17h | _                             | C97h | _                             | D17h | —                             |      | See Table 3-7 for<br>Register Mapping |      |                               | See Table 3-7 for<br>Register Mapping | 0                             | E17h | _                             | E97h |                               | F17h | _ |                                       | 0 |

| C18h |                               | C98h | _                             | D18h | _                             |      |                                       |      |                               |                                       | E18h                          |      | E98h                          |      | F18h                          |      | 1 | See Table 3-7 for<br>Register Mapping |   |

| C19h | _                             | C99h | _                             | D19h | _                             |      | Details                               | E19h | —                             | E99h                                  | —                             | F19h | —                             |      | Details                       |      |   |                                       |   |

| C1Ah | _                             | C9Ah | _                             | D1Ah | —                             |      |                                       | E1Ah | _                             | E9Ah                                  |                               | F1Ah | _                             |      |                               |      |   |                                       |   |

| C1Bh | -                             | C9Bh | -                             | D1Bh |                               |      |                                       | E1Bh | —                             | E9Bh                                  | —                             | F1Bh | —                             |      |                               |      |   |                                       |   |

| C1Ch | _                             | C9Ch | _                             | D1Ch | _                             |      |                                       | E1Ch | —                             | E9Ch                                  | —                             | F1Ch | —                             |      |                               |      |   |                                       |   |

| C1Dh | _                             | C9Dh | _                             | D1Dh | —                             |      |                                       | E1Dh | _                             | E9Dh                                  |                               | F1Dh | _                             |      |                               |      |   |                                       |   |

| C1Eh |                               | C9Eh | _                             | D1Eh | _                             |      |                                       | E1Eh |                               | E9Eh                                  |                               | F1Eh |                               |      |                               |      |   |                                       |   |

| C1Fh | _                             | C9Fh | _                             | D1Fh | _                             |      |                                       | E1Fh | —                             | E9Fh                                  | —                             | F1Fh | —                             |      |                               |      |   |                                       |   |

| C20h |                               | CA0h |                               | D20h |                               |      |                                       | E20h |                               | EA0h                                  |                               | F20h |                               |      |                               |      |   |                                       |   |

|      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      |                                       |      | Unimplemented<br>Read as '0'  |                                       | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      |                               |      |   |                                       |   |

| C6Fh |                               | CEFh |                               | D6Fh |                               | DEFh |                                       | E6Fh |                               | EEFh                                  |                               | F6Fh |                               | FEFh |                               |      |   |                                       |   |

| C70h |                               | CF0h |                               | D70h |                               | DF0h |                                       | E70h |                               | EF0h                                  |                               | F70h |                               | FF0h |                               |      |   |                                       |   |

|      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh                   |      | Accesses<br>70h-7Fh           |                                       | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh           |      |   |                                       |   |

| CFFh |                               | CFFh |                               | D7Fh |                               | DFFh |                                       | E7Fh |                               | EFFh                                  |                               | F7Fh |                               | FFFh |                               |      |   |                                       |   |

Legend: 🔲 = Unimplemented data memory locations, read as '0'.

# 5.0 OSCILLATOR MODULE

## 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications, while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources

The oscillator module can be configured in one of the following clock modes:

- 1. ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. INTOSC Internal Oscillator (31 kHz to 32 MHz)

Clock Source modes are selected by the FOSC<1:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The ECH, ECM, and ECL Clock modes rely on an external logic level signal as the device clock source.

The INTOSC internal oscillator block produces low, medium and high-frequency clock sources, designated as LFINTOSC, MFINTOSC and HFINTOSC (see Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these three clock sources.

## 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | х   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is Set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, PD is Set on POR                                         |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during Normal Operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

## TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

| ADC Clock              | Period (TAD) | Device Frequency (Fosc) |            |            |            |            |  |  |  |  |

|------------------------|--------------|-------------------------|------------|------------|------------|------------|--|--|--|--|

| ADC<br>Clock<br>Source | ADCS<2:0>    | 20 MHz 16 MHz 8 MHz     |            | 8 MHz      | 4 MHz      | 1 MHz      |  |  |  |  |

| Fosc/2                 | 000          | 100 ns                  | 125 ns     | 250 ns     | 500 ns     | 2.0 μs     |  |  |  |  |

| Fosc/4                 | 100          | 200 ns                  | 250 ns     | 500 ns     | 1.0 μs     | 4.0 μs     |  |  |  |  |

| Fosc/8                 | 001          | 400 ns                  | 500 ns     | 1.0 μs     | 2.0 μs     | 8.0 μs     |  |  |  |  |

| Fosc/16                | 101          | 800 ns                  | 1.0 μs     | 2.0 μs     | 4.0 μs     | 16.0 μs    |  |  |  |  |

| Fosc/32                | 010          | 1.6 μs                  | 2.0 μs     | 4.0 μs     | 8.0 μs     | 32.0 μs    |  |  |  |  |

| Fosc/64                | 110          | 3.2 μs                  | 4.0 μs     | 8.0 μs     | 16.0 μs    | 64.0 μs    |  |  |  |  |

| FRC                    | x11          | 1.0-6.0 μs              | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs |  |  |  |  |

## TABLE 15-1: ADC CLOCK PERIOD (TAD) VS. DEVICE OPERATING FREQUENCIES

**Legend:** Shaded cells are outside of recommended range.

**Note:** The TAD period when using the FRC clock source can fall within a specified range (see TAD parameter). The TAD period when using the FOSC-based clock source can be configured for a more precise TAD period. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

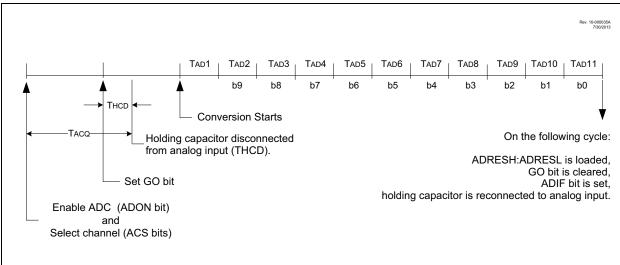

#### FIGURE 15-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

## REGISTER 15-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u    | R/W-x/u |  |

|---------|---------|---------|---------|---------|---------|------------|---------|--|

| —       | —       | —       | —       | —       | —       | ADRES<9:8> |         |  |

| bit 7   |         |         |         |         |         |            | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 1-0 **ADRES<9:8>**: ADC Result Register bits Upper two bits of 10-bit conversion result.

## **REGISTER 15-7:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |  |  |  |

|---------|------------|---------|---------|---------|---------|---------|---------|--|--|--|--|--|--|

|         | ADRES<7:0> |         |         |         |         |         |         |  |  |  |  |  |  |

| bit 7   |            |         |         |         |         |         | bit 0   |  |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result.

| IGURE 19-5:                      | TIMER1 GATE SINGLE-PULSE MODE                                                              |

|----------------------------------|--------------------------------------------------------------------------------------------|

| TMR1GE                           |                                                                                            |

| T1GPOL                           |                                                                                            |

| T1GSPM<br>T <u>1GGO/</u><br>DONE | Cleared by Hardware on<br>Falling Edge of T1GVAL                                           |

| t1g_in                           | Counting Enabled on<br>Rising Edge of T1G                                                  |

| T1CKI                            |                                                                                            |

| T1GVAL                           |                                                                                            |

| Timer1                           | N N + 1 N + 2                                                                              |

| TMR1GIF                          | Cleared by Software Cleared by Software Set by Hardware on Software Falling Edge of T1GVAL |

| Name    | Bit 7      | Bit 6          | Bit 5               | Bit 4               | Bit 3          | Bit 2     | Bit 1           | Bit 0  | Register<br>on Page |

|---------|------------|----------------|---------------------|---------------------|----------------|-----------|-----------------|--------|---------------------|

| ANSELA  |            |                | _                   | ANSA4               | _              | ANSA<2:0> |                 |        | 114                 |

| APFCON  | RXDTSEL    | CWGASEL        | CWGBSEL             | _                   | T1GSEL         | TXCKSEL   | P2SEL           | P1SEL  | 110                 |

| INTCON  | GIE        | PEIE           | TMR0IE              | INTE                | IOCIE          | TMR0IF    | INTF            | IOCIF  | 74                  |

| OSCSTAT | —          | PLLR           | OSTS                | HFIOFR              | HFIOFL         | MFIOFR    | LFIOFR          | HFIOFS | 56                  |

| PIE1    | TMR1GIE    | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | _              | _         | TMR2IE          | TMR1IE | 75                  |

| PIR1    | TMR1GIF    | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | _              | _         | — TMR2IF TMR1IF |        | 79                  |

| TMR1H   | Holding Re | gister for the | Most Signific       | ant Byte of         | the 16-bit TM  | MR1 Count |                 |        | 163*                |

| TMR1L   | Holding Re | gister for the | Least Signifi       | cant Byte of        | the 16-bit T   | MR1 Count |                 |        | 163*                |

| TRISA   | —          | _              | TRISA               | <5:4>               | _(1)           | Т         | RISA<2:0        | >      | 113                 |

| T1CON   | TMR10      | CS<1:0>        | T1CKPS              | S<1:0>              | _              | T1SYNC    |                 | TMR10N | 167                 |

| T1GCON  | TMR1GE     | T1GPOL         | T1GTM               | T1GSPM              | T1GGO/<br>DONE | T1GVAL    | T1GSS<1:0>      |        | 168                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

Note 1: Unimplemented, read as '1'.

2: PIC12(L)F1572 only.

## 21.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH/SPBRGL register pair determines the period of the free-running baud rate timer. In Asynchronous mode, the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 21-3 contains the formulas for determining the baud rate. Example 21-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 21-3. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH/SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is Idle before changing the system clock.

## EXAMPLE 21-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

$Desired Baud Rate = \frac{Fosc}{64([SPBRGH:SPBRGL] + 1)}$ Solving for SPBRGH:SPBRGL:  $\frac{Fosc}{Desired Baud Rate}$

$X = \frac{\overline{Desired Baud Rate}}{64} - 1$  $= \frac{\frac{16000000}{9600}}{64} - 1$ = [25.042] = 25Calculated Baud Rate =  $\frac{16000000}{64(25+1)}$ = 9615Error =  $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$  $= \frac{(9615 - 9600)}{9600} = 0.16\%$

## TABLE 21-3: BAUD RATE FORMULAS

| C    | onfiguration B | its  |                     | Baud Rate Formula |

|------|----------------|------|---------------------|-------------------|

| SYNC | BRG16          | BRGH | BRG/EUSART Mode     | Bauu Kale Formula |

| 0    | 0              | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |

| 0    | 0              | 1    | 8-bit/Asynchronous  |                   |

| 0    | 1              | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |

| 0    | 1              | 1    | 16-bit/Asynchronous |                   |

| 1    | 0              | x    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |

| 1    | 1              | x    | 16-bit/Synchronous  |                   |

**Legend:** x = Don't care; n = value of SPBRGH/SPBRGL register pair.

## TABLE 21-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|-----------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUDCON | ABDOVF    | RCIDL | _     | SCKP  | BRG16 | _     | WUE   | ABDEN | 186                 |

| RCSTA   | SPEN      | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 185                 |

| SPBRGL  | BRG<7:0>  |       |       |       |       |       |       |       |                     |

| SPBRGH  | BRG<15:8> |       |       |       |       |       |       | 187*  |                     |

| TXSTA   | CSRC      | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 184                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

| REGISTER 22-13: | PWMxOFH: PWMx OFFSET COUNT HIGH REGISTER |

|-----------------|------------------------------------------|

|-----------------|------------------------------------------|

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | OF<     | 15:8>          |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable I    | oit     |                |                  |                  |              |

| u = Bit is uncha | anged   | x = Bit is unkn   | own     | U = Unimpler   | nented bit, read | d as '0'         |              |

| '1' = Bit is set |         | '0' = Bit is clea | ared    | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

bit 7-0 OF<15:8>: PWMx Offset High bits Upper eight bits of PWM offset count.

## REGISTER 22-14: PWMxOFL: PWMx OFFSET COUNT LOW REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | OF<     | 7:0>    |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-0 OF<7:0>: PWMx Offset Low bits Lower eight bits of PWM offset count.

PIC12(L)F1571/2

| Mnemonic,                                                          |                                                                   | Description                                                                                                                                                                                                  | Quality                                                                                               | 14-Bit Opcode                                      |                                                              |                                                      |                                                             | Status        | N . 4 |

|--------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|---------------|-------|

| Oper                                                               | •                                                                 | Description                                                                                                                                                                                                  | Cycles                                                                                                | MSb                                                |                                                              |                                                      | LSb                                                         | Affected      | Notes |

|                                                                    |                                                                   | BYTE-ORIENTED FILE                                                                                                                                                                                           | REGISTER OPE                                                                                          | RATIO                                              | NS                                                           |                                                      |                                                             |               |       |

| ADDWF                                                              | f, d                                                              | Add W and f                                                                                                                                                                                                  | 1                                                                                                     | 00                                                 | 0111                                                         | dfff                                                 | ffff                                                        | C, DC, Z      | 2     |

| ADDWFC                                                             | f, d                                                              | Add with Carry W and f                                                                                                                                                                                       | 1                                                                                                     | 11                                                 | 1101                                                         | dfff                                                 | ffff                                                        | C, DC, Z      | 2     |

| ANDWF                                                              | f, d                                                              | AND W with f                                                                                                                                                                                                 | 1                                                                                                     | 00                                                 | 0101                                                         | dfff                                                 | ffff                                                        | Z             | 2     |

| ASRF                                                               | f, d                                                              | Arithmetic Right Shift                                                                                                                                                                                       | 1                                                                                                     | 11                                                 | 0111                                                         | dfff                                                 | ffff                                                        | C, Z          | 2     |

| LSLF                                                               | f, d                                                              | Logical Left Shift                                                                                                                                                                                           | 1                                                                                                     | 11                                                 | 0101                                                         | dfff                                                 | ffff                                                        | C, Z          | 2     |

| LSRF                                                               | f, d                                                              | Logical Right Shift                                                                                                                                                                                          | 1                                                                                                     | 11                                                 | 0110                                                         | dfff                                                 | ffff                                                        | C, Z          | 2     |

| CLRF                                                               | f                                                                 | Clear f                                                                                                                                                                                                      | 1                                                                                                     | 00                                                 | 0001                                                         | lfff                                                 | ffff                                                        | z             | 2     |

| CLRW                                                               | _                                                                 | Clear W                                                                                                                                                                                                      | 1                                                                                                     | 00                                                 |                                                              | 0000                                                 |                                                             | z             |       |

| COMF                                                               | f, d                                                              | Complement f                                                                                                                                                                                                 | 1                                                                                                     | 00                                                 |                                                              | dfff                                                 |                                                             | Z             | 2     |

| DECF                                                               | f, d                                                              | Decrement f                                                                                                                                                                                                  | 1                                                                                                     | 00                                                 | 0011                                                         |                                                      |                                                             | Z             | 2     |

| INCF                                                               | f, d                                                              | Increment f                                                                                                                                                                                                  | 1                                                                                                     | 00                                                 |                                                              | dfff                                                 |                                                             | Z             | 2     |

| IORWF                                                              | f, d                                                              | Inclusive OR W with f                                                                                                                                                                                        | 1                                                                                                     | 00                                                 | 0100                                                         |                                                      | ffff                                                        |               | 2     |

| MOVF                                                               | f, d                                                              | Move f                                                                                                                                                                                                       | 1                                                                                                     | 00                                                 |                                                              | dfff                                                 |                                                             | Z             | 2     |

| MOVWF                                                              | f, u                                                              | Move W to f                                                                                                                                                                                                  | 1                                                                                                     | 00                                                 | 0000                                                         | 1fff                                                 |                                                             | 2             | 2     |

| RLF                                                                | f. d                                                              | Rotate Left f through Carry                                                                                                                                                                                  | 1                                                                                                     | 00                                                 |                                                              | dfff                                                 |                                                             | с             | 2     |

|                                                                    | , -                                                               |                                                                                                                                                                                                              | 1                                                                                                     |                                                    |                                                              |                                                      |                                                             | -             | 2     |

| RRF                                                                | f, d                                                              | Rotate Right f through Carry                                                                                                                                                                                 | -                                                                                                     | 00                                                 |                                                              | dfff                                                 |                                                             | C<br>C DC 7   |       |

| SUBWF                                                              | f, d                                                              | Subtract W from f                                                                                                                                                                                            | 1                                                                                                     | 00                                                 |                                                              | dfff                                                 |                                                             | , ,           | 2     |

| SUBWFB                                                             | f, d                                                              | Subtract with Borrow W from f                                                                                                                                                                                | 1                                                                                                     | 11                                                 |                                                              | dfff                                                 |                                                             | C, DC, Z      | 2     |

| SWAPF                                                              | f, d                                                              | Swap nibbles in f                                                                                                                                                                                            | 1                                                                                                     | 00                                                 | 1110                                                         | dfff                                                 |                                                             | _             | 2     |

| XORWF                                                              | f, d                                                              | Exclusive OR W with f                                                                                                                                                                                        | 1                                                                                                     | 00                                                 | 0110                                                         | dfff                                                 | tttt                                                        | Z             | 2     |

|                                                                    | r                                                                 | BYTE-ORIENTED                                                                                                                                                                                                | SKIP OPERATIO                                                                                         | ONS                                                | T                                                            | 1                                                    | 1                                                           | n             | 1     |

| DECFSZ                                                             | f, d                                                              | Decrement f, Skip if 0                                                                                                                                                                                       | 1(2)                                                                                                  | 00                                                 | 1011                                                         | dfff                                                 | ffff                                                        |               | 1, 2  |

| INCFSZ                                                             | f, d                                                              | Increment f, Skip if 0                                                                                                                                                                                       | 1(2)                                                                                                  | 00                                                 | 1111                                                         | dfff                                                 | ffff                                                        |               | 1, 2  |

|                                                                    |                                                                   | BIT-ORIENTED FILE                                                                                                                                                                                            | REGISTER OPER                                                                                         | ATION                                              | IS                                                           |                                                      |                                                             |               |       |

|                                                                    | f, b                                                              | Bit Clear f                                                                                                                                                                                                  | 1                                                                                                     | 01                                                 | 00bb                                                         | bfff                                                 | ffff                                                        |               | 2     |

| BCF                                                                |                                                                   |                                                                                                                                                                                                              |                                                                                                       |                                                    |                                                              |                                                      |                                                             |               | 0     |

| BCF<br>BSF                                                         | f, b                                                              | Bit Set f                                                                                                                                                                                                    | 1                                                                                                     | 01                                                 | 01bb                                                         | bfff                                                 | ffff                                                        |               | 2     |

|                                                                    | ,                                                                 |                                                                                                                                                                                                              |                                                                                                       |                                                    | 01bb                                                         | bfff                                                 | ffff                                                        |               | Z     |

|                                                                    | ,                                                                 | BIT-ORIENTED<br>Bit Test f, Skip if Clear                                                                                                                                                                    | 1                                                                                                     |                                                    |                                                              |                                                      | ffff                                                        |               | 1, 2  |

| BSF                                                                | f, b                                                              | BIT-ORIENTED                                                                                                                                                                                                 | 1<br>SKIP OPERATIO                                                                                    | NS                                                 | 10bb                                                         |                                                      | ffff                                                        |               | 1     |

| BSF                                                                | f, b<br>f, b                                                      | BIT-ORIENTED<br>Bit Test f, Skip if Clear<br>Bit Test f, Skip if Set                                                                                                                                         | 1<br>SKIP OPERATION<br>1 (2)                                                                          | NS<br>01                                           | 10bb                                                         | bfff                                                 | ffff                                                        |               | 1, 2  |

| BSF                                                                | f, b<br>f, b                                                      | BIT-ORIENTED<br>Bit Test f, Skip if Clear<br>Bit Test f, Skip if Set                                                                                                                                         | 1<br>SKIP OPERATION<br>1 (2)<br>1 (2)<br>DPERATIONS<br>1                                              | NS<br>01                                           | 10bb<br>11bb                                                 | bfff                                                 | ffff<br>ffff                                                | C, DC, Z      | 1, 2  |

| BSF<br>BTFSC<br>BTFSS                                              | f, b<br>f, b<br>f, b                                              | BIT-ORIENTED<br>Bit Test f, Skip if Clear<br>Bit Test f, Skip if Set<br>LITERAL                                                                                                                              | 1<br>SKIP OPERATION<br>1 (2)<br>1 (2)<br>OPERATIONS                                                   | NS<br>01<br>01                                     | 10bb<br>11bb                                                 | bfff<br>bfff                                         | ffff<br>ffff<br>kkkk                                        | C, DC, Z<br>Z | 1, 2  |

| BSF<br>BTFSC<br>BTFSS<br>ADDLW                                     | f, b<br>f, b<br>f, b<br>k                                         | BIT-ORIENTED<br>Bit Test f, Skip if Clear<br>Bit Test f, Skip if Set<br>LITERAL O<br>Add literal and W                                                                                                       | 1<br>SKIP OPERATION<br>1 (2)<br>1 (2)<br>DPERATIONS<br>1                                              | NS<br>01<br>01<br>11                               | 10bb<br>11bb<br>1110<br>1110                                 | bfff<br>bfff<br>kkkk                                 | ffff<br>ffff<br>kkkk<br>kkkk                                |               | 1, 2  |

| BSF<br>BTFSC<br>BTFSS<br>ADDLW<br>ANDLW                            | f, b<br>f, b<br>f, b<br>k<br>k<br>k                               | Bit Test f, Skip if Clear<br>Bit Test f, Skip if Set<br>LITERAL O<br>Add literal and W<br>AND literal with W                                                                                                 | 1<br>SKIP OPERATION<br>1 (2)<br>1 (2)<br>DPERATIONS<br>1<br>1<br>1                                    | NS<br>01<br>01<br>11                               | 10bb<br>11bb<br>1110<br>1110                                 | bfff<br>bfff<br>kkkk<br>kkkk                         | ffff<br>ffff<br>kkkk<br>kkkk<br>kkkk                        | Z             | 1, 2  |

| BSF<br>BTFSC<br>BTFSS<br>ADDLW<br>ANDLW<br>IORLW                   | f, b<br>f, b<br>f, b<br>k<br>k<br>k<br>k<br>k                     | Bit Test f, Skip if Clear<br>Bit Test f, Skip if Set<br>LITERAL<br>Add literal and W<br>AND literal with W<br>Inclusive OR literal with W                                                                    | 1<br>SKIP OPERATION<br>1 (2)<br>1 (2)<br>DPERATIONS<br>1<br>1<br>1<br>1<br>1                          | NS<br>01<br>01<br>11<br>11                         | 10bb<br>11bb<br>1110<br>1001<br>1000<br>0000                 | bfff<br>bfff<br>kkkk<br>kkkk<br>kkkk                 | ffff<br>ffff<br>kkkk<br>kkkk<br>kkkk<br>kkkk                | Z             | 1, 2  |

| BSF<br>BTFSC<br>BTFSS<br>ADDLW<br>ANDLW<br>IORLW<br>MOVLB<br>MOVLP | f, b<br>f, b<br>f, b<br>k<br>k<br>k<br>k<br>k<br>k<br>k           | Bit Test f, Skip if Clear<br>Bit Test f, Skip if Set<br>LITERAL O<br>Add literal and W<br>AND literal with W<br>Inclusive OR literal with W<br>Move literal to BSR                                           | 1<br>SKIP OPERATION<br>1 (2)<br>1 (2)<br>DPERATIONS<br>1<br>1<br>1<br>1<br>1<br>1<br>1                | NS<br>01<br>01<br>11<br>11<br>11<br>00             | 10bb<br>11bb<br>1110<br>1001<br>1000<br>0000<br>0001         | bfff<br>bfff<br>kkkk<br>kkkk<br>kkkk<br>001k         | ffff<br>ffff<br>kkkk<br>kkkk<br>kkkk<br>kkkk<br>kkkk        | Z             | 1, 2  |

| BSF<br>BTFSC<br>BTFSS<br>ADDLW<br>ANDLW<br>IORLW<br>MOVLB          | f, b<br>f, b<br>f, b<br>k<br>k<br>k<br>k<br>k<br>k<br>k<br>k<br>k | BIT-ORIENTED<br>Bit Test f, Skip if Clear<br>Bit Test f, Skip if Set<br>LITERAL 0<br>Add literal and W<br>AND literal with W<br>Inclusive OR literal with W<br>Move literal to BSR<br>Move literal to PCLATH | 1<br>SKIP OPERATION<br>1 (2)<br>1 (2)<br>DPERATIONS<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | NS<br>01<br>01<br>11<br>11<br>11<br>11<br>00<br>11 | 10bb<br>11bb<br>1110<br>1001<br>1000<br>0000<br>0001<br>0000 | bfff<br>bfff<br>kkkk<br>kkkk<br>kkkk<br>001k<br>1kkk | ffff<br>ffff<br>kkkk<br>kkkk<br>kkkk<br>kkkk<br>kkkk<br>kkk | Z             | 1, 2  |

## TABLE 25-3: ENHANCED MID-RANGE INSTRUCTION SET

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

3: See the table in the MOVIW and MOVWI instruction descriptions.

# PIC12(L)F1571/2

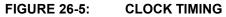

## TABLE 26-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Stanuaru      |      |                                         |      |      |      |       |                      |  |  |  |

|---------------|------|-----------------------------------------|------|------|------|-------|----------------------|--|--|--|

| Param.<br>No. | Sym. | Characteristic                          | Min. | Тур† | Max. | Units | Conditions           |  |  |  |

| OS01          | Fosc | External CLKIN Frequency <sup>(1)</sup> | DC   | _    | 0.5  | MHz   | External Clock (ECL) |  |  |  |

|               |      |                                         | DC   | —    | 4    | MHz   | External Clock (ECM) |  |  |  |

|               |      |                                         | DC   | —    | 20   | MHz   | External Clock (ECH) |  |  |  |

| OS02          | Tosc | External CLKIN Period <sup>(1)</sup>    | 50   | _    | ×    | ns    | External Clock (EC)  |  |  |  |

| OS03          | Тсү  | Instruction Cycle Time <sup>(1)</sup>   | 200  | Тсү  | DC   | ns    | Tcy = 4/Fosc         |  |  |  |

Standard Operating Conditions (unless otherwise stated)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

# PIC12(L)F1571/2

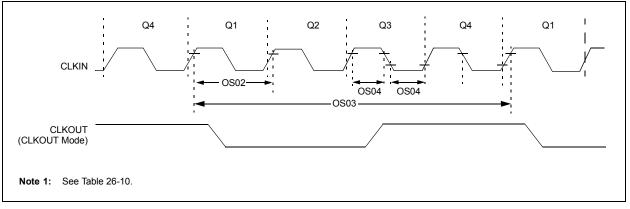

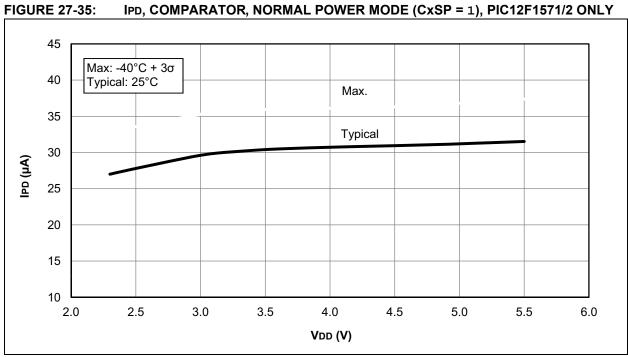

FIGURE 27-21: IPD BASE, LOW-POWER SLEEP MODE, PIC12LF1571/2 ONLY

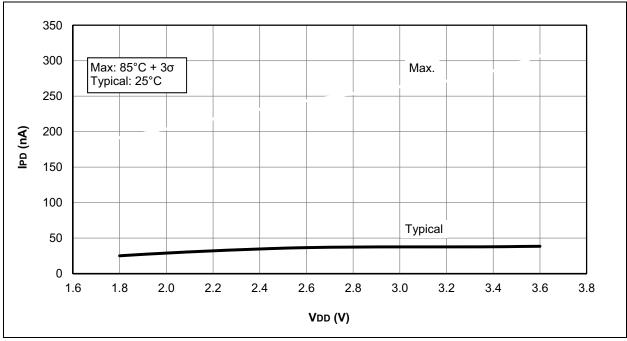

FIGURE 27-22: IPD BASE, LOW-POWER SLEEP MODE, PIC12F1571/2 ONLY

## APPENDIX A: DATA SHEET REVISION HISTORY

## Revision A (10/2013)

Original release of this document.

## Revision B (2/2014)

Updated PIC12(L)F1571/2 Family Types table Program Memory Flash heading (*words* to *K words*).

## Revision C (8/2014)

Updated PWM chapter. Changed to Final data sheet. Updated IDD and IPD parameters in the Electrical Specification chapter. Added Characterization Graphs.

Added Section 1.1: Register and Bit Naming Conventions.

Updated Figures 5-3 and 15-5. Updated Tables 3-1, 3-7, and 3-10. Updated Section 15.2.5. Updated Equation 15-1.

## **Revision D (8/2015)**

Updated Clocking Structure, Memory, Low-Power Features, Family Types table and Pin Diagram Table on cover pages.

Added Sections 3.2: High-Endurance Flash and 5.4: Clock Switching Before Sleep. Added Table 29-2 and 8-pin UDFN packaging.

Updated Examples 3-2 and 15-1.

Updated Figures 8-1, 21-1, 22-8 through 22-13 and 23-1.

Updated Registers 7-5, 8-1, 22-6 and 23-3.

Updated Sections 8.2.2, 15.2.6, 16.0, 21.0, 21.4.2, 22.3.3, 23.9.1.2, 23.11.1, 26.1 and 29.1.

Updated Tables 1, 3-3, 3-4, 3-10, 5-1, 16-1, 17-3, 22-2, 23-2, 26-6, 26-8 and 29-1.

NOTES: