Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-VDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-DFN (3x3)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1571-i-mf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Power Control (PCON) Register** 6.13

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- RESET Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

#### 6.14 **Register Definitions: Power Control**

#### \_\_\_\_\_ DOON DOWED CONTROL DECISTED

| REGISTER 6-2: PCON: POWER CONTROL REGISTER |                                                                                                                                                                 |                                                  |                                      |                   |                  |                  |                 |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------|-------------------|------------------|------------------|-----------------|

| R/W/HS-0/q                                 | R/W/HS-0/q                                                                                                                                                      | U-0                                              | R/W/HC-1/q                           | R/W/HC-1/q        | R/W/HC-1/q       | R/W/HC-q/u       | R/W/HC-q/u      |

| STKOVF                                     | STKUNF                                                                                                                                                          |                                                  | RWDT                                 | RMCLR             | RI               | POR              | BOR             |

| bit 7                                      |                                                                                                                                                                 |                                                  |                                      |                   |                  |                  | bit 0           |

|                                            |                                                                                                                                                                 |                                                  |                                      |                   |                  |                  |                 |

| Legend:                                    |                                                                                                                                                                 |                                                  | e Clearable bit                      |                   | are Settable bit |                  |                 |

| R = Readable                               |                                                                                                                                                                 | W = Writable                                     |                                      |                   | mented bit, read |                  |                 |

| u = Bit is unch                            | nanged                                                                                                                                                          | x = Bit is unkr                                  | nown                                 | -n/n = Value a    | at POR and BO    | R/Value at all o | ther Resets     |

| '1' = Bit is set                           |                                                                                                                                                                 | '0' = Bit is clea                                | ared                                 | q = Value der     | pends on condit  | ion              |                 |

| bit 7                                      | 1 = A Stack                                                                                                                                                     | ack Overflow F<br>Overflow Rese<br>Overflow Rese | •                                    | ed or is cleared  | d by firmware    |                  |                 |

| bit 6                                      | <b>STKUNF:</b> Stack Underflow Reset Flag bit<br>1 = A Stack Underflow Reset occurred<br>0 = A Stack Underflow Reset has not occurred or is cleared by firmware |                                                  |                                      |                   |                  |                  |                 |

| bit 5                                      | Unimpleme                                                                                                                                                       | nted: Read as                                    | '0'                                  |                   |                  |                  |                 |

| bit 4                                      | RWDT: Wate                                                                                                                                                      | hdog Timer Re                                    | eset Flag bit                        |                   |                  |                  |                 |

|                                            |                                                                                                                                                                 |                                                  | et has not occur<br>et has occurred  |                   |                  |                  |                 |

| bit 3                                      | RMCLR: MC                                                                                                                                                       | LR Reset Flag                                    | bit                                  |                   |                  |                  |                 |

|                                            |                                                                                                                                                                 |                                                  | occurred or is s<br>urred (cleared b |                   |                  |                  |                 |

| bit 2                                      | RI: RESET IN                                                                                                                                                    | struction Flag                                   | bit                                  |                   |                  |                  |                 |

|                                            | 1 = A RESET instruction has not been executed or set by firmware<br>0 = A RESET instruction has been executed (cleared by hardware)                             |                                                  |                                      |                   |                  |                  |                 |

| bit 1                                      | POR: Power                                                                                                                                                      | -on Reset Stat                                   | us bit                               |                   |                  |                  |                 |

|                                            | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>               |                                                  |                                      |                   |                  |                  |                 |

| bit 0                                      | BOR: Brown                                                                                                                                                      | -out Reset Sta                                   | tus bit                              |                   |                  |                  |                 |

|                                            |                                                                                                                                                                 | n-out Reset oc<br>out Reset occur                | curred<br>red (must be set           | in software after | a Power-on Res   | set or Brown-ou  | t Reset occurs) |

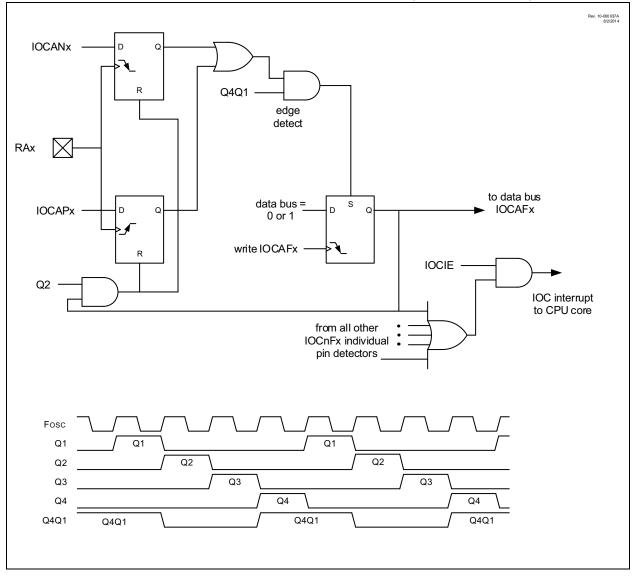

| TABLE 7-1: | SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS |

|------------|-------------------------------------------------|

|            |                                                 |

| Name       | Bit 7   | Bit 6  | Bit 5               | Bit 4               | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|---------|--------|---------------------|---------------------|-------|--------|---------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE              | INTE                | IOCIE | TMR0IF | INTF    | IOCIF  | 74                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS              | TMR0SE              | PSA   |        | PS<2:0> |        | 157                 |

| PIE1       | TMR1GIE | ADIE   | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | _     |        | TMR2IE  | TMR1IE | 75                  |

| PIE2       |         | —      | C1IE                | _                   | —     | —      | _       | _      | 76                  |

| PIE3       | _       | PWM3IE | PWM2IE              | PWM1IE              | —     | —      | _       | _      | 77                  |

| PIR1       | TMR1GIF | ADIF   | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | —     | _      | TMR2IF  | TMR1IF | 78                  |

| PIR2       | _       | _      | C1IF                | _                   | _     | _      | _       | _      | 79                  |

| PIR3       | —       | PWM3IF | PWM2IF              | PWM1IF              |       | _      | _       | _      | 80                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

Note 1: PIC12(L)F1572 only.

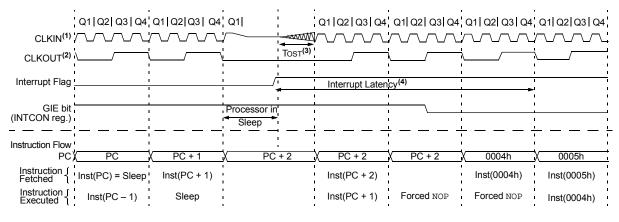

Note 1: External Clock. High, Medium, Low mode assumed.

2: CLKOUT is shown here for timing reference.

3: Tost = 1024 Tosc. This delay does not apply to EC, RC and INTOSC Oscillator modes or Two-Speed Start-up (if available).

4: GIE = 1 assumed. In this case, after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

# 8.2 Low-Power Sleep Mode

This device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

Low-Power Sleep mode allows the user to optimize the operating current in Sleep. Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register, which puts the LDO and reference circuitry in a low-power state whenever the device is in Sleep.

# 8.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

# 8.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The LDO will remain in the normal power mode when those peripherals are enabled. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- External interrupt pin/Interrupt-On-Change pins

- Timer1 (with external clock source)

The Complementary Waveform Generator (CWG) module can utilize the HFINTOSC oscillator as either a clock source or as an input source. Under certain conditions, when the HFINTOSC is selected for use with the CWG module, the HFINTOSC will remain active during Sleep. This will have a direct effect on the Sleep mode current.

Please refer to section **Section 23.10 "Operation During Sleep"** for more information.

Note: The PIC12LF1571/2 does not have a configurable Low-Power Sleep mode. PIC12LF1571/2 is an unregulated device and is always in the lowest power state when in Sleep with no wake-up time penalty. This device has a lower maximum VDD and I/O voltage than the PIC12F1571/2. See Section 26.0 "Electrical Specifications" for more information.

NOTES:

# PIC12(L)F1571/2

## REGISTER 15-4: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADRE    | S<9:2>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     |                |                  |                |              |

| u = Bit is uncha | anged   | x = Bit is unkn   | iown    | U = Unimpler   | nented bit, read | d as '0'       |              |

| '1' = Bit is set |         | '0' = Bit is clea | ared    | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result.

### **REGISTER 15-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | S<1:0>  | —       | —       | —       | —       | _       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-6 **ADRES<1:0>**: ADC Result Register bits Lower two bits of 10-bit conversion result.

bit 5-0 **Reserved**: Do not use

NOTES:

# 18.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-Bit Timer/Counter register (TMR0)

- 3-bit prescaler (independent of Watchdog Timer)

- Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 18-1 is a block diagram of the Timer0 module.

# 18.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 18.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle if used without a prescaler. The 8-Bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted in order to account for the two instruction cycle delay when TMR0 is written.

# FIGURE 18-1: TIMER0 BLOCK DIAGRAM

#### Rev. 10-000017A 8/5/2013 TMR0CS Fosc/4 PSA T0CKI<sup>(1)</sup> T0\_overflow 0 T0CKI 1 TMR0 Sync Circuit Prescaler 1 0 Fosc/2 Q1 write R to TMR0 TMR0SE set bit PS<2:0> TMR0IF Note 1: The T0CKI prescale output frequency should not exceed Fosc/8.

### 18.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the TOCKI pin.

In 8-Bit Counter mode, the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

# PIC12(L)F1571/2

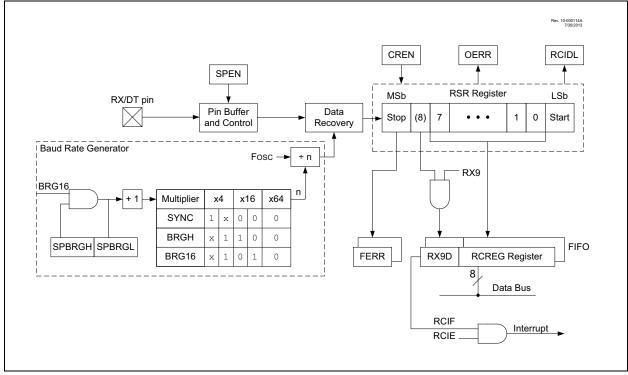

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 21-1, Register 21-2 and Register 21-3, respectively.

When the receiver or transmitter section is not enabled, then the corresponding RX or TX pin may be used for general purpose input and output.

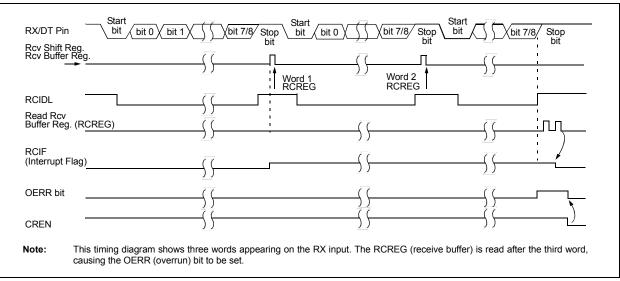

### 21.1.2.8 Asynchronous Reception Setup

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 21.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSELx bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register, and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 21.1.2.9 9-Bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH/SPBRGL register pair, and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 21.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSELx bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register, and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- 8. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

# FIGURE 21-5: ASYNCHRONOUS RECEPTION

## TABLE 21-3: BAUD RATE FORMULAS

| C    | Configuration Bits |      |                     | Baud Rate Formula |  |

|------|--------------------|------|---------------------|-------------------|--|

| SYNC | BRG16              | BRGH | BRG/EUSART Mode     | Baud Kale Formula |  |

| 0    | 0                  | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |  |

| 0    | 0                  | 1    | 8-bit/Asynchronous  |                   |  |

| 0    | 1                  | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |  |

| 0    | 1                  | 1    | 16-bit/Asynchronous |                   |  |

| 1    | 0                  | х    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |  |

| 1    | 1                  | х    | 16-bit/Synchronous  |                   |  |

**Legend:** x = Don't care; n = value of SPBRGH/SPBRGL register pair.

# TABLE 21-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|-----------|----------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUDCON | ABDOVF    | RCIDL    | _     | SCKP  | BRG16 |       | WUE   | ABDEN | 186                 |

| RCSTA   | SPEN      | RX9      | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 185                 |

| SPBRGL  |           | BRG<7:0> |       |       |       |       |       | 187*  |                     |

| SPBRGH  | BRG<15:8> |          |       |       |       |       | 187*  |       |                     |

| TXSTA   | CSRC      | TX9      | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 184                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

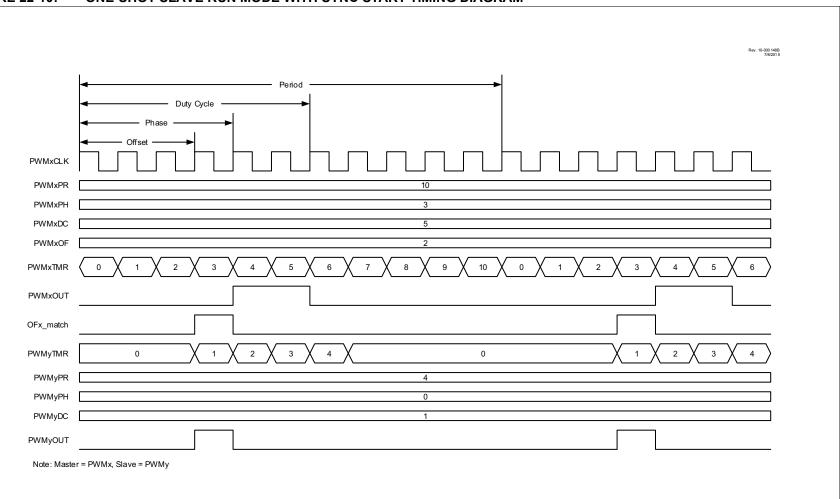

FIGURE 22-10: ONE-SHOT SLAVE RUN MODE WITH SYNC START TIMING DIAGRAM

PIC12(L)F1571/2

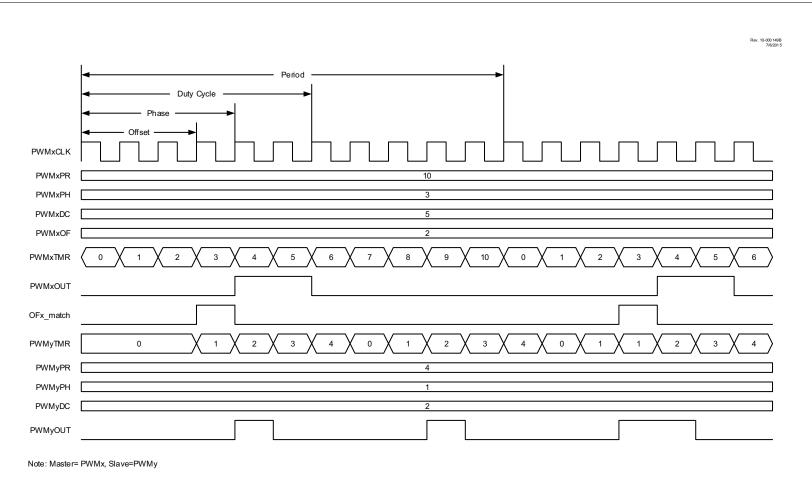

# FIGURE 22-11: CONTINUOUS SLAVE RUN MODE WITH IMMEDIATE RESET AND SYNC START TIMING DIAGRAM

# 23.10 Operation During Sleep

The CWG module operates independently from the system clock, and will continue to run during Sleep provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep, provided that the CWG module is enabled, the input source is active and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, the CPU will go idle during Sleep, but the CWG will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

# 23.11 Configuring the CWG

The following steps illustrate how to properly configure the CWG to ensure a synchronous start:

- Ensure that the TRISx control bits corresponding to CWGxA and CWGxB are set so that both are configured as inputs.

- 2. Clear the GxEN bit if not already cleared.

- 3. Set desired dead-band times with the CWGxDBR and CWGxDBF registers.

- 4. Set up the following controls in the CWGxCON2 auto-shutdown register:

- · Select desired shutdown source.

- Select both output overrides to the desired levels (this is necessary even if not using auto-shutdown because start-up will be from a shutdown state).

- Set the GxASE bit and clear the GxARSEN bit.

- 5. Select the desired input source using the CWGxCON1 register.

- 6. Configure the following controls in the CWGxCON0 register:

- · Select desired clock source.

- · Select the desired output polarities.

- Set the output enables for the outputs to be used.

- 7. Set the GxEN bit.

- Clear the TRISx control bits corresponding to CWGxA and CWGxB to be used to configure those pins as outputs.

- If auto-restart is to be used, set the GxARSEN bit and the GxASE bit will be cleared automatically. Otherwise, clear the GxASE bit to start the CWG.

#### 23.11.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the GxASDLA and GxASDLB bits of the CWGxCON1 register (Register 23-3). GxASDLA controls the CWG1A override level and GxASDLB controls the CWG1B override level. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not apply to the override level.

### 23.11.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the GxARSEN bit of the CWGxCON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 23-5 and Figure 23-6.

#### 23.11.2.1 Software Controlled Restart

When the GxARSEN bit of the CWGxCON2 register is cleared, the CWG must be restarted after an auto-shutdown event by software.

Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise, the GxASE bit will remain set. The overrides will remain in effect until the first rising edge event after the GxASE bit is cleared. The CWG will then resume operation.

#### 23.11.2.2 Auto-Restart

When the GxARSEN bit of the CWGxCON2 register is set, the CWG will restart from the auto-shutdown state automatically.

The GxASE bit will clear automatically when all shutdown sources go low. The overrides will remain in effect until the first rising edge event after the GxASE bit is cleared. The CWG will then resume operation.

# FIGURE 25-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                |

|---------------------------------------------------------------------------------------|

| OPCODE d f(FILE #)                                                                    |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |

| Bit-oriented file register operations                                                 |

| OPCODE b (BIT #) f (FILE #)                                                           |

| b = 3-bit bit address<br>f = 7-bit file register address                              |

| Literal and control operations                                                        |

| General                                                                               |

| 13 8 7 0<br>OPCODE k (literal)                                                        |

|                                                                                       |

| k = 8-bit immediate value                                                             |

| CALL and GOTO instructions only                                                       |

| 13 11 10 0                                                                            |

| OPCODE k (literal)                                                                    |

| k = 11-bit immediate value                                                            |

| MOVL₽ instruction only<br>13 7 6 0                                                    |

| OPCODE k (literal)                                                                    |

| k = 7-bit immediate value                                                             |

|                                                                                       |

| MOVLB instruction only                                                                |

| 13 5 4 0<br>OPCODE k (literal)                                                        |

| k = 5-bit immediate value                                                             |

|                                                                                       |

| BRA instruction only<br>13 9 8 0                                                      |

| OPCODE k (literal)                                                                    |

| k = 9-bit immediate value                                                             |

|                                                                                       |

| FSR Offset instructions                                                               |

|                                                                                       |

| OPCODE n k (literal)                                                                  |

| n = appropriate FSR<br>k = 6-bit immediate value                                      |

| FSR Increment instructions     13   3   2   1   0                                     |

| OPCODE n m (mode)                                                                     |

| n = appropriate FSR<br>m = 2-bit mode value                                           |

| OPCODE only<br>13 0                                                                   |

| OPCODE                                                                                |

|                                                                                       |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                 |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                       |

| SUBLW            | Subtract W from literal                                                                                                               |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                              |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                   |  |  |  |

| Operation:       | $k - (W) \to (W)$                                                                                                                     |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                              |  |  |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the 8-bit literal<br>'k'. The result is placed in the W regis-<br>ter. |  |  |  |

|                  | C = 0 W > k                                                                                                                           |  |  |  |

|                  | $C = 1$ $W \le k$                                                                                                                     |  |  |  |

|                  | DC = 0 W<3:0> k<3:0>                                                                                                                  |  |  |  |

|                  | DC = 1 W<3:0> ≤ k<3:0>                                                                                                                |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                                    |

| Operands:        | None                                                                                                                                                                                                                                               |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                              |

| Status Affected: | TO, PD                                                                                                                                                                                                                                             |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is<br>cleared. Time-out Status bit, $\overline{\text{TO}}$ is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into Sleep mode<br>with the oscillator stopped. |

| SUBWF            | Subtract W from f                                                                                                                                                              |           |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| Syntax:          | [label]                                                                                                                                                                        | SUBWF f,d |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                             |           |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                          |           |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |           |  |  |  |

| Description:     | Subtract (2's complement method) W register from register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f. |           |  |  |  |

|                  | <b>C =</b> 0                                                                                                                                                                   | W > f     |  |  |  |

|                  | _                                                                                                                                                                              |           |  |  |  |

| $\mathbf{C} = 0$ | W > f               |

|------------------|---------------------|

| <b>C =</b> 1     | $W \leq f$          |

| DC = 0           | W<3:0> > f<3:0>     |

| DC = 1           | $W<3:0> \le f<3:0>$ |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                   |  |  |  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |  |  |  |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |

| Standard Operating Conditions (unless otherwise stated) |        |                                              |        |      |        |       |                                                                      |  |

|---------------------------------------------------------|--------|----------------------------------------------|--------|------|--------|-------|----------------------------------------------------------------------|--|

| Param.<br>No.                                           | Sym.   | Characteristic                               | Min.   | Тур† | Max.   | Units | Conditions                                                           |  |

| -                                                       |        | Program Memory<br>Programming Specifications |        |      |        |       |                                                                      |  |

| D110                                                    | VIHH   | Voltage on MCLR/VPP Pin                      | 8.0    | _    | 9.0    | V     | (Note 2)                                                             |  |

| D111                                                    | IDDP   | Supply Current during<br>Programming         | _      | _    | 10     | mA    |                                                                      |  |

| D112                                                    | VBE    | VDD for Bulk Erase                           | 2.7    | _    | VDDMAX | V     |                                                                      |  |

| D113                                                    | VPEW   | VDD for Write or Row Erase                   | VDDMIN | _    | VDDMAX | V     |                                                                      |  |

| D114                                                    | IPPPGM | Current on MCLR/VPP during<br>Erase/Write    | -      | 1.0  | —      | mA    |                                                                      |  |

| D115                                                    | IDDPGM | Current on VDD during<br>Erase/Write         | —      | 5.0  | —      | mA    |                                                                      |  |

|                                                         |        | Program Flash Memory                         |        |      |        |       |                                                                      |  |

| D121                                                    | Eр     | Cell Endurance                               | 10K    | —    | _      | E/W   | -40°C ≤ TA ≤ +85°C<br>(Note 1)                                       |  |

| D122                                                    | VPRW   | VDD for Read/Write                           | VDDMIN | _    | VDDMAX | V     |                                                                      |  |

| D123                                                    | Tiw    | Self-Timed Write Cycle Time                  | _      | 2    | 2.5    | ms    |                                                                      |  |

| D124                                                    | TRETD  | Characteristic Retention                     | -      | 40   | -      | Year  | Provided no other specifications are violated                        |  |

| D125                                                    | EHEFC  | High-Endurance Flash Cell                    | 100K   | —    | —      | E/W   | $0^{\circ}C \le TA \le +60^{\circ}C$ , lower byte last 128 addresses |  |

## TABLE 26-5: MEMORY PROGRAMMING SPECIFICATIONS

† Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Self-write and block erase.

**2**: Required only if single-supply programming is disabled.

# PIC12(L)F1571/2

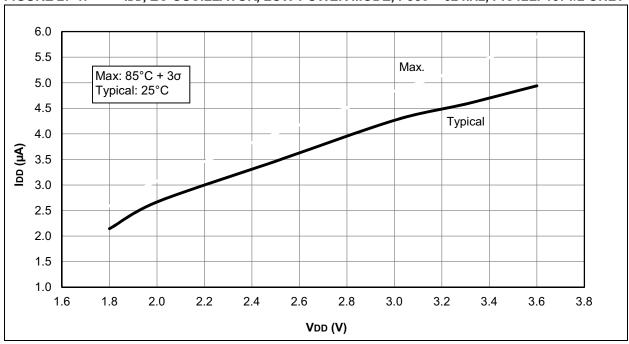

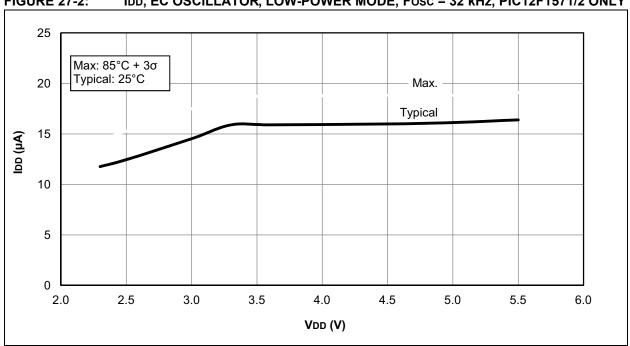

**FIGURE 27-1:** IDD, EC OSCILLATOR, LOW-POWER MODE, Fosc = 32 kHz, PIC12LF1571/2 ONLY

**FIGURE 27-2:** IDD, EC OSCILLATOR, LOW-POWER MODE, Fosc = 32 kHz, PIC12F1571/2 ONLY

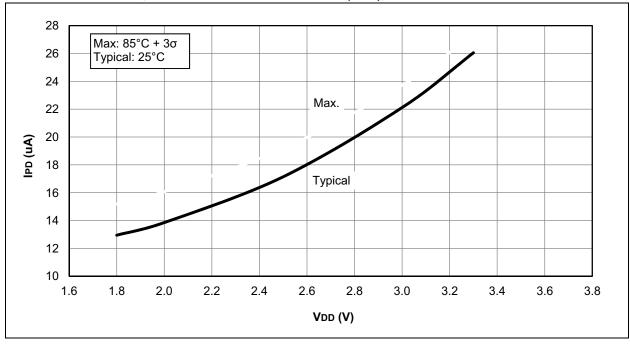

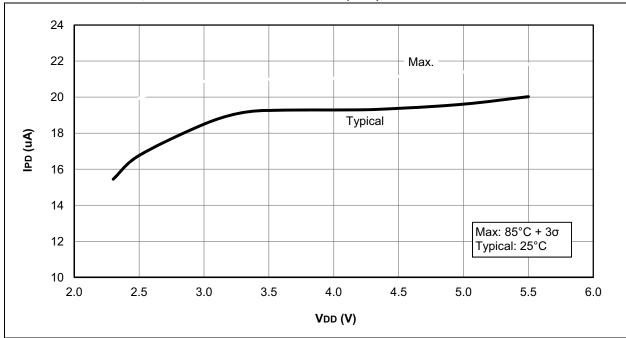

FIGURE 27-25: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC12LF1571/2 ONLY

FIGURE 27-26: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC12F1571/2 ONLY

# 28.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 28.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 28.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 28.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility