Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 6                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-VDFN Exposed Pad                                                          |

| Supplier Device Package    | 8-DFN (3x3)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1571t-i-mf |

# 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 Core Registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of Common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.6 "Indirect Addressing"** for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the bank address and the lower seven bits select the registers/RAM in that bank.

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses: x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-9.

TABLE 3-2: CORE REGISTERS

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| x0Bh or x8Bh | INTCON |

FIGURE 3-9: **INDIRECT ADDRESSING** 0x0000 0x0000 Traditional **Data Memory** 0x0FFF 0x0FFF 0x1000 Reserved 0x1FFF 0x2000 Linear **Data Memory** 0x29AF 0x29B0 Reserved 0x7FFF **FSR** 0x8000 0x0000 Address Range **Program** Flash Memory 0x7FFF 0xFFFF Not all memory regions are completely implemented. Consult device memory tables for memory limits. Note:

# 6.3 Register Definitions: BOR Control

#### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u              | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|----------------------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS <sup>(1)</sup> | _   | _   | _   | _   | _   | BORRDY |

| bit 7   |                      |     |     |     |     |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7 SBOREN: Software Brown-out Reset Enable bit

If BOREN<1:0> in Configuration Words = 01:

1 = BOR is enabled0 = BOR is disabled

If BOREN <1:0> in Configuration Words ≠ 01:

SBOREN is read/write, but has no effect on the BOR.

bit 6 **BORFS:** Brown-out Reset Fast Start bit<sup>(1)</sup>

If BOREN <1:0> = 10 (Disabled in Sleep) or BOREN<1:0> = 01 (Under software control):

1 = Band gap is forced on always (covers Sleep/wake-up/operating cases)

0 = Band gap operates normally and may turn off

If BOREN<1:0> = 11 (Always On) or BOREN<1:0> = 00 (Always Off):

BORFS is read/write, but has no effect on the BOR.

bit 5-1 **Unimplemented:** Read as '0'

bit 0 BORRDY: Brown-out Reset Circuit Ready Status bit

1 = The Brown-out Reset circuit is active0 = The Brown-out Reset circuit is inactive

**Note 1:** BOREN<1:0> bits are located in the Configuration Words.

# 6.4 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) operates like the BOR to detect low-voltage conditions on the VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The BOR bit in PCON is used for both BOR and the LPBOR. Refer to Register 6-2.

The LPBOR Voltage Threshold (VLPBOR) has a wider tolerance than the BOR (VBOR), but requires much less current (LPBOR current) to operate. The LPBOR is intended for use when the BOR is configured as disabled (BOREN<1:0> = 00) or disabled in Sleep mode (BOREN<1:0> = 10).

Refer to Figure 6-1 to see how the LPBOR interacts with other modules.

#### 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of the Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

# 6.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE and LVP bits of the Configuration Words (Table 6-2).

TABLE 6-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| х     | 1   | Enabled  |

#### 6.5.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

| Note: | A Reset does not drive the $\overline{\text{MCLR}}$ pin low. |

|-------|--------------------------------------------------------------|

|       |                                                              |

### 6.5.2 MCLR DISABLED

When  $\overline{MCLR}$  is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 11.3 "PORTA Registers"** for more information.

# 6.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register are changed to indicate the WDT Reset. See Section 9.0 "Watchdog Timer (WDT)" for more information.

#### 6.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{\text{RI}}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

#### 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack overflows or underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in the Configuration Words. See **Section 3.5.2 "Overflow/Underflow Reset"** for more information.

# 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

### 6.10 Power-up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overline{\text{PWRTE}}$  bit of the Configuration Words.

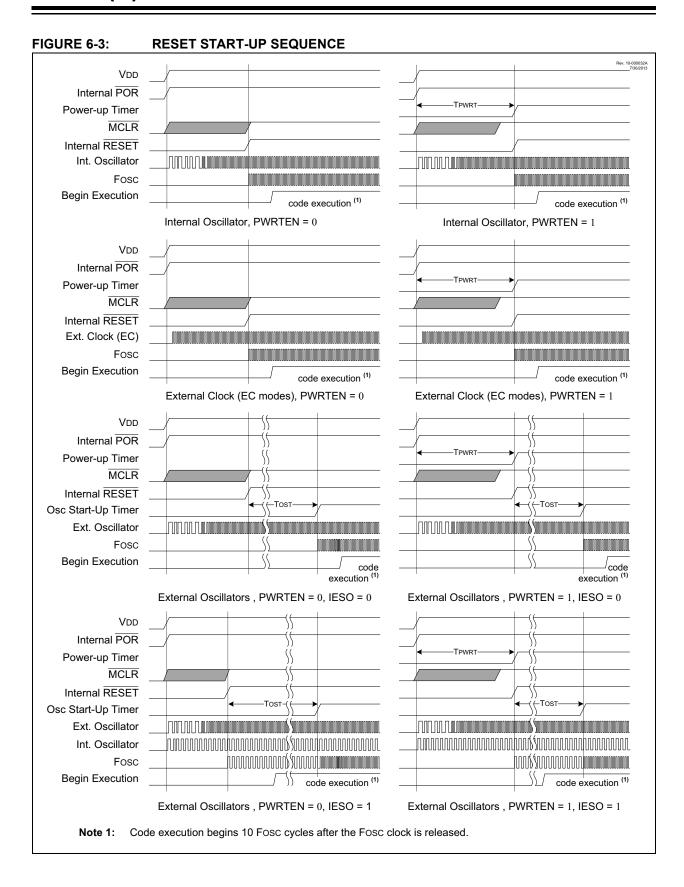

#### 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See Section 5.0 "Oscillator Module" for more information.

The Power-up Timer runs independently of a MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 Fosc cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

# 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                          |

|--------|--------|------|-------|----|-----|-----|----|----|------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                     |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | х  | Illegal, TO is Set on POR          |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | х  | 0  | Illegal, PD is Set on POR          |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                    |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                          |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep             |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep       |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during Normal Operation |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep            |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed         |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)  |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1) |

TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu 0uuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu 0uuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 1uuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | 1u uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | u1 uuuu          |

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

# 6.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- RESET Instruction Reset (RI)

- MCLR Reset (RMCLR)

bit 7

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

# 6.14 Register Definitions: Power Control

### **REGISTER 6-2: PCON: POWER CONTROL REGISTER**

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |            |            |            |            | bit 0      |

| Legend:              | HC = Hardware Clearable bit | HS = Hardware Settable bit                            |

|----------------------|-----------------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit            | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown          | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared        | q = Value depends on condition                        |

|       | <ul><li>1 = A Stack Overflow Reset occurred</li><li>0 = A Stack Overflow Reset has not occurred or is cleared by firmware</li></ul>   |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | STKUNF: Stack Underflow Reset Flag bit                                                                                                |

|       | <ul><li>1 = A Stack Underflow Reset occurred</li><li>0 = A Stack Underflow Reset has not occurred or is cleared by firmware</li></ul> |

| bit 5 | Unimplemented: Read as '0'                                                                                                            |

bit 4 RWDT: Watchdog Timer Reset Flag bit

STKOVF: Stack Overflow Reset Flag bit

1 = A Watchdog Timer Reset has not occurred or is set by firmware0 = A Watchdog Timer Reset has occurred (cleared by hardware)

bit 3 RMCLR: MCLR Reset Flag bit

1 = A  $\overline{MCLR}$  Reset has not occurred or is set by firmware 0 = A  $\overline{MCLR}$  Reset has occurred (cleared by hardware)

bit 2 RI: RESET Instruction Flag bit

1 = A RESET instruction has not been executed or set by firmware 0 = A RESET instruction has been executed (cleared by hardware)

bit 1 **POR:** Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOR: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurs)

# 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 8.0 "Power-Down Mode (Sleep)"** for more details.

### 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

# 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- · W register

- STATUS register (except for TO and PD)

- BSR register

- · FSR registers

- · PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

| <b>PIC12(I</b> | L)F1571/2 |

|----------------|-----------|

|----------------|-----------|

NOTES:

### 11.3 PORTA Registers

#### 11.3.1 DATA REGISTER

PORTA is a 6-bit wide, bidirectional port. The corresponding Data Direction register is TRISA (Register 11-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input-only and its TRISA bit will always read as '1'. Example 11-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 11-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are Read-Modify-Write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the Port Data Latch (LATA).

#### 11.3.2 DIRECTION CONTROL

The TRISA register (Register 11-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.3.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-7) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.3.4 SLEW RATE CONTROL

The SLRCONA register (Register 11-8) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, the corresponding port pin drive slews at the maximum rate possible.

#### 11.3.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 11-9) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an Interrupt-On-Change occurs, if that feature is enabled. See **Section 26.3 "DC Characteristics"** for more information on threshold levels.

Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 11.3.6 ANALOG CONTROL

Note:

The ANSELA register (Register 11-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSELA set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing Read-Modify-Write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSELA bits must be initialized to '0' by user software.

#### **EXAMPLE 11-1: INITIALIZING PORTA**

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

|         | FORTA       |                        |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | digital I/0            |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

#### 15.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set, and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

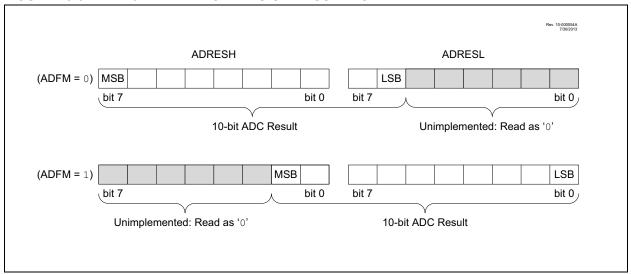

#### 15.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 15-3 shows the two output formats.

#### FIGURE 15-3: 10-BIT ADC CONVERSION RESULT FORMAT

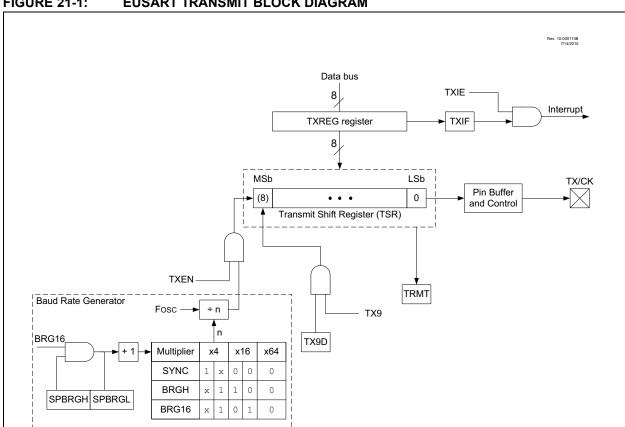

# **ENHANCED UNIVERSAL** 21.0 **SYNCHRONOUS ASYNCHRONOUS RECEIVER** TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer, independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- Full-duplex asynchronous transmit and receive

- Two-character input buffer

- · One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- · Half-duplex synchronous master

- · Half-duplex synchronous slave

- · Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- · 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 21-1 and Figure 21-2.

**FIGURE 21-1: EUSART TRANSMIT BLOCK DIAGRAM**

### REGISTER 22-9: PWMxDCH: PWMx DUTY CYCLE COUNT HIGH REGISTER

| R/W-x/u     | R/W-x/u  | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------------|----------|---------|---------|---------|---------|---------|---------|

|             | DC<15:8> |         |         |         |         |         |         |

| bit 7 bit 0 |          |         |         |         |         |         |         |

Legend:

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7-0 DC<15:8>: PWMx Duty Cycle High bits

Upper eight bits of PWM duty cycle count.

#### REGISTER 22-10: PWMxDCL: PWMx DUTY CYCLE COUNT LOW REGISTER

| R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------------|---------|---------|---------|---------|---------|---------|---------|

|             | DC<7:0> |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         |         |

Legend:

R = Readable bit W = Writable bit

u = Bit is unchanged x = Bit is unknown U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n/n = Value at POR and BOR/Value at all other Resets

bit 7-0 **DC<7:0>**: PWMx Duty Cycle Low bits

Lower eight bits of PWM duty cycle count.

# 23.8 Dead-Band Uncertainty

When the rising and falling edges of the input source triggers the dead-band counters, the input may be asynchronous. This will create some uncertainty in the dead-band time delay. The maximum uncertainty is equal to one CWG clock period. Refer to Equation 23-1 for more detail.

# EQUATION 23-1: DEAD-BAND UNCERTAINTY

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

Example:

$$Fcwg\_clock = 16 MHz$$

Therefore:

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

$$=\frac{1}{16 \, \text{MHz}}$$

$$= 62.5 ns$$

#### 23.9 Auto-Shutdown Control

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software.

#### 23.9.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- · Software generated

- · External Input

#### 23.9.1.1 Software Generated Shutdown

Setting the GxASE bit of the CWGxCON2 register will force the CWG into the shutdown state.

When auto-restart is disabled, the shutdown state will persist as long as the GxASE bit is set.

When auto-restart is enabled, the GxASE bit will clear automatically and resume operation on the next rising edge event. See Figure 23-6.

#### 23.9.1.2 External Input Source

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Any combination of two input sources can be selected to cause a shutdown condition. The sources are:

- Comparator C1 C1OUT\_async

- CWG1FLT

Shutdown inputs are selected in the CWGxCON2 register (Register 23-3).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

TABLE 26-4: I/O PORTS

Standard Operating Conditions (unless otherwise stated)

| Param.<br>No. | Sym. | Characteristic                       | Min.            | Тур† | Max.     | Units | Conditions                                                                 |  |  |

|---------------|------|--------------------------------------|-----------------|------|----------|-------|----------------------------------------------------------------------------|--|--|

|               | VIL  | Input Low Voltage                    |                 |      |          |       |                                                                            |  |  |

|               |      | I/O Ports:                           |                 |      |          |       |                                                                            |  |  |

| D030          |      | with TTL Buffer                      | _               | _    | 0.8      | V     | $4.5V \leq V_{DD} \leq 5.5V$                                               |  |  |

| D030A         |      |                                      | _               | _    | 0.15 VDD | V     | $1.8V \le VDD \le 4.5V$                                                    |  |  |

| D031          |      | with Schmitt Trigger Buffer          | _               | _    | 0.2 VDD  | V     | $2.0V \leq V_{DD} \leq 5.5V$                                               |  |  |

|               |      | with I <sup>2</sup> C Levels         | _               | _    | 0.3 VDD  | V     |                                                                            |  |  |

|               |      | with SMbus Levels                    | _               | _    | 0.8      | V     | $2.7V \leq V_{DD} \leq 5.5V$                                               |  |  |

| D032          |      | MCLR                                 | _               | _    | 0.2 VDD  | V     |                                                                            |  |  |

|               | VIH  | Input High Voltage                   |                 |      |          |       |                                                                            |  |  |

|               |      | I/O Ports:                           |                 |      |          |       |                                                                            |  |  |

| D040          |      | with TTL Buffer                      | 2.0             | _    | _        | V     | $4.5V \leq V_{DD} \leq 5.5V$                                               |  |  |

| D040A         |      |                                      | 0.25 VDD + 0.8  | _    | _        | V     | $1.8V \le V_{DD} \le 4.5V$                                                 |  |  |

| D041          |      | with Schmitt Trigger Buffer          | 0.8 VDD         | _    | _        | V     | $2.0V \leq V \text{DD} \leq 5.5V$                                          |  |  |

|               |      | with I <sup>2</sup> C Levels         | 0.7 VDD         | _    | _        | V     |                                                                            |  |  |

|               |      | with SMbus Levels                    | 2.1             | _    | _        | V     | $2.7V \leq V_{DD} \leq 5.5V$                                               |  |  |

| D042          |      | MCLR                                 | 0.8 VDD         | _    | _        | V     |                                                                            |  |  |

|               | lı∟  | Input Leakage Current <sup>(1)</sup> |                 |      |          |       |                                                                            |  |  |

| D060          |      | I/O Ports                            | _               | ± 5  | ± 125    | nA    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance, +85°C                          |  |  |

|               |      |                                      | _               | ± 5  | ± 1000   | nA    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance, +125°C                         |  |  |

| D061          |      | MCLR <sup>(2)</sup>                  | _               | ± 50 | ± 200    | nA    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance, +85°C                          |  |  |

|               | IPUR | Weak Pull-up Current                 |                 |      |          |       |                                                                            |  |  |

| D070*         |      |                                      | 25              | 100  | 200      | μΑ    | VDD = 3.3V, VPIN = VSS                                                     |  |  |

|               |      |                                      | 25              | 140  | 300      | μΑ    | VDD = 5.0V, VPIN = VSS                                                     |  |  |

|               | VOL  | Output Low Voltage                   |                 |      |          |       |                                                                            |  |  |

| D080          |      | I/O Ports                            | _               | _    | 0.6      | ٧     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |  |

|               | Vон  | Output High Voltage                  |                 |      |          |       |                                                                            |  |  |

| D090          |      | I/O Ports                            | VDD - 0.7       | _    | _        | V     | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8V |  |  |

|               |      | Capacitive Loading Specificat        | tions on Output | Pins | 1        | I.    | ı                                                                          |  |  |

| D101A*        | CIO  | All I/O Pins                         | _               | _    | 50       | pF    |                                                                            |  |  |

|               |      | •                                    |                 |      |          |       | •                                                                          |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Negative current is defined as current sourced by the pin.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

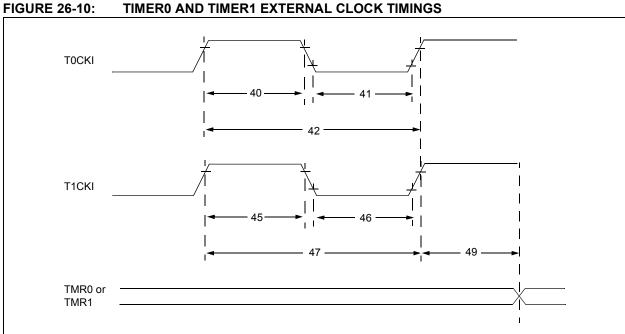

TABLE 26-12: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                    |                                                       |                                           |                                    |      |        |                    |                     |

|---------------|---------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|-------------------------------------------|------------------------------------|------|--------|--------------------|---------------------|

| Param.<br>No. | Sym.                                                    |                                                    | Characteristic                                        |                                           | Min.                               | Тур† | Max.   | Units              | Conditions          |

| 40*           | Тт0Н                                                    | T0CKI High Pulse Width No Prescaler With Prescaler |                                                       | No Prescaler                              | 0.5 Tcy + 20                       | _    | _      | ns                 |                     |

|               |                                                         |                                                    |                                                       | 10                                        | _                                  | _    | ns     |                    |                     |

| 41*           | TT0L                                                    | 0L T0CKI Low Pu                                    |                                                       | Pulse Width No Prescaler                  |                                    | _    | _      | ns                 |                     |

|               |                                                         |                                                    |                                                       | With Prescaler                            | 10                                 | _    | _      | ns                 |                     |

| 42*           | Тт0Р                                                    | T0CKI Period                                       | ·                                                     |                                           | Greater of:<br>20 or TCY + 40<br>N | _    | _      | ns                 | N = Prescale value  |

| 45* TT1H      | T⊤1H                                                    | T1CKI High                                         | Synchronous, No Prescaler Synchronous, with Prescaler |                                           | 0.5 Tcy + 20                       | _    | _      | ns                 |                     |

|               |                                                         | Time                                               |                                                       |                                           | 15                                 | _    | _      | ns                 |                     |

|               |                                                         |                                                    | Asynchronous                                          |                                           | 30                                 | _    | _      | ns                 |                     |

| 46*           | T⊤1L                                                    | T1CKI Low                                          | Synchronous, No Prescaler                             |                                           | 0.5 Tcy + 20                       | _    | _      | ns                 |                     |

|               |                                                         | Time                                               | Synchronous, with Prescaler                           |                                           | 15                                 | 1    |        | ns                 |                     |

|               |                                                         |                                                    | Asynchronous                                          |                                           | 30                                 | 1    |        | ns                 |                     |

| 47*           | Тт1Р                                                    | T1CKI Input Synchronous Period                     |                                                       | Greater of:<br>30 or <u>TCY + 40</u><br>N |                                    | _    | ns     | N = Prescale value |                     |

|               |                                                         |                                                    | Asynchronous                                          |                                           | 60                                 | _    | _      | ns                 |                     |

| 49*           | TCKEZTMR1                                               | Delay from E<br>Increment                          | kternal Clock Edge to Timer                           |                                           | 2 Tosc                             | _    | 7 Tosc | _                  | Timers in Sync mode |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### **TABLE 26-14: ADC CONVERSION REQUIREMENTS**

| Standard Operating Conditions (unless otherwise stated) |      |                                                                 |      |                           |      |       |                                               |

|---------------------------------------------------------|------|-----------------------------------------------------------------|------|---------------------------|------|-------|-----------------------------------------------|

| Param.<br>No.                                           | Sym. | Characteristic                                                  | Min. | Typ†                      | Max. | Units | Conditions                                    |

| AD130*                                                  | TAD  | ADC Clock Period (TADC)                                         | 1.0  | _                         | 6.0  | μS    | Fosc-based                                    |

|                                                         |      | ADC Internal FRC Oscillator Period (TFRC)                       | 1.0  | 2.0                       | 6.0  | μS    | ADCS<2:0> = $x11$ (ADC FRC mode)              |

| AD131                                                   | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _    | 11                        | _    | TAD   | Set GO/DONE bit to conversion complete        |

| AD132*                                                  | TACQ | Acquisition Time                                                | _    | 5.0                       | _    | μS    |                                               |

| AD133*                                                  | THCD | Holding Capacitor Disconnect Time                               | _    | 1/2 TAD<br>1/2 TAD + 1TCY | _    |       | Fosc-based,<br>ADCS<2:0> = x11 (ADC FRC mode) |

These parameters are characterized but not tested.

Note 1: The ADRES register may be read on the following TcY cycle.

<sup>†</sup> Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

TABLE 29-1: 8-LEAD 3x3x0.9 DFN (MF) TOP MARKING

| Part Number      | Marking       |

|------------------|---------------|

| PIC12F1571-E/MF  | MFY0/YYWW/NNN |

| PIC12F1572-E/MF  | MGA0/YYWW/NNN |

| PIC12F1571-I/MF  | MFZ0          |

| PIC12F1572-I/MF  | MGB0          |

| PIC12LF1571-E/MF | MGC0          |

| PIC12LF1572-E/MF | MGE0          |

| PIC12LF1571-I/MF | MGD0          |

| PIC12LF1572-I/MF | MGF0          |

TABLE 29-2: 8-LEAD 3x3x0.5 UDFN (RF) TOP MARKING

| Part Number      | Marking       |

|------------------|---------------|

| PIC12F1571-E/MF  | MFY0/YYWW/NNN |

| PIC12F1572-E/MF  | MGA0/YYWW/NNN |

| PIC12F1571-I/MF  | MFZ0          |

| PIC12F1572-I/MF  | MGB0          |

| PIC12LF1571-E/MF | MGC0          |

| PIC12LF1572-E/MF | MGE0          |

| PIC12LF1571-I/MF | MGD0          |

| PIC12LF1572-I/MF | MGF0          |