Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 6                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                               |

| Supplier Device Package    | 8-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1571t-i-sn |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

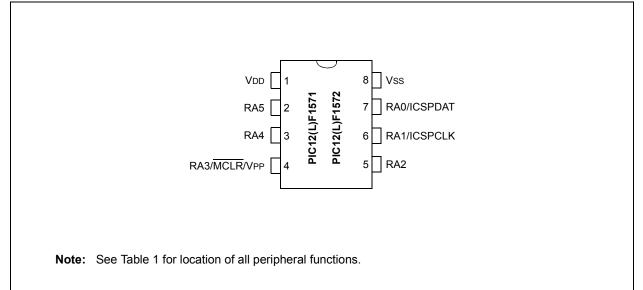

## **PIN DIAGRAMS**

Pin Diagram – 8-Pin PDIP, SOIC, DFN, MSOP, UDFN

| r   | -                             |     | i         |            | · · ·              | • • •               | ,                                          |                      | -          |         |                   |

|-----|-------------------------------|-----|-----------|------------|--------------------|---------------------|--------------------------------------------|----------------------|------------|---------|-------------------|

| 0/  | 8-Pin PDIP/SOIC/MSOP/DFN/UDFN | ADC | Reference | Comparator | Timers             | MWd                 | EUSART <sup>(2)</sup>                      | CWG                  | Interrupt  | Bull-up | Basic             |

| RA0 | 7                             | AN0 | DAC1OUT   | C1IN+      |                    | PWM2                | TX <sup>(2)</sup><br>CK <sup>(2)</sup>     | CWG1B                | IOC        | Y       | ICSPDAT<br>ICDDAT |

| RA1 | 6                             | AN1 | VREF+     | C1IN0-     |                    | PWM1                | RX <sup>(2)</sup><br>DT <sup>(2)</sup>     |                      | IOC        | Y       | ICSPCLK<br>ICDCLK |

| RA2 | 5                             | AN2 | —         | C10UT      | TOCKI              | PWM3                | _                                          | CWG1FLT<br>CWG1A     | IOC<br>INT | Y       | _                 |

| RA3 | 4                             | -   | _         | _          | T1G <sup>(1)</sup> | -                   | _                                          | _                    | IOC        | Y       | MCLR<br>VPP       |

| RA4 | 3                             | AN3 | —         | C1IN1-     | T1G                | PWM2 <sup>(1)</sup> | TX <sup>(1,2)</sup><br>CK <sup>(1,2)</sup> | CWG1B <sup>(1)</sup> | IOC        | Y       | CLKOUT            |

| RA5 | 2                             | —   | —         | —          | T1CKI              | PWM1 <sup>(1)</sup> | RX <sup>(1,2)</sup><br>DT <sup>(1,2)</sup> | CWG1A <sup>(1)</sup> | IOC        | Y       | CLKIN             |

| Vdd | 1                             | _   | _         | _          | _                  | _                   | _                                          | _                    |            | _       | Vdd               |

| Vss | 8                             | _   | —         | —          | —                  | —                   | _                                          |                      | _          | _       | Vss               |

| TABLE 1: | 8-PIN ALLOCATION TABLE (PIC12(L)F1571/2) |  |

|----------|------------------------------------------|--|

|          |                                          |  |

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

2: PIC12(L)F1572 only.

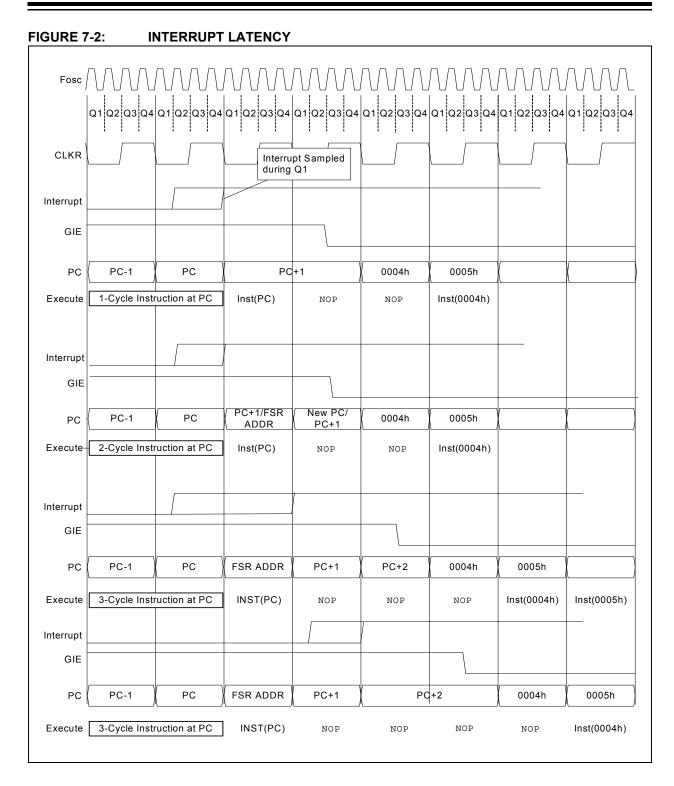

## 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

## 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory, 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a Software Reset. See **Section 3.5 "Stack"** for more details.

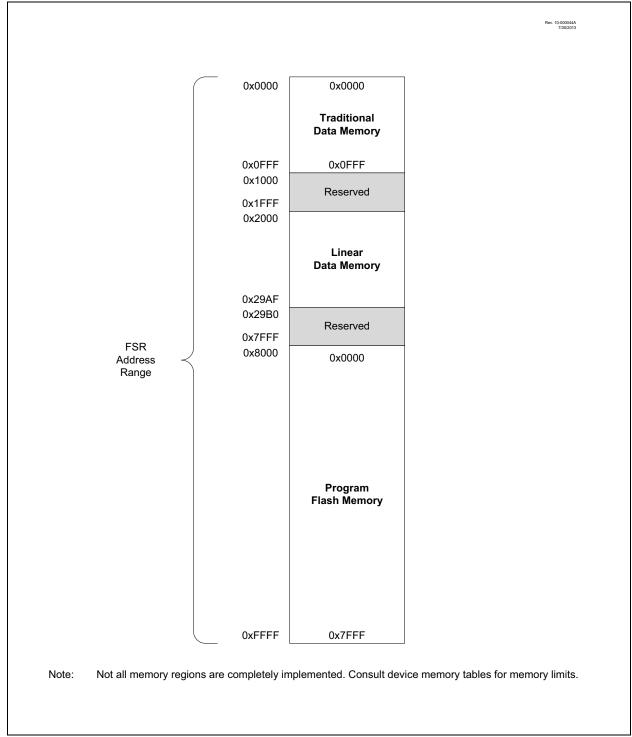

## 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

## 2.4 Instruction Set

There are 49 instructions for the enhanced midrange CPU to support the features of the CPU. See **Section 25.0 "Instruction Set Summary"** for more details.

## TABLE 3-6: PIC12(L)F1571/2 MEMORY MAP, BANK 24-31

|      | BANK 24                       |      | BANK 25                       |      | BANK 26                       |      | BANK 27                               |      | BANK 28                       |      | BANK 29                       |      | BANK 30                       |      | BANK 31                               |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|---------------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|---------------------------------------|

| C00h | Core Registers<br>(Table 3-2) | C80h | Core Registers<br>(Table 3-2) | D00h | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2)         | E00h | Core Registers<br>(Table 3-2) | E80h | Core Registers<br>(Table 3-2) | F00h | Core Registers<br>(Table 3-2) | F80h | Core Registers<br>(Table 3-2)         |

| C0Bh | ( /                           | C8Bh | ( ,                           | D0Bh | ( /                           | D8Bh | ( /                                   | E0Bh | ( /                           | E8Bh | ( /                           | F0Bh | ( /                           | F8Bh | ( /                                   |

| C0Ch | _                             | C8Ch | _                             | D0Ch | _                             | D8Ch |                                       | E0Ch | —                             | E8Ch | —                             | F0Ch | —                             | F8Ch |                                       |

| C0Dh | _                             | C8Dh | _                             | D0Dh | _                             |      |                                       | E0Dh | —                             | E8Dh | —                             | F0Dh | —                             |      |                                       |

| C0Eh | _                             | C8Eh | _                             | D0Eh | _                             |      |                                       | E0Eh | _                             | E8Eh | _                             | F0Eh | _                             |      |                                       |

| C0Fh |                               | C8Fh | _                             | D0Fh | _                             |      |                                       | E0Fh |                               | E8Fh |                               | F0Fh |                               |      |                                       |

| C10h | _                             | C90h | _                             | D10h | _                             |      |                                       | E10h | —                             | E90h | —                             | F10h | —                             |      |                                       |

| C11h | _                             | C91h | _                             | D11h | _                             |      |                                       | E11h | —                             | E91h | —                             | F11h | —                             |      |                                       |

| C12h | _                             | C92h | _                             | D12h | _                             |      |                                       | E12h | —                             | E92h | —                             | F12h | —                             |      |                                       |

| C13h | _                             | C93h | _                             | D13h | _                             |      |                                       | E13h | —                             | E93h | —                             | F13h | —                             |      |                                       |

| C14h | _                             | C94h | _                             | D14h | —                             |      |                                       | E14h | _                             | E94h |                               | F14h | _                             |      |                                       |

| C15h | -                             | C95h | -                             | D15h |                               |      |                                       | E15h | —                             | E95h | —                             | F15h | —                             |      |                                       |

| C16h | _                             | C96h | _                             | D16h | _                             |      |                                       | E16h | —                             | E96h | —                             | F16h | —                             |      |                                       |

| C17h | _                             | C97h | _                             | D17h | —                             |      | 0                                     | E17h | _                             | E97h |                               | F17h | _                             |      | 0                                     |

| C18h |                               | C98h | _                             | D18h | _                             |      | See Table 3-7 for<br>Register Mapping | E18h |                               | E98h |                               | F18h |                               |      | See Table 3-7 for<br>Register Mapping |

| C19h | _                             | C99h | _                             | D19h | _                             |      | Details                               | E19h | —                             | E99h | —                             | F19h | —                             |      | Details                               |

| C1Ah | _                             | C9Ah | _                             | D1Ah | —                             |      |                                       | E1Ah | _                             | E9Ah |                               | F1Ah | _                             |      |                                       |

| C1Bh | -                             | C9Bh | -                             | D1Bh |                               |      |                                       | E1Bh | —                             | E9Bh | —                             | F1Bh | —                             |      |                                       |

| C1Ch | _                             | C9Ch | _                             | D1Ch | _                             |      |                                       | E1Ch | —                             | E9Ch | —                             | F1Ch | —                             |      |                                       |

| C1Dh | _                             | C9Dh | _                             | D1Dh | —                             |      |                                       | E1Dh | _                             | E9Dh |                               | F1Dh | _                             |      |                                       |

| C1Eh |                               | C9Eh | _                             | D1Eh | _                             |      |                                       | E1Eh |                               | E9Eh |                               | F1Eh |                               |      |                                       |

| C1Fh | _                             | C9Fh | _                             | D1Fh | _                             |      |                                       | E1Fh | —                             | E9Fh | —                             | F1Fh | —                             |      |                                       |

| C20h |                               | CA0h |                               | D20h |                               |      |                                       | E20h |                               | EA0h |                               | F20h |                               |      |                                       |

|      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      |                                       |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      |                                       |

| C6Fh |                               | CEFh |                               | D6Fh |                               | DEFh |                                       | E6Fh |                               | EEFh |                               | F6Fh |                               | FEFh |                                       |

| C70h |                               | CF0h |                               | D70h |                               | DF0h |                                       | E70h |                               | EF0h |                               | F70h |                               | FF0h |                                       |

|      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh                   |      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh                   |

| CFFh |                               | CFFh |                               | D7Fh |                               | DFFh |                                       | E7Fh |                               | EFFh |                               | F7Fh |                               | FFFh |                                       |

Legend: 🔲 = Unimplemented data memory locations, read as '0'.

# PIC12(L)F1571/2

## 5.2.2.7 32 MHz Internal Oscillator Frequency Selection

The internal oscillator block can be used with the 4x PLL associated with the external oscillator block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSCx bits in the Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<1:0> = 00).

- The SCSx bits in the OSCCON register must be cleared to use the clock determined by FOSC<1:0> in the Configuration Words (SCS<1:0> = 00).

- The IRCFx bits in the OSCCON register must be set to the 8 MHz HFINTOSC to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4x PLL is not available for use with the internal oscillator when the SCSx bits of the OSCCON register are set to '1x'. The SCSx bits must be set to '00' to use the 4x PLL with the internal oscillator.

## 5.2.2.8 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-3). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-3 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables of **Section 26.0 "Electrical Specifications"**.

## 8.3 Register Definitions: Voltage Regulator Control

## **REGISTER 8-1:** VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1  |

|-------|-----|-----|-----|-----|-----|---------|----------|

| —     | —   | —   | —   | —   | —   | VREGPM  | Reserved |

| bit 7 |     |     |     |     |     |         | bit 0    |

|       |     |     |     |     |     |         |          |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

#### bit 7-2 Unimplemented: Read as '0'

bit 1

Unimplemented. Read as 0

VREGPM: Voltage Regulator Power Mode Selection bit

- 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup> Draws lowest current in Sleep, slower wake-up.

- 0 = Normal power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up.

bit 0 **Reserved:** Read as '1', maintain this bit set

**Note 1:** PIC12F1571/2 only.

2: See Section 26.0 "Electrical Specifications"

| Name   | Bit 7   | Bit 6  | Bit 5               | Bit 4               | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|--------|---------------------|---------------------|-----------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | TMR0IE              | INTE                | IOCIE     | TMR0IF | INTF   | IOCIF  | 74                  |

| IOCAF  | _       | _      | IOCAF5              | IOCAF4              | IOCAF3    | IOCAF2 | IOCAF1 | IOCAF0 | 122                 |

| IOCAN  | _       | —      | IOCAN5              | IOCAN4              | IOCAN3    | IOCAN2 | IOCAN1 | IOCAN0 | 121                 |

| IOCAP  | _       | _      | IOCAP5              | IOCAP4              | IOCAP3    | IOCAP2 | IOCAP1 | IOCAP0 | 121                 |

| PIE1   | TMR1GIE | ADIE   | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | _         | —      | TMR2IE | TMR1IE | 75                  |

| PIE2   | _       | _      | C1IE                | _                   | _         | —      | _      | _      | 76                  |

| PIE3   | _       | PWM3IE | PWM2IE              | PWM1IE              | _         | —      | _      | —      | 77                  |

| PIR1   | TMR1GIF | ADIF   | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | _         | —      | TMR2IF | TMR1IF | 78                  |

| PIR2   | —       | —      | C1IF                | —                   | —         | —      | —      | —      | 79                  |

| PIR3   | _       | PWM3IF | PWM2IF              | PWM1IF              | _         | —      | _      | —      | 80                  |

| STATUS |         |        |                     | TO                  | PD        | Z      | DC     | С      | 19                  |

| WDTCON |         | _      |                     | V                   | VDTPS<4:0 | >      |        | SWDTEN | 89                  |

## TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

**Note 1:** PIC12(L)F1572 only.

## 10.5 Write Verify

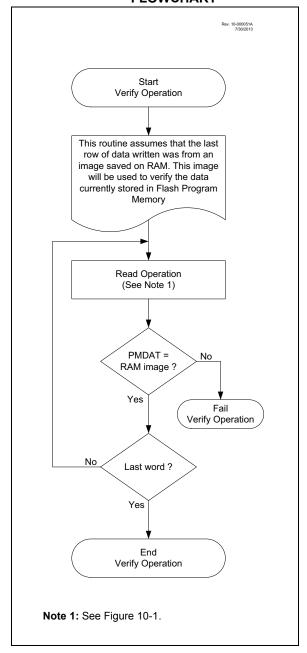

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 10-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

## 11.3 PORTA Registers

## 11.3.1 DATA REGISTER

PORTA is a 6-bit wide, bidirectional port. The corresponding Data Direction register is TRISA (Register 11-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input-only and its TRISA bit will always read as '1'. Example 11-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 11-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are Read-Modify-Write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the Port Data Latch (LATA).

#### 11.3.2 DIRECTION CONTROL

The TRISA register (Register 11-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

## 11.3.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-7) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

## 11.3.4 SLEW RATE CONTROL

The SLRCONA register (Register 11-8) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, the corresponding port pin drive slews at the maximum rate possible.

## 11.3.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 11-9) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an Interrupt-On-Change occurs, if that feature is enabled. See **Section 26.3 "DC Characteristics"** for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 11.3.6 ANALOG CONTROL

The ANSELA register (Register 11-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSELA set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing Read-Modify-Write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSELA bits must be initialized to '0' by user software.

#### EXAMPLE 11-1: INITIALIZING PORTA

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

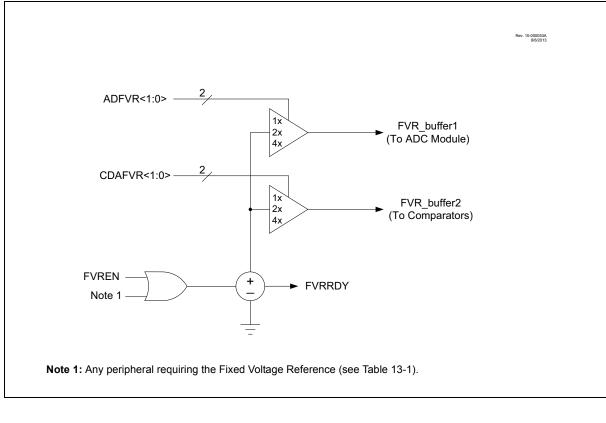

## 13.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference (FVR) is a stable voltage reference, independent of VDD, with a nominal output level (VFVR) of 1.024V. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- · Comparator positive input

- · Comparator negative input

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

## 13.1 Independent Gain Amplifier

The output of the FVR supplied to the peripherals, (listed above), is routed through a programmable gain amplifier. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 15.0 "Analog-to-Digital Converter (ADC) Module"** for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the comparator modules. Reference **Section 17.0 "Comparator Module"** for additional information.

To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clearing the Buffer Gain Selection bits.

## 13.2 FVR Stabilization Period

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See the FVR Stabilization Period characterization graph, Figure 27-21.

#### FIGURE 13-1: VOLTAGE REFERENCE BLOCK DIAGRAM

## 15.3 Register Definitions: ADC Control

| U-0            | R/W-0/0    | R/W-0/0                               | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0           | R/W-0/0      |

|----------------|------------|---------------------------------------|-----------------|------------------|------------------|-------------------|--------------|

| _              |            |                                       | CHS<4:0>        |                  |                  | GO/DONE           | ADON         |

| bit 7          |            |                                       |                 |                  |                  |                   | bit          |

|                |            |                                       |                 |                  |                  |                   |              |

| Legend:        |            |                                       |                 |                  |                  |                   |              |

| R = Readab     | ole bit    | W = Writable                          | bit             |                  |                  |                   |              |

| u = Bit is un  | changed    | x = Bit is unk                        | nown            | U = Unimpler     | mented bit, rea  | id as '0'         |              |

| '1' = Bit is s | et         | '0' = Bit is cle                      | ared            | -n/n = Value a   | at POR and BO    | OR/Value at all o | other Resets |

| bit 7          | Unimpleme  | ented: Read as                        | ʻ0'             |                  |                  |                   |              |

| bit 6-2        | CHS<4:0>:  | Analog Channe                         | I Select bits   |                  |                  |                   |              |

|                | 00000 = A  | NO                                    |                 |                  |                  |                   |              |

|                | 00001 = A  | N1                                    |                 |                  |                  |                   |              |

|                | 00010 = A  |                                       |                 |                  |                  |                   |              |

|                | 00011 = A  |                                       |                 | -1               |                  |                   |              |

|                | 00100 = R  | eserved; no cha                       | nnel connecte   | a                |                  |                   |              |

|                | •          |                                       |                 |                  |                  |                   |              |

|                | •          |                                       |                 |                  |                  |                   |              |

|                |            | eserved; no cha                       |                 | d                |                  |                   |              |

|                |            | mperature indic                       |                 |                  |                  |                   |              |

|                |            | AC (Digital-to-Ar                     |                 |                  | (3)              |                   |              |

|                |            | VR (Fixed Voltag                      |                 | Buffer 1 output  | (0)              |                   |              |

| bit 1          |            | ADC Conversio                         |                 |                  |                  |                   |              |

|                |            | onversion cycle i                     |                 | This h           | :4 :             |                   |              |

|                | •          | this bit starts an<br>C conversion ha |                 | on cycle. This b | it is automatica | any cleared by h  | ardware whe  |

|                |            | onversion compl                       |                 | aress            |                  |                   |              |

| bit 0          |            | C Enable bit                          | otournot in pro | 9.000            |                  |                   |              |

|                | 1 = ADC is |                                       |                 |                  |                  |                   |              |

|                |            | disabled and co                       | nsumes no op    | erating current  |                  |                   |              |

| Note 1.        |            |                                       |                 | -                | information      |                   |              |

|                |            | .0 "Temperature                       |                 |                  |                  | moro informatio   | n            |

|                |            | .0 "5-Bit Digital                     | -               | (EVD)" for mor   |                  |                   |              |

## REGISTER 15-1: ADCON0: ADC CONTROL REGISTER 0

3: See Section 13.0 "Fixed Voltage Reference (FVR)" for more information.

NOTES:

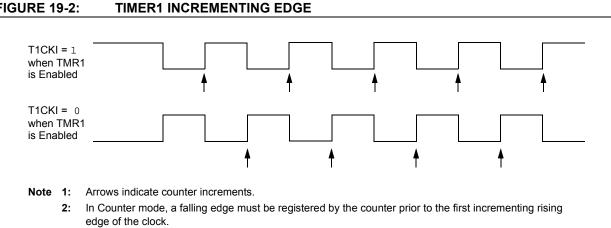

#### 19.6 **Timer1 Interrupt**

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- · PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

The TMR1H:TMR1L register pair and the Note: TMR1IF bit should be cleared before enabling interrupts.

#### 19.7 **Timer1 Operation During Sleep**

Timer1 can only operate during Sleep when set up in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- · TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- · TMR1CS bits of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the T1SYNC bit setting.

#### ALTERNATE PIN LOCATIONS 19.7.1

This module incorporates I/O pins that can be moved to other locations with the use of the Alternate Pin Function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see Section 11.1 "Alternate Pin Function" for more information.

## 22.2 PWM Modes

PWM modes are selected with the MODE<1:0> bits of the PWMxCON register (Register 22-1).

In all PWM modes, an offset match event can also be used to synchronize the PWMxTMR in three Offset modes. See **Section 22.3 "Offset Modes"** for more information.

## 22.2.1 STANDARD MODE

The Standard mode (MODE<1:0> = 00) selects a single-phase PWM output. The PWM output in this mode is determined by when the period, duty cycle and phase counts match the PWMxTMR value. The start of the duty cycle occurs on the phase match and the end of the duty cycle occurs on the duty cycle match. The period match resets the timer. The offset match can also be used to synchronize the PWMxTMR in the Offset modes. See Section 22.3 "Offset Modes" for more information.

Equation 22-1 is used to calculate the PWM period in Standard mode.

Equation 22-2 is used to calculate the PWM duty cycle ratio in Standard mode.

#### EQUATION 22-1: PWM PERIOD IN STANDARD MODE

$$Period = \frac{(PWMxPR + 1) \cdot Prescale}{PWMxCLK}$$

## EQUATION 22-2: PWM DUTY CYCLE IN STANDARD MODE

$$Duty \ Cycle = \frac{(PWMxDC - PWMxPH)}{PWMxPR + 1}$$

A detailed timing diagram for Standard mode is shown in Figure 22-4.

## 22.2.2 SET ON MATCH MODE

The Set On Match mode (MODE<1:0> = 01) generates an active output when the phase count matches the PWMxTMR value. The output stays active until the OUT bit of the PWMxCON register is cleared or the PWM module is disabled. The duty cycle count has no effect in this mode. The period count only determines the maximum PWMxTMR value above which no phase matches can occur. The OUT bit can be used to set or clear the output of the PWM in this mode. Writes to this bit will take place on the next rising edge of the PWM\_clock after the bit is written.

A detailed timing diagram for Set On Match mode is shown in Figure 22-5.

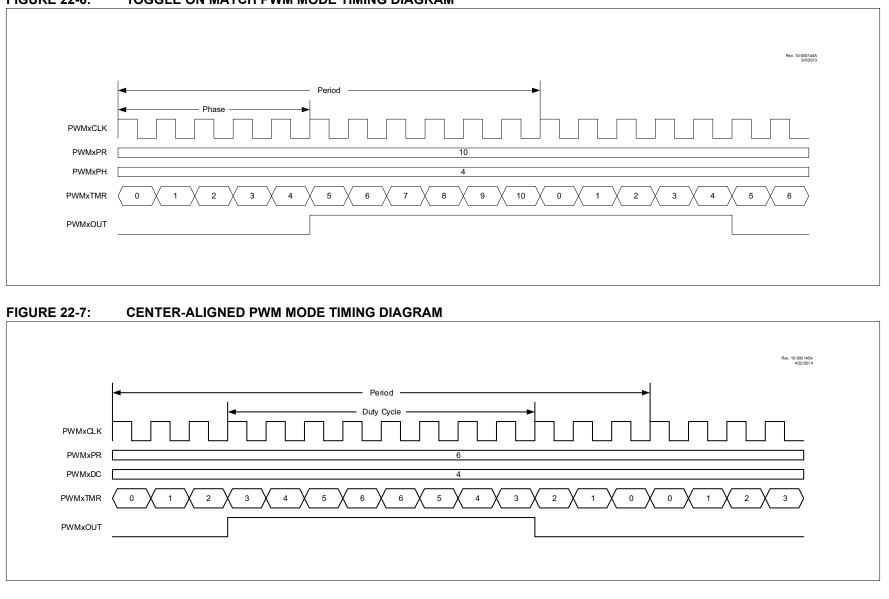

## 22.2.3 TOGGLE ON MATCH MODE

The Toggle On Match mode (MODE<1:0> = 10) generates a 50% duty cycle PWM with a period twice as long as that computed for the Standard PWM mode. Duty cycle count has no effect in this mode. The phase count determines how many PWMxTMR periods, after a period event, the output will toggle.

Writes to the OUT bit of the PWMxCON register will have no effect in this mode.

A detailed timing diagram for Toggle On Match mode is shown in Figure 22-6.

## 22.2.4 CENTER-ALIGNED MODE

The Center-Aligned mode (MODE = 11) generates a PWM waveform that is centered in the period. In this mode, the period is two times the PWMxPR count. The PWMxTMR counts up to the period value, then counts back down to 0. The duty cycle count determines both the start and end of the active PWM output. The start of the duty cycle occurs at the match event when PWMxTMR is incrementing and the duty cycle ends at the match event when PWMxTMR is decrementing. The incrementing match value is the period count minus the duty cycle count. The decrementing match value is the incrementing match value plus 1.

Equation 22-3 is used to calculate the PWM period in Center-Aligned mode.

## EQUATION 22-3: PWM PERIOD IN CENTER-ALIGNED MODE

$$Period = \frac{(PWMxPR + 1) \cdot Prescale \cdot 2}{PWMxCLK}$$

Equation 22-4 is used to calculate the PWM duty cycle ratio in Center-Aligned mode.

## EQUATION 22-4: PWM DUTY CYCLE IN CENTER-ALIGNED MODE

$$Duty Cycle = \frac{PWMxDC \cdot 2}{(PWMxPR + 1) \cdot 2}$$

Writes to the OUT bit will have no effect in this mode.

A detailed timing diagram for Center-Aligned mode is shown in Figure 22-7.

## FIGURE 22-6:

#### 5: TOGGLE ON MATCH PWM MODE TIMING DIAGRAM

PIC12(L)F1571/2

## REGISTER 22-6: PWMxOFCON: PWMx OFFSET TRIGGER SOURCE SELECT REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0            | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|--------------------|-----|-----|---------|---------|

| —     | OFM     | <1:0>   | OFO <sup>(1)</sup> | —   | —   | OFS     | <1:0>   |

| bit 7 |         |         |                    |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-5 | OFM<1:0>: Offset Mode Select bits                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Continuous Slave Run mode with immediate Reset and synchronized start when the selected offset trigger occurs</li> <li>10 = One-Shot Slave Run mode with synchronized start when the selected offset trigger occurs</li> <li>01 = Independent Slave Run mode with synchronized start when the selected offset trigger occurs</li> <li>00 = Independent Run mode</li> </ul> |

| bit 4   | OFO: Offset Match Output Control bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                      |

|         | If MODE<1:0> = 11 (PWM Center-Aligned mode):<br>1 = OFx_match occurs on counter match when counter decrementing, (second match)<br>0 = OFx_match occurs on counter match when counter incrementing, (first match)<br>If MODE<1:0> = 00, 01 or 10 (all other modes):<br>Bit is ignored.                                                                                                   |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                               |

| bit 1-0 | OFS<1:0>: Offset Trigger Source Select bits<br>11 = OF3_match <sup>(1)</sup><br>10 = OF2_match <sup>(1)</sup><br>01 = OF1_match <sup>(1)</sup><br>00 = Reserved                                                                                                                                                                                                                          |

**Note 1:** The OFx\_match corresponding to the PWM used becomes reserved.

# FIGURE 25-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                   |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| OPCODE d f(FILE #)                                                                       |  |  |  |  |  |  |  |  |

| d = 0  for destination W<br>d = 1  for destination f<br>f = 7-bit  file register address |  |  |  |  |  |  |  |  |

| Bit-oriented file register operations                                                    |  |  |  |  |  |  |  |  |

| OPCODE b (BIT #) f (FILE #)                                                              |  |  |  |  |  |  |  |  |

| b = 3-bit bit address<br>f = 7-bit file register address                                 |  |  |  |  |  |  |  |  |

| Literal and control operations                                                           |  |  |  |  |  |  |  |  |

| General                                                                                  |  |  |  |  |  |  |  |  |

| 13 8 7 0<br>OPCODE k (literal)                                                           |  |  |  |  |  |  |  |  |

|                                                                                          |  |  |  |  |  |  |  |  |

| k = 8-bit immediate value                                                                |  |  |  |  |  |  |  |  |

| CALL and GOTO instructions only                                                          |  |  |  |  |  |  |  |  |

| 13 11 10 0                                                                               |  |  |  |  |  |  |  |  |

| OPCODE k (literal)                                                                       |  |  |  |  |  |  |  |  |

| k = 11-bit immediate value                                                               |  |  |  |  |  |  |  |  |

| MOVL₽ instruction only<br>13 7 6 0                                                       |  |  |  |  |  |  |  |  |

| OPCODE k (literal)                                                                       |  |  |  |  |  |  |  |  |

| k = 7-bit immediate value                                                                |  |  |  |  |  |  |  |  |

|                                                                                          |  |  |  |  |  |  |  |  |

| MOVLB instruction only                                                                   |  |  |  |  |  |  |  |  |

| 13 5 4 0<br>OPCODE k (literal)                                                           |  |  |  |  |  |  |  |  |

| k = 5-bit immediate value                                                                |  |  |  |  |  |  |  |  |

|                                                                                          |  |  |  |  |  |  |  |  |

| BRA instruction only<br>13 9 8 0                                                         |  |  |  |  |  |  |  |  |

| OPCODE k (literal)                                                                       |  |  |  |  |  |  |  |  |

| k = 9-bit immediate value                                                                |  |  |  |  |  |  |  |  |

|                                                                                          |  |  |  |  |  |  |  |  |

| FSR Offset instructions                                                                  |  |  |  |  |  |  |  |  |

|                                                                                          |  |  |  |  |  |  |  |  |

| OPCODE n k (literal)                                                                     |  |  |  |  |  |  |  |  |

| n = appropriate FSR<br>k = 6-bit immediate value                                         |  |  |  |  |  |  |  |  |

| FSR Increment instructions     13   3   2   1   0                                        |  |  |  |  |  |  |  |  |

| OPCODE n m (mode)                                                                        |  |  |  |  |  |  |  |  |

| n = appropriate FSR<br>m = 2-bit mode value                                              |  |  |  |  |  |  |  |  |

| OPCODE only<br>13 0                                                                      |  |  |  |  |  |  |  |  |

| OPCODE                                                                                   |  |  |  |  |  |  |  |  |

|                                                                                          |  |  |  |  |  |  |  |  |

| Mnemonic,<br>Operands |      | Description                                   | Cycles | 14-Bit Opcode |      |      | Status | Notes    |       |

|-----------------------|------|-----------------------------------------------|--------|---------------|------|------|--------|----------|-------|

|                       |      |                                               |        | MSb           |      |      | LSb    | Affected | Notes |

|                       |      | CONTROL OPERA                                 | TIONS  |               |      |      |        |          |       |

| BRA                   | k    | Relative Branch                               | 2      | 11            | 001k | kkkk | kkkk   |          |       |

| BRW                   | -    | Relative Branch with W                        | 2      | 00            | 0000 | 0000 | 1011   |          |       |

| CALL                  | k    | Call Subroutine                               | 2      | 10            | 0kkk | kkkk | kkkk   |          |       |

| CALLW                 | -    | Call Subroutine with W                        | 2      | 00            | 0000 | 0000 | 1010   |          |       |

| GOTO                  | k    | Go to address                                 | 2      | 10            | 1kkk | kkkk | kkkk   |          |       |

| RETFIE                | k    | Return from interrupt                         | 2      | 00            | 0000 | 0000 | 1001   |          |       |

| RETLW                 | k    | Return with literal in W                      | 2      | 11            | 0100 | kkkk | kkkk   |          |       |

| RETURN                | -    | Return from Subroutine                        | 2      | 00            | 0000 | 0000 | 1000   |          |       |

|                       |      | INHERENT OPERA                                | ATIONS |               |      |      |        |          |       |

| CLRWDT                | _    | Clear Watchdog Timer                          | 1      | 00            | 0000 | 0110 | 0100   | TO, PD   |       |

| NOP                   | _    | No Operation                                  | 1      | 00            | 0000 | 0000 | 0000   |          |       |

| OPTION                | _    | Load OPTION_REG register with W               | 1      | 00            | 0000 | 0110 | 0010   |          |       |

| RESET                 | _    | Software device Reset                         | 1      | 00            | 0000 | 0000 | 0001   |          |       |

| SLEEP                 | -    | Go into Standby mode                          | 1      | 00            | 0000 | 0110 | 0011   | TO, PD   |       |

| TRIS                  | f    | Load TRIS register with W                     | 1      | 00            | 0000 | 0110 | Offf   |          |       |

|                       |      | C COMPILER OPT                                | IMIZED |               |      |      |        |          |       |

| ADDFSR                | n, k | Add Literal k to FSRn                         | 1      | 11            | 0001 | 0nkk | kkkk   |          |       |

| MOVIW                 | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00            | 0000 | 0001 | 0nmm   | Z        | 2, 3  |

|                       |      | modifier, mm                                  |        |               |      |      | kkkk   |          |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.            | 1      | 11            | 1111 | 0nkk | 1nmm   | Z        | 2     |

| MOVWI                 | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00            | 0000 | 0001 | kkkk   |          | 2, 3  |

|                       |      | modifier, mm                                  |        |               |      |      |        |          |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.            | 1      | 11            | 1111 | 1nkk |        |          | 2     |

## TABLE 25-3: ENHANCED MID-RANGE INSTRUCTION SET (CONTINUED)

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

3: See the table in the MOVIW and MOVWI instruction descriptions.

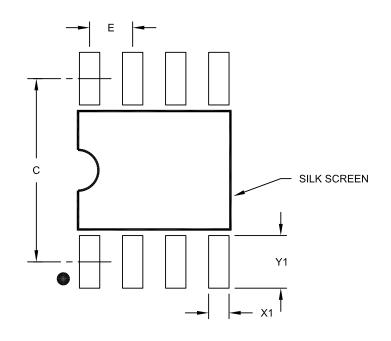

## 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | Units | MILLIMETERS |      |      |  |  |

|-------------------------|-------|-------------|------|------|--|--|

| Dimension               | MIN   | NOM         | MAX  |      |  |  |

| Contact Pitch           | E     | 1.27 BSC    |      |      |  |  |

| Contact Pad Spacing     | С     |             | 5.40 |      |  |  |

| Contact Pad Width (X8)  | X1    |             |      | 0.60 |  |  |

| Contact Pad Length (X8) | Y1    |             |      | 1.55 |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

## APPENDIX A: DATA SHEET REVISION HISTORY

## Revision A (10/2013)

Original release of this document.

## Revision B (2/2014)

Updated PIC12(L)F1571/2 Family Types table Program Memory Flash heading (*words* to *K words*).

## Revision C (8/2014)

Updated PWM chapter. Changed to Final data sheet. Updated IDD and IPD parameters in the Electrical Specification chapter. Added Characterization Graphs.

Added Section 1.1: Register and Bit Naming Conventions.

Updated Figures 5-3 and 15-5. Updated Tables 3-1, 3-7, and 3-10. Updated Section 15.2.5. Updated Equation 15-1.

## **Revision D (8/2015)**

Updated Clocking Structure, Memory, Low-Power Features, Family Types table and Pin Diagram Table on cover pages.

Added Sections 3.2: High-Endurance Flash and 5.4: Clock Switching Before Sleep. Added Table 29-2 and 8-pin UDFN packaging.

Updated Examples 3-2 and 15-1.

Updated Figures 8-1, 21-1, 22-8 through 22-13 and 23-1.

Updated Registers 7-5, 8-1, 22-6 and 23-3.

Updated Sections 8.2.2, 15.2.6, 16.0, 21.0, 21.4.2, 22.3.3, 23.9.1.2, 23.11.1, 26.1 and 29.1.

Updated Tables 1, 3-3, 3-4, 3-10, 5-1, 16-1, 17-3, 22-2, 23-2, 26-6, 26-8 and 29-1.