Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-UDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-UDFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1572-e-rf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral, thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C, the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

#### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

COG1CON0bits.MD = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name, MD2, and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

#### Example 1:

```

MOVLW ~(1<<G1MD1)

ANDWF COG1CON0,F

MOVLW 1<<G1MD2 | 1<<G1MD0

IORWF COG1CON0,F

```

#### Example 2:

| BSF | COG1CON0,G1MD2 |

|-----|----------------|

| BCF | COG1CON0,G1MD1 |

| BSF | COG1CON0,G1MD0 |

# 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

#### 1.1.3.1 Status, Interrupt and Mirror Bits

Status, interrupt enables, interrupt flags and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

## 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

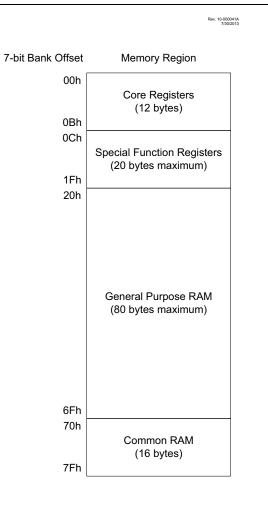

## 3.3.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses: x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.3.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses: x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.3.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2 "Linear Data Memory"** for more information.

#### 3.3.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### 3.3.5 DEVICE MEMORY MAPS

The memory maps for PIC12(L)F1571/2 are as shown in Table 3-3 through Table 3-8.

#### FIGURE 3-3: BANKED MEMORY PARTITIONING

## 5.0 OSCILLATOR MODULE

#### 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications, while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources

The oscillator module can be configured in one of the following clock modes:

- 1. ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. INTOSC Internal Oscillator (31 kHz to 32 MHz)

Clock Source modes are selected by the FOSC<1:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The ECH, ECM, and ECL Clock modes rely on an external logic level signal as the device clock source.

The INTOSC internal oscillator block produces low, medium and high-frequency clock sources, designated as LFINTOSC, MFINTOSC and HFINTOSC (see Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these three clock sources.

## 6.4 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) operates like the BOR to detect low-voltage conditions on the VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The BOR bit in PCON is used for both BOR and the LPBOR. Refer to Register 6-2.

The LPBOR Voltage Threshold (VLPBOR) has a wider tolerance than the BOR (VBOR), but requires much less current (LPBOR current) to operate. The LPBOR is intended for use when the BOR is configured as disabled (BOREN<1:0> = 00) or disabled in Sleep mode (BOREN<1:0> = 10).

Refer to Figure 6-1 to see how the LPBOR interacts with other modules.

## 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the  $\overline{LPBOR}$  bit of the Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

## 6.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE and LVP bits of the Configuration Words (Table 6-2).

## TABLE 6-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

## 6.5.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

## Note: A Reset does not drive the MCLR pin low.

## 6.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 11.3** "**PORTA Registers**" for more information.

## 6.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the WDT Reset. See **Section 9.0 "Watchdog Timer (WDT)"** for more information.

## 6.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

## 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack overflows or underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in the Configuration Words. See **Section 3.5.2 "Overflow/Underflow Reset"** for more information.

## 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

## 6.10 Power-up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\text{PWRTE}}$  bit of the Configuration Words.

## 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section 5.0 "Oscillator Module"** for more information.

The Power-up Timer runs independently of a MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 Fosc cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

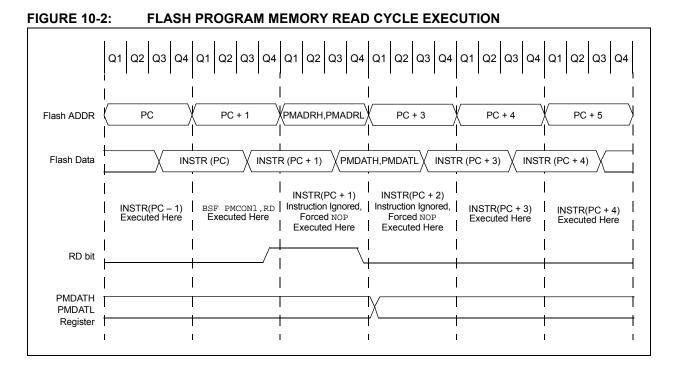

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

|      |          | block will read 1 |                                     |

|------|----------|-------------------|-------------------------------------|

| * me | -        | the memory addres |                                     |

|      | —        | R_HI : PROG_ADDR_ | •                                   |

|      |          | l be returned in  |                                     |

| *    | PROG_DAT | A_HI, PROG_DATA_L | 0                                   |

|      | BANKSEL  | PMADRL            | ; Select Bank for PMCON registers   |

|      | MOVLW    | PROG_ADDR_LO      | ;                                   |

|      | MOVWF    | PMADRL            | ; Store LSB of address              |

|      | MOVLW    | PROG_ADDR_HI      | ;                                   |

|      | MOVWF    | PMADRH            | ; Store MSB of address              |

|      | BCF      | PMCON1,CFGS       | ; Do not select Configuration Space |

|      | BSF      | PMCON1,RD         | ; Initiate read                     |

|      | NOP      |                   | ; Ignored (Figure 10-2)             |

|      | NOP      |                   | ; Ignored (Figure 10-2)             |

|      | MOVF     | PMDATL,W          | ; Get LSB of word                   |

|      | MOVWF    | PROG_DATA_LO      | ; Store in user location            |

|      | MOVF     | PMDATH,W          | ; Get MSB of word                   |

|      | MOVWF    | PROG_DATA_HI      | ; Store in user location            |

## 10.6 Register Definitions: Flash Program Memory Control

#### REGISTER 10-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | PMDA    | T<7:0>         |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     |                |                  |                  |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | nown    | U = Unimpler   | nented bit, read | l as '0'         |             |

| '1' = Bit is set |         | '0' = Bit is clea | ared    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

bit 7-0 PMDAT<7:0>: Read/Write Value for Least Significant bits of Program Memory bits

#### REGISTER 10-2: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|--|

| _     | —   |         | PMDAT<13:8> |         |         |         |         |  |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDAT<13:8>: Read/Write Value for Most Significant bits of Program Memory bits

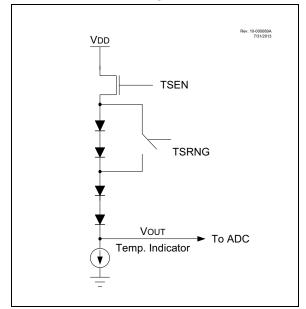

## 14.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS00001333) for more details regarding the calibration process.

## 14.1 Circuit Operation

Figure 14-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 14-1 describes the output characteristics of the temperature indicator.

## EQUATION 14-1: VOUT RANGES

High Range: VOUT = VDD - 4 VT

Low Range: VOUT = VDD - 2 VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 13.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low-voltage operation.

## FIGURE 14-1: TEMPERATURE CIRCUIT DIAGRAM

## 14.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 14-1 shows the recommended minimum  $\mathsf{V}\mathsf{D}\mathsf{D}$  vs. range setting.

#### TABLE 14-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |  |  |  |  |  |

|---------------------|---------------------|--|--|--|--|--|

| 3.6V                | 1.8V                |  |  |  |  |  |

## 14.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 15.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

## 14.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

| R/W-0/0          | R/W-0/0                                                                                          | R/W-0/0                                                                                                                                                        | R/W-0/0           | R/W-0/0         | R-0/0              | R-0/0            | R-0/0        |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|--------------------|------------------|--------------|--|--|--|--|

| SPEN             | RX9                                                                                              | SREN                                                                                                                                                           | CREN              | ADDEN           | FERR               | OERR             | RX9D         |  |  |  |  |

| bit 7            |                                                                                                  |                                                                                                                                                                |                   |                 |                    |                  | bit (        |  |  |  |  |

|                  |                                                                                                  |                                                                                                                                                                |                   |                 |                    |                  |              |  |  |  |  |

| Legend:          |                                                                                                  |                                                                                                                                                                |                   |                 |                    |                  |              |  |  |  |  |

| R = Readable     | e bit                                                                                            | W = Writable                                                                                                                                                   | bit               |                 |                    |                  |              |  |  |  |  |

| u = Bit is uncl  | hanged                                                                                           | x = Bit is unk                                                                                                                                                 | nown              | U = Unimpler    | nented bit, read   | as '0'           |              |  |  |  |  |

| '1' = Bit is set |                                                                                                  | '0' = Bit is cle                                                                                                                                               | ared              | -n/n = Value    | at POR and BO      | R/Value at all c | other Resets |  |  |  |  |

| bit 7            | SPEN: Seria                                                                                      | l Port Enable b                                                                                                                                                | ŧ                 |                 |                    |                  |              |  |  |  |  |

|                  |                                                                                                  |                                                                                                                                                                |                   | DT and TX/Ck    | C pins as serial p | ort pins)        |              |  |  |  |  |

|                  |                                                                                                  | ort is disabled (                                                                                                                                              |                   |                 |                    | sort pillo)      |              |  |  |  |  |

| bit 6            | <b>RX9:</b> 9-Bit R                                                                              | eceive Enable I                                                                                                                                                | oit               |                 |                    |                  |              |  |  |  |  |

|                  |                                                                                                  | 9-bit reception<br>8-bit reception                                                                                                                             |                   |                 |                    |                  |              |  |  |  |  |

| bit 5            | SREN: Single                                                                                     | e Receive Enal                                                                                                                                                 | ole bit           |                 |                    |                  |              |  |  |  |  |

|                  | Asynchronou<br>Don't care.                                                                       | is mode:                                                                                                                                                       |                   |                 |                    |                  |              |  |  |  |  |

|                  | Synchronous                                                                                      | s mode – Maste                                                                                                                                                 | <u>r:</u>         |                 |                    |                  |              |  |  |  |  |

|                  |                                                                                                  | single receive                                                                                                                                                 |                   |                 |                    |                  |              |  |  |  |  |

|                  |                                                                                                  | s single receive<br>ared after rece                                                                                                                            | ntion is compl    | ata             |                    |                  |              |  |  |  |  |

|                  |                                                                                                  | s mode – Slave                                                                                                                                                 |                   |                 |                    |                  |              |  |  |  |  |

|                  | Don't care.                                                                                      |                                                                                                                                                                | -                 |                 |                    |                  |              |  |  |  |  |

| bit 4            | CREN: Conti                                                                                      | inuous Receive                                                                                                                                                 | Enable bit        |                 |                    |                  |              |  |  |  |  |

|                  | Asynchronou                                                                                      |                                                                                                                                                                |                   |                 |                    |                  |              |  |  |  |  |

|                  | 1 = Enables<br>0 = Disables                                                                      |                                                                                                                                                                |                   |                 |                    |                  |              |  |  |  |  |

|                  | Synchronous                                                                                      |                                                                                                                                                                |                   |                 |                    |                  |              |  |  |  |  |

|                  |                                                                                                  |                                                                                                                                                                | eive until enal   | ole bit CREN is | cleared (CREN      | l overrides SR   | EN)          |  |  |  |  |

|                  |                                                                                                  | s continuous ree                                                                                                                                               |                   |                 | , ,                |                  | ,            |  |  |  |  |

| bit 3            | ADDEN: Add                                                                                       | dress Detect Er                                                                                                                                                | able bit          |                 |                    |                  |              |  |  |  |  |

|                  | Asynchronous mode 9-bit (RX9 = 1):                                                               |                                                                                                                                                                |                   |                 |                    |                  |              |  |  |  |  |

|                  | 1 = Enables address detection, enables interrupt and loads the receive buffer when RSR<8> is set |                                                                                                                                                                |                   |                 |                    |                  |              |  |  |  |  |

|                  |                                                                                                  | <ul> <li>0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit</li> <li>Asynchronous mode 8-bit (RX9 = 0):</li> </ul> |                   |                 |                    |                  |              |  |  |  |  |

|                  | Don't care.                                                                                      |                                                                                                                                                                | 0,0 = 0           |                 |                    |                  |              |  |  |  |  |

| bit 2            | FERR: Fram                                                                                       | ing Error bit                                                                                                                                                  |                   |                 |                    |                  |              |  |  |  |  |

|                  |                                                                                                  | -                                                                                                                                                              | pdated by rea     | ding RCREG      | register and rec   | eiving next vali | d byte)      |  |  |  |  |

|                  | 0 = No frami                                                                                     | ing error                                                                                                                                                      |                   |                 |                    |                  |              |  |  |  |  |

| bit 1            | OERR: Over                                                                                       |                                                                                                                                                                |                   |                 |                    |                  |              |  |  |  |  |

|                  | 1 = Overrun<br>0 = No overr                                                                      | error (can be c<br>run error                                                                                                                                   | leared by clea    | iring bit, CREN | 1)                 |                  |              |  |  |  |  |

| bit 0            | RX9D: Ninth                                                                                      | Bit of Received                                                                                                                                                | l Data bit        |                 |                    |                  |              |  |  |  |  |

|                  | This can be a                                                                                    | address/data bi                                                                                                                                                | t or a parity bit | and must be o   | calculated by us   | er firmware      |              |  |  |  |  |

## REGISTER 21-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

## 21.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in Transmit mode; otherwise, the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

## 21.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes is identical (see **Section 21.5.1.3 "Synchronous Master Transmission")**, except in the case of Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 21.5.2.2 Synchronous Slave Transmission Setup

- 1. Set the SYNC and SPEN bits, and clear the CSRC bit.

- 2. Clear the ANSELx bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

## TABLE 21-9: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name    | Bit 7                         | Bit 6 | Bit 5               | Bit 4               | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|-------|---------------------|---------------------|-------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL |                     | SCKP                | BRG16 | _      | WUE    | ABDEN  | 186                 |

| INTCON  | GIE                           | PEIE  | TMR0IE              | INTE                | IOCIE | TMR0IF | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE                       | ADIE  | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | _     | _      | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF                       | ADIF  | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | —     | —      | TMR2IF | TMR1IF | 78                  |

| RCSTA   | SPEN                          | RX9   | SREN                | CREN                | ADDEN | FERR   | OERR   | RX9D   | 185                 |

| TXREG   | EUSART Transmit Data Register |       |                     |                     |       |        |        |        |                     |

| TXSTA   | CSRC                          | TX9   | TXEN                | SYNC                | SENDB | BRGH   | TRMT   | TX9D   | 184                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave transmission. \* Page provides register information.

Note 1: PIC12(L)F1572 only.

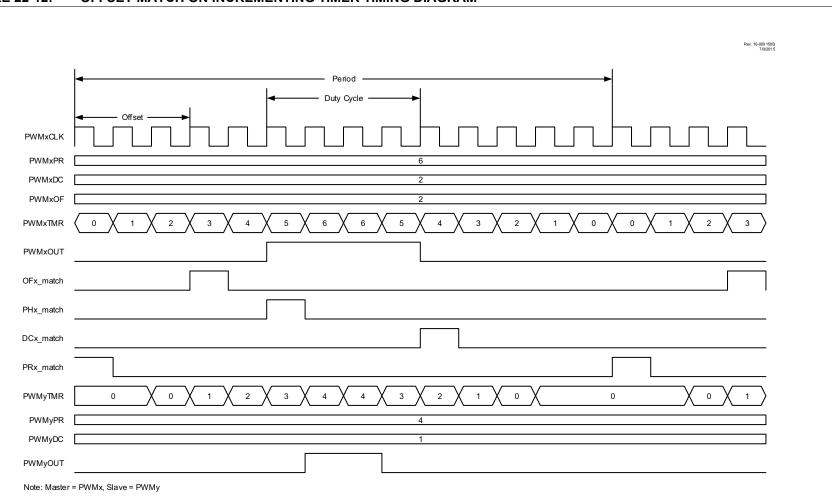

#### FIGURE 22-12: OFFSET MATCH ON INCREMENTING TIMER TIMING DIAGRAM

PIC12(L)F1571/2

| PIC12LF1571/2 |                        | Operating Conditions (unless otherwise stated)<br>Low-Power Sleep Mode |                                  |       |        |          |     |                                    |  |  |  |  |

|---------------|------------------------|------------------------------------------------------------------------|----------------------------------|-------|--------|----------|-----|------------------------------------|--|--|--|--|

| PIC12F157     | 71/2                   | Low-Po                                                                 | Low-Power Sleep Mode, VREGPM = 1 |       |        |          |     |                                    |  |  |  |  |

| Param.        | Device Changeteriotics | Min                                                                    | Truck                            | Max.  | Max.   | l lucito |     | Conditions                         |  |  |  |  |

| No.           | Device Characteristics | Min.                                                                   | Тур†                             | +85°C | +125°C | Units    | Vdd | Note                               |  |  |  |  |

| D027          |                        | —                                                                      | 4                                | 7     | 9      | μA       | 1.8 | Comparator,                        |  |  |  |  |

|               |                        | _                                                                      | 4.2                              | 8     | 10     | μA       | 3.0 | CxSP = 0                           |  |  |  |  |

| D027          |                        | _                                                                      | 13                               | 20    | 21     | μA       | 2.3 | Comparator,                        |  |  |  |  |

|               |                        | _                                                                      | 14                               | 23    | 25     | μA       | 3.0 | CxSP = 0                           |  |  |  |  |

|               |                        | —                                                                      | 16                               | 24    | 26     | μA       | 5.0 | ]                                  |  |  |  |  |

| D028A         |                        | —                                                                      | 20                               | 35    | 36     | μA       | 1.8 | Comparator,                        |  |  |  |  |

|               |                        | —                                                                      | 21                               | 36    | 38     | μA       | 3.0 | Normal Power, CxSP = 1<br>(Note 1) |  |  |  |  |

| D028A         |                        | _                                                                      | 28                               | 47    | 48     | μA       | 2.3 | Comparator,                        |  |  |  |  |

|               |                        | _                                                                      | 29                               | 51    | 52     | μA       | 3.0 | Normal Power, $CxSP = 1$ ,         |  |  |  |  |

|               |                        | _                                                                      | 31                               | 52    | 53     | μA       | 5.0 | VREGPM = 1 (Note 1)                |  |  |  |  |

#### POWER-DOWN CURRENTS (IPD)<sup>(1,2)</sup> (CONTINUED) **TABLE 26-3**:

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

Note 1: The peripheral  $\Delta$  current can be determined by subtracting the base IPD current from this limit. Max. values should be used when calculating total current consumption.

The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with 2: the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC clock source is FRC.

#### TABLE 26-4: I/O PORTS

| Standard      | d Operati | ing Conditions (unless otherwi       | se stated)                            |      |          |       |                                                                            |  |  |  |  |  |

|---------------|-----------|--------------------------------------|---------------------------------------|------|----------|-------|----------------------------------------------------------------------------|--|--|--|--|--|

| Param.<br>No. | Sym.      | Characteristic                       | Min.                                  | Тур† | Max.     | Units | Conditions                                                                 |  |  |  |  |  |

|               | VIL       | Input Low Voltage                    |                                       |      |          |       |                                                                            |  |  |  |  |  |

|               |           | I/O Ports:                           |                                       |      |          |       |                                                                            |  |  |  |  |  |

| D030          |           | with TTL Buffer                      | —                                     | _    | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |  |  |

| D030A         |           |                                      | —                                     | _    | 0.15 VDD | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |  |  |  |  |  |

| D031          |           | with Schmitt Trigger Buffer          | —                                     | —    | 0.2 Vdd  | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |  |  |

|               |           | with I <sup>2</sup> C Levels         | —                                     | —    | 0.3 VDD  | V     |                                                                            |  |  |  |  |  |

|               |           | with SMbus Levels                    | —                                     | _    | 0.8      | V     | $2.7V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |  |  |

| D032          |           | MCLR                                 | —                                     | —    | 0.2 Vdd  | V     |                                                                            |  |  |  |  |  |

|               | Viн       | Input High Voltage                   |                                       |      |          |       |                                                                            |  |  |  |  |  |

|               |           | I/O Ports:                           |                                       |      |          |       |                                                                            |  |  |  |  |  |

| D040          |           | with TTL Buffer                      | 2.0                                   | _    | _        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |  |  |

| D040A         |           |                                      | 0.25 VDD + 0.8                        | _    | _        | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |  |  |  |  |  |

| D041          |           | with Schmitt Trigger Buffer          | 0.8 VDD                               | —    | —        | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |  |  |

|               |           | with I <sup>2</sup> C Levels         | 0.7 VDD                               | —    | _        | V     |                                                                            |  |  |  |  |  |

|               |           | with SMbus Levels                    | 2.1                                   | —    | —        | V     | $2.7V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |  |  |

| D042          |           | MCLR                                 | 0.8 VDD                               | —    | —        | V     |                                                                            |  |  |  |  |  |

|               | lı∟       | Input Leakage Current <sup>(1)</sup> |                                       |      |          |       |                                                                            |  |  |  |  |  |

| D060          |           | I/O Ports                            | —                                     | ± 5  | ± 125    | nA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, +85°C                   |  |  |  |  |  |

|               |           |                                      | —                                     | ± 5  | ± 1000   | nA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-impedance, +125°C                  |  |  |  |  |  |

| D061          |           | MCLR <sup>(2)</sup>                  | —                                     | ± 50 | ± 200    | nA    | VSS $\leq$ VPIN $\leq$ VDD, Pin at high-impedance, +85°C                   |  |  |  |  |  |

|               | IPUR      | Weak Pull-up Current                 |                                       |      |          |       |                                                                            |  |  |  |  |  |

| D070*         |           |                                      | 25                                    | 100  | 200      | μA    | VDD = 3.3V, VPIN = VSS                                                     |  |  |  |  |  |

|               |           |                                      | 25                                    | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                     |  |  |  |  |  |

|               | Vol       | Output Low Voltage                   |                                       |      |          |       |                                                                            |  |  |  |  |  |

| D080          |           | I/O Ports                            | —                                     | —    | 0.6      | V     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |  |  |  |  |

|               | Voн       | Output High Voltage                  | · · · · · · · · · · · · · · · · · · · |      | ·        | •     |                                                                            |  |  |  |  |  |

| D090          | I/O Ports |                                      | Vdd - 0.7                             |      | _        | V     | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8V |  |  |  |  |  |

|               |           | Capacitive Loading Specifica         | tions on Output                       | Pins |          | -     | •                                                                          |  |  |  |  |  |

| D101A*        | CIO       | All I/O Pins                         | _                                     | _    | 50       | pF    |                                                                            |  |  |  |  |  |

|               |           |                                      |                                       |      |          | •     |                                                                            |  |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

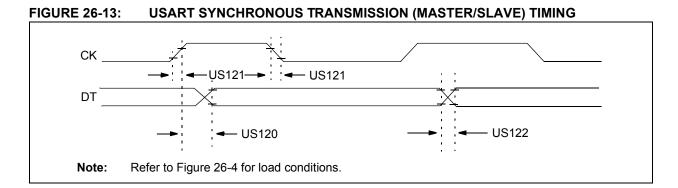

## TABLE 26-17: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |          |                                                              |      |      |       |                                  |

|---------------------------------------------------------|----------|--------------------------------------------------------------|------|------|-------|----------------------------------|

| Param.<br>No.                                           | Symbol   | Characteristic                                               | Min. | Max. | Units | Conditions                       |

| US120                                                   | TCKH2DTV | SYNC XMIT (Master and Slave)<br>Clock High to Data-Out Valid |      | 80   | ns    | $3.0V \le V\text{DD} \le 5.5V$   |

|                                                         |          |                                                              | _    | 100  | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| US121                                                   | TCKRF    | Clock Out Rise Time and Fall Time (Master mode)              | _    | 45   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |

|                                                         |          |                                                              | _    | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| US122                                                   | TDTRF    | Data-Out Rise Time and Fall Time                             | _    | 45   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |

|                                                         |          |                                                              |      | 50   | ns    | $1.8V \le V\text{DD} \le 5.5V$   |

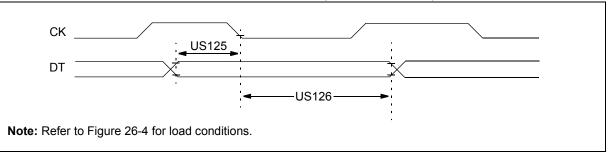

#### FIGURE 26-14: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 26-18: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |          |                                                                                |      |      |       |            |  |

|---------------------------------------------------------|----------|--------------------------------------------------------------------------------|------|------|-------|------------|--|

| Param.<br>No.                                           | Symbol   | Characteristic                                                                 | Min. | Max. | Units | Conditions |  |

| US125                                                   | TDTV2CKL | SYNC RCV (Master and Slave)<br>Data-Hold before $CK \downarrow$ (DT hold time) | 10   |      | ns    |            |  |

| US126                                                   | TCKL2DTL | Data-Hold after CK $\downarrow$ (DT hold time)                                 | 15   | _    | ns    |            |  |

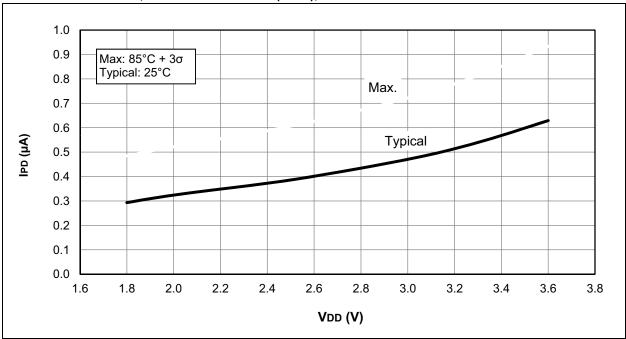

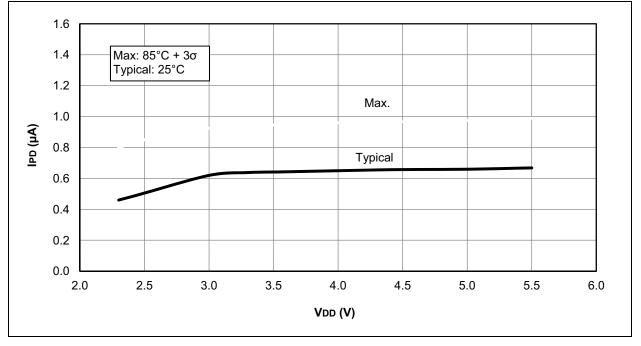

FIGURE 27-23: IPD, WATCHDOG TIMER (WDT), PIC12LF1571/2 ONLY

## 29.0 PACKAGING INFORMATION

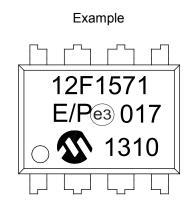

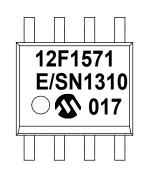

## 29.1 Package Marking Information

8-Lead PDIP (300 mil)

8-Lead SOIC (3.90 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                             |