Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | LINbus, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 6                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | <u> </u>                                                                    |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-VDFN Exposed Pad                                                          |

| Supplier Device Package    | 8-DFN (3x3)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1572t-i-mf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral, thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C, the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

COG1CON0bits.MD = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name, MD2, and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

### Example 1:

```

MOVLW ~(1<<G1MD1)

ANDWF COG1CON0,F

MOVLW 1<<G1MD2 | 1<<G1MD0

IORWF COG1CON0,F

```

#### Example 2:

| BSF | COG1CON0,G1MD2 |

|-----|----------------|

| BCF | COG1CON0,G1MD1 |

| BSF | COG1CON0,G1MD0 |

# 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

# 1.1.3.1 Status, Interrupt and Mirror Bits

Status, interrupt enables, interrupt flags and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

# 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

# TABLE 3-7:PIC12(L)F1571/2 MEMORY<br/>MAP, BANK 27

|      | Bank 31                             |              |

|------|-------------------------------------|--------------|

| D8Ch |                                     |              |

| D8Dh |                                     |              |

| D8Eh | PWMEN                               |              |

| D8Fh | PWMLD                               |              |

| D90h | PWMOUT                              |              |

| D91h | PWM1PHL                             |              |

| D92h | PWM1PHH                             |              |

| D93h | PWM1DCL                             |              |

| D94h | PWM1DCH                             |              |

| D95h | PWM1PRL                             |              |

| D96h | PWM1PRH                             |              |

| D97h | PWM10FL                             |              |

| D98h | PWM10FH                             |              |

| D99h | PWM1TMRL                            |              |

| D9Ah | PWM1TMRH                            |              |

| D9Bh | PWM1CON                             |              |

| D9Ch | PWM1INTE                            |              |

| D9Dh | PWM1INTF                            |              |

| D9Eh | PWM1CLKCON                          |              |

| D9Fh | PWM1LDCON                           |              |

| DA0h | PWM10FC0N                           |              |

| DA1h | PWM2PHL                             |              |

| DA2h | PWM2PHH                             |              |

| DA3h | PWM2DCL                             |              |

| DA4h | PWM2DCH                             |              |

| DA5h | PWM2PRL                             |              |

| DA6h | PWM2PRH                             |              |

| DA7h | PWM2OFL                             |              |

| DA8h | PWM2OFH                             |              |

| DA9h | PWM2TMRL                            |              |

| DAAh | PWM2TMRH                            |              |

| DABh | PWM2CON                             |              |

| DACh | PWM2INTE                            |              |

| DADh | PWM2INTF                            |              |

| DAEh | PWM2CLKCON                          |              |

| DAFh | PWM2LDCON                           |              |

| DB0h | PWM2OFCON                           |              |

| DB1h | PWM3PHL                             |              |

| DB2h | PWM3PHH                             |              |

| DB3h | PWM3DCL                             |              |

| DB4h | PWM3DCH                             |              |

| DB5h | PWM2PRL                             |              |

| DB6h | PWM3PRH                             |              |

| DB7h | PWM3OFL                             |              |

| DB8h | PWM30FH                             |              |

| DB9h | PWM3TMRL                            |              |

| DBAh | PWM3TMRH                            |              |

| DBBh | PWM3CON                             |              |

| DBCh | PWM3INTE                            |              |

| DBDh | PWM3INTF                            |              |

| DBEh | PWM3CLKCON                          |              |

| DBFh | PWM3LDCON                           |              |

| DC0h | PWM3OFCON                           |              |

| DC1h |                                     |              |

|      | -                                   |              |

| DEFh |                                     |              |

|      |                                     |              |

|      |                                     |              |

|      | nplemented data memory<br>d as '0'. | y locations, |

| read | u ao U.                             |              |

# TABLE 3-8:PIC12(L)F1571/2 MEMORY<br/>MAP, BANK 31

|                | Bank 31                           |

|----------------|-----------------------------------|

| F8Ch           | Dalik 51                          |

| FOCI           |                                   |

|                | Unimplemented                     |

|                | Read as '0'                       |

|                |                                   |

| FE3h           |                                   |

| FE4h           | STATUS_SHAD                       |

| FE5h           | WREG_SHAD                         |

| FE6h           | BSR_SHAD                          |

| FE7h           | PCLATH_SHAD                       |

| FE8h           | FSR0L_SHAD                        |

| FE9h           | FSR0H_SHAD                        |

| FEAh           | FSR1L_SHAD                        |

| FEBh           | FSR1H_SHAD                        |

| FECh           | _                                 |

| FEDh           | STKPTR                            |

| FEEh           | TOSL                              |

| FEFh           | TOSH                              |

|                |                                   |

|                |                                   |

| Legend: = Unir | nplemented data memory locations, |

|                | d as '0'.                         |

# 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run time. See **Section 5.3 "Clock Switching**" for more information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in the Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Locked Loop, HFPLL, that can produce one of three internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Locked Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 2. The **MFINTOSC** (Medium Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

# 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.8 "Internal Oscillator Clock Switch Timing"** for more information.

The HFINTOSC is enabled by:

- Configuring the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- Setting FOSC<1:0> = 00, or

- Setting the System Clock Source x (SCSx) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

# 5.2.2.2 MFINTOSC

The Medium Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.8 "Internal Oscillator Clock Switch Timing"** for more information.

The MFINTOSC is enabled by:

- Configuring the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- Setting FOSC<1:0> = 00, or

- Setting the System Clock Source x (SCSx) bits of the OSCCON register to '1x'

The Medium Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

NOTES:

#### **Power Control (PCON) Register** 6.13

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- RESET Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

#### 6.14 **Register Definitions: Power Control**

#### \_\_\_\_\_ DOON DOWED CONTROL DECISTED

| REGISTER 6       | 6-2: PCO                                                                                                                                                        | N: POWER C                                       | ONTROL RE                            | GISTER            |                  |                  |                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------|-------------------|------------------|------------------|-----------------|

| R/W/HS-0/q       | R/W/HS-0/q                                                                                                                                                      | U-0                                              | R/W/HC-1/q                           | R/W/HC-1/q        | R/W/HC-1/q       | R/W/HC-q/u       | R/W/HC-q/u      |

| STKOVF           | STKUNF                                                                                                                                                          |                                                  | RWDT                                 | RMCLR             | RI               | POR              | BOR             |

| bit 7            |                                                                                                                                                                 |                                                  |                                      |                   |                  |                  | bit 0           |

|                  |                                                                                                                                                                 |                                                  |                                      |                   |                  |                  |                 |

| Legend:          |                                                                                                                                                                 |                                                  | e Clearable bit                      |                   | are Settable bit |                  |                 |

| R = Readable     |                                                                                                                                                                 | W = Writable                                     |                                      |                   | mented bit, read |                  |                 |

| u = Bit is unch  | nanged                                                                                                                                                          | x = Bit is unkr                                  | nown                                 | -n/n = Value a    | at POR and BO    | R/Value at all o | ther Resets     |

| '1' = Bit is set |                                                                                                                                                                 | '0' = Bit is clea                                | ared                                 | q = Value der     | pends on condit  | ion              |                 |

| bit 7            | 1 = A Stack                                                                                                                                                     | ack Overflow F<br>Overflow Rese<br>Overflow Rese | •                                    | ed or is cleared  | d by firmware    |                  |                 |

| bit 6            | <b>STKUNF:</b> Stack Underflow Reset Flag bit<br>1 = A Stack Underflow Reset occurred<br>0 = A Stack Underflow Reset has not occurred or is cleared by firmware |                                                  |                                      |                   |                  |                  |                 |

| bit 5            | Unimpleme                                                                                                                                                       | nted: Read as                                    | '0'                                  |                   |                  |                  |                 |

| bit 4            | RWDT: Wato                                                                                                                                                      | hdog Timer Re                                    | eset Flag bit                        |                   |                  |                  |                 |

|                  |                                                                                                                                                                 |                                                  | et has not occur<br>et has occurred  |                   |                  |                  |                 |

| bit 3            | RMCLR: MC                                                                                                                                                       | LR Reset Flag                                    | bit                                  |                   |                  |                  |                 |

|                  |                                                                                                                                                                 |                                                  | occurred or is s<br>urred (cleared b |                   |                  |                  |                 |

| bit 2            | RI: RESET IN                                                                                                                                                    | struction Flag                                   | bit                                  |                   |                  |                  |                 |

|                  |                                                                                                                                                                 |                                                  | s not been exec<br>s been executed   | •                 |                  |                  |                 |

| bit 1            | POR: Power                                                                                                                                                      | -on Reset Stat                                   | us bit                               |                   |                  |                  |                 |

|                  |                                                                                                                                                                 | er-on Reset occ<br>on Reset occu                 | curred<br>Irred (must be s           | et in software a  | after a Power-or | Reset occurs)    | )               |

| bit 0            | BOR: Brown                                                                                                                                                      | -out Reset Sta                                   | tus bit                              |                   |                  |                  |                 |

|                  |                                                                                                                                                                 | n-out Reset oc<br>out Reset occur                | curred<br>red (must be set           | in software after | a Power-on Res   | set or Brown-ou  | t Reset occurs) |

# 8.3 Register Definitions: Voltage Regulator Control

### **REGISTER 8-1:** VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1  |  |  |

|-------------|-----|-----|-----|-----|-----|---------|----------|--|--|

| —           | —   | —   | —   | —   | —   | VREGPM  | Reserved |  |  |

| bit 7 bit 0 |     |     |     |     |     |         |          |  |  |

|             |     |     |     |     |     |         |          |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

### bit 7-2 Unimplemented: Read as '0'

bit 1

Unimplemented. Read as 0

VREGPM: Voltage Regulator Power Mode Selection bit

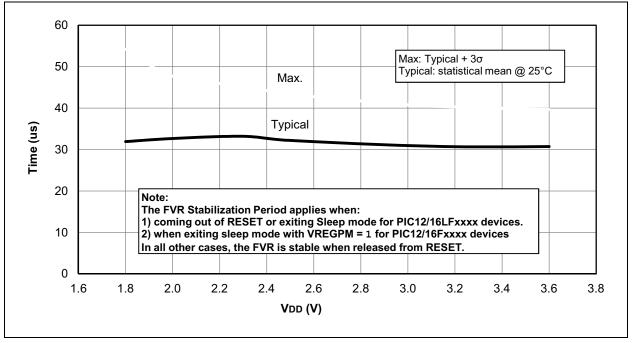

- 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup> Draws lowest current in Sleep, slower wake-up.

- 0 = Normal power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up.

bit 0 **Reserved:** Read as '1', maintain this bit set

**Note 1:** PIC12F1571/2 only.

2: See Section 26.0 "Electrical Specifications"

| Name   | Bit 7   | Bit 6  | Bit 5               | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|--------|---------------------|---------------------|--------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | TMR0IE              | INTE                | IOCIE  | TMR0IF | INTF   | IOCIF  | 74                  |

| IOCAF  | _       | _      | IOCAF5              | IOCAF4              | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 122                 |

| IOCAN  | _       | —      | IOCAN5              | IOCAN4              | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 121                 |

| IOCAP  | _       | _      | IOCAP5              | IOCAP4              | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 121                 |

| PIE1   | TMR1GIE | ADIE   | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | _      | —      | TMR2IE | TMR1IE | 75                  |

| PIE2   | _       | _      | C1IE                | —                   | _      | —      | _      | _      | 76                  |

| PIE3   | _       | PWM3IE | PWM2IE              | PWM1IE              | _      | —      | _      | —      | 77                  |

| PIR1   | TMR1GIF | ADIF   | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | _      | —      | TMR2IF | TMR1IF | 78                  |

| PIR2   | —       | —      | C1IF                | —                   | —      | —      | —      | —      | 79                  |

| PIR3   | _       | PWM3IF | PWM2IF              | PWM1IF              | _      | —      | _      | —      | 80                  |

| STATUS |         |        |                     | TO                  | PD     | Z      | DC     | С      | 19                  |

| WDTCON |         | _      |                     | V                   |        | SWDTEN | 89     |        |                     |

# TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

**Note 1:** PIC12(L)F1572 only.

# 10.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat Steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 10-5 (row writes to program memory with 16 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper 11 bits of PMADRH:PMADRL (PMADRH<6:0>:PMADRL<7:4>), with the lower 4 bits of PMADRL (PMADRL<3:0>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF.

The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

Note: The special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. If the unlock sequence is interrupted, writing to the latches or program memory will not be initiated.

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- 6. Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat Steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- 11. Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- **Note:** The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 10-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using Indirect Addressing.

# 10.4 User ID, Device ID and Configuration Word Access

Instead of accessing program memory, the User IDs, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the PMCON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 10-2. When read access is initiated on an address outside the parameters listed in Table 10-2, the PMDATH:PMDATL register pair is cleared, reading back '0's.

### TABLE 10-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h/8005h | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### EXAMPLE 10-4: CONFIGURATION WORD AND DEVICE ID ACCESS

\* This code block will read 1 word of program memory at the memory address:

\* PROG\_ADDR\_LO (must be 00h-08h) data will be returned in the variables;

\* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL                                | PMADRL                                                   | ; Select correct Bank                                                                                                                                      |  |

|----------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MOVLW                                  | PROG_ADDR_LO                                             | ;                                                                                                                                                          |  |

| MOVWF                                  | PMADRL                                                   | ; Store LSB of address                                                                                                                                     |  |

| CLRF                                   | PMADRH                                                   | ; Clear MSB of address                                                                                                                                     |  |

| BSF<br>BCF<br>BSF<br>NOP<br>NOP<br>BSF | PMCON1, CFGS<br>INTCON, GIE<br>PMCON1, RD<br>INTCON, GIE | <pre>; Select Configuration Space ; Disable interrupts ; Initiate read ; Executed (See Figure 10-2) ; Ignored (See Figure 10-2) ; Restore interrupts</pre> |  |

| MOVF                                   | PMDATL,W                                                 | ; Get LSB of word                                                                                                                                          |  |

| MOVWF                                  | PROG_DATA_LO                                             | ; Store in user location                                                                                                                                   |  |

| MOVF                                   | PMDATH,W                                                 | ; Get MSB of word                                                                                                                                          |  |

| MOVWF                                  | PROG_DATA_HI                                             | ; Store in user location                                                                                                                                   |  |

| Name       | Bit 7   | Bit 6   | Bit 5      | Bit 4       | Bit 3  | Bit 2      | Bit 1     | Bit 0 | Register<br>on Page |

|------------|---------|---------|------------|-------------|--------|------------|-----------|-------|---------------------|

| ANSELA     | _       | —       | _          | ANSA4       | _      | ŀ          | ANSA<2:0> |       | 114                 |

| APFCON     | RXDTSEL | CWGASEL | CWGBSEL    | _           | T1GSEL | TXCKSEL    | P2SEL     | P1SEL | 110                 |

| INLVLA     | _       | —       |            | INLVLA<5:0> |        |            |           |       | 116                 |

| LATA       | _       | —       | LATA<      | :5:4>       | —      | LATA<2:0>  |           |       | 114                 |

| ODCONA     | _       | —       | ODA<       | 5:4>        | _      | ODA<2:0>   |           |       | 115                 |

| OPTION_REG | WPUEN   | INTEDG  | TMR0CS     | TMR0SE      | PSA    |            | PS<2:0>   |       | 157                 |

| PORTA      | _       | _       |            |             | RA<    | <5:0>      |           |       | 113                 |

| SLRCONA    | _       | —       | SLRA       | <5:4>       | —      | SLRA<2:0>  |           |       | 116                 |

| TRISA      | _       | _       | TRISA<5:4> |             | _(1)   | TRISA<2:0> |           |       | 113                 |

| WPUA       | _       | _       |            |             | WPU/   | A<5:0>     |           |       | 115                 |

TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** Unimplemented, read as '1'.

#### TABLE 11-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2           | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|--------------------|---------|---------|---------------------|

|         | 13:8 |         |         | FCMEN    | IESO      | CLKOUTEN | BOREN<1:0>         |         |         | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | DTE<1:0> FOSC<2:0> |         |         | 42                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

# 16.6 Register Definitions: DAC Control

# REGISTER 16-1: DACxCON0: DACx VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0          | U-0          | R/W-0/0           | U-0            | R/W-0/0        | R/W-0/0          | U-0             | U-0         |

|------------------|--------------|-------------------|----------------|----------------|------------------|-----------------|-------------|

| DACEN            | _            | DACOE             |                | DACPS          | SS<1:0>          | —               | —           |

| bit 7            |              |                   |                |                |                  |                 | bit 0       |

|                  |              |                   |                |                |                  |                 |             |

| Legend:          |              |                   |                |                |                  |                 |             |

| R = Readable     | bit          | W = Writable      | bit            |                |                  |                 |             |

| u = Bit is unch  | anged        | x = Bit is unkn   | own            | U = Unimpler   | nented bit, read | as '0'          |             |

| '1' = Bit is set |              | '0' = Bit is clea | ared           | -n/n = Value a | at POR and BOR   | /Value at all o | ther Resets |

|                  |              |                   |                |                |                  |                 |             |

| bit 7            | DACEN: DAC   | C Enable bit      |                |                |                  |                 |             |

|                  | 1 = DACx is  | enabled           |                |                |                  |                 |             |

|                  | 0 = DACx is  | disabled          |                |                |                  |                 |             |

| bit 6            | Unimplemen   | ted: Read as 'd   | )'             |                |                  |                 |             |

| bit 5            | DACOE: DAG   | C Voltage Outpu   | ut Enable bit  |                |                  |                 |             |

|                  | 1 = DACx vo  | Itage level is ou | Itput on the D | ACxOUT1 pin    |                  |                 |             |

|                  | 0 = DACx vo  | Itage level is di | sconnected fr  | om the DACxC   | UT1 pin          |                 |             |

| bit 4            | Unimplemen   | ted: Read as 'o   | )'             |                |                  |                 |             |

| bit 3-2          | DACPSS<1:0   | >: DAC Positiv    | e Source Sel   | ect bits       |                  |                 |             |

|                  | 11 = Reserve | ed                |                |                |                  |                 |             |

|                  | 10 = FVR_bu  |                   |                |                |                  |                 |             |

|                  | 01 = VREF+ p | pin               |                |                |                  |                 |             |

|                  | 00 = VDD     |                   |                |                |                  |                 |             |

| bit 1-0          | Unimplemen   | ted: Read as '    | )'             |                |                  |                 |             |

# REGISTER 16-2: DACxCON1: DACx VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| —     | —   | -   |         |         | DACR<4:0> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits

### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1 | Bit 0 | Register<br>on Page |

|----------|-------|-------|-------|-------|-------|-----------|-------|-------|---------------------|

| DACxCON0 | DACEN | _     | DACOE |       | DACPS | S<1:0>    | _     | _     | 145                 |

| DACxCON1 | _     | _     | _     |       |       | DACR<4:0> | >     |       | 145                 |

**Legend:** — = Unimplemented location, read as '0'.

# 21.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer, independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- · Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- · 13-bit Break character transmit

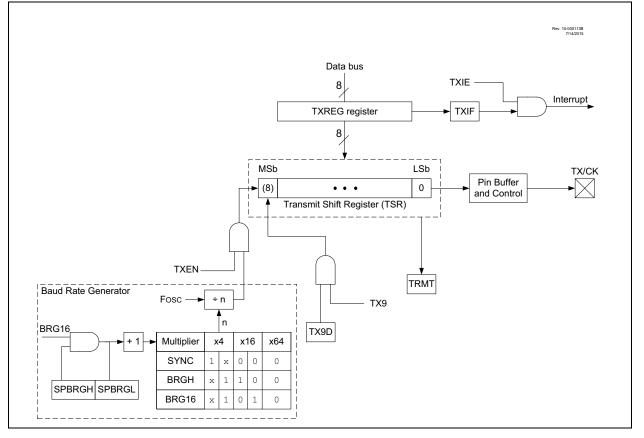

Block diagrams of the EUSART transmitter and receiver are shown in Figure 21-1 and Figure 21-2.

# FIGURE 21-1: EUSART TRANSMIT BLOCK DIAGRAM

| R/W-0/0          | R/W-0/0                     | R/W-0/0                                                                                    | R/W-0/0           | R/W-0/0         | R-0/0                            | R-0/0            | R-0/0        |  |  |

|------------------|-----------------------------|--------------------------------------------------------------------------------------------|-------------------|-----------------|----------------------------------|------------------|--------------|--|--|

| SPEN             | RX9                         | SREN                                                                                       | CREN              | ADDEN           | FERR                             | OERR             | RX9D         |  |  |

| bit 7            |                             |                                                                                            |                   |                 |                                  |                  | bit (        |  |  |

|                  |                             |                                                                                            |                   |                 |                                  |                  |              |  |  |

| Legend:          |                             |                                                                                            |                   |                 |                                  |                  |              |  |  |

| R = Readable     | e bit                       | W = Writable                                                                               | bit               |                 |                                  |                  |              |  |  |

| u = Bit is uncl  | hanged                      | x = Bit is unk                                                                             | nown              | U = Unimpler    | nented bit, read                 | as '0'           |              |  |  |

| '1' = Bit is set |                             | '0' = Bit is cle                                                                           | ared              | -n/n = Value    | at POR and BO                    | R/Value at all c | other Resets |  |  |

| bit 7            | SPEN: Seria                 | l Port Enable b                                                                            | ŧ                 |                 |                                  |                  |              |  |  |

|                  |                             |                                                                                            |                   | DT and TX/Ck    | C pins as serial p               | ort pins)        |              |  |  |

|                  |                             | ort is disabled (                                                                          |                   |                 |                                  | sort pillo)      |              |  |  |

| bit 6            | <b>RX9:</b> 9-Bit R         | eceive Enable I                                                                            | oit               |                 |                                  |                  |              |  |  |

|                  |                             | 9-bit reception<br>8-bit reception                                                         |                   |                 |                                  |                  |              |  |  |

| bit 5            | SREN: Single                | e Receive Enal                                                                             | ole bit           |                 |                                  |                  |              |  |  |

|                  | Asynchronou<br>Don't care.  | is mode:                                                                                   |                   |                 |                                  |                  |              |  |  |

|                  | Synchronous                 | s mode – Maste                                                                             | <u>r:</u>         |                 |                                  |                  |              |  |  |

|                  |                             | single receive                                                                             |                   |                 |                                  |                  |              |  |  |

|                  |                             | s single receive<br>ared after rece                                                        | ntion is compl    | ata             |                                  |                  |              |  |  |

|                  |                             | s mode – Slave                                                                             |                   |                 |                                  |                  |              |  |  |

|                  | Don't care.                 |                                                                                            | -                 |                 |                                  |                  |              |  |  |

| bit 4            | CREN: Conti                 | inuous Receive                                                                             | Enable bit        |                 |                                  |                  |              |  |  |

|                  | Asynchronou                 |                                                                                            |                   |                 |                                  |                  |              |  |  |

|                  | 1 = Enables<br>0 = Disables |                                                                                            |                   |                 |                                  |                  |              |  |  |

|                  | Synchronous                 |                                                                                            |                   |                 |                                  |                  |              |  |  |

|                  |                             |                                                                                            | eive until enal   | ole bit CREN is | cleared (CREN                    | l overrides SR   | EN)          |  |  |

|                  |                             | s continuous ree                                                                           |                   |                 | , ,                              |                  | ,            |  |  |

| bit 3            | ADDEN: Add                  | dress Detect Er                                                                            | able bit          |                 |                                  |                  |              |  |  |

|                  |                             | is mode 9-bit (F                                                                           |                   |                 |                                  |                  |              |  |  |

|                  |                             |                                                                                            |                   | •               | ads the receive nd ninth bit can |                  |              |  |  |

|                  |                             | is mode 8-bit (F                                                                           | -                 | ale leceiveu a  | nu minur bit can                 | be used as pa    |              |  |  |

|                  | Don't care.                 |                                                                                            | 0,0 = 0           |                 |                                  |                  |              |  |  |

| bit 2            | FERR: Fram                  | ing Error bit                                                                              |                   |                 |                                  |                  |              |  |  |

|                  |                             | 1 = Framing error (can be updated by reading RCREG register and receiving next valid byte) |                   |                 |                                  |                  |              |  |  |

|                  | 0 = No frami                | ing error                                                                                  |                   |                 |                                  |                  |              |  |  |

| bit 1            | OERR: Over                  |                                                                                            |                   |                 |                                  |                  |              |  |  |

|                  | 1 = Overrun<br>0 = No overr | error (can be c<br>run error                                                               | leared by clea    | iring bit, CREN | 1)                               |                  |              |  |  |

| bit 0            | RX9D: Ninth                 | Bit of Received                                                                            | l Data bit        |                 |                                  |                  |              |  |  |

|                  | This can be a               | address/data bi                                                                            | t or a parity bit | and must be o   | calculated by us                 | er firmware      |              |  |  |

# REGISTER 21-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

# 21.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH/SPBRGL register pair determines the period of the free-running baud rate timer. In Asynchronous mode, the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 21-3 contains the formulas for determining the baud rate. Example 21-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 21-3. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH/SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is Idle before changing the system clock.

# EXAMPLE 21-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

$Desired Baud Rate = \frac{Fosc}{64([SPBRGH:SPBRGL] + 1)}$ Solving for SPBRGH:SPBRGL:  $\frac{Fosc}{Desired Baud Rate}$

$X = \frac{\overline{Desired Baud Rate}}{64} - 1$  $= \frac{\frac{16000000}{9600}}{64} - 1$ = [25.042] = 25Calculated Baud Rate =  $\frac{16000000}{64(25+1)}$ = 9615Error =  $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$  $= \frac{(9615 - 9600)}{9600} = 0.16\%$

Note: There are no long and short bit name variants for the following three mirror registers

# **REGISTER 22-17: PWMEN: PWMEN BIT ACCESS REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0  | R/W-0/0  | R/W-0/0  |

|-------|-----|-----|-----|-----|----------|----------|----------|

| —     | —   | —   | —   | _   | PWM3EN_A | PWM2EN_A | PWM1EN_A |

| bit 7 |     |     |     |     |          |          | bit 0    |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-3 Unimplemented: Read as '0' bit 2-0 PWMxEN\_A: PWM3/PWM2/PWM1 Enable bits Mirror copy of EN bit (PWMxCON<7>).

# REGISTER 22-18: PWMLD: LD BIT ACCESS REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0   | R/W-0/0   | R/W-0/0   |

|-------|-----|-----|-----|-----|-----------|-----------|-----------|

| —     | —   | —   | —   | —   | PWM3LDA_A | PWM2LDA_A | PWM1LDA_A |

| bit 7 |     |     |     |     |           |           | bit 0     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

bit 7-3 Unimplemented: Read as '0' bit 2-0 PWMxLDA\_A: PWM3/PWM2/PWM1 LD bits Mirror copy of LD bit (PWMxLDCON<7>).

#### **REGISTER 22-19: PWMOUT: PWMOUT BIT ACCESS REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0   | R/W-0/0   | R/W-0/0   |

|-------|-----|-----|-----|-----|-----------|-----------|-----------|

| —     | —   | —   | —   | _   | PWM3OUT_A | PWM2OUT_A | PWM1OUT_A |

| bit 7 |     |     |     |     |           |           | bit 0     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     |                                                       |

| u = Bit is unchanged | x = Bit is unknown   | U = Unimplemented bit, read as '0'                    |

| '1' = Bit is set     | '0' = Bit is cleared | -n/n = Value at POR and BOR/Value at all other Resets |

# bit 7-3 Unimplemented: Read as '0'

bit 2-0 **PWMxOUT\_A:** PWM3/PWM2/PWM1 Output bits Mirror copy of OUT bit (PWMxCON<5>).

#### 25.2 **Instruction Descriptions**

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDFSR FSRn, k                                                                        |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                         |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wraparound.

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

AND W with f

[label] ANDWF

(W) .AND. (f)  $\rightarrow$  (destination)

$0 \leq f \leq 127$  $d \in [0,1]$

Ζ

f,d

ANDWF

Syntax:

Operands:

Operation:

Description:

Status Affected:

| ADDLW            | Add literal and W                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |

| Operation:       | $(W) + k \to (W)$                                                                                                   |

| Status Affected: | C, DC, Z                                                                                                            |

| Description:     | The contents of the W register are<br>added to the 8-bit literal 'k' and the<br>result is placed in the W register. |

| ADDWF Add | d V | V and | f |

|-----------|-----|-------|---|

|-----------|-----|-------|---|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| Description: | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASRF         | Arithmetic Right Shift                                                                                                                                          |

| Syntax:      | [ <i>label</i> ] ASRF f {,d}                                                                                                                                    |

| Operands:    | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |

| Operation:   | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,                                                                                                                        |

$(f<0>) \rightarrow C,$

Status Affected: C, Z The contents of register 'f' are shifted one bit to the right through the Carry flag. The MSb remains unchanged. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'.

| ADDWFC |  |

|--------|--|

|--------|--|

ADD W and CARRY bit to f

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                            |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                               |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |  |

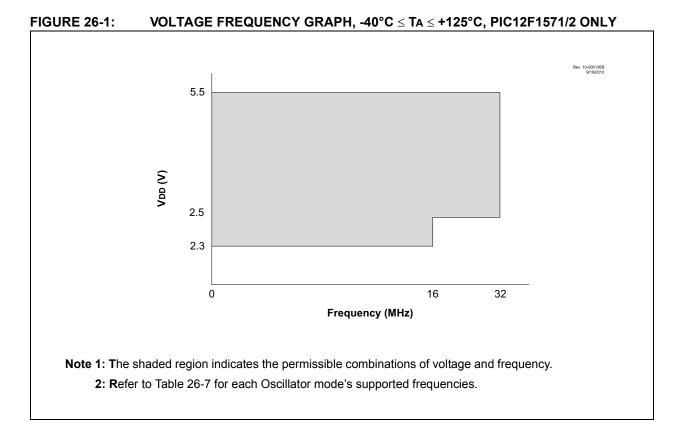

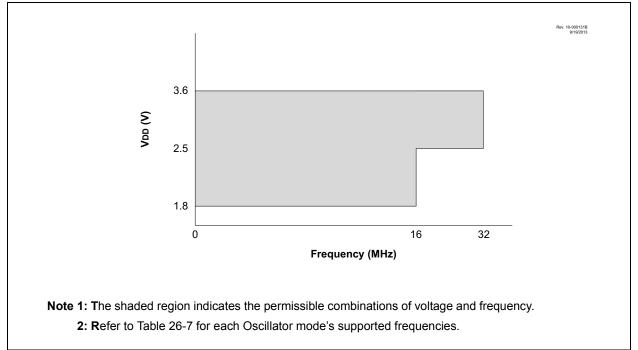

FIGURE 26-2: VOLTAGE FREQUENCY GRAPH, -40°C ≤ TA ≤ +125°C, PIC12LF1571/2 ONLY

# Package Marking Information (Continued)

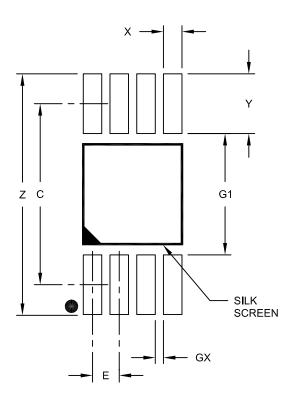

8-Lead MSOP (3x3 mm)

8-Lead DFN (3x3x0.9 mm) 8-Lead UDFN (3x3x0.5 mm)

Example

Example

# 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                         | Units            |          | MILLIMETERS |      |  |

|-------------------------|------------------|----------|-------------|------|--|

| Dimensio                | Dimension Limits |          | NOM         | MAX  |  |

| Contact Pitch           | E                | 0.65 BSC |             |      |  |

| Contact Pad Spacing     | С                |          | 4.40        |      |  |

| Overall Width           | Z                |          |             | 5.85 |  |

| Contact Pad Width (X8)  | X1               |          |             | 0.45 |  |

| Contact Pad Length (X8) | Y1               |          |             | 1.45 |  |

| Distance Between Pads   | G1               | 2.95     |             |      |  |

| Distance Between Pads   | GX               | 0.20     |             |      |  |

# Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2111A