Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z3                                                                  |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 60MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI, UART/USART                           |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 80                                                                      |

| Program Memory Size        | 768KB (768K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | <u>.</u>                                                                |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.25V                                                            |

| Data Converters            | A/D 32x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5632mf1mlq60 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

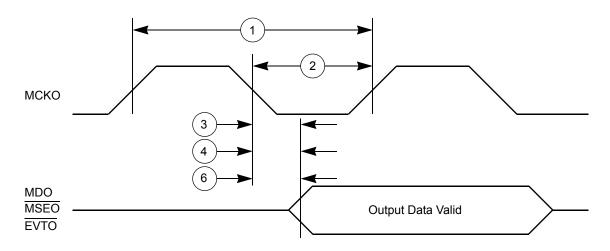

- Auxiliary Output port

- 1 MCKO (message clock out) pin

- 4 MDO (message data out) pins

- $-2 \overline{\text{MSEO}}$  (message start/end out) pins

- $-1 \overline{\text{EVTO}}$  (event out) pin

- Auxiliary input port

- $-1 \overline{\text{EVTI}}$  (event in) pin

- 17-pin Full Port interface in calibration package used on VertiCal boards

- 3.3 V interface

- Auxiliary Output port

- 1 MCKO (message clock out) pin

- 4 (reduced port mode) or 12 (full port mode) MDO (message data out) pins; 8 extra full port pins shared with calibration bus

- 2 MSEO (message start/end out) pins

- $-1 \overline{\text{EVTO}}$  (event out) pin

- Auxiliary input port

- $-1 \overline{\text{EVTI}}$  (event in) pin

- Host processor (e200) development support features

- IEEE-ISTO 5001-2003 standard class 2 compliant

- Program trace via branch trace messaging (BTM). Branch trace messaging displays program flow discontinuities (direct branches, indirect branches, exceptions, etc.), allowing the development tool to interpolate what transpires between the discontinuities. Thus, static code may be traced.

- Watchpoint trigger enable of program trace messaging

- Data Value Breakpoints (JTAG feature of the e200z335 core): allows CPU to be halted when the CPU writes a specific value to a memory location

- 4 data value breakpoints

- CPU only

- Detects 'equal' and 'not equal'

- Byte, half word, word (naturally aligned)

### NOTE

This feature is imprecise due to CPU pipelining.

- Subset of Power Architecture software debug facilities with OnCE block (Nexus class 1 features)

- eTPU development support features

- IEEE-ISTO 5001-2003 standard class 1 compliant for the eTPU

- Nexus based breakpoint configuration and single step support (JTAG feature of the eTPU)

- Run-time access to the on-chip memory map via the Nexus read/write access protocol. This feature supports accesses for run-time internal visibility, calibration variable acquisition, calibration constant tuning, and external rapid prototyping for powertrain automotive development systems.

- All features are independently configurable and controllable via the IEEE 1149.1 I/O port

- Power-on-reset status indication during reset via MDO[0] in disabled and reset modes

### 2.2.20.2 JTAG

The JTAGC (JTAG Controller) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. Testing is performed via a boundary scan technique, as defined in the IEEE 1149.1-2001

# 3.5 208 MAPBGA ballmap (MPC5633M only)

Figure 6 shows the 208-pin MAPBGA ballmap for the MPC5633M (1024 KB flash memory) as viewed from above.

|   | 1                | 2       | 3                | 4               | 5               | 6                | 7                    | 8               | 9                     | 10                   | 11                   | 12               | 13              | 14              | 15               | 16               |

|---|------------------|---------|------------------|-----------------|-----------------|------------------|----------------------|-----------------|-----------------------|----------------------|----------------------|------------------|-----------------|-----------------|------------------|------------------|

| А | VSS              | AN9     | AN11             | VDDA1           | VSSA1           | AN1              | AN5                  | VRH             | VRL                   | AN27                 | VSSA0                | AN12-SDS         | ALT_<br>MDO2    | ALT_<br>MDO0    | VRC33            | VSS              |

| в | VDD              | VSS     | AN38             | AN21            | AN0             | AN4              | REFBYPC              | AN22            | AN25                  | AN28                 | VDDA0                | AN13-SDO         | ALT_<br>MDO3    | ALT_<br>MDO1    | VSS              | VDD              |

| с | VSTBY            | VDD     | VSS              | AN17            | AN34            | AN16             | AN3                  | AN7             | AN23                  | AN32                 | AN33                 | AN14-SDI         | AN15<br>FCK     | VSS             | ALT<br>MSEO0     | тск              |

| D | VRC33            | AN39    | VDD              | VSS             | AN18            | AN2              | AN6                  | AN24            | AN30                  | AN31                 | AN35                 | VDDEH7           | VSS             | TMS             | ALT_EVTO         | NIC <sup>1</sup> |

| Е | ETPUA30          | ETPUA31 | NC <sup>2</sup>  | VDD             |                 |                  |                      |                 |                       |                      |                      |                  | VDDE7           | TDI             | ALT<br>EVTI      | ALT_<br>MSEO1    |

| F | ETPUA28          | ETPUA29 | ETPUA26          | NC <sup>2</sup> |                 |                  |                      |                 |                       |                      |                      |                  | VDDEH6          | TDO             | ALT_MCKO         | JCOMP            |

| G | ETPUA24          | ETPUA27 | ETPUA25          | ETPUA21         |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | DSPI_B_<br>SOUT | DSPI_B_<br>PCS3 | DSPI_B_<br>SIN   | DSPI_B_<br>PCS0  |

| н | ETPUA23          | ETPUA22 | ETPUA17          | ETPUA18         |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | NC <sup>2</sup> | DSPI_B_<br>PCS4 | DSPI_B_<br>PCS2  | DSPI_B_<br>PCS1  |

| J | ETPUA20          | ETPUA19 | ETPUA14          | ETPUA13         |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | DSPI_B_<br>PCS5 | SCI_A_TX        | NC <sup>2</sup>  | DSPI_B_<br>SCK   |

| к | ETPUA16          | ETPUA15 | ETPUA7           | VDDEH1          |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | CAN_C_<br>TX    | SCI_A_RX        | RSTOUT           | VDDREG           |

| L | ETPUA12          | ETPUA11 | ETPUA6           | ETPUA0          |                 |                  |                      |                 |                       |                      |                      |                  | SCI_B_TX        | CAN_C_<br>RX    | WKPCFG           | RESET            |

| м | ETPUA10          | ETPUA9  | ETPUA1           | ETPUA5          |                 |                  |                      |                 |                       |                      |                      |                  | SCI_B_RX        | PLLREF          | BOOTCFG1         | VSSPLL           |

| N | ETPUA8           | ETPUA4  | ETPUA0           | VSS             | VDD             | VRC33            | EMIOS2               | EMIOS10         | VDDEH1/6 <sup>3</sup> | EMIOS12              | eTPUA19 <sup>4</sup> | VRC33            | VSS             | VRCCTL          | NIC <sup>1</sup> | EXTAL            |

| Ρ | ETPUA3           | ETPUA2  | VSS              | VDD             | NC <sup>2</sup> | VDDE7            | NIC <sup>1</sup>     | EMIOS8          | eTPUA29 <sup>3</sup>  | eTPUA2 <sup>3</sup>  | eTPUA21 <sup>3</sup> | CAN_A_<br>TX     | VDD             | VSS             | NIC <sup>1</sup> | XTAL             |

| R | NIC <sup>1</sup> | VSS     | VDD              | NC <sup>2</sup> | EMIOS4          | NIC <sup>1</sup> | EMIOS9               | EMIOS11         | EMIOS14               | eTPUA27 <sup>3</sup> | EMIOS23              | CAN_A_<br>RX     | NC <sup>2</sup> | VDD             | VSS              | VDDPLL           |

| т | VSS              | VDD     | NIC <sup>1</sup> | EMIOS0          | NC <sup>2</sup> | GPIO219          | eTPUA25 <sup>3</sup> | NC <sup>2</sup> | NC <sup>2</sup>       | eTPUA4 <sup>3</sup>  | eTPUA13 <sup>3</sup> | NIC <sup>1</sup> | VDDE5           | CLKOUT          | VDD              | VSS              |

<sup>1</sup> Pins marked "NIC" have no internal connection.

<sup>2</sup> Pins marked "NC" may be connected to internal circuitry. Connections to external circuits or other pins on this device can result in unpredictable system behavior or damage.

<sup>3</sup> This ball may be changed to "NC" (no connection) in a future revision.

<sup>4</sup> eTPU output only channel.

Figure 6. 208-pin MAPBGA ballmap (MPC5633M; top view)

34 4

MPC5634M Microcontroller Data Sheet, Rev.

ø

|                                                                  |                                                     | Pad<br>Config.                 | PCR PA             | I/O    | Voltage <sup>4</sup> /                              |                          | Eurotion / State                                            | F           | Pin No.     |                |

|------------------------------------------------------------------|-----------------------------------------------------|--------------------------------|--------------------|--------|-----------------------------------------------------|--------------------------|-------------------------------------------------------------|-------------|-------------|----------------|

| Name                                                             | Function <sup>1</sup>                               | Register<br>(PCR) <sup>2</sup> | Field <sup>3</sup> | Туре   | Pad Type                                            | Reset State <sup>5</sup> | Function / State<br>After Reset <sup>6</sup>                | 144<br>LQFP | 176<br>LQFP | 208 MAPB<br>GA |

| CAL_ADDR[16] <sup>21</sup><br>ALT_MDO[0] <sup>12</sup>           | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | _                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>15</sup>    | MDO /<br>ALT_ADDR <sup>12</sup> /<br>Low                    | _           | 17          | A14            |

| CAL_ADDR[17] <sup>21</sup><br>ALT_MDO[1] <sup>12</sup>           | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | _                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>15</sup>    | ALT_MDO /<br>CAL_ADDR <sup>12</sup> /<br>Low                | _           | 18          | B14            |

| CAL_ADDR[18] <sup>21</sup><br>ALT_MDO[2] <sup>12</sup>           | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>15</sup>    | ALT_MDO /<br>CAL_ADDR <sup>12</sup> /<br>Low                | _           | 19          | A13            |

| CAL_ADDR[19] <sup>21</sup><br>ALT_MDO[3] <sup>12</sup>           | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>15</sup>    | ALT_MDO /<br>CAL_ADDR <sup>12</sup> /<br>Low                | _           | 20          | B13            |

| CAL_ADDR[20:27]<br>ALT_MDO[4:11]                                 | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>Fast                        | O / Low                  | ALT_MDO /<br>CAL_ADDR <sup>16</sup> /<br>Low                | _           | —           | -              |

| CAL_ <u>ADDR[</u> 28] <sup>21</sup><br>ALT_MSEO[0] <sup>12</sup> | Calibration Address Bus<br>Nexus Msg Start/End Out  | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>17</sup>    | ALT_MSEO <sup>16</sup> /<br>CAL_ADDR <sup>17</sup> /<br>Low | _           | 118         | C15            |

| CAL_ <u>ADDR</u> [29] <sup>21</sup><br>ALT_MSEO[1] <sup>12</sup> | Calibration Address Bus<br>Nexus Msg Start/End Out  | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>17</sup>    | ALT_MSEO <sup>16</sup> /<br>CAL_ADDR <sup>17</sup> /<br>Low | _           | 117         | E16            |

| CAL_ <u>ADD</u> R[30] <sup>21</sup><br>ALT_EVTI <sup>12</sup>    | Calibration Address Bus<br>Nexus Event In           | PCR[345]                       | -                  | 0<br>1 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | 18                       | ALT_EVTI /<br>CAL_ADDR <sup>19</sup>                        | _           | 116         | E15            |

| ALT_EVTO                                                         | Nexus Event Out                                     | PCR[344]                       | -                  | 0      | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low                  | ALT_EVTO /<br>High                                          | _           | 120         | D15            |

| ALT_MCKO                                                         | Nexus Msg Clock Out                                 | PCR[344]                       | -                  | 0      | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low                  | ALT_MCKO /<br>Enabled                                       | _           | 14          | F15            |

| NEXUSCFG <sup>11</sup>                                           | Nexus/Calibration bus selector                      | -                              | -                  | I      | VDDE12<br>Fast                                      | I / Down                 | NEXUSCFG /<br>Down                                          | -           | —           | _              |

| CAL_CS[0] <sup>11</sup>                                          | Calibration Chip Selects                            | PCR[336]                       | _                  | 0      | VDDE12<br>Fast                                      | O / High                 | CAL_CS / High                                               | _           | -           | _              |

| CAL_CS[2] <sup>11</sup><br>CAL_ADDR[10]                          | Calibration Chip Selects<br>Calibration Address Bus | PCR[338]                       | 11<br>10           | 0<br>0 | VDDE12<br>Fast                                      | O / High                 | CAL_CS / High                                               |             | -           | _              |

Table 2. MPC563xM signal properties (continued)

MPC5634M Microcontroller Data Sheet, Rev. 9

36

Pinout and signal description

# 3.7 Signal details

Table 4 contains details on the multiplexed signals that appear in Table 2, "MPC563xM signal properties".

| Signal                       | Module or Function | Description                                                                                                                                                                                                               |

|------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT                       | Clock Generation   | MPC5634M clock output for the external/calibration bus interface                                                                                                                                                          |

| EXTAL                        | Clock Generation   | Input pin for an external crystal oscillator or an external clock source based on the value driven on the PLLREF pin at reset.                                                                                            |

| EXTCLK                       | Clock Generation   | External clock input                                                                                                                                                                                                      |

| PLLREF                       | Clock Generation   | PLLREF is used to select whether the oscillator operates in xtal mode or external reference mode from reset. PLLREF=0 selects external reference mode.                                                                    |

| XTAL                         | Clock Generation   | Crystal oscillator input                                                                                                                                                                                                  |

| SCK_B_LVDS-<br>SCK_B_LVDS+   | DSPI               | LVDS pair used for DSPI_B TSB mode transmission                                                                                                                                                                           |

| SOUT_B_LVDS-<br>SOUT_B_LVDS+ | DSPI               | LVDS pair used for DSPI_B TSB mode transmission                                                                                                                                                                           |

| SCK_C_LVDS-<br>SCK_C_LVDS+   | DSPI               | LVDS pair used for DSPI_C TSB mode transmission                                                                                                                                                                           |

| SOUT_C_LVDS-<br>SOUT_C_LVDS+ | DSPI               | LVDS pair used for DSPI_C TSB mode transmission                                                                                                                                                                           |

| PCS_B[0]<br>PCS_C[0]         | DSPI_B – DSPI_C    | Peripheral chip select when device is in master mode—slave select when used in slave mode                                                                                                                                 |

| PCS_B[1:5]<br>PCS_C[1:5]     | DSPI_B – DSPI_C    | Peripheral chip select when device is in master mode—not used in slave mode                                                                                                                                               |

| SCK_B<br>SCK_C               | DSPI_B – DSPI_C    | DSPI clock—output when device is in master mode; input when in slave mode                                                                                                                                                 |

| SIN_B<br>SIN_C               | DSPI_B – DSPI_C    | DSPI data in                                                                                                                                                                                                              |

| SOUT_B<br>SOUT_C             | DSPI_B – DSPI_C    | DSPI data out                                                                                                                                                                                                             |

| CAL_ADDR[12:30]              | Calibration Bus    | The CAL_ADDR[12:30] signals specify the physical address of the bus transaction.                                                                                                                                          |

| CAL_ <u>CS</u> [0:3]         | Calibration Bus    | $\overline{\text{CS}}$ x is asserted by the master to indicate that this transaction is targeted for a particular memory bank on the Primary external bus.                                                                |

| CAL_DATA[0:15]               | Calibration Bus    | The CAL_DATA[0:15] signals contain the data to be transferred for the current transaction.                                                                                                                                |

| CAL_OE                       | Calibration Bus    | OE is used to indicate when an external memory is permitted to<br>drive back read data. External memories must have their data<br>output buffers off when OE is negated. OE is only asserted for<br>chip-select accesses. |

### Table 4. Signal details

The thermal resistance is expressed as the sum of a junction-to-case thermal resistance plus a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA} \qquad \qquad Eqn. 3$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)  $R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$R_{\Theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and is not affected by other factors. The thermal environment can be controlled to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For example, change the air flow around the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This description is most useful for packages with heat sinks where 90% of the heat flow is through the case to heat sink to ambient. For most packages, a better model is required.

A more accurate two-resistor thermal model can be constructed from the junction-to-board thermal resistance and the junction-to-case thermal resistance. The junction-to-case thermal resistance describes when using a heat sink or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. This model can be used to generate simple estimations and for computational fluid dynamics (CFD) thermal models.

To determine the junction temperature of the device in the application on a prototype board, use the thermal characterization parameter ( $\Psi_{JT}$ ) to determine the junction temperature by measuring the temperature at the top center of the package case using the following equation:

$$T_{J} = T_{T} + (\Psi_{JT} \times P_{D}) \qquad \qquad Eqn. 4$$

where:

$T_T$  = thermocouple temperature on top of the package (<sup>o</sup>C)

$\Psi_{JT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured in compliance with the JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. Position the thermocouple so that the thermocouple junction rests on the package. Place a small amount of epoxy on the thermocouple junction and approximately 1 mm of wire extending from the junction. Place the thermocouple wire flat against the package case to avoid measurement errors caused by the cooling effects of the thermocouple wire.

References:

Semiconductor Equipment and Materials International 3081 Zanker Road San Jose, CA 95134 USA (408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the web at http://www.jedec.org.

- C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47-54.

- G. Kromann, S. Shidore, and S. Addison, "Thermal Modeling of a PBGA for Air-Cooled Applications", Electronic Packaging and Production, pp. 53-58, March 1998.

| Symbol             |    | с | Parameter                                                                                     | Conditions             |                        | Value <sup>2</sup> |                        | Unit |

|--------------------|----|---|-----------------------------------------------------------------------------------------------|------------------------|------------------------|--------------------|------------------------|------|

| Symbol             |    | C | Parameter                                                                                     | Conditions             | min                    | typ                | max                    | Unit |

| $V_{IL_{LS}}$      | CC | С | Multi-voltage pad I/O<br>input low voltage in                                                 | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | —                  | 0.8                    | V    |

|                    |    | Ρ | low-swing<br>mode <sup>10,11,12,13</sup>                                                      | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _                  | 1.1                    |      |

| $V_{IL_{HS}}$      | CC | С | Multi-voltage pad I/O<br>input low voltage in                                                 | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _                  | 0.35 V <sub>DDEH</sub> | V    |

|                    |    | Ρ | high-swing mode                                                                               | Hysteresis<br>disabled | V <sub>SS</sub> –0.3   |                    | 0.4 V <sub>DDEH</sub>  |      |

| V <sub>IH_S</sub>  | CC | С | Slow/medium pad I/O<br>input high voltage                                                     | Hysteresis<br>enabled  | 0.65 V <sub>DDEH</sub> |                    | V <sub>DDEH</sub> +0.3 | V    |

|                    |    | Ρ |                                                                                               | hysteresis<br>disabled | 0.55 V <sub>DDEH</sub> | _                  | V <sub>DDEH</sub> +0.3 |      |

| V <sub>IH_F</sub>  | CC | С | Fast pad I/O input high voltage                                                               | Hysteresis<br>enabled  | 0.65 V <sub>DDE</sub>  |                    | V <sub>DDE</sub> +0.3  | V    |

|                    |    | Ρ |                                                                                               | hysteresis<br>disabled | 0.55 V <sub>DDE</sub>  |                    | V <sub>DDE</sub> +0.3  |      |

| V <sub>IH_LS</sub> | CC | С | Multi-voltage pad I/O<br>input high voltage in                                                | Hysteresis<br>enabled  | 2.5                    | _                  | V <sub>DDEH</sub> +0.3 | V    |

|                    |    | Ρ | low-swing<br>mode <sup>10,11,12,13,14</sup>                                                   | Hysteresis<br>disabled | 2.2                    | —                  | V <sub>DDEH</sub> +0.3 |      |

| V <sub>IH_HS</sub> | CC | С | Multi-voltage pad I/O<br>input high voltage in                                                | Hysteresis<br>enabled  | 0.65 V <sub>DDEH</sub> | —                  | V <sub>DDEH</sub> +0.3 | V    |

|                    |    | Ρ | high-swing mode <sup>15</sup>                                                                 | Hysteresis<br>disabled | 0.55 V <sub>DDEH</sub> | _                  | V <sub>DDEH</sub> +0.3 |      |

| V <sub>OL_S</sub>  | CC | Ρ | Slow/medium<br>multi-voltage pad I/O<br>output low voltage <sup>18,16</sup>                   | _                      | —                      | _                  | 0.2*V <sub>DDEH</sub>  | V    |

| V <sub>OL_F</sub>  | СС | Ρ | Fast pad I/O output low voltage <sup>17,18</sup>                                              | _                      | —                      | _                  | 0.2*V <sub>DDE</sub>   | V    |

| V <sub>OL_LS</sub> | CC | Ρ | Multi-voltage pad I/O<br>output low voltage in<br>low-swing<br>mode <sup>10,11,12,13,17</sup> | I <sub>OL</sub> = 2 mA | _                      |                    | 0.6                    | V    |

| V <sub>OL_HS</sub> | CC | Р | Multi-voltage pad I/O<br>output low voltage in<br>high-swing mode <sup>17</sup>               | _                      | —                      | _                  | 0.2 V <sub>DDEH</sub>  | V    |

| V <sub>OH_S</sub>  | CC | Ρ | Slow/medium pad I/O<br>output high<br>voltage <sup>18,16</sup>                                |                        | 0.8 V <sub>DDEH</sub>  | _                  | _                      | V    |

| V <sub>OH_F</sub>  | CC | Ρ | Fast pad I/O output<br>high voltage <sup>17,18</sup>                                          | _                      | 0.8 V <sub>DDE</sub>   |                    | _                      | V    |

| Table 22. DC electrical s | pecifications <sup>1</sup> | (continued) |

|---------------------------|----------------------------|-------------|

|---------------------------|----------------------------|-------------|

#### **Electrical characteristics**

| Symbol                                            |    | с | Parameter                                                                                      | Conditions                            |                         | Value <sup>2</sup> |     | Unit |

|---------------------------------------------------|----|---|------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------|--------------------|-----|------|

| Symbol                                            |    | C | Farameter                                                                                      | Conditions                            | min                     | typ                | max |      |

| V <sub>OH_LS</sub>                                | CC | Ρ | Multi-voltage pad I/O<br>output high voltage in<br>low-swing<br>mode <sup>10,11,12,13,17</sup> | I <sub>OH_LS</sub>                    | 2.1                     | _                  | 3.7 | V    |

| V <sub>OH_HS</sub>                                | СС | Ρ | Multi-voltage pad I/O<br>output high voltage in<br>high-swing mode <sup>17</sup>               | _                                     | 0.8 V <sub>DDEH</sub>   | _                  | _   | V    |

| V <sub>HYS_S</sub>                                | CC | С | Slow/medium/multi-vol<br>tage I/O input<br>hysteresis                                          | _                                     | 0.1 * V <sub>DDEH</sub> | _                  | _   | V    |

| V <sub>HYS_F</sub>                                | СС | С | Fast I/O input<br>hysteresis                                                                   | —                                     | 0.1 * V <sub>DDE</sub>  | _                  | _   | V    |

| V <sub>HYS_LS</sub>                               | CC | С | Low-Swing-Mode<br>Multi-Voltage I/O Input<br>Hysteresis                                        | hysteresis<br>enabled                 | 0.25                    | _                  | _   | V    |

| I <sub>DD</sub> +I <sub>DDPLL</sub> <sup>19</sup> | СС | Ρ | Operating current<br>1.2 V supplies                                                            | V <sub>DD</sub> = 1.32 V,<br>80 MHz   | —                       | —                  | 195 | mA   |

|                                                   | СС | Ρ |                                                                                                | V <sub>DD</sub> = 1.32 V,<br>60 MHz   | —                       | _                  | 135 |      |

|                                                   | СС | Ρ |                                                                                                | V <sub>DD</sub> = 1.32 V,<br>40 MHz   | _                       | _                  | 98  |      |

| I <sub>DDSTBY</sub>                               | CC | Т | Operating current 1 V                                                                          | T <sub>J</sub> = 25 <sup>o</sup> C    | —                       | _                  | 80  | μA   |

|                                                   | CC | Т | supplies                                                                                       | T <sub>J</sub> = 55 <sup>o</sup> C    | —                       | _                  | 100 | μA   |

| IDDSTBY150                                        | CC | Ρ | Operating current                                                                              | Т <sub>Ј</sub> =150 <sup>о</sup> С    | —                       | _                  | 700 | μA   |

| IDDSLOW                                           | CC | Р | V <sub>DD</sub> low-power mode                                                                 | Slow mode <sup>20</sup>               | —                       | _                  | 50  | mA   |

| IDDSTOP                                           |    | С | operating current @<br>1.32 V                                                                  | Stop mode <sup>21</sup>               | —                       | _                  | 50  |      |

| I <sub>DD33</sub>                                 | СС | Т | Operating current<br>3.3 V supplies @<br>80 MHz                                                | V <sub>RC33</sub> <sup>4,22</sup>     | -                       | _                  | 70  | mA   |

| I <sub>DDA</sub>                                  | СС | Ρ | Operating current                                                                              | V <sub>DDA</sub>                      |                         | _                  | 30  | mA   |

| I <sub>REF</sub><br>I <sub>DDREG</sub>            |    | Ρ | 5.0 V supplies @<br>80 MHz                                                                     | Analog<br>reference<br>supply current | _                       | —                  | 1.0 |      |

|                                                   |    | С |                                                                                                | V <sub>DDREG</sub>                    | —                       | _                  | 70  | 1    |

Table 22. DC electrical specifications<sup>1</sup> (continued)

- <sup>8</sup> V<sub>FLASH</sub> is only available in the calibration package.

- <sup>9</sup> Regulator is functional, with derated performance, with supply voltage down to 4.0 V.

- <sup>10</sup> Multi-voltage pads (type pad\_multv\_hv) must be supplied with a power supply between 4.75 V and 5.25 V.

- <sup>11</sup> The slew rate (SRC) setting must be 0b11 when in low-swing mode.

- <sup>12</sup> While in low-swing mode there are no restrictions in transitioning to high-swing mode.

- <sup>13</sup> Pin in low-swing mode can accept a 5 V input.

- <sup>14</sup> Values are pending characterization.

- <sup>15</sup> Pin in low-swing mode can accept a 5 V input.

- <sup>16</sup> Characterization based capability:

- IOH\_S = {6, 11.6} mA and IOL\_S = {9.2, 17.7} mA for {slow, medium} I/O with VDDEH=4.5 V;

- IOH\_S = {2.8, 5.4} mA and IOL\_S = {4.2, 8.1} mA for {slow, medium} I/O with VDDEH=3.0 V

- <sup>17</sup> Characterization based capability:

IOH\_F = {12, 20, 30, 40} mA and IOL\_F = {24, 40, 50, 65} mA for {00, 01,10, 11} drive mode with VDDE=3.0 V; IOH\_F = {7, 13, 18, 25} mA and IOL\_F = {18, 30, 35, 50} mA for {00, 01, 10, 11} drive mode with VDDE=2.25 V; IOH\_F = {3, 7, 10, 15} mA and IOL\_F = {12, 20, 27, 35} mA for {00, 01, 10, 11} drive mode with VDDE=1.62 V <sup>18</sup> All VOL/VOH values 100% tested with ± 2 mA load.

- <sup>19</sup> Run mode as follows:

- System clock = 40/60/80 MHz + FM 2% Code executed from flash memory ADC0 at 16 MHz with DMA enabled ADC1 at 8 MHz eMIOS pads toggle in PWM mode with a rate between 100 kHz and 500 kHz eTPU pads toggle in PWM mode with a rate between 10 kHz and 500 kHz CAN configured for a bit rate of 500 kHz

- DSPI configured in master mode with a bit rate of 2 MHz

- eSCI transmission configured with a bit rate of 100 kHz

- <sup>20</sup> Bypass mode, system clock at 1 MHz (using system clock divider), PLL shut down, CPU running simple executive code, 4 x ADC conversion every 10 ms, 2 × PWM channels at 1 kHz, all other modules stopped.

- <sup>21</sup> Bypass mode, system clock at 1 MHz (using system clock divider), CPU stopped, PIT running, all other modules stopped.

- <sup>22</sup> When using the internal regulator only, a bypass capacitor should be connected to this pin. External circuits should not be powered by the internal regulator. The internal regulator can be used as a reference for an external debugger.

- <sup>23</sup> Power requirements for each I/O segment are dependent on the frequency of operation and load of the I/O pins on a particular I/O segment, and the voltage of the I/O segment. See Table 23 for values to calculate power dissipation for specific operation. The total power consumption of an I/O segment is the sum of the individual power consumptions for each pin on the segment.

- $^{24}$  Absolute value of current, measured at  $V_{IL}$  and  $V_{IH}.$

- <sup>25</sup> Weak pull up/down inactive. Measured at V<sub>DDE</sub> = 3.6 V and V<sub>DDEH</sub> = 5.25 V. Applies to pad types: fast (pad\_fc).

- <sup>26</sup> Maximum leakage occurs at maximum operating temperature. Leakage current decreases by approximately one-half for each 8 to 12 °C, in the ambient temperature range of 50 to 125 °C. Applies to pad types: pad a and pad ae.

- <sup>27</sup> Applies to CLKOUT, external bus pins, and Nexus pins.

- $^{28}$  Applies to the FCK, SDI, SDO, and  $\overline{\text{SDS}}$  pins.

- <sup>29</sup> This programmable option applies only to eQADC differential input channels and is used for biasing and sensor diagnostics.

- <sup>30</sup> When the pull-up and pull-down of the same nominal 200 KΩ or 100 KΩ value are both enabled, assuming no interference from external devices, the resulting pad voltage will be  $0.5*V_{DDE} \pm 2.5\%$

### **Electrical characteristics**

| Pad<br>Type | Symb    | ol | с | Period<br>(ns) | Load <sup>2</sup><br>(pF) | V <sub>RC33</sub><br>(V) | V <sub>DDE</sub><br>(V) | Drive<br>Select | I <sub>DD33</sub> Avg<br>(μΑ) | Ι <sub>DD33</sub> RMS<br>(μΑ) |

|-------------|---------|----|---|----------------|---------------------------|--------------------------|-------------------------|-----------------|-------------------------------|-------------------------------|

|             |         | СС | D | 10             | 50                        | 3.6                      | 3.6                     | 11              | 2.35                          | 6.12                          |

|             |         | СС | D | 10             | 30                        | 3.6                      | 3.6                     | 10              | 1.75                          | 4.3                           |

|             |         | СС | D | 10             | 20                        | 3.6                      | 3.6                     | 01              | 1.41                          | 3.43                          |

| Fast        |         | СС | D | 10             | 10                        | 3.6                      | 3.6                     | 00              | 1.06                          | 2.9                           |

| 1 431       | IDRV_FC | СС | D | 10             | 50                        | 3.6                      | 1.98                    | 11              | 1.75                          | 4.56                          |

|             |         | СС | D | 10             | 30                        | 3.6                      | 1.98                    | 10              | 1.32                          | 3.44                          |

|             |         | СС | D | 10             | 20                        | 3.6                      | 1.98                    | 01              | 1.14                          | 2.95                          |

|             |         | СС | D | 10             | 10                        | 3.6                      | 1.98                    | 00              | 0.95                          | 2.62                          |

### Table 25. V<sub>RC33</sub> pad average DC current<sup>1</sup>

These are typical values that are estimated from simulation and not tested. Currents apply to output pins only.

<sup>2</sup> All loads are lumped.

## 4.9.2 LVDS pad specifications

LVDS pads are implemented to support the MSC (Microsecond Channel) protocol which is an enhanced feature of the DSPI module. The LVDS pads are compliant with LVDS specifications and support data rates up to 50 MHz.

| #  | Characteristic                                 | Symb                           | ol  | с    | Condition           | Min.<br>Value | Typ.<br>Value | Max.<br>Value | Unit |  |  |  |  |

|----|------------------------------------------------|--------------------------------|-----|------|---------------------|---------------|---------------|---------------|------|--|--|--|--|

|    |                                                |                                | Dat | a Ra | ite                 |               |               |               |      |  |  |  |  |

| 4  | Data Frequency                                 | FLVDSCLK                       | CC  | D    |                     |               | 50            |               | MHz  |  |  |  |  |

|    | Driver Specs                                   |                                |     |      |                     |               |               |               |      |  |  |  |  |

| 5  | Differential output voltage                    | V <sub>OD</sub> <sup>3</sup>   | CC  | Ρ    | SRC=0b00 or<br>0b11 | 150           |               | 430           | mV   |  |  |  |  |

|    |                                                |                                | CC  | Р    | SRC=0b01            | 90            |               | 340           |      |  |  |  |  |

|    |                                                |                                | CC  | Р    | SRC=0b10            | 155           |               | 480           |      |  |  |  |  |

| 6  | Common mode voltage<br>(LVDS), V <sub>OS</sub> | V <sub>OS</sub> <sup>3</sup>   | СС  | Ρ    |                     | 0.8           | 1.2           | 1.6           | V    |  |  |  |  |

| 7  | Rise/Fall time                                 | T <sub>R</sub> /T <sub>F</sub> | CC  | D    |                     |               | 2             |               | ns   |  |  |  |  |

| 8  | Propagation delay (Low to High)                | T <sub>PLH</sub>               | CC  | D    |                     |               | 4             |               | ns   |  |  |  |  |

| 9  | Propagation delay (High to Low)                | T <sub>PHL</sub>               | СС  | D    |                     |               | 4             |               | ns   |  |  |  |  |

| 10 | Delay (H/L), sync Mode                         | t <sub>PDSYNC</sub>            | CC  | D    |                     |               | 4             |               | ns   |  |  |  |  |

| 11 | Delay, Z to Normal (High/Low)                  | T <sub>DZ</sub>                | CC  | D    |                     |               | 500           |               | ns   |  |  |  |  |

Table 26. DSPI LVDS pad specification <sup>1, 2</sup>

- <sup>4</sup> Exceeding limit may cause conversion error on stressed channels and on unstressed channels. Transitions within the limit do not affect device reliability or cause permanent damage.

- <sup>5</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values using  $V_{POSCLAMP} = V_{DDA} + 0.5 V$  and  $V_{NEGCLAMP} = -0.3 V$ , then use the larger of the calculated values.

- <sup>6</sup> Condition applies to two adjacent pins at injection limits.

- <sup>7</sup> Performance expected with production silicon.

- <sup>8</sup> All channels have same 10 k $\Omega$  < Rs < 100 k $\Omega$ ; Channel under test has Rs=10 k $\Omega$ ;  $I_{INJ}=I_{INJMAX}$ ,  $I_{INJMIN}$ .

- <sup>9</sup> TUE is tested by averaging 10 samples.

- <sup>10</sup> TUE is tested by averaging three samples.

- <sup>11</sup> These values can be significantly improved by using three samples of averaging. Input frequency of 1 kHz was used as the reference for the Signal to Noise Ratio.

- <sup>12</sup> Variable gain is controlled by setting the PRE\_GAIN bits in the ADC\_ACR1-8 registers to select a gain factor of ×1, ×2, or ×4. Settings are for differential input only. Tested at ×1 gain. Values for other settings are guaranteed by as indicated.

- $^{13}$  At V<sub>RH</sub> V<sub>RL</sub> = 5.12 V, one LSB = 1.25 mV.

- <sup>14</sup> Guaranteed 10-bit monotonicity.

- <sup>15</sup> Voltages between VRL and VRH will not cause damage to the pins. However, they may not be converted accurately if the differential voltage is above the maximum differential voltage. In addition, conversion errors may occur if the common mode voltage of the differential signal violates the Differential Input common mode voltage specification.

# 4.13 Platform flash controller electrical characteristics

| Target Max Frequency<br>(MHz) | APC <sup>2</sup> | RWSC <sup>2</sup> | wwsc |

|-------------------------------|------------------|-------------------|------|

| 21 <sup>3</sup>               | 000              | 000               | 01   |

| 41 <sup>3</sup>               | 001              | 001               | 01   |

| 62 <sup>3</sup>               | 010              | 010               | 01   |

| 82 <sup>3</sup>               | 011              | 011               | 01   |

| All                           | 111              | 111               | 111  |

Table 30. APC, RWSC, WWSC settings vs. frequency of operation<sup>1</sup>

<sup>1</sup> Illegal combinations exist, all entries must be taken from the same row

<sup>2</sup> APC must be equal to RWSC

<sup>3</sup> Maximum Frequency includes FM modulation

# 4.14 Flash memory electrical characteristics

### Table 31. Program and erase specifications

| Symbol                   |   | Parameter                                       | Min Value | Typical<br>Value <sup>1</sup> | Initial<br>Max <sup>2</sup> | Max <sup>3</sup> | Unit |

|--------------------------|---|-------------------------------------------------|-----------|-------------------------------|-----------------------------|------------------|------|

| T <sub>dwprogram</sub>   | Ρ | Double Word (64 bits) Program Time <sup>4</sup> | —         | 22                            | 50                          | 500              | μS   |

| T <sub>16kpperase</sub>  | Ρ | 16 KB Block Pre-program and Erase Time          | —         | 300                           | 500                         | 5000             | ms   |

| T <sub>32kpperase</sub>  | Ρ | 32 KB Block Pre-program and Erase Time          | —         | 400                           | 600                         | 5000             | ms   |

| T <sub>64kpperase</sub>  | Ρ | 64 KB Block Pre-program and Erase Time          | —         | 600                           | 900                         | 5000             | ms   |

| T <sub>128kpperase</sub> | Ρ | 128 KB Block Pre-program and Erase Time         | —         | 800                           | 1300                        | 7500             | ms   |

<sup>1</sup> Typical program and erase times assume nominal supply values and operation at 25 °C. All times are subject to change pending device characterization.

<sup>2</sup> Initial factory condition: < 100 program/erase cycles, 25 °C, typical supply voltage.

<sup>3</sup> The maximum program & erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

<sup>4</sup> Actual hardware programming times. This does not include software overhead.

### **Electrical characteristics**

| Symbo     |   | Parameter                                                                                                                    | Conditions                          | Val     | ue      | Unit   |

|-----------|---|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------|---------|--------|

| Symbo     |   | Falameter                                                                                                                    | conditions                          | Min     | Тур     | onit   |

| P/E       | С | Number of program/erase cycles per block<br>for 16 Kbyte blocks over the operating<br>temperature range (T <sub>J</sub> )    | _                                   | 100,000 | _       | cycles |

| P/E       | С | Number of program/erase cycles per block<br>for 32 and 64 Kbyte blocks over operating<br>temperature range (T <sub>J</sub> ) | _                                   | 10,000  | 100,000 | cycles |

| P/E       | С | Number of program/erase cycles per block<br>for 128 Kbyte blocks over the operating<br>temperature range (T <sub>J</sub> )   | _                                   | 1,000   | 100,000 | cycles |

| Retention | С | Minimum data retention at 85 °C average<br>ambient temperature <sup>1</sup>                                                  | Blocks with 0 – 1,000<br>P/E cycles | 20      |         | years  |

|           |   |                                                                                                                              | Blocks with 10,000 P/E cycles       | 10      | —       | years  |

|           |   |                                                                                                                              | Blocks with 100,000 P/E cycles      | 5       |         | years  |

### Table 32. Flash module life

<sup>1</sup> Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

# 4.15 AC specifications

# 4.15.1 Pad AC specifications

| Name                       |     | с | Output Delay (ns) <sup>3,4</sup><br>Low-to-High /<br>High-to-Low |                | Rise/Fall Edge ( ) <sup>4,5</sup> |                  | Drive Load<br>(pF) | SRC/DSC         |

|----------------------------|-----|---|------------------------------------------------------------------|----------------|-----------------------------------|------------------|--------------------|-----------------|

|                            |     |   | Min                                                              | Max            | Min                               | Max              |                    | MSB,LSB         |

|                            | CC  | D | 4.6/3.7                                                          | 12/12          | 2.2/2.2                           | 7/7              | 50                 | 11 <sup>9</sup> |

|                            | CC  | D | 13/10                                                            | 32/32          | 9/9                               | 22/22            | 200                |                 |

|                            | N/A |   |                                                                  |                |                                   |                  | 10 <sup>10</sup>   |                 |

| Medium <sup>6,7,8</sup>    | СС  | D | 12/13                                                            | 28/34          | 5.6/6                             | 15/15            | 50                 | 01              |

|                            | CC  | D | 23/23                                                            | 52/59          | 11/14                             | 31/31            | 200                |                 |

|                            | CC  | D | 69/71                                                            | 152/165        | 34/35                             | 74/74            | 50                 | 00              |

|                            | CC  | D | 95/90                                                            | 205/220        | 44/51                             | 96/96            | 200                |                 |

|                            | CC  | D | 7.3/5.7                                                          | 19/18          | 4.4/4.3                           | 14/14            | 50                 | 11 <sup>9</sup> |

|                            | CC  | D | 24/19                                                            | 58/58          | 17/15                             | 42/42            | 200                |                 |

|                            | N/A |   |                                                                  |                |                                   | 10 <sup>10</sup> |                    |                 |

| Slow <sup>8,11</sup>       | CC  | D | 26/27                                                            | 61/69          | 13/13                             | 34/34            | 50                 | 01              |

|                            | CC  | D | 49/45                                                            | 115/115        | 27/23                             | 61/61            | 200                |                 |

|                            | CC  | D | 137/142                                                          | 320/330        | 72/74                             | 164/164          | 50                 |                 |

|                            | СС  | D | 182/172                                                          | 420/420        | 90/85                             | 200/200          | 200                |                 |

|                            | CC  | D | 4.1/3.6                                                          | 10.3/8.9       | 3.28/2.98                         | 8/8              | 50                 | 11 <sup>9</sup> |

|                            | СС  | D | 10.4/10.2                                                        | 24.2/23.6      | 12.7/11.54                        | 29/29            | 200                |                 |

|                            | N/A |   |                                                                  |                |                                   | 10 <sup>10</sup> |                    |                 |

| MultiV <sup>12</sup>       | CC  | D | 8.38/6.11                                                        | 16/12.9        | 5.48/4.81                         | 11/11            | 50                 | 01              |

| (High Swing Mode)          | СС  | D | 15.9/13.6                                                        | 31/28.5        | 14.6/13.1                         | 31/31            | 200                |                 |

|                            | CC  | D | 61.7/10.4                                                        | 92.2/24.3      | 42.0/12.2                         | 63/63            | 50                 | 00              |

|                            | СС  | D | 85.5/37.3                                                        | 132.6/<br>78.9 | 57.7/46.4                         | 85/85            | 200                |                 |

| MultiV<br>(Low Swing Mode) | СС  | D | 2.31/2.34                                                        | 7.62/6.33      | 1.26/1.67                         | 7/7              | 30                 | 11 <sup>9</sup> |

| Fast <sup>13</sup>         | N/A |   |                                                                  |                |                                   |                  |                    |                 |

| pad_i_hv <sup>14</sup>     | CC  | D | 0.5/0.5                                                          | 1.9/1.9        | 0.3/0.3                           | 1.5/1.5          | 0.5                | N/A             |

| pull_hv                    | CC  | D | NA                                                               | 6000           |                                   | 5000/5000        | 50                 | N/A             |

<sup>1</sup> These are worst case values that are estimated from simulation and not tested. Values in the table are simulated at  $f_{SYS}$  = 80 MHz,  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDE}$  = 1.62 V to 1.98 V,  $V_{DDEH}$  = 4.5 V to 5.25 V,  $T_A$  =  $T_L$  to  $T_H$ .

<sup>2</sup> TBD: To Be Defined.

| #  | Symb               | ol | С | Characteristic                  | Min. Value       | Max. Value | Unit             |

|----|--------------------|----|---|---------------------------------|------------------|------------|------------------|

| 9  | t <sub>TCYC</sub>  | CC | D | TCK Cycle Time                  | 4 <sup>6,7</sup> | _          | t <sub>CYC</sub> |

| 9a | t <sub>TCYC</sub>  | CC | D | Absolute Minimum TCK Cycle Time | 100 <sup>8</sup> | —          | ns               |

| 10 | t <sub>TDC</sub>   | CC | D | TCK Duty Cycle                  | 40               | 60         | %                |

| 11 | t <sub>NTDIS</sub> | CC | D | TDI Data Setup Time             | 5                | —          | ns               |

| 12 | t <sub>NTDIH</sub> | CC | D | TDI Data Hold Time              | 25               | —          | ns               |

| 13 | t <sub>NTMSS</sub> | CC | D | TMS Data Setup Time             | 5                | —          | ns               |

| 14 | t <sub>NTMSH</sub> | CC | D | TMS Data Hold Time              | 25               | —          | ns               |

| 15 | t <sub>JOV</sub>   | CC | D | TCK Low to TDO Data Valid       | 10               | 20         | ns               |

Table 37. Nexus debug port timing<sup>1</sup> (continued)

<sup>1</sup> All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal. Nexus timing specified at V<sub>DD</sub> = 1.14 V to 1.32 V, V<sub>DDEH</sub> = 4.5 V to 5.25 V with multi-voltage pads programmed to Low-Swing mode, T<sub>A</sub> = TL to TH, and CL = 30 pF with DSC = 0b10.

<sup>2</sup> Achieving the absolute minimum MCKO cycle time may require setting the MCKO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV] depending on the actual system frequency being used.

<sup>3</sup> This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum MCKO period specification.

<sup>4</sup> This may require setting the MCKO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV]) depending on the actual system frequency being used.

<sup>5</sup> MDO,  $\overline{\text{MSEO}}$ , and  $\overline{\text{EVTO}}$  data is held valid until next MCKO low cycle.

<sup>6</sup> Achieving the absolute minimum TCK cycle time may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

- <sup>7</sup> This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum TCK period specification.

- <sup>8</sup> This may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

Figure 13. Nexus output timing

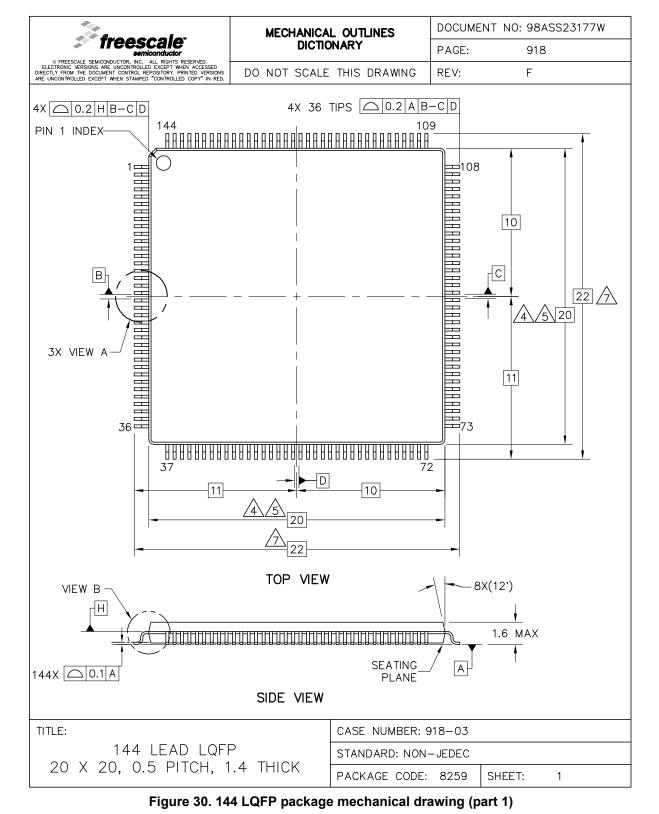

# 5 Packages

- 5.1 Package mechanical data

- 5.1.1 144 LQFP

Packages

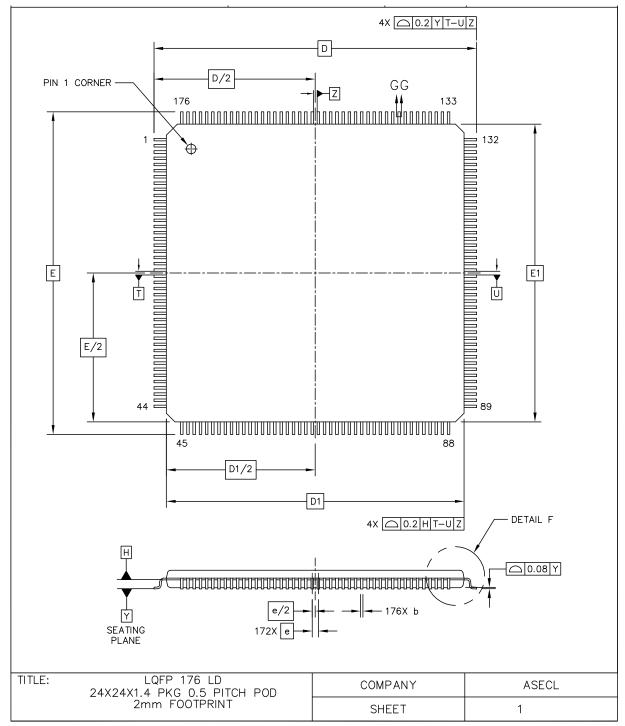

## 5.1.2 176 LQFP

Figure 33. 176 LQFP package mechanical drawing (part 1)

**Ordering information**

# 6 Ordering information

Table 42 shows the orderable part numbers for the MPC5634M series.

| Part Number     | Flash/SRAM<br>(Kbytes) | Package            | Speed<br>(MHz) |

|-----------------|------------------------|--------------------|----------------|

| SPC5632MF2MLQ60 | 768 / 48               | 144 LQFP Pb-free   | 60             |

| SPC5632MF2MLQ40 | 768 / 48               | 144 LQFP Pb-free   | 40             |

| SPC5633MF2MMG80 | 1024 / 64              | 208 MAPBGA Pb-free | 80             |

| SPC5633MF2MLU80 | 1024 / 64              | 176 LQFP Pb-free   | 80             |

| SPC5633MF2MLQ80 | 1024 / 64              | 144 LQFP Pb-free   | 80             |

| SPC5633MF2MMG60 | 1024 / 64              | 208 MAPBGA Pb-free | 60             |

| SPC5633MF2MLU60 | 1024 / 64              | 176 LQFP Pb-free   | 60             |

| SPC5633MF2MLQ60 | 1024 / 64              | 144 LQFP Pb-free   | 60             |

| SPC5633MF2MLQ40 | 1024 / 64              | 144 LQFP Pb-free   | 40             |

| SPC5634MF2MMG80 | 1536 / 94              | 208 MAPBGA Pb-free | 80             |

| SPC5634MF2MLU80 | 1536 / 94              | 176 LQFP Pb-free   | 80             |

| SPC5634MF2MLQ80 | 1536 / 94              | 144 LQFP Pb-free   | 80             |

| SPC5634MF2MMG60 | 1536 / 94              | 208 MAPBGA Pb-free | 60             |

| SPC5634MF2MLU60 | 1536 / 94              | 176 LQFP Pb-free   | 60             |

| SPC5634MF2MLQ60 | 1536 / 94              | 144 LQFP Pb-free   | 60             |

| SPC563M60L3CPBY |                        |                    |                |

| SPC563M60L3CPAY |                        |                    |                |

Table 42. Orderable part number summary

### **Document revision history**

| Revision | Date    | Description of Changes                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 5   | 04/2010 | <ul> <li>Updates to features list:</li> <li>MMU is 16-entry (previously noted as 8-entry)</li> <li>ECSM features include single-bit error correction reporting</li> <li>eTPU2 is object code compatible with previous eTPU versions</li> </ul>                                                                                                          |

|          |         | Updates to feature details:<br>• Programming feature: eTPU2 channel flags can be tested                                                                                                                                                                                                                                                                 |

|          |         | Pinout/ballmap changes:<br>144 pin LQFP package:<br>• Pin 46 is now VDDEH1B (was VDDEH4A)<br>• Pin 61 is now VDDEH6A (was VDDEH4B)                                                                                                                                                                                                                      |

|          |         | <ul> <li>176 pin LQFP package (1.5M devices)</li> <li>Pin 55 is now VDDEH1B (was VDDEH4A)</li> <li>Pin 74 is now VDDEH6A (was VDDEH4B)</li> </ul>                                                                                                                                                                                                       |

|          |         | <ul> <li>176 pin LQFP package (1.5M devices)</li> <li>Pin 55 is now VDDEH1B (was VDDEH4A)</li> <li>Pin 74 is now VDDEH6A (was VDDEH4B)</li> </ul>                                                                                                                                                                                                       |

|          |         | 208 ball BGA package (all devices)<br>Ball N9 changed to VDDEH1/6 (was VDDEH6). In a future revision of the device this may<br>be changed to NC (no connect).                                                                                                                                                                                           |

|          |         | Changes to calibration ball names on devices with 1 MB flash memory:<br>• CAL_MDO0 changed to ALT_MDO0<br>• CAL_MDO1 changed to ALT_MDO1<br>• CAL_MDO2 changed to ALT_MDO2<br>• CAL_MDO3 changed to ALT_MDO3<br>• CAL_MSEO0 changed to ALT_MSEO0<br>• CAL_MSEO1 changed to ALT_EVTI<br>• CAL_EVTI changed to ALT_EVTO<br>• CAL_MCKO changed to ALT_MCKO |

|          |         | <ul> <li>Power/ground segment changes:</li> <li>The following pins are on VDDE7 I/O segment only on the 208-ball BGA package:<br/>ALT_MDO[0:3], ALT_MSEO[0:1], ALT_EVTI, ALT_EVTO, ALT_MCKO.</li> <li>Power segments VDDEH4, VDDEH4A and VDDEH4B have been removed.</li> </ul>                                                                          |

|          |         | CLKOUT power segment is VDDE5 (was VDDE12)                                                                                                                                                                                                                                                                                                              |

|          |         | Thermal characteristics for 176-pin LQFP updated (all parameter values)                                                                                                                                                                                                                                                                                 |

### Table 43. Revision history (continued)

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MPC5634M Rev. 9 05/2012 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and

Power.org logos and related marks are trademarks and service marks licensed by Power.org

© Freescale Semiconductor, Inc. 2008-2012. All rights reserved.