Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | e200z3                                                       |

| Core Size                  | 32-Bit Single-Core                                           |

| Speed                      | 40MHz                                                        |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI, UART/USART                |

| Peripherals                | DMA, POR, PWM, WDT                                           |

| Number of I/O              | 80                                                           |

| Program Memory Size        | 1MB (1M × 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                |                                                              |

| RAM Size                   | 64K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.25V                                                 |

| Data Converters            | A/D 32x12b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 144-LQFP                                                     |

| Supplier Device Package    | 144-LQFP (20x20)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5633mf1mlq40 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

The CPU core has an additional 'Wait for Interrupt' instruction that is used in conjunction with low power STOP mode. When Low Power Stop mode is selected, this instruction is executed to allow the system clock to be stopped. An external interrupt source or the system wake-up timer is used to restart the system clock and allow the CPU to service the interrupt.

# 2.2.2 Crossbar

The XBAR multi-port crossbar switch supports simultaneous connections between three master ports and four slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.

The crossbar allows three concurrent transactions to occur from the master ports to any slave port; but each master must access a different slave. If a slave port is simultaneously requested by more than one master port, arbitration logic selects the higher priority master and grants it ownership of the slave port. All other masters requesting that slave port are stalled until the higher priority master completes its transactions. Requesting masters are treated with equal priority and are granted access to a slave port in round-robin fashion, based upon the ID of the last master to be granted access. The crossbar provides the following features:

- 3 master ports:

- e200z335 core complex Instruction port

- e200z335 core complex Load/Store port

- eDMA

- 4 slave ports

- FLASH

- calibration bus

- SRAM

- Peripheral bridge A/B (eTPU2, eMIOS, SIU, DSPI, eSCI, FlexCAN, eQADC, BAM, decimation filter, PIT, STM and SWT)

- 32-bit internal address, 64-bit internal data paths

## 2.2.3 eDMA

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 32 programmable channels, with minimal intervention from the host processor. The hardware micro architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels. This implementation is utilized to minimize the overall block size. The eDMA module provides the following features:

- All data movement via dual-address transfers: read from source, write to destination

- Programmable source and destination addresses, transfer size, plus support for enhanced addressing modes

- · Transfer control descriptor organized to support two-deep, nested transfer operations

- An inner data transfer loop defined by a "minor" byte transfer count

- An outer data transfer loop defined by a "major" iteration count

- Channel activation via one of three methods:

- Explicit software initiation

- Initiation via a channel-to-channel linking mechanism for continuous transfers

- Peripheral-paced hardware requests (one per channel)

- Support for fixed-priority and round-robin channel arbitration

- Channel completion reported via optional interrupt requests

- 1 interrupt per channel, optionally asserted at completion of major iteration count

- Error termination interrupts are optionally enabled

- Support for scatter/gather DMA processing

intervention. Consequently, for each timer event, the host CPU setup and service times are minimized or eliminated. A powerful timer subsystem is formed by combining the eTPU2 with its own instruction and data RAM. High-level assembler/compiler and documentation allows customers to develop their own functions on the eTPU2.

The eTPU2 includes these distinctive features:

- The Timer Counter (TCR1), channel logic and digital filters (both channel and the external timer clock input [TCRCLK]) now have an option to run at full system clock speed or system clock / 2.

- Channels support unordered transitions: transition 2 can now be detected before transition 1. Related to this enhancement, the transition detection latches (TDL1 and TDL2) can now be independently negated by microcode.

- A new User Programmable Channel Mode has been added: the blocking, enabling, service request and capture characteristics of this channel mode can be programmed via microcode.

- Microinstructions now provide an option to issue Interrupt and Data Transfer requests selected by channel. They can also be requested simultaneously at the same instruction.

- Channel Flags 0 and 1 can now be tested for branching, in addition to selecting the entry point.

- Channel digital filters can be bypassed.

- The Timer Counter (TCR1), channel logic and digital filters (both channel and the external timer clock input [TCRCLK]) now have an option to run at full system clock speed or system clock / 2.

- Channels support unordered transitions: transition 2 can now be detected before transition 1. Related to this enhancement, the transition detection latches (TDL1 and TDL2) can now be independently negated by microcode.

- A new User Programmable Channel Mode has been added: the blocking, enabling, service request and capture characteristics of this channel mode can be programmed via microcode.

- Microinstructions now provide an option to issue Interrupt and Data Transfer requests selected by channel. They can also be requested simultaneously at the same instruction.

- Channel Flags 0 and 1 can now be tested for branching, in addition to selecting the entry point.

- Channel digital filters can be bypassed.

- 32 channels, each channel is associated with one input and one output signal

- Enhanced input digital filters on the input pins for improved noise immunity.

- Identical, orthogonal channels: each channel can perform any time function. Each time function can be assigned to more than one channel at a given time, so each signal can have any functionality.

- Each channel has an event mechanism which supports single and double action functionality in various combinations. It includes two 24-bit capture registers, two 24-bit match registers, 24-bit greater-equal and equal-only comparators

- Input and output signal states visible from the host

- 2 independent 24-bit time bases for channel synchronization:

- First time base clocked by system clock with programmable prescale division from 2 to 512 (in steps of 2), or by output of second time base prescaler

- Second time base counter can work as a continuous angle counter, enabling angle based applications to match angle instead of time

- Both time bases can be exported to the eMIOS timer module

- Both time bases visible from the host

- Event-triggered microengine:

- Fixed-length instruction execution in two-system-clock microcycle

- 14 KB of code memory (SCM)

- 3 KB of parameter (data) RAM (SPRAM)

- Parallel execution of data memory, ALU, channel control and flow control sub-instructions in selected combinations

## Overview

- Queue\_0 can bypass all prioritization, buffering and abort current conversions to start a Queue\_0 conversion a

deterministic time after the queue trigger

- Streaming mode operation of Queue\_0 to execute some commands several times

- Supports software and hardware trigger modes to arm a particular Queue

- Generates interrupt when command coherency is not achieved

- External hardware triggers

- Supports rising edge, falling edge, high level and low level triggers

- Supports configurable digital filter

- Supports four external 8-to-1 muxes which can expand the input channels to 56 channels total

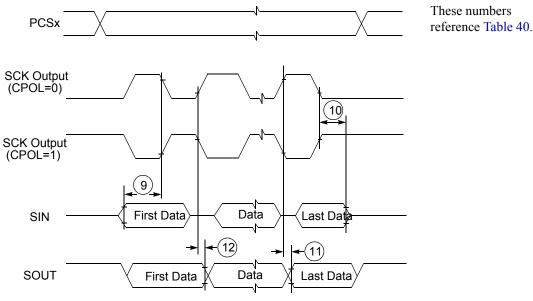

## 2.2.15 DSPI

The deserial serial peripheral interface (DSPI) block provides a synchronous serial interface for communication between the MPC5634M MCU and external devices. The DSPI supports pin count reduction through serialization and deserialization of eTPU and eMIOS channels and memory-mapped registers. The channels and register content are transmitted using a SPI-like protocol. This SPI-like protocol is completely configurable for baud rate, polarity and phase, frame length, chip select assertion, etc. Each bit in the frame may be configured to serialize either eTPU channels, eMIOS channels or GPIO signals. The DSPI can be configured to serialize data to an external device that supports the Microsecond Channel protocol. There are two identical DSPI blocks on the MPC5634M MCU. The DSPI output pins support 5 V logic levels or Low Voltage Differential Signalling (LVDS) according to the Microsecond Channel specification.

The DSPIs have three configurations:

- Serial peripheral interface (SPI) configuration where the DSPI operates as an up to 16-bit SPI with support for queues

- Enhanced deserial serial interface (DSI) configuration where DSPI serializes up to 32 bits with three possible sources per bit

- eTPU, eMIOS, new virtual GPIO registers as possible bit source

- Programmable inter-frame gap in continuous mode

- Bit source selection allows microsecond channel downstream with command or data frames up to 32 bits

- Microsecond channel dual receiver mode

- Combined serial interface (CSI) configuration where the DSPI operates in both SPI and DSI configurations interleaving DSI frames with SPI frames, giving priority to SPI frames

For queued operations, the SPI queues reside in system memory external to the DSPI. Data transfers between the memory and the DSPI FIFOs are accomplished through the use of the eDMA controller or through host software.

The DSPI supports these SPI features:

- Full-duplex, synchronous transfers

- Selectable LVDS Pads working at 40 MHz for SOUT and SCK pins

- Master and Slave Mode

- Buffered transmit operation using the TX FIFO with parameterized depth of 4 entries

- Buffered receive operation using the RX FIFO with parameterized depth of 4 entries

- TX and RX FIFOs can be disabled individually for low-latency updates to SPI queues

- Visibility into the TX and RX FIFOs for ease of debugging

- FIFO Bypass Mode for low-latency updates to SPI queues

- Programmable transfer attributes on a per-frame basis:

- Parameterized number of transfer attribute registers (from two to eight)

- Serial clock with programmable polarity and phase

- Various programmable delays:

- PCS to SCK delay

## Overview

- SCK to PCS delay

- Delay between frames

- Programmable serial frame size of 4 to 16 bits, expandable with software control

- Continuously held chip select capability

- 6 Peripheral Chip Selects, expandable to 64 with external demultiplexer

- Deglitching support for up to 32 Peripheral Chip Selects with external demultiplexer

- DMA support for adding entries to TX FIFO and removing entries from RX FIFO:

- TX FIFO is not full (TFFF)

- RX FIFO is not empty (RFDF)

- 6 Interrupt conditions:

- End of queue reached (EOQF)

- TX FIFO is not full (TFFF)

- Transfer of current frame complete (TCF)

- Attempt to transmit with an empty Transmit FIFO (TFUF)

- RX FIFO is not empty (RFDF)

- FIFO Underrun (slave only and SPI mode, the slave is asked to transfer data when the TxFIFO is empty)

- FIFO Overrun (serial frame received while RX FIFO is full)

- Modified transfer formats for communication with slower peripheral devices

- Continuous Serial Communications Clock (SCK)

- Power savings via support for Stop Mode

- Enhanced DSI logic to implement a 32-bit Timed Serial Bus (TSB) configuration, supporting the Microsecond Channel downstream frame format

The DSPIs also support these features unique to the DSI and CSI configurations:

- 2 sources of the serialized data:

- eTPU\_A and eMIOS output channels

- Memory-mapped register in the DSPI

- Destinations for the deserialized data:

- eTPU\_A and eMIOS input channels

- SIU External Interrupt Request inputs

- Memory-mapped register in the DSPI

- Deserialized data is provided as Parallel Output signals and as bits in a memory-mapped register

- Transfer initiation conditions:

- Continuous

- Edge sensitive hardware trigger

- Change in data

- · Pin serialization/deserialization with interleaved SPI frames for control and diagnostics

- Continuous serial communications clock

- Support for parallel and serial chaining of up to four DSPI blocks

## 2.2.16 eSCI

The enhanced serial communications interface (eSCI) allows asynchronous serial communications with peripheral devices and other MCUs. It includes special support to interface to Local Interconnect Network (LIN) slave devices. The eSCI block provides the following features:

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

# 3.5 208 MAPBGA ballmap (MPC5633M only)

Figure 6 shows the 208-pin MAPBGA ballmap for the MPC5633M (1024 KB flash memory) as viewed from above.

|   | 1                | 2       | 3                | 4               | 5               | 6                | 7                    | 8               | 9                     | 10                   | 11                   | 12               | 13              | 14              | 15               | 16               |

|---|------------------|---------|------------------|-----------------|-----------------|------------------|----------------------|-----------------|-----------------------|----------------------|----------------------|------------------|-----------------|-----------------|------------------|------------------|

| А | VSS              | AN9     | AN11             | VDDA1           | VSSA1           | AN1              | AN5                  | VRH             | VRL                   | AN27                 | VSSA0                | AN12-SDS         | ALT_<br>MDO2    | ALT_<br>MDO0    | VRC33            | VSS              |

| в | VDD              | VSS     | AN38             | AN21            | AN0             | AN4              | REFBYPC              | AN22            | AN25                  | AN28                 | VDDA0                | AN13-SDO         | ALT_<br>MDO3    | ALT_<br>MDO1    | VSS              | VDD              |

| с | VSTBY            | VDD     | VSS              | AN17            | AN34            | AN16             | AN3                  | AN7             | AN23                  | AN32                 | AN33                 | AN14-SDI         | AN15<br>FCK     | VSS             | ALT<br>MSEO0     | тск              |

| D | VRC33            | AN39    | VDD              | VSS             | AN18            | AN2              | AN6                  | AN24            | AN30                  | AN31                 | AN35                 | VDDEH7           | VSS             | TMS             | ALT_EVTO         | NIC <sup>1</sup> |

| Е | ETPUA30          | ETPUA31 | NC <sup>2</sup>  | VDD             |                 |                  |                      |                 |                       |                      |                      |                  | VDDE7           | TDI             | ALT<br>EVTI      | ALT_<br>MSEO1    |

| F | ETPUA28          | ETPUA29 | ETPUA26          | NC <sup>2</sup> |                 |                  |                      |                 |                       |                      |                      |                  | VDDEH6          | TDO             | ALT_MCKO         | JCOMP            |

| G | ETPUA24          | ETPUA27 | ETPUA25          | ETPUA21         |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | DSPI_B_<br>SOUT | DSPI_B_<br>PCS3 | DSPI_B_<br>SIN   | DSPI_B_<br>PCS0  |

| н | ETPUA23          | ETPUA22 | ETPUA17          | ETPUA18         |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | NC <sup>2</sup> | DSPI_B_<br>PCS4 | DSPI_B_<br>PCS2  | DSPI_B_<br>PCS1  |

| J | ETPUA20          | ETPUA19 | ETPUA14          | ETPUA13         |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | DSPI_B_<br>PCS5 | SCI_A_TX        | NC <sup>2</sup>  | DSPI_B_<br>SCK   |

| к | ETPUA16          | ETPUA15 | ETPUA7           | VDDEH1          |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | CAN_C_<br>TX    | SCI_A_RX        | RSTOUT           | VDDREG           |

| L | ETPUA12          | ETPUA11 | ETPUA6           | ETPUA0          |                 |                  |                      |                 |                       |                      |                      |                  | SCI_B_TX        | CAN_C_<br>RX    | WKPCFG           | RESET            |

| м | ETPUA10          | ETPUA9  | ETPUA1           | ETPUA5          |                 |                  |                      |                 |                       |                      |                      |                  | SCI_B_RX        | PLLREF          | BOOTCFG1         | VSSPLL           |

| N | ETPUA8           | ETPUA4  | ETPUA0           | VSS             | VDD             | VRC33            | EMIOS2               | EMIOS10         | VDDEH1/6 <sup>3</sup> | EMIOS12              | eTPUA19 <sup>4</sup> | VRC33            | VSS             | VRCCTL          | NIC <sup>1</sup> | EXTAL            |

| Ρ | ETPUA3           | ETPUA2  | VSS              | VDD             | NC <sup>2</sup> | VDDE7            | NIC <sup>1</sup>     | EMIOS8          | eTPUA29 <sup>3</sup>  | eTPUA2 <sup>3</sup>  | eTPUA21 <sup>3</sup> | CAN_A_<br>TX     | VDD             | VSS             | NIC <sup>1</sup> | XTAL             |

| R | NIC <sup>1</sup> | VSS     | VDD              | NC <sup>2</sup> | EMIOS4          | NIC <sup>1</sup> | EMIOS9               | EMIOS11         | EMIOS14               | eTPUA27 <sup>3</sup> | EMIOS23              | CAN_A_<br>RX     | NC <sup>2</sup> | VDD             | VSS              | VDDPLL           |

| т | VSS              | VDD     | NIC <sup>1</sup> | EMIOS0          | NC <sup>2</sup> | GPIO219          | eTPUA25 <sup>3</sup> | NC <sup>2</sup> | NC <sup>2</sup>       | eTPUA4 <sup>3</sup>  | eTPUA13 <sup>3</sup> | NIC <sup>1</sup> | VDDE5           | CLKOUT          | VDD              | VSS              |

<sup>1</sup> Pins marked "NIC" have no internal connection.

<sup>2</sup> Pins marked "NC" may be connected to internal circuitry. Connections to external circuits or other pins on this device can result in unpredictable system behavior or damage.

<sup>3</sup> This ball may be changed to "NC" (no connection) in a future revision.

<sup>4</sup> eTPU output only channel.

Figure 6. 208-pin MAPBGA ballmap (MPC5633M; top view)

34 4

MPC5634M Microcontroller Data Sheet, Rev.

ø

|                                                                  | Function <sup>1</sup>                               | Pad<br>Config.                 | PCR PA             | I/O    | Voltage <sup>4</sup> /                              |                          | Eurotion / State                                            | F           | Pin No.     |                |

|------------------------------------------------------------------|-----------------------------------------------------|--------------------------------|--------------------|--------|-----------------------------------------------------|--------------------------|-------------------------------------------------------------|-------------|-------------|----------------|

| Name                                                             |                                                     | Register<br>(PCR) <sup>2</sup> | Field <sup>3</sup> | Туре   | Pad Type                                            | Reset State <sup>5</sup> | Function / State<br>After Reset <sup>6</sup>                | 144<br>LQFP | 176<br>LQFP | 208 MAPB<br>GA |

| CAL_ADDR[16] <sup>21</sup><br>ALT_MDO[0] <sup>12</sup>           | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | _                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>15</sup>    | MDO /<br>ALT_ADDR <sup>12</sup> /<br>Low                    | _           | 17          | A14            |

| CAL_ADDR[17] <sup>21</sup><br>ALT_MDO[1] <sup>12</sup>           | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | _                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>15</sup>    | ALT_MDO /<br>CAL_ADDR <sup>12</sup> /<br>Low                | _           | 18          | B14            |

| CAL_ADDR[18] <sup>21</sup><br>ALT_MDO[2] <sup>12</sup>           | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>15</sup>    | ALT_MDO /<br>CAL_ADDR <sup>12</sup> /<br>Low                | _           | 19          | A13            |

| CAL_ADDR[19] <sup>21</sup><br>ALT_MDO[3] <sup>12</sup>           | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>15</sup>    | ALT_MDO /<br>CAL_ADDR <sup>12</sup> /<br>Low                | _           | 20          | B13            |

| CAL_ADDR[20:27]<br>ALT_MDO[4:11]                                 | Calibration Address Bus<br>Nexus Msg Data Out       | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>Fast                        | O / Low                  | ALT_MDO /<br>CAL_ADDR <sup>16</sup> /<br>Low                | _           | —           | -              |

| CAL_ <u>ADDR[</u> 28] <sup>21</sup><br>ALT_MSEO[0] <sup>12</sup> | Calibration Address Bus<br>Nexus Msg Start/End Out  | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>17</sup>    | ALT_MSEO <sup>16</sup> /<br>CAL_ADDR <sup>17</sup> /<br>Low | _           | 118         | C15            |

| CAL_ <u>ADDR</u> [29] <sup>21</sup><br>ALT_MSEO[1] <sup>12</sup> | Calibration Address Bus<br>Nexus Msg Start/End Out  | PCR[345]                       | -                  | 0<br>0 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low <sup>17</sup>    | ALT_MSEO <sup>16</sup> /<br>CAL_ADDR <sup>17</sup> /<br>Low | _           | 117         | E16            |

| CAL_ <u>ADD</u> R[30] <sup>21</sup><br>ALT_EVTI <sup>12</sup>    | Calibration Address Bus<br>Nexus Event In           | PCR[345]                       | -                  | 0<br>1 | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | 18                       | ALT_EVTI /<br>CAL_ADDR <sup>19</sup>                        | _           | 116         | E15            |

| ALT_EVTO                                                         | Nexus Event Out                                     | PCR[344]                       | -                  | 0      | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low                  | ALT_EVTO /<br>High                                          | _           | 120         | D15            |

| ALT_MCKO                                                         | Nexus Msg Clock Out                                 | PCR[344]                       | -                  | 0      | VDDE12 <sup>13</sup><br>VDDE7 <sup>14</sup><br>Fast | O / Low                  | ALT_MCKO /<br>Enabled                                       | _           | 14          | F15            |

| NEXUSCFG <sup>11</sup>                                           | Nexus/Calibration bus selector                      | -                              | -                  | I      | VDDE12<br>Fast                                      | I / Down                 | NEXUSCFG /<br>Down                                          | -           | —           | _              |

| CAL_CS[0] <sup>11</sup>                                          | Calibration Chip Selects                            | PCR[336]                       | _                  | 0      | VDDE12<br>Fast                                      | O / High                 | CAL_CS / High                                               | _           | -           | _              |

| CAL_CS[2] <sup>11</sup><br>CAL_ADDR[10]                          | Calibration Chip Selects<br>Calibration Address Bus | PCR[338]                       | 11<br>10           | 0<br>0 | VDDE12<br>Fast                                      | O / High                 | CAL_CS / High                                               |             | -           | _              |

Table 2. MPC563xM signal properties (continued)

MPC5634M Microcontroller Data Sheet, Rev. 9

36

Pinout and signal description

|                                                      |                                                     | Pad                                       | PCR PA                       | 1/0           | Malta wa <sup>4</sup> /            |                          | Function / State                               | F           | Pin No.     |                |

|------------------------------------------------------|-----------------------------------------------------|-------------------------------------------|------------------------------|---------------|------------------------------------|--------------------------|------------------------------------------------|-------------|-------------|----------------|

| Name                                                 | Function <sup>1</sup>                               | Config.<br>Register<br>(PCR) <sup>2</sup> | Field <sup>3</sup>           | l/O<br>Type   | Voltage <sup>4</sup> /<br>Pad Type | Reset State <sup>5</sup> | Function / State –<br>After Reset <sup>6</sup> | 144<br>LQFP | 176<br>LQFP | 208 MAPB<br>GA |

| CAL_ <del>CS</del> [3] <sup>11</sup><br>CAL_ADDR[11] | Calibration Chip Selects<br>Calibration Address Bus | PCR[339]                                  | 11<br>10                     | 0<br>0        | VDDE12<br>Fast                     | O / High                 | CAL_CS / High                                  | -           | —           | —              |

| CAL_DATA[0:9] <sup>11</sup>                          | Calibration Data Bus                                | PCR[341]                                  |                              | I/O           | VDDE12<br>Fast                     | – / Up                   | – / Up                                         | —           | —           | —              |

| CAL_DATA[10:15] <sup>11</sup>                        | Calibration Data Bus                                | PCR[341]                                  |                              | I/O           | VDDE12<br>Fast                     | – / Up                   | – / Up                                         | -           | —           | —              |

| CAL_OE <sup>11</sup>                                 | Calibration Output Enable                           | PCR[342]                                  | _                            | 0             | VDDE12<br>Fast                     | O / High                 | CAL_OE / High                                  | —           | —           | —              |

| CAL_RD_WR <sup>11</sup>                              | Calibration Read/Write                              | PCR[342]                                  | -                            | 0             | VDDE12<br>Fast                     | O / High                 | CAL_RD_ <del>WR</del><br>/High                 | —           | —           | —              |

| CAL_TS_ALE <sup>11</sup>                             | Calibration Transfer Start<br>Address Latch Enable  | PCR[343]                                  | TS=0b1<br>ALE=0b0            | 0<br>0        | VDDE12<br>Fast                     | O / High                 | CAL_TS / High                                  | —           | —           | —              |

| CAL_WE_BE[0:1] <sup>11</sup>                         | Calibration Write Enable<br>Byte Enable             | PCR[342]                                  | -                            | 0             | VDDE12<br>Fast                     | O / High                 | CAL_WE /<br>High                               | —           | —           | —              |

|                                                      |                                                     |                                           |                              | NEX           | US <sup>20</sup>                   |                          |                                                |             |             | •              |

| EVTI <sup>21</sup><br>eTPU_A[2]<br>GPIO[231]         | Nexus Event In<br>eTPU A Ch.<br>GPIO                | PCR[231]                                  | 01<br>10<br>00               | <br>0<br> /0  | VDDEH7<br>Multi-V                  | -/-                      | -/-                                            | 103         | 126         | P10            |

| EVTO <sup>21</sup><br>eTPU_A[4]<br>GPIO[227]         | Nexus Event Out<br>eTPU A Ch.<br>GPIO               | PCR[227]                                  | 01 <sup>22</sup><br>10<br>00 | 0<br>0<br>I/O | VDDEH7<br>Multi-V                  | I / Up                   | I / Up                                         | 106         | 129         | T10            |

| MCKO <sup>21</sup><br>GPIO[219]                      | Nexus Msg Clock Out<br>GPIO                         | PCR[219]                                  | N/A <sup>22</sup><br>00      | 0<br>I/O      | VDDEH7<br>Multi-V                  | -/-                      | -/-                                            | 99          | 122         | T6             |

| MDO[0] <sup>21</sup><br>eTPU_A[13]<br>GPIO[220]      | Nexus Msg Data Out<br>eTPU A Ch.<br>GPIO            | PCR[220]                                  | 01<br>10<br>00               | 0<br>0<br>I/O | VDDEH7<br>Multi-V                  | -/-                      | -/-                                            | 110         | 135         | T11            |

| MDO[1] <sup>21</sup><br>eTPU_A[19]<br>GPIO[221]      | Nexus Msg Data Out<br>eTPU A Ch.<br>GPIO            | PCR[221]                                  | 01 <sup>22</sup><br>10<br>00 | 0<br>0<br>I/O | VDDEH7<br>Multi-V                  | -/-                      | -/-                                            | 111         | 136         | N11            |

| MDO[2] <sup>21</sup><br>eTPU_A[21]<br>GPIO[222]      | Nexus Msg Data Out<br>eTPU A Ch.<br>GPIO            | PCR[222]                                  | 01 <sup>22</sup><br>10<br>00 | 0<br>0<br>I/0 | VDDEH7<br>Multi-V                  | -/-                      | -1-                                            | 112         | 137         | P11            |

37

# MPC5634M Microcontroller Data Sheet, Rev. 9

## Table 2. MPC563xM signal properties (continued)

|                                             |                                                                                    | Pad                                       |                              |               | No. 160                            |                          | Francisco ( Oto to                             | F           | Pin No.     |                |

|---------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------|------------------------------|---------------|------------------------------------|--------------------------|------------------------------------------------|-------------|-------------|----------------|

| Name                                        | Function <sup>1</sup>                                                              | Config.<br>Register<br>(PCR) <sup>2</sup> | PCR PA<br>Field <sup>3</sup> | l/O<br>Type   | Voltage <sup>4</sup> /<br>Pad Type | Reset State <sup>5</sup> | Function / State –<br>After Reset <sup>6</sup> | 144<br>LQFP | 176<br>LQFP | 208 MAPB<br>GA |

| DSPI_B_PCS[5]<br>DSPI_C_PCS[0]<br>GPIO[110] | DSPI_B Periph Chip Select<br>DSPI_C Periph Chip Select<br>GPIO                     | PCR[110]                                  | 01<br>10<br>00               | 0<br>0<br>I/O | VDDEH6b<br>Medium                  | – / Up                   | – / Up                                         | 87          | 104         | J13            |

|                                             |                                                                                    |                                           |                              | eQA           | DC                                 |                          | · · · · ·                                      | ·           |             |                |

| AN[0] <sup>27</sup><br>DAN0+                | Single Ended Analog Input<br>Positive Terminal Diff. Input                         | _                                         | —                            |               | VDDA                               | I /                      | AN[0] /                                        | 143         | 172         | B5             |

| AN[1] <sup>27</sup><br>DAN0-                | Single Ended Analog Input<br>Negative Terminal Diff. Input                         | _                                         | —                            |               | VDDA                               | l / –                    | AN[1] /                                        | 142         | 171         | A6             |

| AN[2] <sup>27</sup><br>DAN1+                | Single Ended Analog Input<br>Positive Terminal Diff. Input                         | -                                         | —                            | l<br>I        | VDDA                               | I / —                    | AN[2] /                                        | 141         | 170         | D6             |

| AN[3] <sup>27</sup><br>DAN1-                | Single Ended Analog Input<br>Negative Terminal Diff. Input                         | -                                         | —                            |               | VDDA                               | I / –                    | AN[3] /                                        | 140         | 169         | C7             |

| AN[4] <sup>27</sup><br>DAN2+                | Single Ended Analog Input<br>Positive Terminal Diff. Input                         | —                                         | —                            |               | VDDA                               | I / –                    | AN[4] /                                        | 139         | 168         | B6             |

| AN[5] <sup>27</sup><br>DAN2-                | Single Ended Analog Input<br>Negative Terminal Diff. Input                         | —                                         | —                            |               | VDDA                               | I / –                    | AN[5] /                                        | 138         | 167         | A7             |

| AN[6] <sup>27</sup><br>DAN3+                | Single Ended Analog Input<br>Positive Terminal Diff. Input                         | —                                         | —                            |               | VDDA                               | I /                      | AN[6] /                                        | 137         | 166         | D7             |

| AN[7] <sup>27</sup><br>DAN3-                | Single Ended Analog Input<br>Negative Terminal Diff. Input                         | —                                         | —                            |               | VDDA                               | I / –                    | AN[7] /                                        | 136         | 165         | C8             |

| AN[8]                                       | See AN[38]-AN[8]-ANW                                                               |                                           |                              | J             | I                                  |                          |                                                | •           |             |                |

| AN[9]<br>ANX                                | Single Ended Analog Input<br>External Multiplexed Analog<br>Input                  | _                                         | _                            |               | VDDA                               | I /                      | AN[9] /                                        | 5           | 5           | A2             |

| AN[10]                                      | See AN[39]-AN[10]-ANY                                                              |                                           |                              |               |                                    |                          |                                                |             |             |                |

| AN[11]<br>ANZ                               | Single Ended Analog Input<br>External Multiplexed Analog<br>Input                  | _                                         | _                            |               | VDDA                               | I /                      | AN[11] / -                                     | 4           | 4           | A3             |

| AN[12]<br>MA[0]<br>ETPU_A[19]<br>SDS        | Single Ended Analog Input<br>Mux Address<br>ETPU_A Ch.<br>eQADC Serial Data Strobe | PCR[215]                                  | 011<br>010<br>100<br>000     | <br>0<br>0    | VDDEH7                             | I /                      | AN[12] / –                                     | 119         | 148         | A12            |

Pinout and signal description

40

|                                                          |                                                        | Pad                                       |                              |                      |                                    |                          |                                                | F           | Pin No.     |                |

|----------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|------------------------------|----------------------|------------------------------------|--------------------------|------------------------------------------------|-------------|-------------|----------------|

| Name                                                     | Function <sup>1</sup>                                  | Config.<br>Register<br>(PCR) <sup>2</sup> | PCR PA<br>Field <sup>3</sup> | l/O<br>Type          | Voltage <sup>4</sup> /<br>Pad Type | Reset State <sup>5</sup> | Function / State —<br>After Reset <sup>6</sup> | 144<br>LQFP | 176<br>LQFP | 208 MAPB<br>GA |

| AN[38]-AN[8]-<br>ANW                                     | Single Ended Analog Input<br>Multiplexed Analog Input  | -                                         | -                            | I                    | VDDA                               | I /                      | AN[38] / –                                     | 9           | 9           | B3             |

| AN[39]-AN[10]-<br>ANY                                    | Single Ended Analog Input<br>Multiplexed Analog Input  | _                                         | —                            | I                    | VDDA                               | l / –                    | AN[39] /                                       | 8           | 8           | D2             |

| VRH                                                      | Voltage Reference High                                 | —                                         | —                            | I                    | VDDA                               | _/_                      | VRH                                            | 134         | 163         | A8             |

| VRL                                                      | Voltage Reference Low                                  | —                                         | —                            | I                    | VSSA0                              | _/_                      | VRL                                            | 133         | 162         | A9             |

| REFBYPC                                                  | Bypass Capacitor Input                                 | —                                         | —                            | I                    | VRL                                | _/_                      | REFBYPC                                        | 135         | 164         | B7             |

|                                                          |                                                        | 1                                         |                              | eTP                  | PU2                                |                          | 1                                              | 1           | 1           |                |

| eTPU_A[0]<br>eTPU_A[12]<br>eTPU_A[19]<br>GPIO[114]       | eTPU_A Ch.<br>eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO         | PCR[114]                                  | 011<br>010<br>100<br>000     | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | – / WKPCFG               | -/WKPCFG                                       | 52          | 61          | L4, N3         |

| eTPU_A[1]<br>eTPU_A[13]<br>GPIO[115]                     | eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO                       | PCR[115]                                  | 01<br>10<br>00               | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | -/WKPCFG                 | – / WKPCFG                                     | 51          | 60          | M3             |

| eTPU_A[2]<br>eTPU_A[14]<br>GPIO[116]                     | eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO                       | PCR[116]                                  | 01<br>10<br>00               | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | -/WKPCFG                 | -/WKPCFG                                       | 50          | 59          | P2             |

| eTPU_A[3]<br>eTPU_A[15]<br>GPIO[117]                     | eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO                       | PCR[117]                                  | 01<br>10<br>00               | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | -/WKPCFG                 | – / WKPCFG                                     | 49          | 58          | P1             |

| eTPU_A[4]<br>eTPU_A[16]<br>GPIO[118]                     | eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO                       | PCR[118]                                  | 01<br>10<br>00               | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | -/WKPCFG                 | – / WKPCFG                                     | 47          | 56          | N2             |

| eTPU_A[5]<br>eTPU_A[17]<br>DSPI_B_SCK_LVDS-<br>GPI0[119] | eTPU_A Ch.<br>eTPU_A Ch.<br>DSPI_B CLOCK LVDS-<br>GPIO | PCR[119]                                  | 001<br>010<br>100<br>000     | I/O<br>O<br>O<br>I/O | VDDEH1b<br>Slow                    | -/WKPCFG                 | – / WKPCFG                                     | 45          | 54          | M4             |

| eTPU_A[6]<br>eTPU_A[18]<br>DSPI_B_SCK_LVDS+<br>GPI0[120] | eTPU_A Ch.<br>eTPU_A Ch.<br>DSPI_B Clock LVDS+<br>GPIO | PCR[120]                                  | 001<br>010<br>100<br>000     | I/O<br>O<br>O<br>I/O | VDDEH1b<br>Medium                  | -/WKPCFG                 | – / WKPCFG                                     | 44          | 53          | L3             |

## Table 2. MPC563xM signal properties (continued)

• B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212-220.

# 4.4 Electromagnetic Interference (EMI) characteristics

| Symbol    | Parameter                                                                                                                             | Conditions                | f <sub>OSC</sub> /f <sub>BUS</sub>                | Frequency        | Level<br>(Typ) | Unit       |                  |    |      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------|------------------|----------------|------------|------------------|----|------|

| Radiated  | V <sub>EME</sub>                                                                                                                      | Configuration, test Frequ |                                                   |                  |                | Oscillator | 150 kHz – 50 MHz | 26 | dBµV |

| Emissions | conditions and EM<br>testing per standard<br>IEC61967-2; Supply<br>Voltage = 5.0V DC,<br>Ambient<br>Temperature =<br>25°C, Worst-case |                           | Frequency = 8<br>MHz;                             | 50–150 MHz       | 24             |            |                  |    |      |

|           |                                                                                                                                       | - ·                       | System Bus                                        | 150–500 MHz      | 24             |            |                  |    |      |

|           |                                                                                                                                       | Frequency = 80<br>MHz;    | 500–1000 MHz                                      | 21               |                |            |                  |    |      |

|           |                                                                                                                                       | ne = Frequency            | IEC Level                                         | К                | —              |            |                  |    |      |

|           |                                                                                                                                       | 25°C, Worst-case          | Modulation                                        |                  |                |            |                  |    |      |

|           |                                                                                                                                       | Orientation               | Oscillator<br>Frequency = 8<br>MHz;<br>System Bus | 150 kHz – 50 MHz | 20             | dBµV       |                  |    |      |

|           |                                                                                                                                       |                           |                                                   |                  | 50–150 MHz     | 19         |                  |    |      |

|           |                                                                                                                                       |                           |                                                   | 150–500 MHz      | 14             |            |                  |    |      |

|           |                                                                                                                                       |                           | Frequency = 80<br>MHz;                            | 500–1000 MHz     | 7              |            |                  |    |      |

|           |                                                                                                                                       | 1% PLL<br>Frequency       | IEC Level                                         | L                | —              |            |                  |    |      |

|           |                                                                                                                                       | Modulation                |                                                   |                  |                |            |                  |    |      |

## Table 11. EMI testing specifications<sup>1</sup>

<sup>1</sup> IEC Classification Level: L = 24dBuV; K = 30dBuV.

# 4.5 Electromagnetic static discharge (ESD) characteristics

| Symbol | Symbol Parameter |                                           | Conditions            | Value | Unit |

|--------|------------------|-------------------------------------------|-----------------------|-------|------|

| —      | SR               | ESD for Human Body Model (HBM)            | —                     | 2000  | V    |

| R1     | SR               | HBM circuit description                   | —                     | 1500  | Ω    |

| С      | SR               |                                           | _                     | 100   | pF   |

| —      | SR               | ESD for field induced charge Model (FCDM) | All pins              | 500   | V    |

|        |                  |                                           | Corner pins           | 750   |      |

| —      | SR               | Number of pulses per pin                  | Positive pulses (HBM) | 1     | —    |

|        |                  |                                           | Negative pulses (HBM) | 1     | —    |

| —      | SR               | Number of pulses                          | —                     | 1     | —    |

## Table 12. ESD ratings<sup>1,2</sup>

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> Device failure is defined as: "If after exposure to ESD pulses, the device does not meet the device specification requirements, which includes the complete DC parametric and functional testing at room temperature and hot temperature."

# 4.6.2 Recommended power transistors

The following NPN transistors are recommended for use with the on-chip voltage regulator controller: ON Semiconductor<sup>TM</sup> BCP68T1 or NJD2873 as well as Philips Semiconductor<sup>TM</sup> BCP68. The collector of the external transistor is preferably connected to the same voltage supply source as the output stage of the regulator.

| Symbol              | Parameter                               | Value                   | Unit |

|---------------------|-----------------------------------------|-------------------------|------|

| h <sub>FE</sub> (β) | DC current gain (Beta)                  | 60 – 550                | _    |

| P <sub>D</sub>      | Absolute minimum power dissipation      | >1.0<br>(1.5 preferred) | W    |

| I <sub>CMaxDC</sub> | Minimum peak collector current          | 1.0                     | А    |

| VCE <sub>SAT</sub>  | Collector-to-emitter saturation voltage | 200–600 <sup>1</sup>    | mV   |

| V <sub>BE</sub>     | Base-to-emitter voltage                 | 0.4–1.0                 | V    |

Table 19. Recommended operating characteristics

<sup>1</sup> Adjust resistor at bipolar transistor collector for 3.3 V/5.0 V to avoid VCE < VCE<sub>SAT</sub>

# 4.7 Power up/down sequencing

There is no power sequencing required among power sources during power up and power down, in order to operate within specification but use of the following sequence is strongly recommended when the internal regulator is bypassed:

$5 \text{ V} \rightarrow 3.3 \text{ V}$  and 1.2 V

This is also the normal sequence when the internal regulator is enabled.

Although there are no power up/down sequencing requirements to prevent issues like latch-up, excessive current spikes, etc., the state of the I/O pins during power up/down varies according to table Table 20 for all pins with fast pads and Table 21 for all pins with medium, slow and multi-voltage pads.<sup>1</sup>

| V <sub>DDE</sub> | V <sub>RC33</sub> | V <sub>DD</sub> | Fast (pad_fc)  |

|------------------|-------------------|-----------------|----------------|

| LOW              | Х                 | Х               | LOW            |

| V <sub>DDE</sub> | LOW               | Х               | HIGH           |

| V <sub>DDE</sub> | V <sub>RC33</sub> | LOW             | HIGH IMPEDANCE |

| V <sub>DDE</sub> | V <sub>RC33</sub> | V <sub>DD</sub> | FUNCTIONAL     |

Table 20. Power sequence pin states for fast pads

| Table 21 Power sequence   | e pin states for medium | , slow and multi-voltage pads |

|---------------------------|-------------------------|-------------------------------|

| Table 21. I Ower Sequence | e pin states for mealum | , slow and multi-voltage paus |

| V <sub>DDEH</sub>     | V <sub>DD</sub> | Medium (pad_msr_hv)<br>Slow (pad_ssr_hv)<br>Multi-voltage (pad_multv_hv) |

|-----------------------|-----------------|--------------------------------------------------------------------------|

| LOW                   | Х               | LOW                                                                      |

| V <sub>DDEH</sub> LOW |                 | HIGH IMPEDANCE                                                           |

| V <sub>DDEH</sub>     | $V_{DD}$        | FUNCTIONAL                                                               |

<sup>1.</sup>If an external 3.3V external regulator is used to supply current to the 1.2V pass transistor and this supply also supplies current for the other 3.3V supplies, then the 5V supply must always be greater than or equal to the external 3.3V supply.

| Symbol                                            |        | с | Parameter                                                                                      | Conditions                            | Value <sup>2</sup>      |     |     | Unit |

|---------------------------------------------------|--------|---|------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------|-----|-----|------|

| Symbol                                            | Gymbol |   | Parameter                                                                                      |                                       | min                     | typ | max |      |

| V <sub>OH_LS</sub>                                | CC     | Ρ | Multi-voltage pad I/O<br>output high voltage in<br>low-swing<br>mode <sup>10,11,12,13,17</sup> | I <sub>OH_LS</sub>                    | 2.1                     | _   | 3.7 | V    |

| V <sub>OH_HS</sub>                                | СС     | Ρ | Multi-voltage pad I/O<br>output high voltage in<br>high-swing mode <sup>17</sup>               |                                       | 0.8 V <sub>DDEH</sub>   | _   | _   | V    |

| V <sub>HYS_S</sub>                                | СС     | С | Slow/medium/multi-vol<br>tage I/O input<br>hysteresis                                          |                                       | 0.1 * V <sub>DDEH</sub> | _   | _   | V    |

| V <sub>HYS_F</sub>                                | СС     | С | Fast I/O input<br>hysteresis                                                                   | —                                     | 0.1 * V <sub>DDE</sub>  | —   | _   | V    |

| V <sub>HYS_LS</sub>                               | CC     | С | Low-Swing-Mode<br>Multi-Voltage I/O Input<br>Hysteresis                                        | hysteresis<br>enabled                 | 0.25                    | —   | _   | V    |

| I <sub>DD</sub> +I <sub>DDPLL</sub> <sup>19</sup> | СС     | Ρ | Operating current<br>1.2 V supplies                                                            | V <sub>DD</sub> = 1.32 V,<br>80 MHz   | —                       | —   | 195 | mA   |

|                                                   | СС     | Ρ | -                                                                                              | V <sub>DD</sub> = 1.32 V,<br>60 MHz   | —                       | —   | 135 |      |

|                                                   | СС     | Ρ |                                                                                                | V <sub>DD</sub> = 1.32 V,<br>40 MHz   | —                       | —   | 98  |      |

| I <sub>DDSTBY</sub>                               | CC     | Т | Operating current 1 V                                                                          | T <sub>J</sub> = 25 <sup>o</sup> C    | —                       | —   | 80  | μA   |

|                                                   | CC     | Т | supplies                                                                                       | T <sub>J</sub> = 55 <sup>o</sup> C    | _                       | _   | 100 | μA   |

| IDDSTBY150                                        | CC     | Р | Operating current                                                                              | Т <sub>Ј</sub> =150 <sup>о</sup> С    | _                       | _   | 700 | μA   |

| IDDSLOW                                           |        |   | V <sub>DD</sub> low-power mode                                                                 | Slow mode <sup>20</sup>               |                         | _   | 50  | mA   |

| IDDSTOP                                           |        | С | operating current @<br>1.32 V                                                                  | Stop mode <sup>21</sup>               | —                       | —   | 50  |      |

| I <sub>DD33</sub>                                 | CC     | Т | Operating current<br>3.3 V supplies @<br>80 MHz                                                | V <sub>RC33</sub> <sup>4,22</sup>     | —                       | —   | 70  | mA   |

| I <sub>DDA</sub>                                  |        | Ρ |                                                                                                | V <sub>DDA</sub>                      | _                       | _   | 30  | mA   |

| I <sub>REF</sub><br>I <sub>DDREG</sub>            |        | Ρ | 5.0 V supplies @<br>80 MHz                                                                     | Analog<br>reference<br>supply current | _                       | —   | 1.0 |      |

|                                                   |        | С |                                                                                                | V <sub>DDREG</sub>                    | —                       | _   | 70  | 1    |

Table 22. DC electrical specifications<sup>1</sup> (continued)

## Table 27. PLLMRFM electrical specifications<sup>1</sup>

| Symbol             |    | с | Parameter                           | Conditions                                                     | Value |                               | Unit               |

|--------------------|----|---|-------------------------------------|----------------------------------------------------------------|-------|-------------------------------|--------------------|

| Symbo              | 01 |   | Faidilleter                         | Conditions                                                     | min   | max                           | Omt                |

| V <sub>ILEXT</sub> | CC | Т | EXTAL input low voltage             | Crystal Mode <sup>14</sup> ,<br>0.65≤Vxtal≤1.25V <sup>15</sup> | —     | Vxtal –<br>0.4                | V                  |

|                    |    | Т |                                     | External Reference <sup>14,</sup><br>16                        | 0     | V <sub>RC33</sub> /2<br>- 0.4 |                    |

| —                  | CC | Т | XTAL load capacitance <sup>12</sup> | 4 MHz                                                          | 5     | 30                            | pF                 |

|                    |    |   |                                     | 8 MHz                                                          | 5     | 26                            |                    |

|                    |    |   |                                     | 12 MHz                                                         | 5     | 23                            |                    |

|                    |    |   |                                     | 16 MHz                                                         | 5     | 19                            |                    |

|                    |    |   |                                     | 20 MHz                                                         | 5     | 16                            |                    |

| t <sub>ipli</sub>  | CC | Р | PLL lock time <sup>12, 17</sup>     | —                                                              | _     | 200                           | μS                 |

| t <sub>dc</sub>    | CC | Т | Duty cycle of reference             | —                                                              | 40    | 60                            | %                  |

| f <sub>LCK</sub>   | CC | Т | Frequency LOCK range                | —                                                              | -6    | 6                             | % f <sub>sys</sub> |

| f <sub>UL</sub>    | CC | Т | Frequency un-LOCK range             | —                                                              | -18   | 18                            | % f <sub>sys</sub> |

| f <sub>CS</sub>    | CC | D | Modulation Depth                    | Center spread                                                  | ±0.25 | ±4.0                          | %f <sub>sys</sub>  |

| f <sub>DS</sub>    |    | D |                                     | Down Spread                                                    | -0.5  | -8.0                          |                    |

| f <sub>MOD</sub>   | CC | D | Modulation frequency <sup>18</sup>  | —                                                              | _     | 100                           | kHz                |

## ( $V_{DDPLL}$ =1.14 V to 1.32 V, $V_{SS}$ = $V_{SSPLL}$ = 0 V, $T_A$ = $T_L$ to $T_H$ ) (continued)

<sup>1</sup> All values given are initial design targets and subject to change.

- <sup>2</sup> Considering operation with PLL not bypassed.

- $^{3}$  f<sub>VCO</sub> is calculated as follows:

- In Legacy Mode  $f_{VCO} = (f_{crystal} / (PREDIV + 1)) * (4 * (MFD + 4))$  In Enhanced Mode fvco =  $(f_{crystal} / (EPREDIV + 1)) * (EMFD + 4)$

- <sup>4</sup> All internal registers retain data at 0 Hz.

- <sup>5</sup> "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self clocked mode.

- 6 Self clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

- 7 f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

- <sup>8</sup> This value is determined by the crystal manufacturer and board design.

- 9 Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via VDDPLL and VSSPLL and variation in crystal oscillator frequency increase the C<sub>IITTER</sub> percentage for a given interval.

- <sup>10</sup> Proper PC board layout procedures must be followed to achieve specifications.

- <sup>11</sup> Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

- <sup>12</sup> This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits. For a 20 MHz crystal the maximum load should be 17 pF.

- <sup>13</sup> Proper PC board layout procedures must be followed to achieve specifications.

- <sup>14</sup> This parameter is guaranteed by design rather than 100% tested.

| Symbol               |    | с | Doromotor                                                                 |                              | Value                    |                          | Unit                 |  |

|----------------------|----|---|---------------------------------------------------------------------------|------------------------------|--------------------------|--------------------------|----------------------|--|

|                      |    |   | Parameter                                                                 |                              | min                      | max                      | Unit                 |  |

| TUE8                 | CC | С | Total unadjusted error (TUE) at 8 MHz <sup>9</sup>                        |                              | -4                       | 4                        | Counts               |  |

| TUE16                | СС | С | Total unadjusted error at 16 MHz <sup>10</sup>                            | )                            | -8                       | 8                        | Counts               |  |

| SNR                  | СС | Т | Signal to Noise Ratio <sup>11</sup>                                       |                              | 55.2                     |                          | dB                   |  |

| THD                  | СС | Т | Total Harmonic Distorsion                                                 |                              | 70.0                     |                          | dB                   |  |

| SFDR                 | СС | Т | Spurious Free Dynamic Range                                               |                              | 65.0                     |                          | dB                   |  |

| SINAD                | СС | Т | Signal to Noise and Distorsion                                            |                              | 55.0                     |                          | dB                   |  |

| ENOB                 | CC | Т | Effective Number of Bits                                                  |                              | 8.8                      |                          | Counts               |  |

| GAINVGA1             | СС | - | Variable gain amplifier accuracy (g                                       | ain=1) <sup>12</sup>         |                          | •                        |                      |  |

|                      | СС | С | INL                                                                       | 8 MHz ADC                    | -4                       | 4                        | Counts <sup>13</sup> |  |

|                      | CC | С |                                                                           | 16 MHz ADC                   | -8                       | 8                        | Counts               |  |

|                      | СС | С | DNL                                                                       | 8 MHz ADC                    | -3 <sup>14</sup>         | 3 <sup>14</sup>          | Counts               |  |

|                      | СС | С |                                                                           | 16 MHz ADC                   | -3 <sup>14</sup>         | 3 <sup>14</sup>          | Counts               |  |

| GAINVGA2             | СС | - | Variable gain amplifier accuracy (gain=2) <sup>12</sup>                   |                              |                          |                          |                      |  |

|                      | СС | D | INL                                                                       | 8 MHz ADC                    | -5                       | 5                        | Counts               |  |

|                      | CC | D |                                                                           | 16 MHz ADC                   | -8                       | 8                        | Counts               |  |

|                      | СС | D | DNL                                                                       | 8 MHz ADC                    | -3                       | 3                        | Counts               |  |

|                      | CC | D |                                                                           | 16 MHz ADC                   | -3                       | 3                        | Counts               |  |

| GAINVGA4             | CC | - | Variable gain amplifier accuracy (gain=4) <sup>12</sup>                   |                              |                          |                          |                      |  |

|                      | СС | D | INL                                                                       | 8 MHz ADC                    | -7                       | 7                        | Counts               |  |

|                      | СС | D |                                                                           | 16 MHz ADC                   | -8                       | 8                        | Counts               |  |

|                      | СС | D | DNL                                                                       | 8 MHz ADC                    | -4                       | 4                        | Counts               |  |

|                      | СС | D |                                                                           | 16 MHz ADC                   | -4                       | 4                        | Counts               |  |

| DIFF <sub>max</sub>  | CC | С | Maximum differential voltage<br>(DANx+ - DANx-) or (DANx                  | PREGAIN set<br>to 1X setting | _                        | (VRH -<br>VRL)/2         | V                    |  |

| DIFF <sub>max2</sub> | CC | С | DANx+)                                                                    | PREGAIN set<br>to 2X setting | _                        | (VRH -<br>VRL)/4         | V                    |  |

| DIFF <sub>max4</sub> | CC | С |                                                                           | PREGAIN set<br>to 4X setting | _                        | (VRH -<br>VRL)/8         | V                    |  |

| DIFF <sub>cmv</sub>  | CC | С | Differential input Common mode<br>voltage (DANx- + DANx+)/2 <sup>15</sup> |                              | (VRH -<br>VRL)/2 -<br>5% | (VRH -<br>VRL)/2 +<br>5% | V                    |  |

Table 29. eQADC conversion specifications (operating) (continued)

<sup>1</sup> Stop mode recovery time is the time from the setting of either of the enable bits in the ADC Control Register to the time that the ADC is ready to perform conversions. Delay from power up to full accuracy = 8 ms.

<sup>2</sup> At V<sub>RH</sub> - V<sub>RL</sub> = 5.12 V, one count = 1.25 mV. Without using pregain.

<sup>3</sup> Below disruptive current conditions, the channel being stressed has conversion values of 0x3FF for analog inputs greater then V<sub>RH</sub> and 0x0 for values less then V<sub>RL</sub>. Other channels are not affected by non-disruptive conditions.

| Symbol    |   | Parameter                                                                                                                                           | Conditions                          | Val    | Unit    |        |  |

|-----------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------|---------|--------|--|

| Symbo     | • | Falameter                                                                                                                                           | contaitions                         | Min    | Тур     | Jint   |  |

| P/E       | С | C       Number of program/erase cycles per block       —         for 16 Kbyte blocks over the operating temperature range (T <sub>J</sub> )       — |                                     |        | _       | cycles |  |

| P/E       | С | Number of program/erase cycles per block<br>for 32 and 64 Kbyte blocks over operating<br>temperature range (T <sub>J</sub> )                        | _                                   | 10,000 | 100,000 | cycles |  |

| P/E       | С | Number of program/erase cycles per block<br>for 128 Kbyte blocks over the operating<br>temperature range (T <sub>J</sub> )                          | _                                   | 1,000  | 100,000 | cycles |  |

| Retention | С | Minimum data retention at 85 °C average<br>ambient temperature <sup>1</sup>                                                                         | Blocks with 0 – 1,000<br>P/E cycles | 20     | _       | years  |  |

|           |   |                                                                                                                                                     | Blocks with 10,000 P/E cycles       | 10     | —       | years  |  |

|           |   |                                                                                                                                                     | Blocks with 100,000 P/E cycles      | 5      | _       | years  |  |

## Table 32. Flash module life

<sup>1</sup> Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

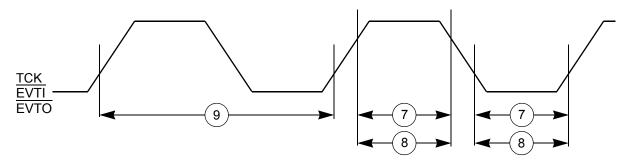

Figure 14. Nexus event trigger and test clock timings

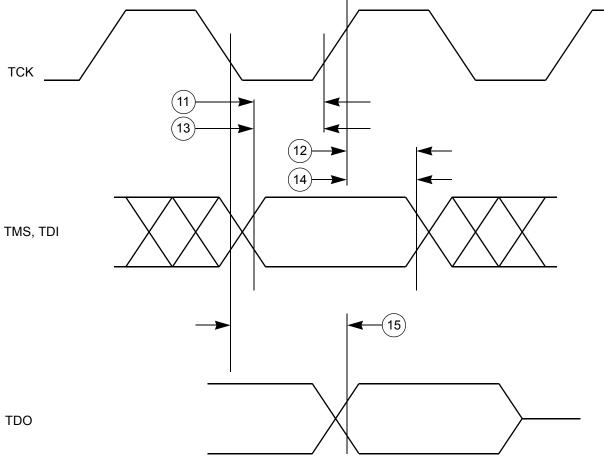

Figure 15. Nexus TDI, TMS, TDO timing

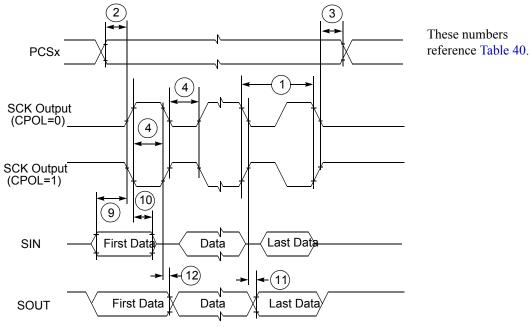

Figure 20. DSPI classic SPI timing – master, CPHA = 0

Packages

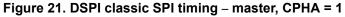

Figure 34. 176 LQFP package mechanical drawing (part 2)

### Packages

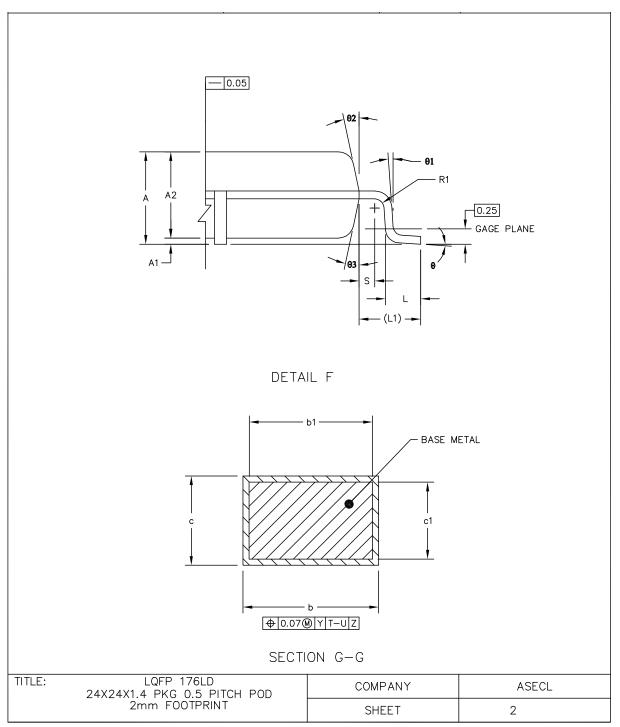

Figure 37. 208 MAPBGA package mechanical drawing (part 2)

| Revision | Date    | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |