Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | e200z3                                                                  |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 60MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI, UART/USART                           |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 80                                                                      |

| Program Memory Size        | 1MB (1M × 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.25V                                                            |

| Data Converters            | A/D 34x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 176-LQFP                                                                |

| Supplier Device Package    | 176-LQFP (24x24)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5633mf1mlu60 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Introd | luction                                |

|---|--------|----------------------------------------|

|   | 1.1    | Document overview                      |

|   | 1.2    | Description                            |

| 2 | Over\  | /iew                                   |

|   | 2.1    | Device comparison                      |

|   | 2.2    | MPC5634M feature details               |

|   |        | 2.2.1 e200z335 core                    |

|   |        | 2.2.2 Crossbar                         |

|   |        | 2.2.3 eDMA                             |

|   |        | 2.2.4 Interrupt controller             |

|   |        | 2.2.5 FMPLL                            |

|   |        | 2.2.6 Calibration EBI                  |

|   |        | 2.2.7 SIU                              |

|   |        | 2.2.8 ECSM                             |

|   |        | 2.2.9 Flash                            |

|   |        | 2.2.10 SRAM                            |

|   |        | 2.2.11 BAM15                           |

|   |        | 2.2.12 eMIOS                           |

|   |        | 2.2.13 eTPU2                           |

|   |        | 2.2.14 eQADC                           |

|   |        | 2.2.15 DSPI                            |

|   |        | 2.2.16 eSCI                            |

|   |        | 2.2.17 FlexCAN                         |

|   |        | 2.2.18 System timers                   |

|   |        | 2.2.19 Software Watchdog Timer (SWT)24 |

|   |        | 2.2.20 Debug features                  |

|   | 2.3    | MPC5634M series architecture           |

|   |        | 2.3.1 Block diagram                    |

|   |        | 2.3.2 Block summary                    |

| 3 |        | it and signal description              |

|   | 3.1    | 144 LQFP pinout                        |

|   | 3.2    | 176 LQFP pinout (MPC5634M)             |

|   | 3.3    | 176 LQFP pinout (MPC5633M)             |

|   | 3.4    | 208 MAPBGA ballmap (MPC5634M)          |

|   | 3.5    | 208 MAPBGA ballmap (MPC5633M only)     |

|   | 3.6    | Signal summary                         |

|   | 3.7    | Signal details                         |

| 4 |        | rical characteristics                  |

|   | 4.1    | Parameter classification               |

|   | 4.2  | Maximum ratings                                        |    |

|---|------|--------------------------------------------------------|----|

|   | 4.3  | Thermal characteristics 5                              | 58 |

|   |      | 4.3.1 General notes for specifications at maximum      |    |

|   |      | junction temperature                                   | 30 |

|   | 4.4  | Electromagnetic Interference (EMI) characteristics6    | 32 |

|   | 4.5  | Electromagnetic static discharge (ESD) characteristics | 62 |

|   | 4.6  | Power Management Control (PMC)                         |    |

|   |      | and Power On Reset (POR) electrical specifications . 6 | 33 |

|   |      | 4.6.1 Regulator example                                | 37 |

|   |      | 4.6.2 Recommended power transistors                    | 39 |

|   | 4.7  | Power up/down sequencing                               | 39 |

|   | 4.8  | DC electrical specifications                           | 70 |

|   | 4.9  | I/O Pad current specifications                         | 77 |

|   |      | 4.9.1 I/O pad VRC33 current specifications 7           |    |

|   |      | 4.9.2 LVDS pad specifications                          |    |

|   | 4.10 | Oscillator and PLLMRFM electrical characteristics 8    | 30 |

|   | 4.11 | Temperature sensor electrical characteristics          | 32 |

|   | 4.12 | eQADC electrical characteristics                       | 32 |

|   | 4.13 | Platform flash controller electrical characteristics 8 | 35 |

|   | 4.14 | Flash memory electrical characteristics                | 35 |

|   | 4.15 | AC specifications                                      | 37 |

|   |      | 4.15.1 Pad AC specifications 8                         | 37 |

|   | 4.16 | AC timing                                              |    |

|   |      | 4.16.1 IEEE 1149.1 interface timing 9                  | 90 |

|   |      | 4.16.2 Nexus timing                                    | 93 |

|   |      | 4.16.3 Calibration bus interface timing 9              | 96 |

|   |      | 4.16.4 eMIOS timing 9                                  | 99 |

|   |      | 4.16.5 DSPI timing 9                                   |    |

|   |      | 4.16.6 eQADC SSI timing 10                             | )5 |

| 5 | Pack | ages10                                                 | )6 |

|   | 5.1  | Package mechanical data 10                             |    |

|   |      | 5.1.1 144 LQFP 10                                      |    |

|   |      | 5.1.2 176 LQFP 11                                      |    |

|   |      | 5.1.3 208 MAPBGA                                       |    |

| 6 |      | ring information                                       |    |

| 7 | Docu | ment revision history 11                               | 17 |

|   |      |                                                        |    |

- Four pairs of differential analog input channels

- Full duplex synchronous serial interface to an external device

- Has a free-running clock for use by the external device

- Supports a 26-bit message length

- Transmits a null message when there are no triggered CFIFOs with commands bound for external CBuffers, or when there are triggered CFIFOs with commands bound for external CBuffers but the external CBuffers are full

- Parallel Side Interface to communicate with an on-chip companion module

- Zero jitter triggering for queue 0. (Queue 0 trigger causes current conversion to be aborted and the queued conversions in the CBUFFER to be bypassed. Delay from Trigger to start of conversion is 13 system clocks + 1 ADC clock.)

- eQADC Result Streaming. Generation of a continuous stream of ADC conversion results from a single eQADC command word. Controlled by two different trigger signals; one to define the rate at which results are generated and the other to define the beginning and ending of the stream. Used to digitize waveforms during specific time/angle windows, e.g., engine knock sensor sampling.

- Angular Decimation. The ability of the eQADC to sample an analog waveform in the time domain, perform Finite Impulse Response (FIR) or Infinite Impulse Response (IIR) filtering also in the time domain, but to down sample the results in the angle domain. Resulting in a time domain filtered result at a given engine angle.

- Priority Based CFIFOs

- Supports six CFIFOs with fixed priority. The lower the CFIFO number, the higher its priority. When

commands of distinct CFIFOs are bound for the same CBuffer, the higher priority CFIFO is always served

first.

- Supports software and several hardware trigger modes to arm a particular CFIFO

- Generates interrupt when command coherency is not achieved

- External Hardware Triggers

- Supports rising edge, falling edge, high level and low level triggers

- Supports configurable digital filter

- Supports four external 8-to-1 muxes which can expand the input channel number from  $34^1$  to 59

- Two deserial serial peripheral interface modules (DSPI)

- SPI

- Full duplex communication ports with interrupt and DMA request support

- Supports all functional modes from QSPI subblock of QSMCM (MPC5xx family)

- Support for queues in RAM

- 6 chip selects, expandable to 64 with external demultiplexers

- Programmable frame size, baud rate, clock delay and clock phase on a per frame basis

- Modified SPI mode for interfacing to peripherals with longer setup time requirements

- LVDS option for output clock and data to allow higher speed communication

- Deserial serial interface (DSI)

- Pin reduction by hardware serialization and deserialization of eTPU, eMIOS channels and GPIO

- 32 bits per DSPI module

- Triggered transfer control and change in data transfer control (for reduced EMI)

- Compatible with Microsecond Channel Version 1.0 downstream

- Two enhanced serial communication interface (eSCI) modules

- UART mode provides NRZ format and half or full duplex interface

- eSCI bit rate up to 1 Mbps

- 1. 176-pin and 208-pin packages have 34 input channels; 144-pin package has 32.

- 1. 176-pin and 208-ball packages.

#### Overview

Branch Address adder to minimize delays during change of flow operations. Sequential prefetching is performed to ensure a supply of instructions into the execution pipeline. Branch target prefetching is performed to accelerate taken branches. Prefetched instructions are placed into an instruction buffer capable of holding six instructions.

Branches can also be decoded at the instruction buffer and branch target addresses calculated prior to the branch reaching the instruction decode stage, allowing the branch target to be prefetched early. When a branch is detected at the instruction buffer, a prediction may be made on whether the branch is taken or not. If the branch is predicted to be taken, a target fetch is initiated and its target instructions are placed in the instruction buffer following the branch instruction. Many branches take zero cycle to execute by using branch folding. Branches are folded out from the instruction execution pipe whenever possible. These include unconditional branches and conditional branches with condition codes that can be resolved early.

Conditional branches which are not taken and not folded execute in a single clock. Branches with successful target prefetching which are not folded have an effective execution time of one clock. All other taken branches have an execution time of two clocks. Memory load and store operations are provided for byte, halfword, and word (32-bit) data with automatic zero or sign extension of byte and halfword load data as well as optional byte reversal of data. These instructions can be pipelined to allow effective single cycle throughput. Load and store multiple word instructions allow low overhead context save and restore operations. The load/store unit contains a dedicated effective address adder to allow effective address generation to be optimized. Also, a load-to-use dependency does not incur any pipeline bubbles for most cases.

The Condition Register unit supports the condition register (CR) and condition register operations defined by the Power Architecture. The condition register consists of eight 4-bit fields that reflect the results of certain operations, such as move, integer and floating-point compare, arithmetic, and logical instructions, and provide a mechanism for testing and branching. Vectored and autovectored interrupts are supported by the CPU. Vectored interrupt support is provided to allow multiple interrupt sources to have unique interrupt handlers invoked with no software overhead.

The hardware floating-point unit utilizes the IEEE-754 single-precision floating-point format and supports single-precision floating-point operations in a pipelined fashion. The general purpose register file is used for source and destination operands, thus there is a unified storage model for single-precision floating-point data types of 32 bits and the normal integer type. Single-cycle floating-point add, subtract, multiply, compare, and conversion operations are provided. Divide instructions are multi-cycle and are not pipelined.

The Signal Processing Extension (SPE) Auxiliary Processing Unit (APU) provides hardware SIMD operations and supports a full complement of dual integer arithmetic operation including Multiply Accumulate (MAC) and dual integer multiply (MUL) in a pipelined fashion. The general purpose register file is enhanced such that all 32 of the GPRs are extended to 64 bits wide and are used for source and destination operands, thus there is a unified storage model for 32×32 MAC operations which generate greater than 32-bit results.

The majority of both scalar and vector operations (including MAC and MUL) are executed in a single clock cycle. Both scalar and vector divides take multiple clocks. The SPE APU also provides extended load and store operations to support the transfer of data to and from the extended 64-bit GPRs. This SPE APU is fully binary compatible with e200z6 SPE APU used in MPC5554 and MPC5553.

The CPU includes support for Variable Length Encoding (VLE) instruction enhancements. This enables the classic Power Architecture instruction set to be represented by a modified instruction set made up from a mixture of 16- and 32-bit instructions. This results in a significantly smaller code size footprint without noticeably affecting performance. The Power Architecture instruction set and VLE instruction set are available concurrently. Regions of the memory map are designated as PPC or VLE using an additional configuration bit in each of Table Look-aside Buffers (TLB) entries in the MMU.

The CPU core is enhanced by the addition of two additional interrupt sources; Non-Maskable Interrupt and Critical Interrupt. These two sources are routed directly from package pins, via edge detection logic in the SIU to the CPU, bypassing completely the Interrupt Controller. Once the edge detection logic is programmed, it cannot be disabled, except by reset. The non-maskable Interrupt is, as the name suggests, completely un-maskable and when asserted will always result in the immediate execution of the respective interrupt service routine. The non-maskable interrupt is not guaranteed to be recoverable. The Critical Interrupt is very similar to the non-maskable interrupt, but it can be masked by other exceptional interrupts in the CPU and is guaranteed to be recoverable (code execution may be resumed from where it stopped).

- Auxiliary Output port

- 1 MCKO (message clock out) pin

- 4 MDO (message data out) pins

- $-2 \overline{\text{MSEO}}$  (message start/end out) pins

- $-1 \overline{\text{EVTO}}$  (event out) pin

- Auxiliary input port

- $-1 \overline{\text{EVTI}}$  (event in) pin

- 17-pin Full Port interface in calibration package used on VertiCal boards

- 3.3 V interface

- Auxiliary Output port

- 1 MCKO (message clock out) pin

- 4 (reduced port mode) or 12 (full port mode) MDO (message data out) pins; 8 extra full port pins shared with calibration bus

- 2 MSEO (message start/end out) pins

- $-1 \overline{\text{EVTO}}$  (event out) pin

- Auxiliary input port

- $-1 \overline{\text{EVTI}}$  (event in) pin

- Host processor (e200) development support features

- IEEE-ISTO 5001-2003 standard class 2 compliant

- Program trace via branch trace messaging (BTM). Branch trace messaging displays program flow discontinuities (direct branches, indirect branches, exceptions, etc.), allowing the development tool to interpolate what transpires between the discontinuities. Thus, static code may be traced.

- Watchpoint trigger enable of program trace messaging

- Data Value Breakpoints (JTAG feature of the e200z335 core): allows CPU to be halted when the CPU writes a specific value to a memory location

- 4 data value breakpoints

- CPU only

- Detects 'equal' and 'not equal'

- Byte, half word, word (naturally aligned)

## NOTE

This feature is imprecise due to CPU pipelining.

- Subset of Power Architecture software debug facilities with OnCE block (Nexus class 1 features)

- eTPU development support features

- IEEE-ISTO 5001-2003 standard class 1 compliant for the eTPU

- Nexus based breakpoint configuration and single step support (JTAG feature of the eTPU)

- Run-time access to the on-chip memory map via the Nexus read/write access protocol. This feature supports accesses for run-time internal visibility, calibration variable acquisition, calibration constant tuning, and external rapid prototyping for powertrain automotive development systems.

- All features are independently configurable and controllable via the IEEE 1149.1 I/O port

- Power-on-reset status indication during reset via MDO[0] in disabled and reset modes

# 2.2.20.2 JTAG

The JTAGC (JTAG Controller) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. Testing is performed via a boundary scan technique, as defined in the IEEE 1149.1-2001

|                                                          |                                                          | Pad                                       |                              |                      |                                    |                          |                                                | F           | Pin No.     |                |

|----------------------------------------------------------|----------------------------------------------------------|-------------------------------------------|------------------------------|----------------------|------------------------------------|--------------------------|------------------------------------------------|-------------|-------------|----------------|

| Name                                                     | Function <sup>1</sup>                                    | Config.<br>Register<br>(PCR) <sup>2</sup> | PCR PA<br>Field <sup>3</sup> | l/O<br>Type          | Voltage <sup>4</sup> /<br>Pad Type | Reset State <sup>5</sup> | Function / State —<br>After Reset <sup>6</sup> | 144<br>LQFP | 176<br>LQFP | 208 MAPB<br>GA |

| AN[38]-AN[8]-<br>ANW                                     | Single Ended Analog Input<br>Multiplexed Analog Input    | -                                         | -                            | I                    | VDDA                               | I /                      | AN[38] / –                                     | 9           | 9           | B3             |

| AN[39]-AN[10]-<br>ANY                                    | Single Ended Analog Input<br>Multiplexed Analog Input    | _                                         | —                            | I                    | VDDA                               | l / –                    | AN[39] /                                       | 8           | 8           | D2             |

| VRH                                                      | Voltage Reference High                                   | —                                         | —                            | I                    | VDDA                               | _/_                      | VRH                                            | 134         | 163         | A8             |

| VRL                                                      | Voltage Reference Low                                    | —                                         | —                            | I                    | VSSA0                              | _/_                      | VRL                                            | 133         | 162         | A9             |

| REFBYPC                                                  | Bypass Capacitor Input                                   | —                                         | —                            | I                    | VRL                                | _/_                      | REFBYPC                                        | 135         | 164         | B7             |

|                                                          |                                                          | 1                                         |                              | eTP                  | PU2                                |                          | 1                                              | 1           | 1           |                |

| eTPU_A[0]<br>eTPU_A[12]<br>eTPU_A[19]<br>GPIO[114]       | eTPU_A Ch.<br>eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO           | PCR[114]                                  | 011<br>010<br>100<br>000     | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | – / WKPCFG               | -/WKPCFG                                       | 52          | 61          | L4, N3         |

| eTPU_A[1]<br>eTPU_A[13]<br>GPIO[115]                     | eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO                         | PCR[115]                                  | 01<br>10<br>00               | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | -/WKPCFG                 | – / WKPCFG                                     | 51          | 60          | M3             |

| eTPU_A[2]<br>eTPU_A[14]<br>GPIO[116]                     | eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO                         | PCR[116]                                  | 01<br>10<br>00               | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | -/WKPCFG                 | -/WKPCFG                                       | 50          | 59          | P2             |

| eTPU_A[3]<br>eTPU_A[15]<br>GPIO[117]                     | eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO                         | PCR[117]                                  | 01<br>10<br>00               | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | -/WKPCFG                 | – / WKPCFG                                     | 49          | 58          | P1             |

| eTPU_A[4]<br>eTPU_A[16]<br>GPIO[118]                     | eTPU_A Ch.<br>eTPU_A Ch.<br>GPIO                         | PCR[118]                                  | 01<br>10<br>00               | I/O<br>O<br>I/O      | VDDEH1b<br>Slow                    | -/WKPCFG                 | -/WKPCFG                                       | 47          | 56          | N2             |

| eTPU_A[5]<br>eTPU_A[17]<br>DSPI_B_SCK_LVDS-<br>GPI0[119] | PU_A[17] eTPU_A Ch.<br>PI_B_SCK_LVDS- DSPI_B CLOCK LVDS- |                                           | 001<br>010<br>100<br>000     | I/O<br>O<br>O<br>I/O | VDDEH1b<br>Slow                    | -/WKPCFG                 | – / WKPCFG                                     | 45          | 54          | M4             |

| eTPU_A[6]<br>eTPU_A[18]<br>DSPI_B_SCK_LVDS+<br>GPI0[120] | eTPU_A Ch.<br>eTPU_A Ch.<br>DSPI_B Clock LVDS+<br>GPIO   | PCR[120]                                  | 001<br>010<br>100<br>000     | I/O<br>O<br>O<br>I/O | VDDEH1b<br>Medium                  | -/WKPCFG                 | – / WKPCFG                                     | 44          | 53          | L3             |

# Table 2. MPC563xM signal properties (continued)

# Table 2. MPC563xM signal properties (continued)

|                    |                                            | Pad                                       |                              | I/O           | Voltage <sup>4</sup> / |                          | Eurotion / State                             | Pin No.    |      |                     |  |

|--------------------|--------------------------------------------|-------------------------------------------|------------------------------|---------------|------------------------|--------------------------|----------------------------------------------|------------|------|---------------------|--|

| Name               | Function <sup>1</sup>                      | Config.<br>Register<br>(PCR) <sup>2</sup> | PCR PA<br>Field <sup>3</sup> | Type Pad Type |                        | Reset State <sup>5</sup> | Function / State<br>After Reset <sup>6</sup> | 14<br>LQ   |      |                     |  |

| VSTBY              | Power Supply for Standby RAM               | -                                         | —                            | I             | VSTBY                  | l / –                    | —                                            | 1:         | : 12 | C1                  |  |

| VRC33              | 3.3V Voltage Regulator<br>Bypass Capacitor | —                                         | —                            | 0             | VRC33                  | O / –                    | —                                            | 1:         | 13   | A15, D1,<br>N6, N12 |  |

| VRCCTL             | Voltage Regulator Control<br>Output        | _                                         | —                            | 0             | NA                     | O / –                    | —                                            | 1          | 11   | N14                 |  |

| VDDA <sup>34</sup> | Analog Power Input for eQADC               | _                                         | —                            | I             | VDDA (5.0 V)           | l / –                    | —                                            | 6          | 6    | -                   |  |

| VDDA0              | Analog Power Input for eQADC               | _                                         | —                            | I             | VDDA                   | l / –                    | —                                            | -          |      | B11                 |  |

| VSSA0              | Analog Ground Input for eQADC              | -                                         | —                            | I             | VSSA                   | l / –                    | —                                            | -          |      | A11                 |  |

| VDDA1              | Analog Power Input for eQADC               | _                                         | —                            | I             | VDDA                   | l / –                    | —                                            | -          |      | A4                  |  |

| VSSA1              | Analog Ground Input for eQADC              | _                                         | —                            | I             | VSSA                   | l / –                    | —                                            | -          |      | A5                  |  |

| VSSA <sup>35</sup> | Analog Ground Input for eQADC              | -                                         | —                            | I             | VSSA                   | l / –                    | —                                            | 7          | 7    | -                   |  |

| VDDREG             | Voltage Regulator Supply                   | _                                         | —                            | I             | VDDREG<br>(5.0 V)      | l / –                    | —                                            | 1          | 10   | K16                 |  |

| VDD                | Internal Logic Supply Input                | _                                         | _                            | I             | VDD (1.2 V)            | I <i>/</i> –             | _                                            | 26,<br>86, |      |                     |  |

## Pinout and signal description

| Signal               | Module or Function       | Description                                                                                                    |

|----------------------|--------------------------|----------------------------------------------------------------------------------------------------------------|

| CAL_RD_WR            | Calibration Bus          | RD_WR indicates whether the current transaction is a read access or a write access.                            |

| CAL_TS_ALE           | Calibration Bus          | The Transfer Start signal $(\overline{TS})$ is asserted by the MPC5634M to indicate the start of a transfer.   |

|                      |                          | The Address Latch Enable (ALE) signal is used to demultiplex the address from the data bus.                    |

| CAL_EVTO             | Calibration Bus          | Nexus Event Out                                                                                                |

| CAL_MCKO             | Calibration Bus          | Nexus Message Clock Out                                                                                        |

| NEXUSCFG             | Nexus/Calibration Bus    | Nexus/Calibration Bus selector                                                                                 |

| eMIOS[0:23]          | eMIOS                    | eMIOS I/O channels                                                                                             |

| AN[0:39]             | eQADC                    | Single-ended analog inputs for analog-to-digital converter                                                     |

| FCK                  | eQADC                    | eQADC free running clock for eQADC SSI.                                                                        |

| MA[0:2]              | eQADC                    | These three control bits are output to enable the selection for an external Analog Mux for expansion channels. |

| REFBYPC              | eQADC                    | Bypass capacitor input                                                                                         |

| SDI                  | eQADC                    | Serial data in                                                                                                 |

| SDO                  | eQADC                    | Serial data out                                                                                                |

| SDS                  | eQADC                    | Serial data select                                                                                             |

| VRH                  | eQADC                    | Voltage reference high input                                                                                   |

| VRL                  | eQADC                    | Voltage reference low input                                                                                    |

| SCI_A_RX<br>SCI_B_RX | eSCI_A – eSCI_B          | eSCI receive                                                                                                   |

| SCI_A_TX<br>SCI_B_TX | eSCI_A – eSCI_B          | eSCI transmit                                                                                                  |

| ETPU_A[0:31]         | eTPU                     | eTPU I/O channel                                                                                               |

| CAN_A_TX<br>CAN_C_TX | FlexCan_A –<br>FlexCAN_C | FlexCAN transmit                                                                                               |

| CAN_A_RX<br>CAN_C_RX | FlexCAN_A –<br>FlexCAN_C | FlexCAN receive                                                                                                |

| JCOMP                | JTAG                     | Enables the JTAG TAP controller.                                                                               |

| ТСК                  | JTAG                     | Clock input for the on-chip test and debug logic.                                                              |

| TDI                  | JTAG                     | Serial test instruction and data input for the on-chip test and debug logic.                                   |

| TDO                  | JTAG                     | Serial test data output for the on-chip test logic.                                                            |

| TMS                  | JTAG                     | Controls test mode operations for the on-chip test and debug logic.                                            |

# Table 4. Signal details (continued)

- <sup>8</sup> Internal structures hold the voltage greater than –1.0 V if the injection current limit of 2 mA is met.

- <sup>9</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDEH</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDEH</sub> is within the operating voltage specifications.

- <sup>10</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDE</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDE</sub> is within the operating voltage specifications.

- <sup>11</sup> Total injection current for all pins (including both digital and analog) must not exceed 25 mA.

- <sup>12</sup> Total injection current for all analog input pins must not exceed 15 mA.

- <sup>13</sup> Lifetime operation at these specification limits is not guaranteed.

- <sup>14</sup> Solder profile per CDF-AEC-Q100.

- <sup>15</sup> Moisture sensitivity per JEDEC test method A112.

# 4.3 Thermal characteristics

| Symbo               | ol                                                               | С | Parameter                                            | Conditions              | Value | Unit |

|---------------------|------------------------------------------------------------------|---|------------------------------------------------------|-------------------------|-------|------|

| $R_{\thetaJA}$      | CC                                                               | D | Junction-to-Ambient, Natural Convection <sup>1</sup> | Single layer board – 1s | 43    | °C/W |

| $R_{\thetaJA}$      | CC                                                               | D | Junction-to-Ambient, Natural Convection <sup>2</sup> | Four layer board – 2s2p | 35    | °C/W |

| $R_{\thetaJMA}$     | CC                                                               | D | Junction-to-Ambient (@200 ft/min) <sup>2</sup>       | Single layer board –1s  | 34    | °C/W |

| R <sub>0JMA</sub>   | CC                                                               | D | Junction-to-Ambient (@200 ft/min) <sup>2</sup>       | Four layer board – 2s2p | 29    | °C/W |

| $R_{\theta JB}$     | CC                                                               | D | Junction-to-Board <sup>2</sup>                       |                         | 22    | °C/W |

| R <sub>0JCtop</sub> | CC                                                               | D | Junction-to-Case (Top) <sup>3</sup>                  |                         | 8     | °C/W |

| Ψ <sub>JT</sub>     | CC D Junction-to-Package Top, Natural<br>Convection <sup>4</sup> |   |                                                      |                         | 2     | °C/W |

## Table 8. Thermal characteristics for 144-pin LQFP

<sup>1</sup> Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>2</sup> Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

<sup>3</sup> Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

<sup>4</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

# 4.6 Power Management Control (PMC) and Power On Reset (POR) electrical specifications

|    |        |    | _ |                                                                                                                                                                                                |                   |      |      |      |

|----|--------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|

| ID | Name   |    | С | Parameter                                                                                                                                                                                      | Min               | Тур  | Max  | Unit |

| 1  | Jtemp  | SR | — | Junction temperature                                                                                                                                                                           | -40               | 27   | 150  | °C   |

| 2  | Vddreg | SR | — | PMC 5 V supply voltage VDDREG                                                                                                                                                                  | 4.75 <sup>1</sup> | 5    | 5.25 | V    |

| 3  | Vdd    | SR |   | Core supply voltage 1.2 V VDD when external regulator is used without disabling the internal regulator (PMC unit turned on, LVI monitor active) <sup>2</sup>                                   | 1.26 <sup>3</sup> | 1.3  | 1.32 | V    |

| 3a | _      | SR |   | Core supply voltage 1.2 V VDD when external regulator is used with a disabled internal regulator (PMC unit turned-off, LVI monitor disabled)                                                   | 1.14              | 1.2  | 1.32 | V    |

| 4  | lvdd   | SR | _ | Voltage regulator core supply maximum DC output current <sup>4</sup>                                                                                                                           | 400               | -    | _    | mA   |

| 5  | Vdd33  | SR | _ | Regulated 3.3 V supply voltage when external regulator is used without disabling the internal regulator (PMC unit turned-on, internal 3.3V regulator enabled, LVI monitor active) <sup>5</sup> | 3.3               | 3.45 | 3.6  | V    |

| 5a | _      | SR |   | Regulated 3.3 V supply voltage when external regulator is used with a disabled internal regulator (PMC unit turned-off, LVI monitor disabled)                                                  | 3                 | 3.3  | 3.6  | V    |

| 6  | _      | SR | - | Voltage regulator 3.3 V supply maximum required DC output current                                                                                                                              | 80                | -    | _    | mA   |

## Table 13. PMC Operating conditions and external regulators supply voltage

<sup>1</sup> During start up operation the minimum required voltage to come out of reset state is 4.6 V.

<sup>2</sup> An internal regulator controller can be used to regulate core supply.

<sup>3</sup> The minimum supply required for the part to exit reset and enter in normal run mode is 1.28 V.

<sup>4</sup> The onchip regulator can support a minimum of 400 ma although the worst case core current is 180 ma.

$^5$  An internal regulator can be used to regulate 3.3 V supply.

| Table 14. PM | IC electrical | characteristics |

|--------------|---------------|-----------------|

|--------------|---------------|-----------------|

| ID | Name C |    | С | Parameter                                                         | Min      | Тур   | Max      | Unit       | Notes |

|----|--------|----|---|-------------------------------------------------------------------|----------|-------|----------|------------|-------|

| 1  | Vbg    | СС | С | Nominal bandgap voltage reference                                 | —        | 1.219 | _        | V          |       |

| 1a | _      | СС | Ρ | Untrimmed bandgap<br>reference voltage                            | Vbg–7%   | Vbg   | Vbg+6%   | V          |       |

| 1b |        | СС | Ρ | Trimmed bandgap<br>reference voltage (5 V,<br>27 °C) <sup>1</sup> | Vbg–10mV | Vbg   | Vbg+10mV | V          |       |

| 1c | —      | СС | С | Bandgap reference temperature variation                           | —        | 100   |          | ppm<br>/°C |       |

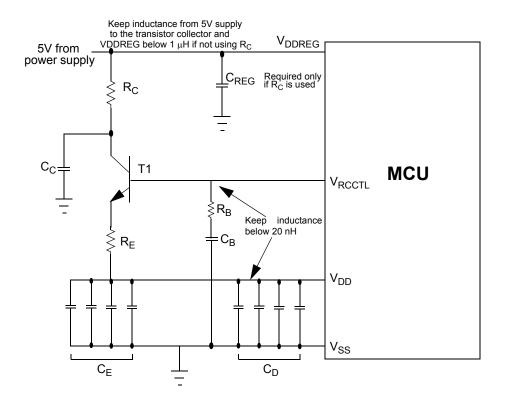

# 4.6.1 Regulator example

## Figure 7. Core voltage regulator controller external components preferred configuration

There are three options for the bypassing and compensation networks for the 1.2V regulator controller. The component values in the following table are the same for all PMC network requirements.

| Component                                     | Symbol           | Minimum | Typical | Maximum | Units | Comment             |

|-----------------------------------------------|------------------|---------|---------|---------|-------|---------------------|

| Pass Transistor                               | T1               |         |         |         |       | NJD2873 or<br>BCP68 |

| VDDREG capacitor                              | C <sub>REG</sub> |         | 10      |         | μF    | X7R,<br>-50%/+35%   |

| Pass transistor Collector<br>bypass capacitor | C <sub>C</sub>   |         |         | 13.3    | μF    | X7R,<br>-50%/+35%   |

| Collector resistor <sup>1</sup>               | R <sub>C</sub>   | 1.1     | —       | 5.6     | Ω     |                     |

Table 15. Required external PMC component values

<sup>1</sup> The collector resistor may not be required. It depends on the allowable power dissipation of the pass transistor (T1).

Table 16, Table 17 and Table 18 show the required component values for the three different options.

# 4.8 DC electrical specifications

Table 22. DC electrical specifications<sup>1</sup>

| Symbol                               |    | с | Parameter                                                     | Conditions             |                        | Value <sup>2</sup> |                        | Unit |

|--------------------------------------|----|---|---------------------------------------------------------------|------------------------|------------------------|--------------------|------------------------|------|

| Symbol                               |    |   | Farameter                                                     | Conditions             | min                    | typ                | max                    | Onit |

| V <sub>DD</sub>                      | SR | — | Core supply voltage                                           | —                      | 1.14                   | _                  | 1.32                   | V    |

| V <sub>DDE</sub>                     | SR | — | I/O supply voltage                                            | _                      | 1.62                   | _                  | 3.6 <sup>3</sup>       | V    |

| V <sub>DDEH</sub>                    | SR | — | I/O supply voltage                                            | _                      | 3.0                    | _                  | 5.25                   | V    |

| V <sub>RC33</sub>                    | SR | — | 3.3 V external voltage <sup>4</sup>                           | —                      | 3.0                    | _                  | 3.6                    | V    |

| V <sub>DDA</sub>                     | SR | — | Analog supply voltage                                         | —                      | 4.75 <sup>5</sup>      | —                  | 5.25                   | V    |

| V <sub>INDC</sub>                    | SR | — | Analog input voltage <sup>6</sup>                             | —                      | V <sub>SSA</sub> – 0.3 | —                  | V <sub>DDA</sub> +0.3  | V    |

| $V_{SS} - V_{SSA}$                   | SR | — | V <sub>SS</sub> differential voltage                          | —                      | -100                   | —                  | 100                    | mV   |

| V <sub>RL</sub>                      | SR | - | Analog reference low voltage                                  | _                      | V <sub>SSA</sub>       | —                  | V <sub>SSA</sub> +0.1  | V    |

| V <sub>RL</sub> – V <sub>SSA</sub>   | SR | — | V <sub>RL</sub> differential voltage                          | _                      | -100                   | _                  | 100                    | mV   |

| V <sub>RH</sub>                      | SR | - | Analog reference high voltage                                 | _                      | V <sub>DDA</sub> – 0.1 | —                  | V <sub>DDA</sub>       | V    |

| V <sub>RH</sub> – V <sub>RL</sub>    | SR | — | V <sub>REF</sub> differential<br>voltage                      | _                      | 4.75                   | —                  | 5.25                   | V    |

| V <sub>DDF</sub>                     | SR | - | Flash operating<br>voltage <sup>7</sup>                       | _                      | 1.14                   | —                  | 1.32                   | V    |

| V <sub>FLASH</sub> <sup>8</sup>      | SR |   | Flash read voltage                                            | —                      | 4.75                   | _                  | 5.25                   | V    |

| V <sub>STBY</sub>                    | SR | — | SRAM standby voltage                                          | Unregulated mode       | 0.95                   | —                  | 1.2                    | V    |

|                                      |    |   |                                                               | Regulated mode         | 2.0                    | —                  | 5.5                    |      |

| V <sub>DDREG</sub>                   | SR | — | Voltage regulator<br>supply voltage <sup>9</sup>              | _                      | 4.75                   | —                  | 5.25                   | V    |

| V <sub>DDPLL</sub>                   | SR | - | Clock synthesizer<br>operating voltage                        | _                      | 1.14                   | _                  | 1.32                   | V    |

| V <sub>SSPLL</sub> – V <sub>SS</sub> | SR | - | V <sub>SSPLL</sub> to V <sub>SS</sub><br>differential voltage | —                      | -100                   | _                  | 100                    | mV   |

| V <sub>IL_S</sub>                    | CC | С | Slow/medium pad I/O<br>input low voltage                      | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | —                  | 0.35*V <sub>DDEH</sub> | V    |

|                                      |    | Ρ |                                                               | hysteresis<br>disabled | V <sub>SS</sub> -0.3   | —                  | 0.40*V <sub>DDEH</sub> |      |

| V <sub>IL_F</sub>                    | CC | С | Fast pad I/O input low voltage                                | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | —                  | 0.35*V <sub>DDE</sub>  | V    |

|                                      |    | Ρ |                                                               | hysteresis<br>disabled | V <sub>SS</sub> -0.3   | —                  | 0.40*V <sub>DDE</sub>  |      |

| Symbol                      |    | с | Parameter                                                         | Conditions               |       | Unit |       |      |  |

|-----------------------------|----|---|-------------------------------------------------------------------|--------------------------|-------|------|-------|------|--|

| Cynisol                     |    |   | Parameter                                                         | Conditions               | min   | typ  | max   |      |  |

| CL                          | CC | D | Load capacitance (fast I/O) <sup>27</sup>                         | DSC(PCR[8:9<br>]) = 0b00 | —     | _    | 10    | pF   |  |

|                             |    | D |                                                                   | DSC(PCR[8:9<br>]) = 0b01 | _     | -    | 20    |      |  |

|                             |    | D |                                                                   | DSC(PCR[8:9<br>]) = 0b10 | _     | _    | 30    |      |  |

|                             |    | D |                                                                   | DSC(PCR[8:9<br>]) = 0b11 |       | _    | 50    |      |  |

| C <sub>IN</sub>             | СС | D | Input capacitance<br>(digital pins)                               | _                        | —     | -    | 7     | pF   |  |

| C <sub>IN_A</sub>           | СС | D | Input capacitance<br>(analog pins)                                | —                        | —     | _    | 10    | pF   |  |

| C <sub>IN_M</sub>           | CC | D | Input capacitance<br>(digital and analog<br>pins <sup>28</sup> )  | _                        | _     | -    | 12    | pF   |  |

| R <sub>PUPD200K</sub>       | CC | Ρ | Weak Pull-Up/Down<br>Resistance <sup>29,30</sup><br>200 kΩ Option | _                        | 130   | -    | 280   | kΩ   |  |

| R <sub>PUPDMATCH</sub>      | CC | С | 200KΩ Option                                                      |                          | -2.5  |      | 2.5   | %    |  |

| R <sub>PUPD100K</sub>       | CC | Ρ | Weak Pull-Up/Down<br>Resistance <sup>29,30</sup><br>100 kΩ Option | _                        | 65    | -    | 140   | kΩ   |  |

| R <sub>PUPDMATCH</sub>      | CC | С | 100KΩ Option                                                      |                          | -2.5  |      | 2.5   | %    |  |

| R <sub>PUPD5K</sub>         | CC | D | Weak Pull-Up/Down<br>Resistance <sup>29</sup><br>5 kΩ Option      | 5 V ± 5%<br>supply       | 1.4   | -    | 7.5   | kΩ   |  |

| $T_A (T_L \text{ to } T_H)$ | SR |   | Operating temperature<br>range - ambient<br>(packaged)            |                          | -40.0 | -    | 125.0 | °C   |  |

|                             | SR | - | Slew rate on power supply pins                                    | —                        | —     | —    | 50    | V/ms |  |

| Table 22. DC electrical specifications <sup>1</sup> | (continued) |

|-----------------------------------------------------|-------------|

|-----------------------------------------------------|-------------|

<sup>1</sup> These specifications are design targets and subject to change per device characterization.

<sup>2</sup> TBD: To Be Defined.

<sup>3</sup> V<sub>DDE</sub> must be lower than V<sub>RC33</sub>, otherwise there is additional leakage on pins supplied by V<sub>DDE</sub>.

- <sup>4</sup> These specifications apply when  $V_{RC33}$  is supplied externally, after disabling the internal regulator ( $V_{DDREG} = 0$ ).

- <sup>5</sup> ADC is functional with 4 V  $\leq$  V<sub>DDA</sub>  $\leq$  4.75 V but with derated accuracy. This means the ADC will continue to function at full speed with no bad behavior, but the accuracy will be degraded.

- <sup>6</sup> Internal structures hold the input voltage less than V<sub>DDA</sub> + 1.0 V on all pads powered by V<sub>DDA</sub> supplies, if the maximum injection current specification is met (3 mA for all pins) and V<sub>DDA</sub> is within the operating voltage specifications.

<sup>7</sup> The V<sub>DDF</sub> supply is connected to V<sub>DD</sub> in the package substrate. This specification applies to calibration package devices only.

- <sup>4</sup> Ratio from 5.5 V pad spec to 5.25 V data sheet.

- <sup>5</sup> Not specified.

- $^{\rm 6}\,$  Low swing mode is not a strong function of  $V_{\rm DDE}.$

# 4.9.1 I/O pad VRC33 current specifications

The power consumption of the VRC33 supply is dependent on the usage of the pins on all I/O segments. The power consumption is the sum of all output pin  $V_{RC33}$  currents for all I/O segments. The output pin  $V_{RC33}$  current can be calculated from Table 24 based on the voltage, frequency, and load on all medium, slow, and multv\_hv pins. The output pin VRC33 current can be calculated from Table 25 based on the voltage, frequency, and load on all fast pins. Use linear scaling to calculate pin currents for voltage, frequency, and load parameters that fall outside the values given in Table 24 and Table 25.

| Pad Type                  | Symbol                    |    |   | Period<br>(ns) | Load <sup>2</sup><br>(pF) | Slew Rate<br>Select | l <sub>DD33</sub> Avg<br>(μA) | I <sub>DD33</sub> RMS<br>(μΑ) |

|---------------------------|---------------------------|----|---|----------------|---------------------------|---------------------|-------------------------------|-------------------------------|

| Slow                      | I <sub>DRV_SSR_HV</sub>   | СС | D | 100            | 50                        | 11                  | 0.8                           | 235.7                         |

|                           |                           | СС | D | 200            | 50                        | 01                  | 0.04                          | 87.4                          |

|                           |                           | СС | D | 800            | 50                        | 00                  | 0.06                          | 47.4                          |

|                           |                           | СС | D | 800            | 200                       | 00                  | 0.009                         | 47                            |

| Medium                    | I <sub>DRV_MSR_HV</sub>   | CC | D | 40             | 50                        | 11                  | 2.75                          | 258                           |

|                           |                           | СС | D | 100            | 50                        | 01                  | 0.11                          | 76.5                          |

|                           |                           | CC | D | 500            | 50                        | 00                  | 0.02                          | 56.2                          |

|                           |                           | CC | D | 500            | 200                       | 00                  | 0.01                          | 56.2                          |

| MultiV <sup>3</sup> (High | I <sub>DRV_MULTV_HV</sub> | CC | D | 40             | 50                        | 11                  | 2.75                          | 258                           |

| Swing Mode)               |                           | CC | D | 100            | 50                        | 01                  | 0.11                          | 76.5                          |

|                           |                           | CC | D | 500            | 50                        | 00                  | 0.02                          | 56.2                          |

|                           |                           | CC | D | 500            | 200                       | 00                  | 0.01                          | 56.2                          |

| MultiV <sup>4</sup> (Low  | I <sub>DRV_MULTV_HV</sub> | CC | D | 40             | 30                        | 11                  | 2.75                          | 258                           |

| Swing Mode)               |                           | CC | D | 100            | 30                        | 11                  | 0.11                          | 76.5                          |

|                           |                           | CC | D | 500            | 30                        | 11                  | 0.02                          | 56.2                          |

|                           |                           | СС | D | 500            | 30                        | 11                  | 0.01                          | 56.2                          |

Table 24. I/O pad V<sub>RC33</sub> average I<sub>DDE</sub> specifications<sup>1</sup>

<sup>1</sup> These are typical values that are estimated from simulation and not tested. Currents apply to output pins only.

<sup>2</sup> All loads are lumped.

<sup>3</sup> Average current is for pad configured as output only.

<sup>4</sup> In low swing mode, multi-voltage pads (pad\_multv\_hv) must operate in highest slew rate setting.

# Table 27. PLLMRFM electrical specifications<sup>1</sup>

| Symbol             |    | с | Parameter                           | Conditions                                                     | Va    | Unit                          |                    |

|--------------------|----|---|-------------------------------------|----------------------------------------------------------------|-------|-------------------------------|--------------------|

|                    |    |   | Faranieter                          | Conditions                                                     | min   | max                           | Unit               |

| V <sub>ILEXT</sub> | CC | Т | EXTAL input low voltage             | Crystal Mode <sup>14</sup> ,<br>0.65≤Vxtal≤1.25V <sup>15</sup> | —     | Vxtal –<br>0.4                | V                  |

|                    |    | Т |                                     | External Reference <sup>14,</sup><br>16                        | 0     | V <sub>RC33</sub> /2<br>- 0.4 |                    |

| —                  | CC | Т | XTAL load capacitance <sup>12</sup> | 4 MHz                                                          | 5     | 30                            | pF                 |

|                    |    |   |                                     | 8 MHz                                                          | 5     | 26                            |                    |

|                    |    |   |                                     | 12 MHz                                                         | 5     | 23                            |                    |

|                    |    |   |                                     | 16 MHz                                                         | 5     | 19                            |                    |

|                    |    |   |                                     | 20 MHz                                                         | 5     | 16                            |                    |

| t <sub>ipli</sub>  | CC | Р | PLL lock time <sup>12, 17</sup>     | —                                                              | _     | 200                           | μS                 |

| t <sub>dc</sub>    | CC | Т | Duty cycle of reference             | —                                                              | 40    | 60                            | %                  |

| f <sub>LCK</sub>   | CC | Т | Frequency LOCK range                | —                                                              | -6    | 6                             | % f <sub>sys</sub> |

| f <sub>UL</sub>    | CC | Т | Frequency un-LOCK range             | —                                                              | -18   | 18                            | % f <sub>sys</sub> |

| f <sub>CS</sub>    | CC | D | Modulation Depth                    | Center spread                                                  | ±0.25 | ±4.0                          | %f <sub>sys</sub>  |

| f <sub>DS</sub>    |    | D |                                     | Down Spread                                                    | -0.5  | -8.0                          |                    |

| f <sub>MOD</sub>   | CC | D | Modulation frequency <sup>18</sup>  | —                                                              | _     | 100                           | kHz                |

## ( $V_{DDPLL}$ =1.14 V to 1.32 V, $V_{SS}$ = $V_{SSPLL}$ = 0 V, $T_A$ = $T_L$ to $T_H$ ) (continued)

<sup>1</sup> All values given are initial design targets and subject to change.

- <sup>2</sup> Considering operation with PLL not bypassed.

- <sup>3</sup>  $f_{VCO}$  is calculated as follows:

- In Legacy Mode  $f_{VCO} = (f_{crystal} / (PREDIV + 1)) * (4 * (MFD + 4))$  In Enhanced Mode fvco =  $(f_{crystal} / (EPREDIV + 1)) * (EMFD + 4)$

- <sup>4</sup> All internal registers retain data at 0 Hz.

- <sup>5</sup> "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self clocked mode.

- 6 Self clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

- 7 f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

- <sup>8</sup> This value is determined by the crystal manufacturer and board design.

- 9 Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via VDDPLL and VSSPLL and variation in crystal oscillator frequency increase the C<sub>IITTER</sub> percentage for a given interval.

- <sup>10</sup> Proper PC board layout procedures must be followed to achieve specifications.

- <sup>11</sup> Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

- <sup>12</sup> This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits. For a 20 MHz crystal the maximum load should be 17 pF.

- <sup>13</sup> Proper PC board layout procedures must be followed to achieve specifications.

- <sup>14</sup> This parameter is guaranteed by design rather than 100% tested.

| Symbol    |   | Parameter                                                                                                                    | Conditions                          | Val     | Unit    |        |

|-----------|---|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------|---------|--------|

|           |   | Falameter                                                                                                                    | contaitions                         | Min     | Тур     |        |

| P/E       | С | Number of program/erase cycles per block<br>for 16 Kbyte blocks over the operating<br>temperature range (T <sub>J</sub> )    | _                                   | 100,000 | _       | cycles |

| P/E       | С | Number of program/erase cycles per block<br>for 32 and 64 Kbyte blocks over operating<br>temperature range (T <sub>J</sub> ) | _                                   | 10,000  | 100,000 | cycles |

| P/E       | С | Number of program/erase cycles per block<br>for 128 Kbyte blocks over the operating<br>temperature range (T <sub>J</sub> )   | _                                   | 1,000   | 100,000 | cycles |

| Retention | С | Minimum data retention at 85 °C average<br>ambient temperature <sup>1</sup>                                                  | Blocks with 0 – 1,000<br>P/E cycles | 20      | _       | years  |

|           |   |                                                                                                                              | Blocks with 10,000 P/E cycles       | 10      | —       | years  |

|           |   |                                                                                                                              | Blocks with 100,000 P/E cycles      | 5       | _       | years  |

## Table 32. Flash module life

<sup>1</sup> Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

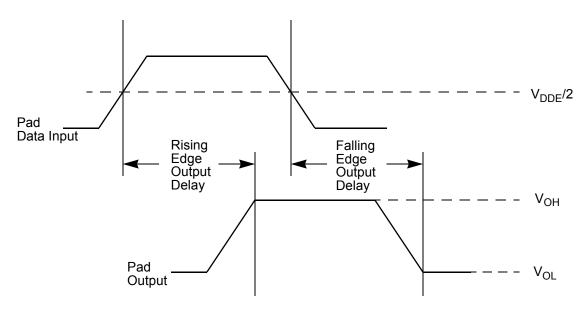

Figure 8. Pad output delay

# 4.16 AC timing

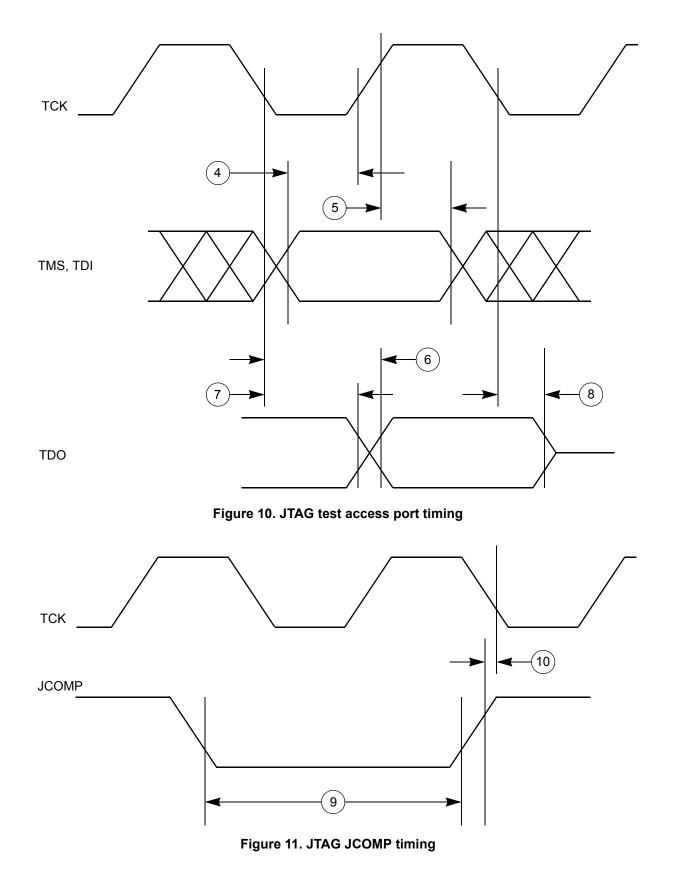

# 4.16.1 IEEE 1149.1 interface timing

# Table 36. JTAG pin AC electrical characteristics<sup>1</sup>

| #  | Symbol                                |    | с | Characteristic                      | Min.<br>Value | Max.<br>Value | Unit |

|----|---------------------------------------|----|---|-------------------------------------|---------------|---------------|------|

| 1  | t <sub>JCYC</sub>                     | CC | D | TCK Cycle Time                      | 100           | —             | ns   |

| 2  | t <sub>JDC</sub>                      | CC | D | TCK Clock Pulse Width               | 40            | 60            | ns   |

| 3  | t <sub>TCKRISE</sub>                  | CC | D | TCK Rise and Fall Times (40% – 70%) | _             | 3             | ns   |

| 4  | t <sub>TMSS,</sub> t <sub>TDIS</sub>  | CC | D | TMS, TDI Data Setup Time            | 5             | _             | ns   |

| 5  | t <sub>TMSH</sub> , t <sub>TDIH</sub> | CC | D | TMS, TDI Data Hold Time             | 25            | _             | ns   |

| 6  | t <sub>TDOV</sub>                     | CC | D | TCK Low to TDO Data Valid           | _             | 23            | ns   |

| 7  | t <sub>TDOI</sub>                     | CC | D | TCK Low to TDO Data Invalid         | 0             | —             | ns   |

| 8  | t <sub>TDOHZ</sub>                    | CC | D | TCK Low to TDO High Impedance       | _             | 20            | ns   |

| 9  | t <sub>JCMPPW</sub>                   | CC | D | JCOMP Assertion Time                | 100           | _             | ns   |

| 10 | t <sub>JCMPS</sub>                    | CC | D | JCOMP Setup Time to TCK Low         | 40            | _             | ns   |

| 11 | t <sub>BSDV</sub>                     | CC | D | TCK Falling Edge to Output Valid    | —             | 50            | ns   |

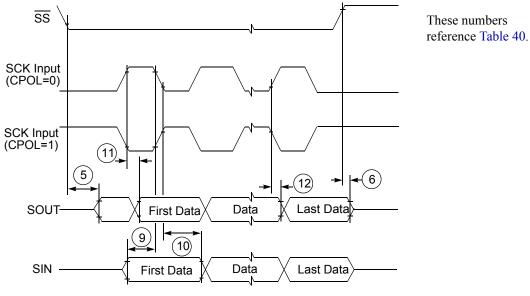

These numbers

reference Table 40.

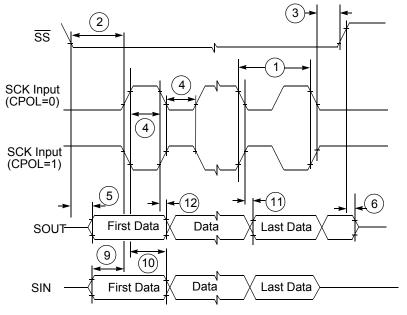

Figure 22. DSPI classic SPI timing – slave, CPHA = 0

Figure 23. DSPI classic SPI timing – slave, CPHA = 1

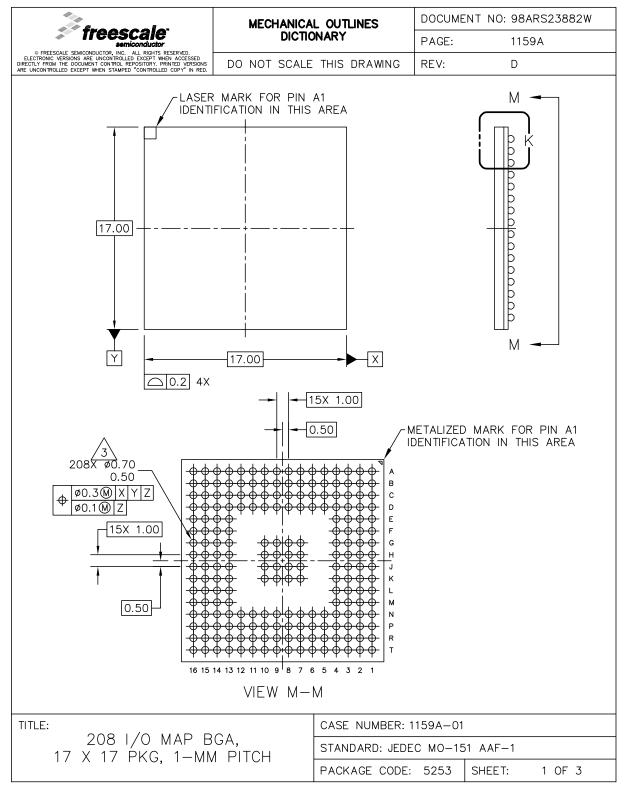

Packages

# 5.1.3 208 MAPBGA

Figure 36. 208 MAPBGA package mechanical drawing (part 1)

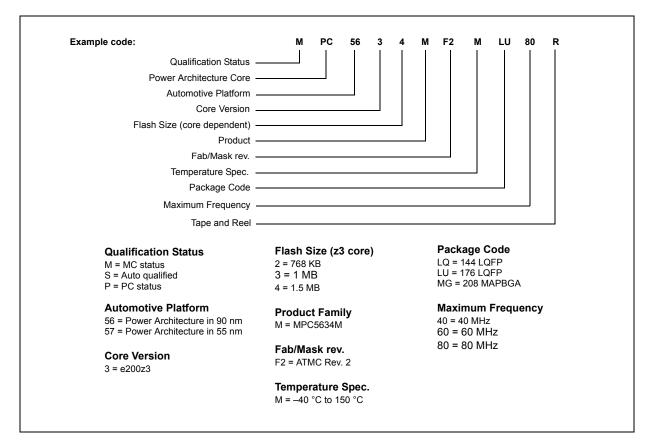

#### **Ordering information**

Figure 38. Commercial product code structure