Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Core Processore200z3Core Size32-Bit Single-CoreSpeed80MHzConnectivityCANbus, EBI/EMI, LINbus, SCI, SPI, UART/USARTPeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory Size1.5MB (1.5M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size94K x 8                                                                                                                                                                                       | 2010                       |                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed80MHzConnectivityCANbus, EBI/EMI, LINbus, SCI, SPI, UART/USARTPeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory Size1.5MB (1.5M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size94K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP (20x20)Nume Towne Towne Temperature-44-LQFP (20x20) | Product Status             | Active                                                                  |

| Speed80MHzConnectivityCANbus, EBI/EMI, LINbus, SCI, SPI, UART/USARTPeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory Size1.5MB (1.5M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size94K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP (20x20)                                                 | Core Processor             | e200z3                                                                  |

| ConnectivityCANbus, EBI/EMI, LINbus, SCI, SPI, UART/USARTPeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory Size1.5MB (1.5M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size94K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP (20x20)                                                           | Core Size                  | 32-Bit Single-Core                                                      |

| PeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory Size1.5MB (1.5M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size94K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting Type144-LQFP (20x20)                                                                                                                                               | Speed                      | 80MHz                                                                   |

| Number of I/O80Program Memory Size1.5MB (1.5M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size94K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFPSupplier Device Package144-LQFP (20x20)                                                                                                                  | Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI, UART/USART                           |

| Program Memory Size1.5MB (1.5M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size94K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFPSupplier Device Package144-LQFP (20x20)                                                                                                                                 | Peripherals                | DMA, POR, PWM, WDT                                                      |

| Program Memory TypeFLASHEEPROM Size-RAM Size94K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP (20x20)                                                                                                                                                                                                   | Number of I/O              | 80                                                                      |

| EEPROM Size-RAM Size94K × 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP (20x20)                                                                                                                                                                                                                           | Program Memory Size        | 1.5MB (1.5M x 8)                                                        |

| RAM Size94K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFPSupplier Device Package144-LQFP (20x20)                                                                                                                                                                                                        | Program Memory Type        | FLASH                                                                   |

| Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFPSupplier Device Package144-LQFP (20x20)                                                                                                                                                                                                                       | EEPROM Size                |                                                                         |

| Data ConvertersA/D 32x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFPSupplier Device Package144-LQFP (20x20)                                                                                                                                                                                                                                                             | RAM Size                   | 94K x 8                                                                 |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFPSupplier Device Package144-LQFP (20x20)                                                                                                                                                                                                                                                                                      | Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.25V                                                            |

| Operating Temperature     -40°C ~ 125°C (TA)       Mounting Type     Surface Mount       Package / Case     144-LQFP       Supplier Device Package     144-LQFP (20x20)                                                                                                                                                                                                                                                                    | Data Converters            | A/D 32x12b                                                              |

| Mounting Type     Surface Mount       Package / Case     144-LQFP       Supplier Device Package     144-LQFP (20x20)                                                                                                                                                                                                                                                                                                                       | Oscillator Type            | Internal                                                                |

| Package / Case     144-LQFP       Supplier Device Package     144-LQFP (20x20)                                                                                                                                                                                                                                                                                                                                                             | Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Supplier Device Package 144-LQFP (20x20)                                                                                                                                                                                                                                                                                                                                                                                                   | Mounting Type              | Surface Mount                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | Package / Case             | 144-LQFP                                                                |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5634mf2mlq80                                                                                                                                                                                                                                                                                                                                                       | Supplier Device Package    | 144-LQFP (20x20)                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5634mf2mlq80 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Non-maskable interrupt (NMI) input for handling external events that must produce an immediate response, e.g., power down detection. On this device, the NMI input is connected to the Critical Interrupt Input. (May not be recoverable)

- Critical Interrupt input. For external interrupt sources that are higher priority than provided by the Interrupt Controller. (Always recoverable)

- New 'Wait for Interrupt' instruction, to be used with new low power modes

- Reservation instructions for implementing read-modify-write accesses

- Signal processing extension (SPE) APU

- Operating on all 32 GPRs that are all extended to 64 bits wide

- Provides a full compliment of vector and scalar integer and floating point arithmetic operations (including integer vector MAC and MUL operations) (SIMD)

- Provides rich array of extended 64-bit loads and stores to/from extended GPRs

- Fully code compatible with e200z6 core

- Floating point (FPU)

- IEEE 754 compatible with software wrapper

- Scalar single precision in hardware, double precision with software library

- Conversion instructions between single precision floating point and fixed point

- Fully code compatible with e200z6 core

- Long cycle time instructions, except for guarded loads, do not increase interrupt latency

- Extensive system development support through Nexus debug port

- Advanced microcontroller bus architecture (AMBA) crossbar switch (XBAR)

- Three master ports, four slave ports

- Masters: CPU Instruction bus; CPU Load/store bus (Nexus); eDMA

- Slave: Flash; SRAM; Peripheral Bridge; calibration EBI

- 32-bit internal address bus, 64-bit internal data bus

- Enhanced direct memory access (eDMA) controller

- 32 channels support independent 8-bit, 16-bit, or 32-bit single value or block transfers

- Supports variable sized queues and circular queues

- Source and destination address registers are independently configured to post-increment or remain constant

- Each transfer is initiated by a peripheral, CPU, or eDMA channel request

- Each eDMA channel can optionally send an interrupt request to the CPU on completion of a single value or block transfer

- Interrupt controller (INTC)

- 191 peripheral interrupt request sources

- 8 software setable interrupt request sources

- 9-bit vector

- Unique vector for each interrupt request source

- Provided by hardware connection to processor or read from register

- Each interrupt source can be programmed to one of 16 priorities

- Preemption

- Preemptive prioritized interrupt requests to processor

- ISR at a higher priority preempts ISRs or tasks at lower priorities

- Automatic pushing or popping of preempted priority to or from a LIFO

- Ability to modify the ISR or task priority. Modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources.

- Low latency-three clocks from receipt of interrupt request from peripheral to interrupt request to processor

# 1 Introduction

# 1.1 Document overview

This document provides an overview and describes the features of the MPC5634M series of microcontroller units (MCUs). For functional characteristics, refer to the device reference manual. Electrical specifications and package mechanical drawings are included in this device data sheet. Pin assignments can be found in both the reference manual and data sheet.

# 1.2 Description

These 32-bit automotive microcontrollers are a family of system-on-chip (SoC) devices that contain all the features of the MPC5500 family and many new features coupled with high performance 90 nm CMOS technology to provide substantial reduction of cost per feature and significant performance improvement. The advanced and cost-efficient host processor core of this automotive controller family is built on Power Architecture<sup>®</sup> technology. This family contains enhancements that improve the architecture's fit in embedded applications, includes additional instruction support for digital signal processing (DSP), integrates technologies—such as an enhanced time processor unit, enhanced queued analog-to-digital converter, Controller Area Network, and an enhanced modular input-output system—that are important for today's lower-end powertrain applications. This device family is a completely compatible extension to Freescale's MPC5500 family. The device has a single level of memory hierarchy consisting of up to 94 KB on-chip SRAM and up to 1.5 MB of internal flash memory. The device also has an external bus interface (EBI) for 'calibration'. This external bus interface has been designed to support most of the standard memories used with the MPC55xx and MPC55xx families.

# 2 Overview

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5634M series of microcontroller units (MCUs). For functional characteristics, refer to the MPC5634M *Microcontroller Reference Manual*.

The MPC5634M series microcontrollers are system-on-chip devices that are built on Power Architecture<sup>®</sup> technology and:

- Are 100% user-mode compatible with the Power Architecture instruction set

- Contain enhancements that improve the architecture's fit in embedded applications

- Include additional instruction support for digital signal processing (DSP)

- Integrate technologies such as an enhanced time processor unit, enhanced queued analog-to-digital converter, Controller Area Network, and an enhanced modular input-output system

# 2.1 Device comparison

# 2.2 MPC5634M feature details

# 2.2.1 e200z335 core

The e200z335 processor utilizes a four stage pipeline for instruction execution. The Instruction Fetch (stage 1), Instruction Decode/Register file Read/Effective Address Calculation (stage 2), Execute/Memory Access (stage 3), and Register Writeback (stage 4) stages operate in an overlapped fashion, allowing single clock instruction execution for most instructions.

The integer execution unit consists of a 32-bit Arithmetic Unit (AU), a Logic Unit (LU), a 32-bit Barrel shifter (Shifter), a Mask-Insertion Unit (MIU), a Condition Register manipulation Unit (CRU), a Count-Leading-Zeros unit (CLZ), a 32×32 Hardware Multiplier array, result feed-forward hardware, and support hardware for division.

Most arithmetic and logical operations are executed in a single cycle with the exception of the divide instructions. A Count-Leading-Zeros unit operates in a single clock cycle. The Instruction Unit contains a PC incrementer and a dedicated

## Overview

- Sets up the MMU to allow user boot code to execute as either Power Architecture code (default) or as Freescale VLE code

- Detection of user boot code

- Automatic switch to serial boot mode if internal flash is blank or invalid

- Supports user programmable 64-bit password protection for serial boot mode

- Supports serial bootloading via FlexCAN bus and eSCI using Freescale protocol

- · Supports serial bootloading via FlexCAN bus and eSCI with auto baud rate sensing

- Supports serial bootloading of either Power Architecture code (default) or Freescale VLE code

- Supports booting from calibration bus interface

- Supports censorship protection for internal flash memory

- Provides an option to enable the core watchdog timer

- Provides an option to disable the software watchdog timer

# 2.2.12 eMIOS

The eMIOS (Enhanced Modular Input Output System) module provides the functionality to generate or measure time events. The channels on this module provide a range of operating modes including the capability to perform dual input capture or dual output compare as well as PWM output.

The eMIOS provides the following features:

- 16 channels (24-bit timer resolution)

- For compatibility with other family members selected channels and timebases are implemented:

- Channels 0 to 6, 8 to 15, and 23

- Timebases A, B and C

- Channels 1, 3, 5 and 6 support modes:

- General Purpose Input/Output (GPIO)

- Single Action Input Capture (SAIC)

- Single Action Output Compare (SAOC)

- Channels 2, 4, 11 and 13 support all the modes above plus:

- Output Pulse Width Modulation Buffered (OPWMB)

- Channels 0, 8, 9, 10, 12, 14, 15, 23 support all the modes above plus:

- Input Period Measurement (IPM)

- Input Pulse Width Measurement (IPWM)

- Double Action Output Compare (set flag on both matches) (DAOC)

- Modulus Counter Buffered (MCB)

- Output Pulse Width and Frequency Modulation Buffered (OPWFMB)

- Three 24-bit wide counter buses

- Counter bus A can be driven by channel 23 or by the eTPU2 and all channels can use it as a reference

- Counter bus B is driven by channel 0 and channels 0 to 6 can use it as a reference

- Counter bus C is driven by channel 8 and channels 8 to 15 can use it as a reference

- Shared time bases with the eTPU2 through the counter buses

- Synchronization among internal and external time bases

# 2.2.13 eTPU2

The eTPU2 is an enhanced co-processor designed for timing control. Operating in parallel with the host CPU, eTPU2 processes instructions and real-time input events, performs output waveform generation, and accesses shared data without host

## Overview

results to the result FIFOs. This allows the ADCs to sample the sensor at a rate high enough to avoid aliasing of out-of-band noise; while providing a reduced sample rate output to minimize the amount DSP processing bandwidth required to fully process the digitized waveform.

The eQADC provides the following features:

- Dual on-chip ADCs

- 2 × 12-bit ADC resolution

- Programmable resolution for increased conversion speed (12 bit, 10 bit, 8 bit)

- 12-bit conversion time 1 µs (1M sample/sec)

- 10-bit conversion time 867 ns (1.2M sample/second)

- 8-bit conversion time 733 ns (1.4M sample/second)

- Up to 10-bit accuracy at 500 KSample/s and 9-bit accuracy at 1 MSample/s

- Differential conversions

- Single-ended signal range from 0 to 5 V

- Variable gain amplifiers on differential inputs  $(\times 1, \times 2, \times 4)$

- Sample times of 2 (default), 8, 64 or 128 ADC clock cycles

- Provides time stamp information when requested

- Parallel interface to eQADC CFIFOs and RFIFOs

- Supports both right-justified unsigned and signed formats for conversion results

- Up to 34<sup>1</sup> input channels (accessible by both ADCs)

- 23 additional internal channels for measuring control and monitoring voltages inside the device

- Including Core voltage, I/O voltage, LVI voltages, etc.

- An internal bandgap reference to allow absolute voltage measurements

- 4 pairs of differential analog input channels

- Programmable pull-up/pull-down resistors on each differential input for biasing and sensor diagnostic (200 kΩ, 100 kΩ, 5 kΩ)

- Silicon die temperature sensor

- provides temperature of silicon as an analog value

- read using an internal ADC analog channel

- may be read with either ADC

- Decimation Filter

- Programmable decimation factor (2 to 16)

- Selectable IIR or FIR filter

- Up to 4th order IIR or 8th order FIR

- Programmable coefficients

- Saturated or non-saturated modes

- Programmable Rounding (Convergent; Two's Complement; Truncated)

- Pre-fill mode to pre-condition the filter before the sample window opens

- · Full duplex synchronous serial interface to an external device

- Free-running clock for use by an external device

- Supports a 26-bit message length

- Priority based Queues

- Supports six Queues with fixed priority. When commands of distinct Queues are bound for the same ADC, the higher priority Queue is always served first

<sup>1. 176-</sup>pin and 208-pin packages have 34 input channels; 144-pin package has 32.

## Overview

- 13-bit baud rate selection

- Programmable 8-bit or 9-bit, data format

- Programmable 12-bit or 13-bit data format for Timed Serial Bus (TSB) configuration to support the Microsecond Channel upstream

- Automatic parity generation

- LIN support

- Autonomous transmission of entire frames

- Configurable to support all revisions of the LIN standard

- Automatic parity bit generation

- Double stop bit after bit error

- 10- or 13-bit break support

- Separately enabled transmitter and receiver

- Programmable transmitter output parity

- 2 receiver wake up methods:

- Idle line wake-up

- Address mark wake-up

- Interrupt-driven operation with flags

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

- DMA support for both transmit and receive data

- Global error bit stored with receive data in system RAM to allow post processing of errors

# 2.2.17 FlexCAN

The MPC5634M MCU contains two controller area network (FlexCAN) blocks. The FlexCAN module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth. FlexCAN module 'A' contains 64 message buffers (MB); FlexCAN module 'C' contains 32 message buffers.

The FlexCAN module provides the following features:

- Based on and including all existing features of the Freescale TouCAN module

- Full Implementation of the CAN protocol specification, Version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- Zero to eight bytes data length

- Programmable bit rate up to 1 Mbit/s

- Content-related addressing

- 64 / 32 message buffers of zero to eight bytes data length

- Individual Rx Mask Register per message buffer

- Each message buffer configurable as Rx or Tx, all supporting standard and extended messages

- Includes 1056 / 544 bytes of embedded memory for message buffer storage

- Includes a 256-byte and a 128-byte memories for storing individual Rx mask registers

- Full featured Rx FIFO with storage capacity for six frames and internal pointer handling

- Powerful Rx FIFO ID filtering, capable of matching incoming IDs against 8 extended, 16 standard or 32 partial (8 bits) IDs, with individual masking capability

| Block                                               | Function                                                                                                                         |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| DMA (direct memory access)                          | Performs complex data movements with minimal intervention from the core                                                          |

| DSPI (deserial serial peripheral interface)         | Provides a synchronous serial interface for communication with external devices                                                  |

| eMIOS (enhanced modular input-output system)        | Provides the functionality to generate or measure events                                                                         |

| eQADC (enhanced queued analog-to-digital converter) | Provides accurate and fast conversions for a wide range of applications                                                          |

| eSCI (serial communication interface)               | Allows asynchronous serial communications with peripheral devices and other microcontroller units                                |

| eTPU (enhanced time processor unit)                 | Processes real-time input events, performs output waveform generation, and accesses shared data without host intervention        |

| FlexCAN (controller area network)                   | Supports the standard CAN communications protocol                                                                                |

| FMPLL (frequency-modulated phase-locked loop)       | Generates high-speed system clocks and supports the programmable frequency modulation of these clocks                            |

| INTC (interrupt controller)                         | Provides priority-based preemptive scheduling of interrupt requests                                                              |

| JTAG controller                                     | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode |

| NPC (Nexus Port Controller)                         | Provides real-time development support capabilities in compliance with the IEEE-ISTO 5001-2003 standard                          |

| PIT (peripheral interrupt timer)                    | Produces periodic interrupts and triggers                                                                                        |

| Temperature sensor                                  | Provides the temperature of the device as an analog value                                                                        |

| SWT (Software Watchdog Timer)                       | Provides protection from runaway code                                                                                            |

| STM (System Timer Module)                           | Timer providing a set of output compare events to support AutoSAR and operating system tasks                                     |

# 3.4 208 MAPBGA ballmap (MPC5634M)

Figure 5 shows the 208-pin MAPBGA ballmap for the MPC5634M (1536 KB flash memory) as viewed from above.

|   | 1                | 2       | 3                | 4       | 5       | 6                | 7                     | 8       | 9                     | 10                    | 11                    | 12               | 13               | 14              | 15                  | 16               |

|---|------------------|---------|------------------|---------|---------|------------------|-----------------------|---------|-----------------------|-----------------------|-----------------------|------------------|------------------|-----------------|---------------------|------------------|

| A | VSS              | AN9     | AN11             | VDDA1   | VSSA1   | AN1              | AN5                   | VRH     | VRL                   | AN27                  | VSSA0                 | AN12- SDS        | ALT_<br>MDO2     | ALT_<br>MDO0    | VRC33               | VSS              |

| В | VDD              | VSS     | AN38             | AN21    | AN0     | AN4              | REFBYPC               | AN22    | AN25                  | AN28                  | VDDA0                 | AN13-SDO         | ALT_<br>MDO3     | ALT_<br>MDO1    | VSS                 | VDD              |

| С | VSTBY            | VDD     | VSS              | AN17    | AN34    | AN16             | AN3                   | AN7     | AN23                  | AN32                  | AN33                  | AN14-SDI         | AN15<br>FCK      | VSS             | <u>ALT</u><br>MSEO0 | тск              |

| D | VRC33            | AN39    | VDD              | VSS     | AN18    | AN2              | AN6                   | AN24    | AN30                  | AN31                  | AN35                  | VDDEH7           | VSS              | TMS             | ALT_EVTO            | NIC <sup>1</sup> |

| E | ETPUA30          | ETPUA31 | AN37             | VDD     |         |                  |                       |         |                       |                       |                       |                  | VDDE7            | TDI             | ALT_EVTI            | ALT_<br>MSEO1    |

| F | ETPUA28          | ETPUA29 | ETPUA26          | AN36    |         |                  |                       |         |                       |                       |                       |                  | VDDEH6           | TDO             | ALT_MCKO            | JCOMP            |

| G | ETPUA24          | ETPUA27 | ETPUA25          | ETPUA21 |         |                  | VSS                   | VSS     | VSS                   | VSS                   |                       |                  | DSPI_B_<br>SOUT  | DSPI_B_<br>PCS3 | DSPI_B_<br>SIN      | DSPI_B_<br>PCS0  |

| н | ETPUA23          | ETPUA22 | ETPUA17          | ETPUA18 |         |                  | VSS                   | VSS     | VSS                   | VSS                   |                       |                  | GPIO99           | DSPI_B_<br>PCS4 | DSPI_B_<br>PCS2     | DSPI_B_<br>PCS1  |

| J | ETPUA20          | ETPUA19 | ETPUA14          | ETPUA13 |         |                  | VSS                   | VSS     | VSS                   | VSS                   |                       |                  | DSPI_B_<br>PCS5  | SCI_A_TX        | GPIO98              | DSPI_B_<br>SCK   |

| к | ETPUA16          | ETPUA15 | ETPUA7           | VDDEH1  |         |                  | VSS                   | VSS     | VSS                   | VSS                   |                       |                  | CAN_C_<br>TX     | SCI_A_RX        | RSTOUT              | VDDREG           |

| L | ETPUA12          | ETPUA11 | ETPUA6           | ETPUA0  |         |                  | <u> </u>              |         |                       |                       | 1                     |                  | SCI_B_TX         | CAN_C_<br>RX    | WKPCFG              | RESET            |

| М | ETPUA10          | ETPUA9  | ETPUA1           | ETPUA5  |         |                  |                       |         |                       |                       |                       |                  | SCI_B_RX         | PLLREF          | BOOTCFG1            | VSSPLL           |

| Ν | ETPUA8           | ETPUA4  | ETPUA0           | VSS     | VDD     | VRC33            | EMIOS2                | EMIOS10 | VDDEH1/6 <sup>2</sup> | EMIOS12               | eTPU_A19 <sup>3</sup> | VRC33            | VSS              | VRCCTL          | NIC <sup>1</sup>    | EXTAL            |

| Ρ | ETPUA3           | ETPUA2  | VSS              | VDD     | GPIO207 | VDDE7            | NIC <sup>1</sup>      | EMIOS8  | eTPU_A29 <sup>3</sup> | eTPU_A2 <sup>3</sup>  | eTPU_A21 <sup>3</sup> | CAN_A_<br>TX     | VDD              | VSS             | NIC <sup>1</sup>    | XTAL             |

| R | NIC <sup>1</sup> | VSS     | VDD              | GPIO206 | EMIOS4  | NIC <sup>1</sup> | EMIOS9                | EMIOS11 | EMIOS14               | eTPU_A27 <sup>3</sup> | EMIOS23               | CAN_A_<br>RX     | NIC <sup>1</sup> | VDD             | VSS                 | VDDPLL           |

| т | VSS              | VDD     | NIC <sup>1</sup> | EMIOS0  | EMIOS1  | GPIO219          | eTPU_A25 <sup>3</sup> | EMIOS13 | EMIOS15               | eTPU_A4 <sup>3</sup>  | eTPU_A13 <sup>3</sup> | NIC <sup>1</sup> | VDDE5            | CLKOUT          | VDD                 | VSS              |

<sup>1</sup> Pins marked "NIC" have no internal connection.

<sup>2</sup> This ball may be changed to "NC" (no connection) in a future revision.

<sup>3</sup> eTPU output only channel.

Figure 5. 208-pin MAPBGA ballmap (MPC5634M; top view)

# 3.5 208 MAPBGA ballmap (MPC5633M only)

Figure 6 shows the 208-pin MAPBGA ballmap for the MPC5633M (1024 KB flash memory) as viewed from above.

|   | 1                | 2       | 3                | 4               | 5               | 6                | 7                    | 8               | 9                     | 10                   | 11                   | 12               | 13              | 14              | 15               | 16               |

|---|------------------|---------|------------------|-----------------|-----------------|------------------|----------------------|-----------------|-----------------------|----------------------|----------------------|------------------|-----------------|-----------------|------------------|------------------|

| А | VSS              | AN9     | AN11             | VDDA1           | VSSA1           | AN1              | AN5                  | VRH             | VRL                   | AN27                 | VSSA0                | AN12-SDS         | ALT_<br>MDO2    | ALT_<br>MDO0    | VRC33            | VSS              |

| в | VDD              | VSS     | AN38             | AN21            | AN0             | AN4              | REFBYPC              | AN22            | AN25                  | AN28                 | VDDA0                | AN13-SDO         | ALT_<br>MDO3    | ALT_<br>MDO1    | VSS              | VDD              |

| с | VSTBY            | VDD     | VSS              | AN17            | AN34            | AN16             | AN3                  | AN7             | AN23                  | AN32                 | AN33                 | AN14-SDI         | AN15<br>FCK     | VSS             | ALT<br>MSEO0     | тск              |

| D | VRC33            | AN39    | VDD              | VSS             | AN18            | AN2              | AN6                  | AN24            | AN30                  | AN31                 | AN35                 | VDDEH7           | VSS             | TMS             | ALT_EVTO         | NIC <sup>1</sup> |

| Е | ETPUA30          | ETPUA31 | NC <sup>2</sup>  | VDD             |                 |                  |                      |                 |                       |                      |                      |                  | VDDE7           | TDI             | ALT<br>EVTI      | ALT_<br>MSEO1    |

| F | ETPUA28          | ETPUA29 | ETPUA26          | NC <sup>2</sup> |                 |                  |                      |                 |                       |                      |                      |                  | VDDEH6          | TDO             | ALT_MCKO         | JCOMP            |

| G | ETPUA24          | ETPUA27 | ETPUA25          | ETPUA21         |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | DSPI_B_<br>SOUT | DSPI_B_<br>PCS3 | DSPI_B_<br>SIN   | DSPI_B_<br>PCS0  |

| н | ETPUA23          | ETPUA22 | ETPUA17          | ETPUA18         |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | NC <sup>2</sup> | DSPI_B_<br>PCS4 | DSPI_B_<br>PCS2  | DSPI_B_<br>PCS1  |

| J | ETPUA20          | ETPUA19 | ETPUA14          | ETPUA13         |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | DSPI_B_<br>PCS5 | SCI_A_TX        | NC <sup>2</sup>  | DSPI_B_<br>SCK   |

| к | ETPUA16          | ETPUA15 | ETPUA7           | VDDEH1          |                 |                  | VSS                  | VSS             | VSS                   | VSS                  |                      |                  | CAN_C_<br>TX    | SCI_A_RX        | RSTOUT           | VDDREG           |

| L | ETPUA12          | ETPUA11 | ETPUA6           | ETPUA0          |                 |                  |                      |                 |                       |                      |                      |                  | SCI_B_TX        | CAN_C_<br>RX    | WKPCFG           | RESET            |

| м | ETPUA10          | ETPUA9  | ETPUA1           | ETPUA5          |                 |                  |                      |                 |                       |                      |                      |                  | SCI_B_RX        | PLLREF          | BOOTCFG1         | VSSPLL           |

| N | ETPUA8           | ETPUA4  | ETPUA0           | VSS             | VDD             | VRC33            | EMIOS2               | EMIOS10         | VDDEH1/6 <sup>3</sup> | EMIOS12              | eTPUA19 <sup>4</sup> | VRC33            | VSS             | VRCCTL          | NIC <sup>1</sup> | EXTAL            |

| Р | ETPUA3           | ETPUA2  | VSS              | VDD             | NC <sup>2</sup> | VDDE7            | NIC <sup>1</sup>     | EMIOS8          | eTPUA29 <sup>3</sup>  | eTPUA2 <sup>3</sup>  | eTPUA21 <sup>3</sup> | CAN_A_<br>TX     | VDD             | VSS             | NIC <sup>1</sup> | XTAL             |

| R | NIC <sup>1</sup> | VSS     | VDD              | NC <sup>2</sup> | EMIOS4          | NIC <sup>1</sup> | EMIOS9               | EMIOS11         | EMIOS14               | eTPUA27 <sup>3</sup> | EMIOS23              | CAN_A_<br>RX     | NC <sup>2</sup> | VDD             | VSS              | VDDPLL           |

| т | VSS              | VDD     | NIC <sup>1</sup> | EMIOS0          | NC <sup>2</sup> | GPIO219          | eTPUA25 <sup>3</sup> | NC <sup>2</sup> | NC <sup>2</sup>       | eTPUA4 <sup>3</sup>  | eTPUA13 <sup>3</sup> | NIC <sup>1</sup> | VDDE5           | CLKOUT          | VDD              | VSS              |

<sup>1</sup> Pins marked "NIC" have no internal connection.

<sup>2</sup> Pins marked "NC" may be connected to internal circuitry. Connections to external circuits or other pins on this device can result in unpredictable system behavior or damage.

<sup>3</sup> This ball may be changed to "NC" (no connection) in a future revision.

<sup>4</sup> eTPU output only channel.

Figure 6. 208-pin MAPBGA ballmap (MPC5633M; top view)

34 4

MPC5634M Microcontroller Data Sheet, Rev.

ø

# MPC5634M Microcontroller Data Sheet, Rev. 9

## Table 2. MPC563xM signal properties (continued)

|                                                                                      |                                                                                                    | Pad<br>Config.                 | PCR PA                               | I/O                  | Voltage <sup>4</sup> / |                          | Function / State         |             | Pin No.     |                |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------|----------------------|------------------------|--------------------------|--------------------------|-------------|-------------|----------------|

| Name                                                                                 | Function <sup>1</sup>                                                                              | Register<br>(PCR) <sup>2</sup> | Field <sup>3</sup>                   | Type                 | Pad Type               | Reset State <sup>5</sup> | After Reset <sup>6</sup> | 144<br>LQFP | 176<br>LQFP | 208 MAPB<br>GA |

| eTPU_A[18]<br>GPIO[132]                                                              | eTPU_A Ch.<br>GPIO                                                                                 | PCR[132]                       | 01<br>00                             | I/O<br>I/O           | VDDEH1b<br>Slow        | – / WKPCFG               | – / WKPCFG               | 30          | 37          | H4             |

| eTPU_A[19]<br>GPIO[133]                                                              | eTPU_A Ch.<br>GPIO                                                                                 | PCR[133]                       | 01<br>00                             | I/O<br>I/O           | VDDEH1b<br>Slow        | – / WKPCFG               | – / WKPCFG               | 29          | 36          | J2             |

| eTPU_A[20]<br>IRQ[8]<br>GPIO[134]                                                    | eTPU_A Ch.<br>External Interrupt Request<br>GPIO                                                   | PCR[134]                       | 01<br>10<br>00                       | I/O<br>I<br>I/O      | VDDEH1b<br>Slow        | -/WKPCFG                 | – / WKPCFG               | 28          | 35          | J1             |

| eTPU_A[21]<br>IRQ[9]<br>GPIO[135]                                                    | eTPU_A Ch.<br>External Interrupt Request<br>GPIO                                                   | PCR[135]                       | 01<br>10<br>00                       | I/O<br>I<br>I/O      | VDDEH1a<br>Slow        | -/WKPCFG                 | – / WKPCFG               | 27          | 34          | G4             |

| eTPU_A[22]<br>IRQ[10]<br>eTPU_A[17]<br>GPI0[136]                                     | eTPU_A Ch.<br>External Interrupt Request<br>eTPU_A Ch. External<br>GPIO                            | PCR[136]                       | 001<br>010<br>100<br>000             | I/O<br>I<br>O<br>I/O | VDDEH1a<br>Slow        | -/WKPCFG                 | – / WKPCFG               | 25          | 32          | H2             |

| eTPU_A[23]<br>IRQ[11]<br>eTPU_A[21]<br>GPI0[137]                                     | eTPU_A Ch.<br>External Interrupt Request<br>eTPU_A Ch. External<br>GPIO                            | PCR[137]                       | 001<br>010<br>100<br>000             | I/O<br>I<br>O<br>I/O | VDDEH1a<br>Slow        | -/WKPCFG                 | – / WKPCFG               | 23          | 30          | H1             |

| eTPU_A[24] <sup>28</sup><br>IRQ[12]<br>DSPI_C_SCK_LVDS-<br>GPI0[138]                 | eTPU_A Ch.<br>External Interrupt Request<br>DSPI_C Clock LVDS-<br>GPIO                             | PCR[138]                       | 001<br>010<br>100<br>000             | I/O<br>I<br>O<br>I/O | VDDEH1a<br>Slow        | -/WKPCFG                 | – / WKPCFG               | 21          | 28          | G1             |

| eTPU_A[25] <sup>28</sup><br>IRQ[13]<br>DSPI_C_SCK_LVDS+<br>GPI0[139]                 | eTPU_A Ch.<br>External Interrupt Request<br>DSPI _C Clock LVDS+<br>GPIO                            | PCR[139]                       | 001<br>010<br>100<br>000             | I/O<br>I<br>O<br>I/O | VDDEH1a<br>Medium      | -/WKPCFG                 | – / WKPCFG               | 20          | 27          | G3             |

| eTPU_A[26] <sup>28</sup><br>IRQ[14]<br>DSPI_C_SOUT_LVDS-<br>GPIO[140]                | eTPU_A Ch.<br>External Interrupt Request<br>DSPI_C Data Output LVDS-<br>GPIO                       | PCR[140]                       | 001<br>010<br>100<br>000             | I/O<br>I<br>O<br>I/O | VDDEH1a<br>Slow        | -/WKPCFG                 | – / WKPCFG               | 19          | 26          | F3             |

| eTPU_A[27] <sup>28</sup><br>IRQ[15]<br>DSPI_C_SOUT_LVDS+<br>DSPI_B_SOUT<br>GPI0[141] | eTPU_A Ch.<br>External Interrupt Request<br>DSPI_C Data Output LVDS+<br>DSPI_B Data Output<br>GPIO | PCR[141]                       | 0001<br>0010<br>0100<br>1000<br>0000 | I/O<br>I<br>O<br>I/O | VDDEH1a<br>Slow        | -/WKPCFG                 | – / WKPCFG               | 18          | 25          | G2             |

Pinout and signal description

| Signal     | Module or Function           | Description                                                                                                                                                                                                                                                                                                                                          |

|------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EVTI       | Nexus                        | EVTI is an input that is read on the negation of RESET to enable<br>or disable the Nexus Debug port. After reset, the EVTI pin is<br>used to initiate program synchronization messages or generate<br>a breakpoint.                                                                                                                                  |

| EVTO       | Nexus                        | Output that provides timing to a development tool for a single watchpoint or breakpoint occurrence.                                                                                                                                                                                                                                                  |

| МСКО       | Nexus                        | MCKO is a free running clock output to the development tools which is used for timing of the MDO and $\overline{\text{MSEO}}$ signals.                                                                                                                                                                                                               |

| MDO[3:0]   | Nexus                        | Trace message output to development tools. This pin also<br>indicates the status of the crystal oscillator clock following a<br>power-on reset, when MDO[0] is driven high until the crystal<br>oscillator clock achieves stability and is then negated.                                                                                             |

| MSEO[1:0]  | Nexus                        | Output pin—Indicates the start or end of the variable length message on the MDO pins                                                                                                                                                                                                                                                                 |

| BOOTCFG[1] | SIU – Configuration          | The BOOTCFG1 pin is sampled during the assertion of the RSTOUT signal, and the value is used to update the RSR and the BAM boot mode                                                                                                                                                                                                                 |

|            |                              | The following values are for BOOTCFG[0:1]:<br>0 Boot from internal flash memory<br>1 FlexCAN/eSCI boot                                                                                                                                                                                                                                               |

| WKPCFG     | SIU – Configuration          | The WKPCFG pin is applied at the assertion of the internal reset signal (assertion of RSTOUT), and is sampled 4 clock cycles before the negation of the RSTOUT pin.                                                                                                                                                                                  |

|            |                              | The value is used to configure whether the eTPU and eMIOS<br>pins are connected to internal weak pull up or weak pull down<br>devices after reset. The value latched on the WKPCFG pin at<br>reset is stored in the Reset Status Register (RSR), and is<br>updated for all reset sources except the Debug Port Reset and<br>Software External Reset. |

|            |                              | <ul><li>0: Weak pulldown applied to eTPU and eMIOS pins at reset</li><li>1: Weak pullup applied to eTPU and eMIOS pins at reset.</li></ul>                                                                                                                                                                                                           |

| ETRIG[2:3] | SIU – eQADC Triggers         | External signal eTRIGx triggers eQADC CFIFOx                                                                                                                                                                                                                                                                                                         |

| IRQ[0:15]  | SIU – External<br>Interrupts | The IRQ[0:15] pins connect to the SIU IRQ inputs. IMUX Select Register 1 is used to select the IRQ[0:15] pins as inputs to the IRQs.                                                                                                                                                                                                                 |

## Table 4. Signal details (continued)

## Pinout and signal description

| Signal  | Module or Function           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMI     | SIU – External<br>Interrupts | Non-Maskable Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GPIO[n] | SIU – GPIO                   | Configurable general purpose I/O pins. Each GPIO input and<br>output is separately controlled by an 8-bit input (GPDI) or output<br>(GPDO) register. Additionally, each GPIO pins is configured<br>using a dedicated SIU_PCR register.                                                                                                                                                                                                                 |

|         |                              | The GPIO pins are generally multiplexed with other I/O pin functions.                                                                                                                                                                                                                                                                                                                                                                                  |

| RESET   | SIU – Reset                  | The RESET pin is an active low input. The RESET pin is<br>asserted by an external device during a power-on or external<br>reset. The internal reset signal asserts only if the RESET pin<br>asserts for 10 clock cycles. Assertion of the RESET pin while the<br>device is in reset causes the reset cycle to start over.<br>The RESET pin has a glitch detector which detects spikes<br>greater than two clock cycles in duration that fall below the |

|         |                              | switch point of the input buffer logic of the VDDEH input pins.<br>The switch point lies between the maximum VIL and minimum<br>VIH specifications for the VDDEH input pins.                                                                                                                                                                                                                                                                           |

| RSTOUT  | SIU – Reset                  | The RSTOUT pin is an active low output that uses a push/pull configuration. The RSTOUT pin is driven to the low state by the MCU for all internal and external reset sources. There is a delay between initiation of the reset and the assertion of the RSTOUT pin.                                                                                                                                                                                    |

## Table 4. Signal details (continued)

Table 5 gives the power/ground segmentation of the MPC563x MCU. Each segment provides the power and ground for the given set of I/O pins, and can be powered by any of the allowed voltages regardless of the power on the other segments.

| Power<br>Segment | 144-LQFP<br>Pin<br>Number | 176-LQFP<br>Pin<br>Number | 208-BGA<br>Pin<br>Number | Voltage<br>Range <sup>1</sup> | I/O Pins Powered<br>by Segment                                                                                   |

|------------------|---------------------------|---------------------------|--------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------|

| VDDA0            | 6                         | 6                         | B11                      | 5.0 V                         | AN[0:7], AN[9], AN[11],<br>AN[16:18], AN[21:25],<br>AN[27:28], AN[30:37],<br>AN38, AN39, VRL,<br>REFBYPC,<br>VRH |

| VDDE5            | —                         | _                         | T13                      | 1.8 V –<br>3.3 V              | CLKOUT                                                                                                           |

| VDDEH1<br>(a,b)  | 24, 34                    | 31, 41                    | K4                       | 3.3 V –<br>5.0 V              | PCKCFG[2],<br>eTPU_A[0:31],<br>eMIOS[0:2]                                                                        |

## Table 5. MPC563x Power/Ground Segmentation

**Electrical characteristics**

# 4.6.2 Recommended power transistors

The following NPN transistors are recommended for use with the on-chip voltage regulator controller: ON Semiconductor<sup>TM</sup> BCP68T1 or NJD2873 as well as Philips Semiconductor<sup>TM</sup> BCP68. The collector of the external transistor is preferably connected to the same voltage supply source as the output stage of the regulator.

| Symbol              | Parameter                               | Value                   | Unit |

|---------------------|-----------------------------------------|-------------------------|------|

| h <sub>FE</sub> (β) | DC current gain (Beta)                  | 60 – 550                | _    |

| P <sub>D</sub>      | Absolute minimum power dissipation      | >1.0<br>(1.5 preferred) | W    |

| I <sub>CMaxDC</sub> | Minimum peak collector current          | 1.0                     | А    |

| VCE <sub>SAT</sub>  | Collector-to-emitter saturation voltage | 200–600 <sup>1</sup>    | mV   |

| V <sub>BE</sub>     | Base-to-emitter voltage                 | 0.4–1.0                 | V    |

Table 19. Recommended operating characteristics

<sup>1</sup> Adjust resistor at bipolar transistor collector for 3.3 V/5.0 V to avoid VCE < VCE<sub>SAT</sub>

# 4.7 Power up/down sequencing

There is no power sequencing required among power sources during power up and power down, in order to operate within specification but use of the following sequence is strongly recommended when the internal regulator is bypassed:

$5 \text{ V} \rightarrow 3.3 \text{ V}$  and 1.2 V

This is also the normal sequence when the internal regulator is enabled.

Although there are no power up/down sequencing requirements to prevent issues like latch-up, excessive current spikes, etc., the state of the I/O pins during power up/down varies according to table Table 20 for all pins with fast pads and Table 21 for all pins with medium, slow and multi-voltage pads.<sup>1</sup>

| V <sub>DDE</sub> | V <sub>RC33</sub> | V <sub>DD</sub> | Fast (pad_fc)  |

|------------------|-------------------|-----------------|----------------|

| LOW              | Х                 | Х               | LOW            |

| V <sub>DDE</sub> | LOW               | Х               | HIGH           |

| V <sub>DDE</sub> | V <sub>RC33</sub> | LOW             | HIGH IMPEDANCE |

| V <sub>DDE</sub> | V <sub>RC33</sub> | V <sub>DD</sub> | FUNCTIONAL     |

Table 20. Power sequence pin states for fast pads

| Table 21, Power sequenc  | e pin states for medium | , slow and multi-voltage pads |

|--------------------------|-------------------------|-------------------------------|

| Tuble 21. Tower bequeite | e pin states for meanum | , slow and multi-voltage paus |

| V <sub>DDEH</sub> | V <sub>DD</sub> | Medium (pad_msr_hv)<br>Slow (pad_ssr_hv)<br>Multi-voltage (pad_multv_hv) |  |  |

|-------------------|-----------------|--------------------------------------------------------------------------|--|--|

| LOW               | Х               | LOW                                                                      |  |  |

| V <sub>DDEH</sub> | LOW             | HIGH IMPEDANCE                                                           |  |  |

| V <sub>DDEH</sub> | $V_{DD}$        | FUNCTIONAL                                                               |  |  |

<sup>1.</sup>If an external 3.3V external regulator is used to supply current to the 1.2V pass transistor and this supply also supplies current for the other 3.3V supplies, then the 5V supply must always be greater than or equal to the external 3.3V supply.

## **Electrical characteristics**

| Symbol    |   | Parameter                                                                                                                    | Conditions                          | Value   |         | Unit   |

|-----------|---|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------|---------|--------|

| Symbo     | • | Falameter                                                                                                                    | contaitions                         | Min     | Тур     | Unit   |

| P/E       | С | Number of program/erase cycles per block<br>for 16 Kbyte blocks over the operating<br>temperature range (T <sub>J</sub> )    | _                                   | 100,000 | _       | cycles |

| P/E       | С | Number of program/erase cycles per block<br>for 32 and 64 Kbyte blocks over operating<br>temperature range (T <sub>J</sub> ) | _                                   | 10,000  | 100,000 | cycles |

| P/E       | С | Number of program/erase cycles per block<br>for 128 Kbyte blocks over the operating<br>temperature range (T <sub>J</sub> )   | _                                   | 1,000   | 100,000 | cycles |

| Retention | С | Minimum data retention at 85 °C average<br>ambient temperature <sup>1</sup>                                                  | Blocks with 0 – 1,000<br>P/E cycles | 20      |         | years  |

|           |   |                                                                                                                              | Blocks with 10,000 P/E cycles       | 10      | —       | years  |

|           |   |                                                                                                                              | Blocks with 100,000 P/E cycles      | 5       | —       | years  |

## Table 32. Flash module life

<sup>1</sup> Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

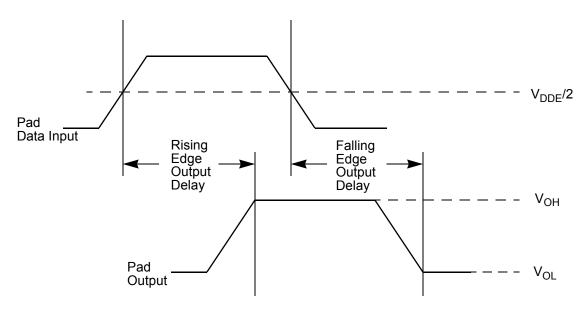

Figure 8. Pad output delay

# 4.16 AC timing

# 4.16.1 IEEE 1149.1 interface timing

## Table 36. JTAG pin AC electrical characteristics<sup>1</sup>

| #  | Symbol                                |    | с | Characteristic                      | Min.<br>Value | Max.<br>Value | Unit |

|----|---------------------------------------|----|---|-------------------------------------|---------------|---------------|------|

| 1  | t <sub>JCYC</sub>                     | CC | D | TCK Cycle Time                      | 100           | —             | ns   |

| 2  | t <sub>JDC</sub>                      | CC | D | TCK Clock Pulse Width               | 40            | 60            | ns   |

| 3  | t <sub>TCKRISE</sub>                  | CC | D | TCK Rise and Fall Times (40% – 70%) | _             | 3             | ns   |

| 4  | t <sub>TMSS,</sub> t <sub>TDIS</sub>  | CC | D | TMS, TDI Data Setup Time            | 5             | _             | ns   |

| 5  | t <sub>TMSH</sub> , t <sub>TDIH</sub> | CC | D | TMS, TDI Data Hold Time             | 25            | _             | ns   |

| 6  | t <sub>TDOV</sub>                     | CC | D | TCK Low to TDO Data Valid           | _             | 23            | ns   |

| 7  | t <sub>TDOI</sub>                     | CC | D | TCK Low to TDO Data Invalid         | 0             | —             | ns   |

| 8  | t <sub>TDOHZ</sub>                    | CC | D | TCK Low to TDO High Impedance       | _             | 20            | ns   |

| 9  | t <sub>JCMPPW</sub>                   | CC | D | JCOMP Assertion Time                | 100           | _             | ns   |

| 10 | t <sub>JCMPS</sub>                    | CC | D | JCOMP Setup Time to TCK Low         | 40            | _             | ns   |

| 11 | t <sub>BSDV</sub>                     | CC | D | TCK Falling Edge to Output Valid    | —             | 50            | ns   |

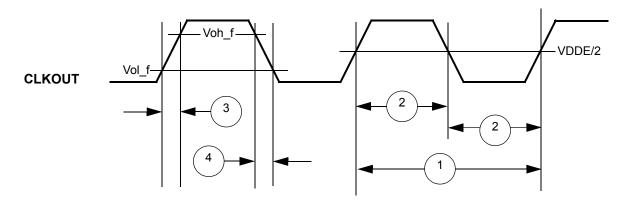

Figure 16. CLKOUT timing

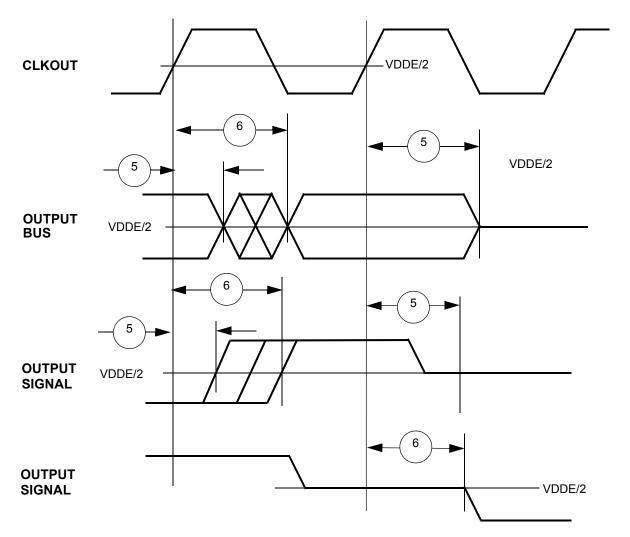

Figure 17. Synchronous output timing

## **Electrical characteristics**

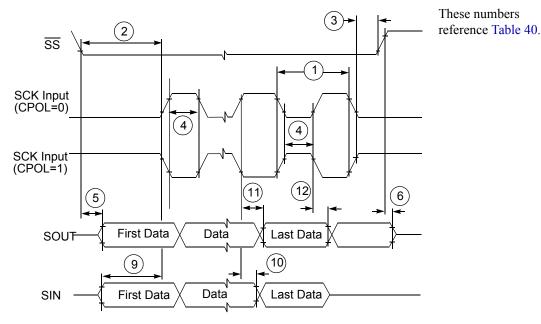

Figure 26. DSPI modified transfer format timing – slave, CPHA =0

Figure 27. DSPI modified transfer format timing – slave, CPHA =1

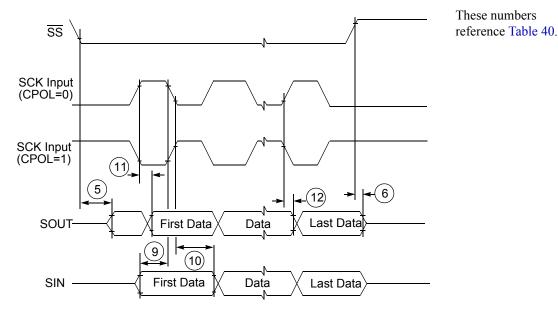

Figure 28. DSPI PCS strobe (PCSS) timing

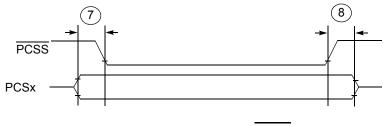

Packages

## Packages

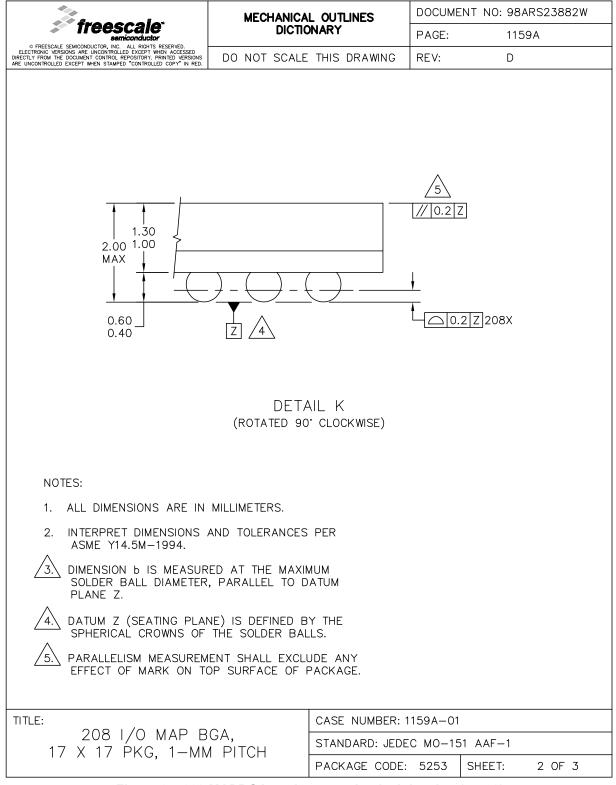

Figure 37. 208 MAPBGA package mechanical drawing (part 2)

**Ordering information**

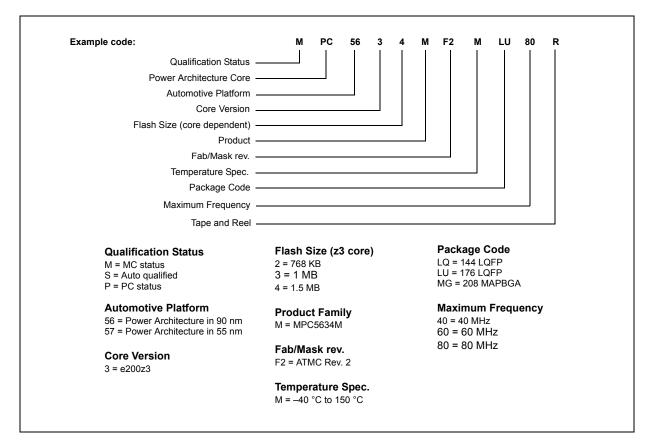

# 6 Ordering information

Table 42 shows the orderable part numbers for the MPC5634M series.

| Part Number     | Flash/SRAM<br>(Kbytes) | Package            | Speed<br>(MHz) |

|-----------------|------------------------|--------------------|----------------|

| SPC5632MF2MLQ60 | 768 / 48               | 144 LQFP Pb-free   | 60             |

| SPC5632MF2MLQ40 | 768 / 48               | 144 LQFP Pb-free   | 40             |

| SPC5633MF2MMG80 | 1024 / 64              | 208 MAPBGA Pb-free | 80             |

| SPC5633MF2MLU80 | 1024 / 64              | 176 LQFP Pb-free   | 80             |

| SPC5633MF2MLQ80 | 1024 / 64              | 144 LQFP Pb-free   | 80             |

| SPC5633MF2MMG60 | 1024 / 64              | 208 MAPBGA Pb-free | 60             |

| SPC5633MF2MLU60 | 1024 / 64              | 176 LQFP Pb-free   | 60             |

| SPC5633MF2MLQ60 | 1024 / 64              | 144 LQFP Pb-free   | 60             |

| SPC5633MF2MLQ40 | 1024 / 64              | 144 LQFP Pb-free   | 40             |

| SPC5634MF2MMG80 | 1536 / 94              | 208 MAPBGA Pb-free | 80             |

| SPC5634MF2MLU80 | 1536 / 94              | 176 LQFP Pb-free   | 80             |

| SPC5634MF2MLQ80 | 1536 / 94              | 144 LQFP Pb-free   | 80             |

| SPC5634MF2MMG60 | 1536 / 94              | 208 MAPBGA Pb-free | 60             |

| SPC5634MF2MLU60 | 1536 / 94              | 176 LQFP Pb-free   | 60             |

| SPC5634MF2MLQ60 | 1536 / 94              | 144 LQFP Pb-free   | 60             |

| SPC563M60L3CPBY |                        |                    |                |

| SPC563M60L3CPAY |                        |                    |                |

Table 42. Orderable part number summary

## **Ordering information**

Figure 38. Commercial product code structure