#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                   |

|---------------------------------|----------------------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                             |

| Speed                           | 180MHz                                                                     |

| Co-Processors/DSP               | -                                                                          |

| RAM Controllers                 | SDRAM, SRAM                                                                |

| Graphics Acceleration           | No                                                                         |

| Display & Interface Controllers | LCD, Touchscreen                                                           |

| Ethernet                        | 10/100Mbps                                                                 |

| SATA                            | -                                                                          |

| USB                             | USB 2.0 (3)                                                                |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                           |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                          |

| Security Features               | -                                                                          |

| Package / Case                  | 217-LFBGA                                                                  |

| Supplier Device Package         | 217-LFBGA (15x15)                                                          |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/at91sam9xe128-cu |

|                                 |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

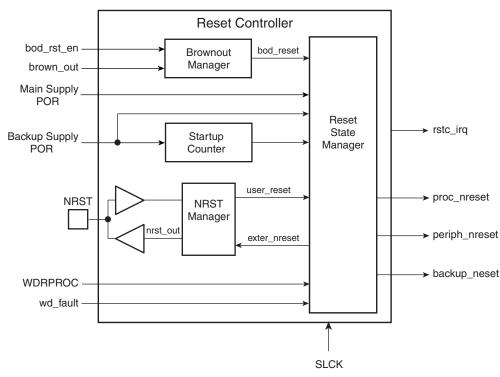

## **15. Reset Controller (RSTC)**

## 15.1 Description

The Reset Controller (RSTC), based on power-on reset cells, handles all the resets of the system without any external components. It reports which reset occurred last.

The Reset Controller also drives independently or simultaneously the external reset and the peripheral and processor resets.

A brownout detection is also available to prevent the processor from falling into an unpredictable state.

## 15.2 Block Diagram

Figure 15-1. Reset Controller Block Diagram

## **15.3 Functional Description**

#### 15.3.1 Reset Controller Overview

The Reset Controller is made up of an NRST Manager, a Brownout Manager, a Startup Counter and a Reset State Manager. It runs at Slow Clock and generates the following reset signals:

- proc\_nreset: Processor reset line. It also resets the Watchdog Timer.

- backup\_nreset: Affects all the peripherals powered by VDDBU.

- periph\_nreset: Affects the whole set of embedded peripherals.

- nrst\_out: Drives the NRST pin.

## 16.4.1 Real-time Timer Mode Register

| Register Name | e: RTT_M | IR    |           |           |              |                 |              |

|---------------|----------|-------|-----------|-----------|--------------|-----------------|--------------|

| Address:      | 0xFFFF   | FD20  |           |           |              |                 |              |

| Access Type:  | Read/V   | Vrite |           |           |              |                 |              |

| 31            | 30       | 29    | 28        | 27        | 26           | 25              | 24           |

| -             | -        | —     | -         | -         | -            | —               | -            |

| 23            | 22       | 21    | 20        | 19<br>-   | 18<br>RTTRST | 17<br>RTTINCIEN | 16<br>ALMIEN |

| 15            | 14       | 13    | 12<br>8TP | 11<br>RES | 10           | 9               | 8            |

|               |          |       | 1111      | nL0       |              |                 |              |

| 7             | 6        | 5     | 4         | 3         | 2            | 1               | 0            |

|               |          |       | RIP       | RES       |              |                 |              |

#### • RTPRES: Real-time Timer Prescaler Value

Defines the number of SLCK periods required to increment the Real-time timer. RTPRES is defined as follows:

RTPRES = 0: The prescaler period is equal to  $2^{16}$ .

RTPRES ...0: The prescaler period is equal to RTPRES.

#### • ALMIEN: Alarm Interrupt Enable

- 0 = The bit ALMS in RTT\_SR has no effect on interrupt.

- 1 = The bit ALMS in RTT\_SR asserts interrupt.

#### • RTTINCIEN: Real-time Timer Increment Interrupt Enable

- 0 = The bit RTTINC in RTT\_SR has no effect on interrupt.

- 1 = The bit RTTINC in RTT\_SR asserts interrupt.

#### • RTTRST: Real-time Timer Restart

1 = Reloads and restarts the clock divider with the new programmed value. This also resets the 32-bit counter.

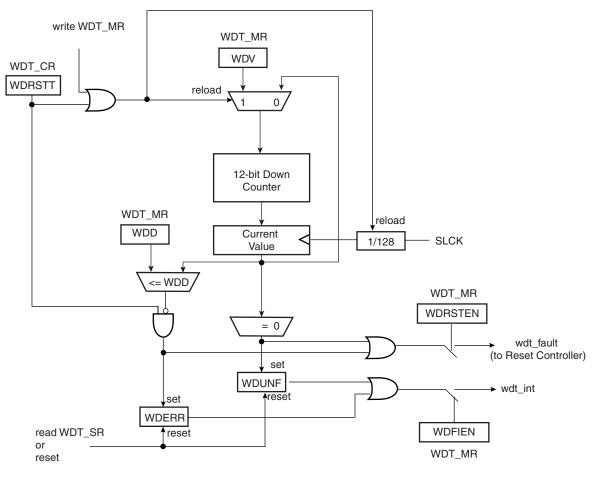

## 18. Watch Dog Timer (WDT)

## 18.1 Description

The Watchdog Timer can be used to prevent system lock-up if the software becomes trapped in a deadlock. It features a 12-bit down counter that allows a watchdog period of up to 16 seconds (slow clock at 32.768 kHz). It can generate a general reset or a processor reset only. In addition, it can be stopped while the processor is in debug mode or idle mode.

## 18.2 Block Diagram

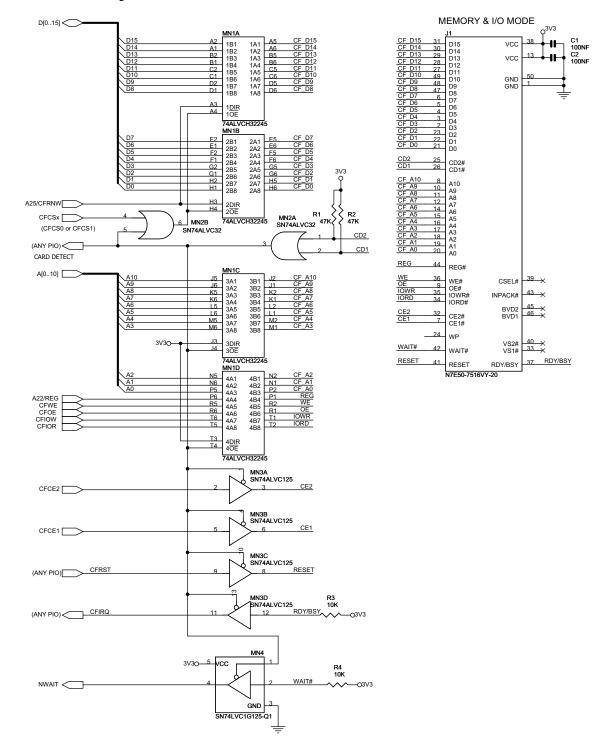

### 22.7.6 Compact Flash

## 22.7.6.1 Hardware Configuration

#### 24.5.3 Border Management

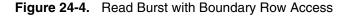

When the memory row boundary has been reached, an automatic page break is inserted. In this case, the SDRAM controller generates a precharge command, activates the new row and initiates a read or write command. To comply with SDRAM timing parameters, an additional clock cycle is inserted between the precharge/active ( $t_{\rm RP}$ ) command and the active/read ( $t_{\rm RCD}$ ) command. This is described in Figure 24-4 below.

| 25.7.4 ECC Par<br>Register Name: | ity Register 3<br>ECC_PR3 |          |    |          |    |          |    |

|----------------------------------|---------------------------|----------|----|----------|----|----------|----|

| Address:                         | 0xFFFFE81                 | С        |    |          |    |          |    |

| Access Type:                     | Read-only                 |          |    |          |    |          |    |

| 31                               | 30                        | 29       | 28 | 27       | 26 | 25       | 24 |

| 23                               | 22                        | 21       | 20 | 19       | 18 | 17       | 16 |

| 0                                |                           |          |    | NPARITY3 |    |          |    |

| 15                               | 14                        | 13       | 12 | 11       | 10 | 9        | 8  |

|                                  | NPARIT                    | Y3       |    | 0        |    | WORDADD3 |    |

| 7                                | 6                         | 5        | 4  | 3        | 2  | 1        | 0  |

|                                  | W                         | ORDADDR3 |    |          |    | BITADDR3 |    |

Once the entire main area of a page is written with data, the register content must be stored at any free location of the spare area.

## • BITADDR3: corrupted Bit Address in the page between the 768th and the 1023rd bytes

During a page read, this value contains the corrupted bit offset where an error occurred, if a single error was detected. If multiple errors were detected, this value is meaningless.

#### • WORDADDR3: corrupted Word Address in the page between the 768th and the 1023rd bytes

During a page read, this value contains the word address (8-bit word) where an error occurred, if a single error was detected. If multiple errors were detected, this value is meaningless

#### • NPARITY3:

Parity N

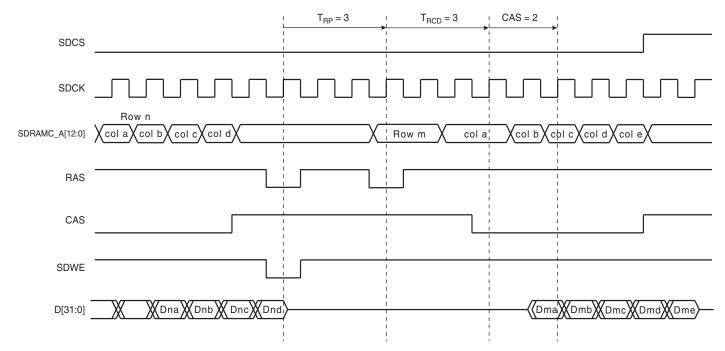

## 28.4 USB Clock Controller

The USB Source Clock is always generated from the PLL B output. If using the USB, the user must program the PLL to generate a 48 MHz, a 96 MHz or a 192 MHz signal with an accuracy of  $\pm$  0.25% depending on the USBDIV bit in CKGR\_PLLBR (see Figure 28-3).

When the PLL B output is stable, i.e., the LOCKB is set:

The USB host clock can be enabled by setting the UHP bit in PMC\_SCER. To save power on this peripheral when it is not used, the user can set the UHP bit in PMC\_SCDR. The UHP bit in PMC\_SCSR gives the activity of this clock. The USB host port require both the 12/48 MHz signal and the Master Clock. The Master Clock may be controlled via the Master Clock Controller.

## Figure 28-3. USB Clock Controller

## 28.5 Peripheral Clock Controller

The Power Management Controller controls the clocks of each embedded peripheral by the way of the Peripheral Clock Controller. The user can individually enable and disable the Master Clock on the peripherals by writing into the Peripheral Clock Enable (PMC\_PCER) and Peripheral Clock Disable (PMC\_PCDR) registers. The status of the peripheral clock activity can be read in the Peripheral Clock Status Register (PMC\_PCSR).

When a peripheral clock is disabled, the clock is immediately stopped. The peripheral clocks are automatically disabled after a reset.

In order to stop a peripheral, it is recommended that the system software wait until the peripheral has executed its last programmed operation before disabling the clock. This is to avoid data corruption or erroneous behavior of the system.

The bit number within the Peripheral Clock Control registers (PMC\_PCER, PMC\_PCDR, and PMC\_PCSR) is the Peripheral Identifier defined at the product level. Generally, the bit number corresponds to the interrupt source number assigned to the peripheral.

## 28.6 Programmable Clock Output Controller

The PMC controls 2 signals to be output on external pins PCKx. Each signal can be independently programmed via the PMC\_PCKx registers.

PCKx can be independently selected between the Slow clock, the PLL A output, the PLL B output and the main clock by writing the CSS field in PMC\_PCKx. Each output signal can also be divided by a power of 2 between 1 and 64 by writing the PRES (Prescaler) field in PMC\_PCKx.

Each output signal can be enabled and disabled by writing 1 in the corresponding bit, PCKx of PMC\_SCER and PMC\_SCDR, respectively. Status of the active programmable output clocks are given in the PCKx bits of PMC\_SCSR (System Clock Status Register).

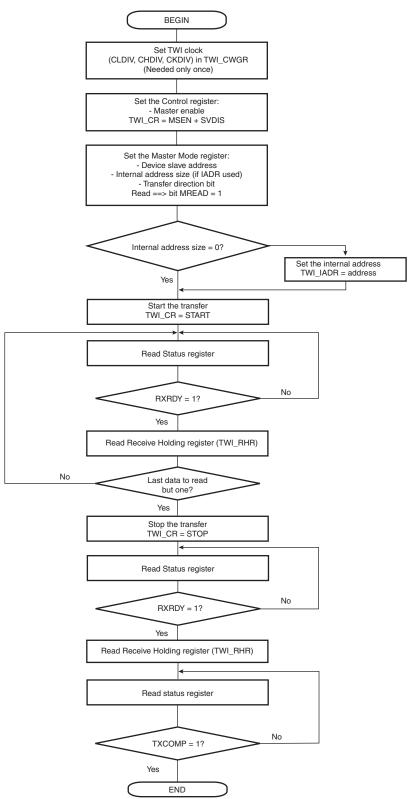

Figure 33-20. TWI Read Operation with Multiple Data Bytes with or without Internal Address

## • SVEN: TWI Slave Mode Enabled

0 = No effect.

1 = If SVDIS = 0, the slave mode is enabled.

Note: Switching from Master to Slave mode is only permitted when TXCOMP = 1.

#### • SVDIS: TWI Slave Mode Disabled

0 = No effect.

1 = The slave mode is disabled. The shifter and holding characters (if it contains data) are transmitted in case of read operation. In write operation, the character being transferred must be completely received before disabling.

#### • QUICK: SMBUS Quick Command

0 = No effect.

1 = If Master mode is enabled, a SMBUS Quick Command is sent.

#### • SWRST: Software Reset

0 = No effect.

1 = Equivalent to a system reset.

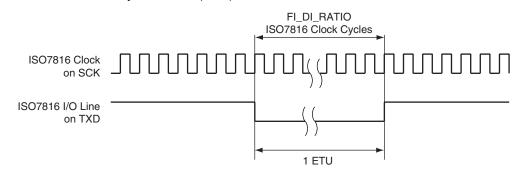

Figure 34-5. Elementary Time Unit (ETU)

#### 34.6.2 Receiver and Transmitter Control

After reset, the receiver is disabled. The user must enable the receiver by setting the RXEN bit in the Control Register (US\_CR). However, the receiver registers can be programmed before the receiver clock is enabled.

After reset, the transmitter is disabled. The user must enable it by setting the TXEN bit in the Control Register (US\_CR). However, the transmitter registers can be programmed before being enabled.

The Receiver and the Transmitter can be enabled together or independently.

At any time, the software can perform a reset on the receiver or the transmitter of the USART by setting the corresponding bit, RSTRX and RSTTX respectively, in the Control Register (US\_CR). The software resets clear the status flag and reset internal state machines but the user interface configuration registers hold the value configured prior to software reset. Regardless of what the receiver or the transmitter is performing, the communication is immediately stopped.

The user can also independently disable the receiver or the transmitter by setting RXDIS and TXDIS respectively in US\_CR. If the receiver is disabled during a character reception, the USART waits until the end of reception of the current character, then the reception is stopped. If the transmitter is disabled while it is operating, the USART waits the end of transmission of both the current character and character being stored in the Transmit Holding Register (US\_THR). If a timeguard is programmed, it is handled normally.

#### 34.6.3 Synchronous and Asynchronous Modes

#### 34.6.3.1 Transmitter Operations

The transmitter performs the same in both synchronous and asynchronous operating modes (SYNC = 0 or SYNC = 1). One start bit, up to 9 data bits, one optional parity bit and up to two stop bits are successively shifted out on the TXD pin at each falling edge of the programmed serial clock.

The number of data bits is selected by the CHRL field and the MODE 9 bit in the Mode Register (US\_MR). Nine bits are selected by setting the MODE 9 bit regardless of the CHRL field. The parity bit is set according to the PAR field in US\_MR. The even, odd, space, marked or none parity bit can be configured. The MSBF field in US\_MR configures which data bit is sent first. If written at 1, the most significant bit is sent first. At 0, the less significant bit is sent first. The number of stop bits is selected by the NBSTOP field in US\_MR. The 1.5 stop bit is supported in asynchronous mode only.

#### 35.6.5 Frame Sync

The Transmitter and Receiver Frame Sync pins, TF and RF, can be programmed to generate different kinds of frame synchronization signals. The Frame Sync Output Selection (FSOS) field in the Receive Frame Mode Register (SSC\_RFMR) and in the Transmit Frame Mode Register (SSC\_TFMR) are used to select the required waveform.

• Programmable low or high levels during data transfer are supported.

• Programmable high levels before the start of data transfers or toggling are also supported.

If a pulse waveform is selected, the Frame Sync Length (FSLEN) field in SSC\_RFMR and SSC\_TFMR programs the length of the pulse, from 1 bit time up to 16 bit time.

The periodicity of the Receive and Transmit Frame Sync pulse output can be programmed through the Period Divider Selection (PERIOD) field in SSC\_RCMR and SSC\_TCMR.

#### 35.6.5.1 Frame Sync Data

Frame Sync Data transmits or receives a specific tag during the Frame Sync signal.

During the Frame Sync signal, the Receiver can sample the RD line and store the data in the Receive Sync Holding Register and the transmitter can transfer Transmit Sync Holding Register in the Shifter Register. The data length to be sampled/shifted out during the Frame Sync signal is programmed by the FSLEN field in SSC\_RFMR/SSC\_TFMR and has a maximum value of 16.

Concerning the Receive Frame Sync Data operation, if the Frame Sync Length is equal to or lower than the delay between the start event and the actual data reception, the data sampling operation is performed in the Receive Sync Holding Register through the Receive Shift Register.

The Transmit Frame Sync Operation is performed by the transmitter only if the bit Frame Sync Data Enable (FSDEN) in SSC\_TFMR is set. If the Frame Sync length is equal to or lower than the delay between the start event and the actual data transmission, the normal transmission has priority and the data contained in the Transmit Sync Holding Register is transferred in the Transmit Register, then shifted out.

#### 35.6.5.2 Frame Sync Edge Detection

The Frame Sync Edge detection is programmed by the FSEDGE field in SSC\_RFMR/SSC\_TFMR. This sets the corresponding flags RXSYN/TXSYN in the SSC Status Register (SSC\_SR) on frame synchro edge detection (signals RF/TF).

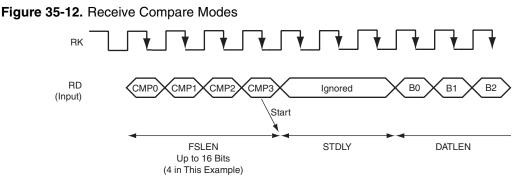

#### 35.6.6 Receive Compare Modes

#### RXBUFF: Receive Buffer Full Interrupt Mask

0 = The Receive Buffer Full Interrupt is disabled.

1 = The Receive Buffer Full Interrupt is enabled.

#### • CP0: Compare 0 Interrupt Mask

0 = The Compare 0 Interrupt is disabled.

1 = The Compare 0 Interrupt is enabled.

#### • CP1: Compare 1 Interrupt Mask

0 = The Compare 1 Interrupt is disabled.

1 = The Compare 1 Interrupt is enabled.

#### • TXSYN: Tx Sync Interrupt Mask

0 = The Tx Sync Interrupt is disabled.

1 = The Tx Sync Interrupt is enabled.

#### • RXSYN: Rx Sync Interrupt Mask

0 = The Rx Sync Interrupt is disabled.

1 = The Rx Sync Interrupt is enabled.

## 36.6.5 TC Channel Mode Register: Waveform Mode

**Register Name:** TC\_CMRx [x=0..2] (WAVE = 1)

Addresses: 0xFFFA0004 (0)[0], 0xFFFA0044 (0)[1], 0xFFFA0084 (0)[2], 0xFFFDC004 (1)[0], 0xFFFDC044 (1)[1], 0xFFFDC084 (1)[2]

### Access Type: Read-write

| 31     | 30      | 29   | 28     | 27   | 26        | 25  | 24   |

|--------|---------|------|--------|------|-----------|-----|------|

| BSW    | /TRG    | B    | EEVT   | BC   | PC BCPB   |     | PB   |

| 23     | 22      | 21   | 20     | 19   | 18        | 17  | 16   |

| ASW    | /TRG    | A    | EEVT   | AC   | ACPC ACPA |     | CPA  |

| 15     | 14      | 13   | 12     | 11   | 10        | 9   | 8    |

| WAVE   | WAW     | /SEL | ENETRG | EE   | VT        | EEV | TEDG |

| 7      | 6       | 5    | 4      | 3    | 2         | 1   | 0    |

| CPCDIS | CPCSTOP | BI   | JRST   | CLKI | TCCLKS    |     |      |

#### • TCCLKS: Clock Selection

|   | TCCLKS |   |              |  |  |  |

|---|--------|---|--------------|--|--|--|

| 0 | 0      | 0 | TIMER_CLOCK1 |  |  |  |

| 0 | 0      | 1 | TIMER_CLOCK2 |  |  |  |

| 0 | 1      | 0 | TIMER_CLOCK3 |  |  |  |

| 0 | 1      | 1 | TIMER_CLOCK4 |  |  |  |

| 1 | 0      | 0 | TIMER_CLOCK5 |  |  |  |

| 1 | 0      | 1 | XC0          |  |  |  |

| 1 | 1      | 0 | XC1          |  |  |  |

| 1 | 1      | 1 | XC2          |  |  |  |

## CLKI: Clock Invert

0 = Counter is incremented on rising edge of the clock.

1 = Counter is incremented on falling edge of the clock.

#### • BURST: Burst Signal Selection

| BURST |   |                                               |

|-------|---|-----------------------------------------------|

| 0     | 0 | The clock is not gated by an external signal. |

| 0     | 1 | XC0 is ANDed with the selected clock.         |

| 1     | 0 | XC1 is ANDed with the selected clock.         |

| 1     | 1 | XC2 is ANDed with the selected clock.         |

#### • CPCSTOP: Counter Clock Stopped with RC Compare

0 = Counter clock is not stopped when counter reaches RC.

1 = Counter clock is stopped when counter reaches RC.

| Register Name: | EMAC_  | IBQP |    |    |    |    |    |

|----------------|--------|------|----|----|----|----|----|

| Address:       | 0xFFFC | 401C |    |    |    |    |    |

| Access Type:   | Read-w | rite |    |    |    |    |    |

| 31             | 30     | 29   | 28 | 27 | 26 | 25 | 24 |

|                |        |      | AD | DR |    |    |    |

| 23             | 22     | 21   | 20 | 19 | 18 | 17 | 16 |

|                |        |      | AD | DR |    |    |    |

| 15             | 14     | 13   | 12 | 11 | 10 | 9  | 8  |

|                |        |      | AD | DR |    |    |    |

| 7              | 6      | 5    | 4  | 3  | 2  | 1  | 0  |

|                |        | AD   | DR |    |    | -  | -  |

## 38.5.6 Transmit Buffer Queue Pointer Register

This register points to the entry in the transmit buffer queue (descriptor list) currently being used. It is written with the start location of the transmit buffer descriptor list. The lower order bits increment as buffers are used up and wrap to their original values after either 1024 buffers or when the wrap bit of the entry is set. This register can only be written when bit 3 in the transmit status register is low.

As transmit buffer reads consist of bursts of two words, it is recommended that bit 2 is always written with zero to prevent a burst crossing a 1K boundary, in violation of section 3.6 of the AMBA specification.

## • ADDR: Transmit buffer queue pointer address

Written with the address of the start of the transmit queue, reads as a pointer to the first buffer of the frame being transmitted or about to be transmitted.

## 38.5.24 Type ID Checking Register

| Register Name | EMAC_  | TID   |    |    |    |    |    |

|---------------|--------|-------|----|----|----|----|----|

| Address:      | 0xFFFC | C40B8 |    |    |    |    |    |

| Access Type:  | Read-w | /rite |    |    |    |    |    |

| 31            | 30     | 29    | 28 | 27 | 26 | 25 | 24 |

| -             | -      | -     | -  | -  | -  | _  | -  |

| 23            | 22     | 21    | 20 | 19 | 18 | 17 | 16 |

| -             | _      | -     | -  | -  | -  | _  | -  |

| 15            | 14     | 13    | 12 | 11 | 10 | 9  | 8  |

|               |        |       | Т  | ID |    |    |    |

| 7             | 6      | 5     | 4  | 3  | 2  | 1  | 0  |

|               |        |       | Т  | ID |    |    |    |

## • TID: Type ID checking

For use in comparisons with received frames TypeID/Length field.

## 38.5.25 User Input/Output Register

| Register Name | : EMAC_ | EMAC_USRIO |    |    |    |       |      |  |

|---------------|---------|------------|----|----|----|-------|------|--|

| Address:      | 0xFFFC  | 40C0       |    |    |    |       |      |  |

| Access Type:  | Read-w  | rite       |    |    |    |       |      |  |

| 31            | 30      | 29         | 28 | 27 | 26 | 25    | 24   |  |

| -             | -       | -          | -  | _  | -  | -     | -    |  |

| 23            | 22      | 21         | 20 | 19 | 18 | 17    | 16   |  |

| -             | —       | -          | -  | _  | -  | -     | -    |  |

| 15            | 14      | 13         | 12 | 11 | 10 | 9     | 8    |  |

| -             | —       | -          | -  | -  | —  | -     | -    |  |

| 7             | 6       | 5          | 4  | 3  | 2  | 1     | 0    |  |

| -             | _       | -          | -  | -  | —  | CLKEN | RMII |  |

|               |         |            |    |    |    |       |      |  |

#### • RMII

When set, this bit enables the RMII operation mode. When reset, it selects the MII mode.

## • CLKEN

When set, this bit enables the transceiver input clock.

Setting this bit to 0 reduces power consumption when the treasurer is not used.

The USB device sets this bit when a UDP resume signal is detected at its port.

After reset, the state of this bit is undefined, the application must clear this bit by setting the RXRSM flag in the UDP\_ICR register.

## EXTRSM: UDP External Resume Interrupt Status

0 = No UDP External Resume Interrupt pending.

1 = UDP External Resume Interrupt has been raised.

## • SOFINT: Start of Frame Interrupt Status

0 = No Start of Frame Interrupt pending.

1 = Start of Frame Interrupt has been raised.

This interrupt is raised each time a SOF token has been detected. It can be used as a synchronization signal by using

isochronous endpoints.

## • ENDBUSRES: End of BUS Reset Interrupt Status

0 = No End of Bus Reset Interrupt pending.

1 = End of Bus Reset Interrupt has been raised.

This interrupt is raised at the end of a UDP reset sequence. The USB device must prepare to receive requests on the endpoint 0. The host starts the enumeration, then performs the configuration.

## • WAKEUP: UDP Resume Interrupt Status

0 = No Wakeup Interrupt pending.

1 = A Wakeup Interrupt (USB Host Sent a RESUME or RESET) occurred since the last clear.

After reset the state of this bit is undefined, the application must clear this bit by setting the WAKEUP flag in the UDP\_ICR register

## 39.6.11 UDP FIFO Data Register

| Register Name | : UDP_FI | UDP_FDRx [x = 05] |       |       |    |    |    |  |  |

|---------------|----------|-------------------|-------|-------|----|----|----|--|--|

| Address:      | 0xFFFA   | 404C              |       |       |    |    |    |  |  |

| Access Type:  | Read-    | write             |       |       |    |    |    |  |  |

| 31            | 30       | 29                | 28    | 27    | 26 | 25 | 24 |  |  |

| -             | —        | -                 | -     | —     | —  | _  | —  |  |  |

| 23            | 22       | 21                | 20    | 19    | 18 | 17 | 16 |  |  |

| _             | _        | _                 | _     | —     | _  | —  | —  |  |  |

| 15            | 14       | 13                | 12    | 11    | 10 | 9  | 8  |  |  |

| _             | _        | _                 | _     | _     | _  | _  | -  |  |  |

| 7             | 6        | 5                 | 4     | 3     | 2  | 1  | 0  |  |  |

|               |          |                   | FIFO_ | _DATA |    |    |    |  |  |

#### • FIFO\_DATA[7:0]: FIFO Data Value

The microcontroller can push or pop values in the FIFO through this register.

RXBYTECNT in the corresponding UDP\_CSRx register is the number of bytes to be read from the FIFO (sent by the host).

The maximum number of bytes to write is fixed by the Max Packet Size in the Standard Endpoint Descriptor. It can not be more than the physical memory size associated to the endpoint. Refer to the *Universal Serial Bus Specification, Rev. 2.0* for more information.

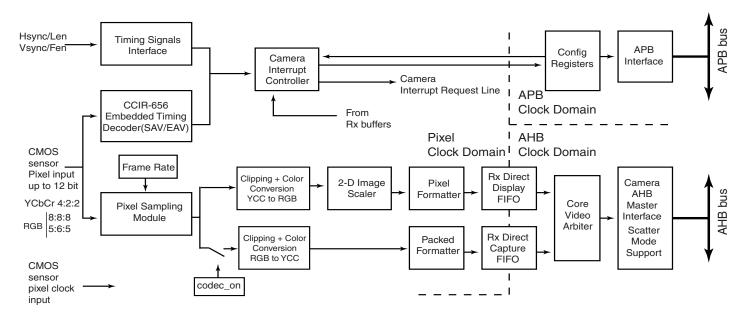

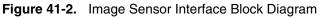

## 41.2 Block Diagram

## 41.3 Functional Description

The Image Sensor Interface (ISI) supports direct connection to the ITU-R BT. 601/656 8-bit mode compliant sensors and up to 12-bit grayscale sensors. It receives the image data stream from the image sensor on the 12-bit data bus.

This module receives up to 12 bits for data, the horizontal and vertical synchronizations and the pixel clock. The reduced pin count alternative for synchronization is supported for sensors that embed SAV (start of active video) and EAV (end of active video) delimiters in the data stream.

The Image Sensor Interface interrupt line is generally connected to the Advanced Interrupt Controller and can trigger an interrupt at the beginning of each frame and at the end of a DMA frame transfer. If the SAV/EAV synchronization is used, an interrupt can be triggered on each delimiter event.

For 8-bit color sensors, the data stream received can be in several possible formats: YCbCr 4:2:2, RGB 8:8:8, RGB 5:6:5 and may be processed before the storage in memory. The data stream may be sent on both preview path and codec path if the bit CODEC\_ON in the ISI\_CR1 is one. To optimize the bandwidth, the codec path should be enabled only when a capture is required.

In grayscale mode, the input data stream is stored in memory without any processing. The 12-bit data, which represent the grayscale level for the pixel, is stored in memory one or two pixels per word, depending on the GS\_MODE bit in the ISI\_CR2 register. The data is stored via the preview path without any treatment (scaling, color conversion,...). The size of the sensor must be programmed in the fields IM\_VSIZE and IM\_HSIZE in the ISI\_CR2 register. The programming of the preview path register (ISI\_PSIZE) is not necessary. The codec datapath is not available when grayscale image is selected.

A frame rate counter allows users to capture all frames or 1 out of every 2 to 8 frames.

# 750 AT91SAM9XE128/256/512 Preliminary

## 42.6.8 ADC Interrupt Enable Register

| Register Name | and preserve and a second preserve and a sec | -    |    |        |       |       |       |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|--------|-------|-------|-------|

| Address:      | 0xFFFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0024 |    |        |       |       |       |

| Access Type:  | Write-or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nly  |    |        |       |       |       |

| 31            | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29   | 28 | 27     | 26    | 25    | 24    |

| -             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _    | -  | -      | -     | -     | -     |

| 23            | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21   | 20 | 19     | 18    | 17    | 16    |

| -             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _    | -  | RXBUFF | ENDRX | GOVRE | DRDY  |

| 15            | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13   | 12 | 11     | 10    | 9     | 8     |

| -             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _    | -  | OVRE3  | OVRE2 | OVRE1 | OVRE0 |

| 7             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5    | 4  | 3      | 2     | 1     | 0     |

| -             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | -  | EOC3   | EOC2  | EOC1  | EOC0  |

• EOCx: End of Conversion Interrupt Enable x

• OVREx: Overrun Error Interrupt Enable x

DRDY: Data Ready Interrupt Enable

- GOVRE: General Overrun Error Interrupt Enable

- ENDRX: End of Receive Buffer Interrupt Enable

- RXBUFF: Receive Buffer Full Interrupt Enable

0 = No effect.

1 = Enables the corresponding interrupt.

| 29 | Advar  | nced Interrupt Controller (AIC)                       | 349 |

|----|--------|-------------------------------------------------------|-----|

|    | 29.1   | Description                                           |     |

|    | 29.2   | Block Diagram                                         | 350 |

|    | 29.3   | Application Block Diagram                             | 350 |

|    | 29.4   | AIC Detailed Block Diagram                            | 350 |

|    | 29.5   | I/O Line Description                                  | 351 |

|    | 29.6   | Product Dependencies                                  | 351 |

|    | 29.7   | Functional Description                                | 352 |

|    | 29.8   | Advanced Interrupt Controller (AIC) User Interface    |     |

| 30 | Debu   | g Unit (DBGU)                                         | 373 |

|    | 30.1   | Description                                           |     |

|    | 30.2   | Block Diagram                                         | 374 |

|    | 30.3   | Product Dependencies                                  | 375 |

|    | 30.4   | UART Operations                                       | 375 |

|    | 30.5   | Debug Unit (DBGU) User Interface                      |     |

| 31 | Parall | lel Input/Output Controller (PIO)                     | 397 |

|    | 31.1   | Description                                           |     |

|    | 31.2   | Block Diagram                                         |     |

|    | 31.3   | Product Dependencies                                  |     |

|    | 31.4   | Functional Description                                | 400 |

|    | 31.5   | I/O Lines Programming Example                         | 404 |

|    | 31.6   | Parallel Input/Output Controller (PIO) User Interface | 406 |

| 32 | Serial | Peripheral Interface (SPI)                            | 423 |

|    | 32.1   | Description                                           | 423 |

|    | 32.2   | Block Diagram                                         | 424 |

|    | 32.3   | Application Block Diagram                             | 424 |

|    | 32.4   | Signal Description                                    | 425 |

|    | 32.5   | Product Dependencies                                  | 425 |

|    | 32.6   | Functional Description                                | 426 |

|    | 32.7   | Serial Peripheral Interface (SPI) User Interface      | 436 |

| 33 | Two-v  | wire Interface (TWI)                                  | 449 |

|    | 33.1   | Description                                           | 449 |

|    | 33.2   | List of Abbreviations                                 | 449 |

|    | 33.3   | Block Diagram                                         | 450 |

|    | 33.4   | Application Block Diagram                             | 450 |

|    |        |                                                       |     |

# AT91SAM9XE128/256/512 Preliminary