# E·XFL

### Atmel - AT91SAM9XE128-QU Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                    |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 180MHz                                                      |

| Co-Processors/DSP               | -                                                           |

| RAM Controllers                 | SDRAM, SRAM                                                 |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | LCD, Touchscreen                                            |

| Ethernet                        | 10/100Mbps                                                  |

| SATA                            | -                                                           |

| USB                             | USB 2.0 (3)                                                 |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | -40°C ~ 85°C (TA)                                           |

| Security Features               | -                                                           |

| Package / Case                  | 208-BFQFP                                                   |

| Supplier Device Package         | 208-PQFP (28x28)                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/atmel/at91sam9xe128-qu |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 11.3.7 ARM9EJ-S Registers

The ARM9EJ-S core has a total of 37 registers.

- 31 general-purpose 32-bit registers

- 6 32-bit status registers

Table 11-2 shows all the registers in all modes.

| Table 11-2.         ARM9TDMI Modes and Registers Layout |

|---------------------------------------------------------|

|---------------------------------------------------------|

| User and<br>System Mode | Supervisor<br>Mode | Abort Mode | Undefined<br>Mode | Interrupt<br>Mode | Fast Interrupt<br>Mode |

|-------------------------|--------------------|------------|-------------------|-------------------|------------------------|

| R0                      | R0                 | R0         | R0                | R0                | R0                     |

| R1                      | R1                 | R1         | R1                | R1                | R1                     |

| R2                      | R2                 | R2         | R2                | R2                | R2                     |

| R3                      | R3                 | R3         | R3                | R3                | R3                     |

| R4                      | R4                 | R4         | R4                | R4                | R4                     |

| R5                      | R5                 | R5         | R5                | R5                | R5                     |

| R6                      | R6                 | R6         | R6                | R6                | R6                     |

| R7                      | R7                 | R7         | R7                | R7                | R7                     |

| R8                      | R8                 | R8         | R8                | R8                | R8_FIQ                 |

| R9                      | R9                 | R9         | R9                | R9                | R9_FIQ                 |

| R10                     | R10                | R10        | R10               | R10               | R10_FIQ                |

| R11                     | R11                | R11        | R11               | R11               | R11_FIQ                |

| R12                     | R12                | R12        | R12               | R12               | R12_FIQ                |

| R13                     | R13_SVC            | R13_ABORT  | R13_UNDEF         | R13_IRQ           | R13_FIQ                |

| R14                     | R14_SVC            | R14_ABORT  | R14_UNDEF         | R14_IRQ           | R14_FIQ                |

| PC                      | PC                 | PC         | PC                | PC                | PC                     |

| CPSR | CPSR     | CPSR           | CPSR           | CPSR     | CPSR     |

|------|----------|----------------|----------------|----------|----------|

|      | SPSR_SVC | SPSR_ABOR<br>T | SPSR_UNDE<br>F | SPSR_IRQ | SPSR_FIQ |

Mode-specific banked registers

The ARM state register set contains 16 directly-accessible registers, r0 to r15, and an additional register, the Current Program Status Register (CPSR). Registers r0 to r13 are general-purpose registers used to hold either data or address values. Register r14 is used as a Link register that holds a value (return address) of r15 when BL or BLX is executed. Register r15 is used as a program counter (PC), whereas the Current Program Status Register (CPSR) contains condition code flags and the current mode bits.

In privileged modes (FIQ, Supervisor, Abort, IRQ, Undefined), mode-specific banked registers (r8 to r14 in FIQ mode or r13 to r14 in the other modes) become available. The corresponding banked registers r14\_fiq, r14\_svc, r14\_abt, r14\_irq, r14\_und are similarly used to hold the val-

#### 13.4.4 In-Application Programming (IAP) Feature

The IAP feature is a function located in ROM that can be called by any software application.

When called, this function sends the desired FLASH command to the EEFC and waits for the FLASH to be ready (looping while the FRDY bit is not set in the MC\_FSR register).

Since this function is executed from ROM, this allows FLASH programming (like sector write) to be done by code running in FLASH.

The IAP function entry point is retrieved by reading the SWI vector in ROM (0x100008).

This function takes one argument in parameter: the command to be sent to the EEFC.

This function returns the value of the MC\_FSR register.

IAP software code example:

```

(unsigned int) (*IAP_Function)(unsigned long);

void main (void)

{

unsigned long FlashSectorNum = 200;

unsigned long flash_cmd = 0;

unsigned long flash_status = 0;

/* Initialize the function pointer (retrieve function address from SWI

vector) */

IAP_Function = ((unsigned long) (*)(unsigned long)) 0x100008;

/* Send your data to the sector */

/* build the command to send to EFC */

flash_cmd = (0x5A << 24) | (FlashSectorNum << 8) | AT91C_MC_FCMD_EWP;

/* Call the IAP function with appropriate command */

flash_status = IAP_Function (flash_cmd);

}

```

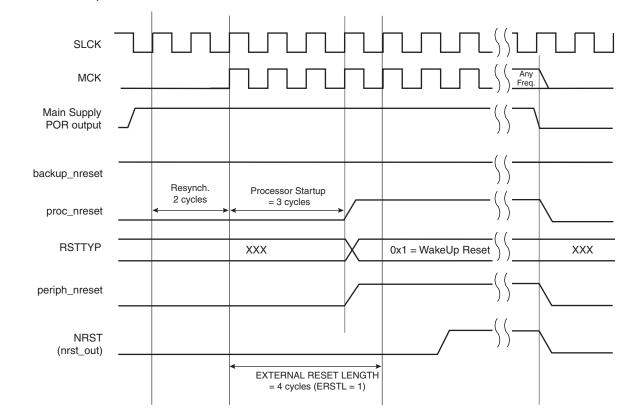

#### 15.3.4.2 Wake-up Reset

The Wake-up Reset occurs when the Main Supply is down. When the Main Supply POR output is active, all the reset signals are asserted except backup\_nreset. When the Main Supply powers up, the POR output is resynchronized on Slow Clock. The processor clock is then re-enabled during 3 Slow Clock cycles, depending on the requirements of the ARM processor.

At the end of this delay, the processor and other reset signals rise. The field RSTTYP in RSTC\_SR is updated to report a Wake-up Reset.

The "nrst\_out" remains asserted for EXTERNAL\_RESET\_LENGTH cycles. As RSTC\_MR is backed-up, the programmed number of cycles is applicable.

When the Main Supply is detected falling, the reset signals are immediately asserted. This transition is synchronous with the output of the Main Supply POR.

Figure 15-5. Wake-up State

15.3.4.3 User Reset

The User Reset is entered when a low level is detected on the NRST pin and the bit URSTEN in RSTC\_MR is at 1. The NRST input signal is resynchronized with SLCK to insure proper behavior of the system.

The User Reset is entered as soon as a low level is detected on NRST. The Processor Reset and the Peripheral Reset are asserted.

The User Reset is left when NRST rises, after a two-cycle resynchronization time and a 3-cycle processor startup. The processor clock is re-enabled as soon as NRST is confirmed high.

| Master Clock                            |                               |                                                     |                            |                        |                            |

|-----------------------------------------|-------------------------------|-----------------------------------------------------|----------------------------|------------------------|----------------------------|

| ARM Request<br>(32-bit)                 | 1                             |                                                     | 16 @20 @24 @28             |                        | @44 @48 @52                |

| Flash Access                            | @Byte 0                       | @4 @8 @12 @                                         |                            | @32 @36 @40<br>32-47 X | @44 @48 @52<br>Bytes 48-63 |

| Buffer 0 (128bits)                      | XXX                           | _χ                                                  | Bytes 0-15                 | X                      | Bytes 32-47                |

| Buffer 1 (128bits)                      | XX                            | XX                                                  | X                          | Bytes 16               | -31                        |

| Data To ARM                             | Xxxx                          | <b>X</b> 0-3 <b>X</b> 4-7 <b>X</b> 8-11 <b>X</b> 12 | 2-15 16-19 20-23 24-27     | 28-31 32-35 36-39      | 40-43 44-47 48-51          |

| Note: When FWS<br>1 cycle.              | S is included between 1 and 3 | , in case of sequentia                              | reads, the first access t  | akes (FWS+1) cycle     | es, the other ones only    |

| -                                       | de Read Optimization in A     | RM Mode for FWS                                     | = 4<br>) [] [] [] [] [] [] |                        |                            |

| Master Clock<br>ARM Request<br>(32-bit) | _] [_] [_] [_] [_]<br>Byte 0  | @4 @8 @12                                           | € € € € € € € €            | @28 @32                | @36 @40                    |

| Flash Access                            | Bytes 0-15                    | ХВу                                                 | tes 16-31                  | Bytes 32-47            | Bytes 48-63                |

| Buffer 0 (128bits)                      | X xxx                         | Χ                                                   | Bytes 0-15                 |                        | Bytes 32-47                |

| Buffer 1 (128bits)                      | χ                             | XXX                                                 | X                          | Bytes 16-31            | 1                          |

| Data To ARM                             | X xxx                         | 0-3 4-7 8-11                                        | (12-15) (16-19) (20-2      | 3 24-27 28-31          | 32-35 36-39                |

**Figure 20-3.** Code Read Optimization in ARM Mode for FWS = 3

Note: When FWS is included between 4 and 10, in case of sequential reads, the first access takes (FWS+1) cycles, each first access of the 128-bit read (FWS-2) cycles, and the others only 1 cycle.

|                 | Access to CompactFlash Device | Access to Other EBI Devices |

|-----------------|-------------------------------|-----------------------------|

| Pins            | CompactFlash Signals          | EBI Signals                 |

| NRD/CFOE        | CFOE                          | NRD                         |

| NWR0/NWE/CFWE   | CFWE                          | NWR0/NWE                    |

| NWR1/NBS1/CFIOR | CFIOR                         | NWR1/NBS1                   |

| NWR3/NBS3/CFIOW | CFIOW                         | NWR3/NBS3                   |

| A25/CFRNW       | CFRNW                         | A25                         |

Table 22-9. Shared CompactFlash Interface Multiplexing

#### 22.6.6.5 Application Example

Figure 22-5 on page 182 illustrates an example of a CompactFlash application. CFCS0 and CFRNW signals are not directly connected to the CompactFlash slot 0, but do control the direction and the output enable of the buffers between the EBI and the CompactFlash Device. The timing of the CFCS0 signal is identical to the NCS4 signal. Moreover, the CFRNW signal remains valid throughout the transfer, as does the address bus. The CompactFlash \_WAIT signal is connected to the NWAIT input of the Static Memory Controller. For details on these waveforms and timings, refer to the Static Memory Controller Section.

1 = Errors Detected. If MUL\_ERROR is 0, a single correctable error was detected. Otherwise multiple uncorrected errors were detected.

#### • ECCERR12: ECC Error in the page between the 3072nd and the 3327th bytes

Fixed to 0 if TYPECORREC = 0

0 = No Errors Detected

1 = A single bit error occurred in the ECC bytes.

Read ECC Parity 12 register, the error occurred at the location which contains a 1 in the least significant 24 bits.

#### • MULERR12: Multiple Error in the page between the 3072nd and the 3327th bytes

Fixed to 0 if TYPECORREC = 0.

0 = No Multiple Errors Detected.

1 = Multiple Errors Detected.

#### • RECERR13: Recoverable Error in the page between the 3328th and the 3583rd bytes

Fixed to 0 if TYPECORREC = 0.

0 = No Errors Detected.

1 = Errors Detected. If MUL\_ERROR is 0, a single correctable error was detected. Otherwise multiple uncorrected errors were detected.

#### • ECCERR13: ECC Error in the page between the 3328th and the 3583rd bytes

Fixed to 0 if TYPECORREC = 0.

0 = No Errors Detected.

1 = A single bit error occurred in the ECC bytes.

Read ECC Parity 13 register, the error occurred at the location which contains a 1 in the least significant 24 bits.

#### • MULERR13: Multiple Error in the page between the 3328th and the 3583rd bytes

Fixed to 0 if TYPECORREC = 0.

0 = No Multiple Errors Detected.

1 = Multiple Errors Detected.

#### • RECERR14: Recoverable Error in the page between the 3584th and the 3839th bytes

Fixed to 0 if TYPECORREC = 0.

0 = No Errors Detected.

1 = Errors Detected. If MUL\_ERROR is 0, a single correctable error was detected. Otherwise, multiple uncorrected errors were detected.

#### • ECCERR14: ECC Error in the page between the 3584th and the 3839th bytes

Fixed to 0 if TYPECORREC = 0.

0 = No Errors Detected.

1 = A single bit error occurred in the ECC bytes.

Read ECC Parity 14 register, the error occurred at the location which contains a 1 in the least significant 24 bits.

| 25.7.3 ECC Par<br>Register Name: | rity Register 2<br>ECC_PR2 |           |    |          |    |          |    |

|----------------------------------|----------------------------|-----------|----|----------|----|----------|----|

| Address:                         | 0xFFFFE81                  | 18        |    |          |    |          |    |

| Access Type:                     | Read-only                  |           |    |          |    |          |    |

| 31                               | 30                         | 29        | 28 | 27       | 26 | 25       | 24 |

| 23                               | 22                         | 21        | 20 | 19       | 18 | 17       | 16 |

| 0                                |                            |           |    | NPARITY2 |    |          |    |

| 15                               | 14                         | 13        | 12 | 11       | 10 | 9        | 8  |

|                                  | NPARIT                     | -Y2       |    | 0        |    | WORDADD2 |    |

| 7                                | 6                          | 5         | 4  | 3        | 2  | 1        | 0  |

|                                  | V                          | VORDADDR2 |    |          |    | BITADDR2 |    |

Once the entire main area of a page is written with data, the register content must be stored at any free location of the spare area.

#### • BITADDR2: corrupted Bit Address in the page between the 512th and the 767th bytes

During a page read, this value contains the corrupted bit offset where an error occurred, if a single error was detected. If multiple errors were detected, this value is meaningless.

#### • WORDADDR2: corrupted Word Address in the page between the 512th and the 767th bytes

During a page read, this value contains the word address (8-bit word) where an error occurred, if a single error was detected. If multiple errors were detected, this value is meaningless.

#### • NPARITY2:

Parity N

## 31. Parallel Input/Output Controller (PIO)

### 31.1 Description

The Parallel Input/Output Controller (PIO) manages up to 32 fully programmable input/output lines. Each I/O line may be dedicated as a general-purpose I/O or be assigned to a function of an embedded peripheral. This assures effective optimization of the pins of a product.

Each I/O line is associated with a bit number in all of the 32-bit registers of the 32-bit wide User Interface.

Each I/O line of the PIO Controller features:

- An input change interrupt enabling level change detection on any I/O line.

- A glitch filter providing rejection of pulses lower than one-half of clock cycle.

- Multi-drive capability similar to an open drain I/O line.

- Control of the the pull-up of the I/O line.

- Input visibility and output control.

The PIO Controller also features a synchronous output providing up to 32 bits of data output in a single write operation.

#### 31.6.17 PIO Controller Interrupt Status Register

| ess Type: | Read-or | nly |     |     |     |     |     |

|-----------|---------|-----|-----|-----|-----|-----|-----|

| 31        | 30      | 29  | 28  | 27  | 26  | 25  | 24  |

| P31       | P30     | P29 | P28 | P27 | P26 | P25 | P24 |

| 23        | 22      | 21  | 20  | 19  | 18  | 17  | 16  |

| P23       | P22     | P21 | P20 | P19 | P18 | P17 | P16 |

| 15        | 14      | 13  | 12  | 11  | 10  | 9   | 8   |

| P15       | P14     | P13 | P12 | P11 | P10 | P9  | P8  |

| 7         | 6       | 5   | 4   | 3   | 2   | 1   | 0   |

| P7        | P6      | P5  | P4  | P3  | P2  | P1  | P0  |

1 = At least one Input Change has been detected on the I/O line since PIO\_ISR was last read or since reset.

#### 31.6.18 PIO Multi-driver Enable Register

| Name:        | PIO_ME   | DER            |               |              |            |     |     |

|--------------|----------|----------------|---------------|--------------|------------|-----|-----|

| Addresses:   | 0xFFFF   | F450 (PIOA), C | xFFFFF650 (PI | OB), 0xFFFF8 | 850 (PIOC) |     |     |

| Access Type: | Write-or | nly            |               |              |            |     |     |

| 31           | 30       | 29             | 28            | 27           | 26         | 25  | 24  |

| P31          | P30      | P29            | P28           | P27          | P26        | P25 | P24 |

| 23           | 22       | 21             | 20            | 19           | 18         | 17  | 16  |

| P23          | P22      | P21            | P20           | P19          | P18        | P17 | P16 |

| 15           | 14       | 13             | 12            | 11           | 10         | 9   | 8   |

| P15          | P14      | P13            | P12           | P11          | P10        | P9  | P8  |

| 7            | 6        | 5              | 4             | 3            | 2          | 1   | 0   |

| P7           | P6       | P5             | P4            | P3           | P2         | P1  | P0  |

### • P0-P31: Multi Drive Enable.

0 = No effect.

1 = Enables Multi Drive on the I/O line.

#### 32.7.8 SPI Interrupt Mask Register

Name: SPI\_IMR

Addresses: 0xFFFC801C (0), 0xFFFCC01C (1)

Access Type: Read-only

| 31     | 30     | 29    | 28    | 27    | 26   | 25      | 24   |

|--------|--------|-------|-------|-------|------|---------|------|

| —      | _      | -     | —     | _     | _    | _       | _    |

| 23     | 22     | 21    | 20    | 19    | 18   | 17      | 16   |

| -      | _      | -     | -     | _     | —    | _       | _    |

| 15     | 14     | 13    | 12    | 11    | 10   | 9       | 8    |

| -      | _      |       | —     | -     | 0    | TXEMPTY | NSSR |

| 7      | 6      | 5     | 4     | 3     | 2    | 1       | 0    |

| TXBUFE | RXBUFF | ENDTX | ENDRX | OVRES | MODF | TDRE    | RDRF |

0 = The corresponding interrupt is not enabled.

1 = The corresponding interrupt is enabled.

- RDRF: Receive Data Register Full Interrupt Mask

- TDRE: SPI Transmit Data Register Empty Interrupt Mask

- MODF: Mode Fault Error Interrupt Mask

- OVRES: Overrun Error Interrupt Mask

- ENDRX: End of Receive Buffer Interrupt Mask

- ENDTX: End of Transmit Buffer Interrupt Mask

- RXBUFF: Receive Buffer Full Interrupt Mask

- TXBUFE: Transmit Buffer Empty Interrupt Mask

- NSSR: NSS Rising Interrupt Mask

- TXEMPTY: Transmission Registers Empty Mask

#### 33.7.7 Using the Peripheral DMA Controller (PDC)

The use of the PDC significantly reduces the CPU load.

To assure correct implementation, respect the following programming sequences:

#### 33.7.7.1 Data Transmit with the PDC

- 1. Initialize the transmit PDC (memory pointers, size, etc.).

- 2. Configure the master mode (DADR, CKDIV, etc.).

- 3. Start the transfer by setting the PDC TXTEN bit.

- 4. Wait for the PDC end TX flag.

- 5. Disable the PDC by setting the PDC TXDIS bit.

#### 33.7.7.2 Data Receive with the PDC

- 1. Initialize the receive PDC (memory pointers, size 1, etc.).

- 2. Configure the master mode (DADR, CKDIV, etc.).

- 3. Start the transfer by setting the PDC RXTEN bit.

- 4. Wait for the PDC end RX flag.

- 5. Disable the PDC by setting the PDC RXDIS bit.

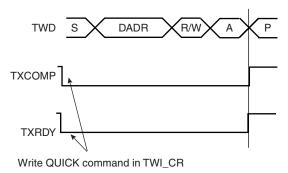

#### 33.7.8 SMBUS Quick Command (Master Mode Only)

The TWI interface can perform a Quick Command:

- 1. Configure the master mode (DADR, CKDIV, etc.).

- 2. Write the MREAD bit in the TWI\_MMR register at the value of the one-bit command to be sent.

- 3. Start the transfer by setting the QUICK bit in the TWI\_CR.

#### Figure 33-14. SMBUS Quick Command

Read-write Flowcharts

33.7.9

The following flowcharts shown in Figure 33-16 on page 460, Figure 33-17 on page 461, Figure 33-18 on page 462, Figure 33-19 on page 463 and Figure 33-20 on page 464 give examples for read and write operations. A polling or interrupt method can be used to check the status bits. The interrupt method requires that the interrupt enable register (TWI\_IER) be configured first.

# 458 AT91SAM9XE128/256/512 Preliminary

# AT91SAM9XE128/256/512 Preliminary

$$B = \frac{Di}{Fi} \times i$$

where:

- B is the bit rate

- Di is the bit-rate adjustment factor

- Fi is the clock frequency division factor

- f is the ISO7816 clock frequency (Hz)

Di is a binary value encoded on a 4-bit field, named DI, as represented in Table 34-3.

Table 34-3. Binary and Decimal Values for Di

| DI field     | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 1000 | 1001 |

|--------------|------|------|------|------|------|------|------|------|

| Di (decimal) | 1    | 2    | 4    | 8    | 16   | 32   | 12   | 20   |

Fi is a binary value encoded on a 4-bit field, named FI, as represented in Table 34-4.

Table 34-4. Binary and Decimal Values for Fi

| FI field    | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 1001 | 1010 | 1011 | 1100 | 1101 |

|-------------|------|------|------|------|------|------|------|------|------|------|------|------|

| Fi (decimal | 372  | 372  | 558  | 744  | 1116 | 1488 | 1860 | 512  | 768  | 1024 | 1536 | 2048 |

Table 34-5 shows the resulting Fi/Di Ratio, which is the ratio between the ISO7816 clock and the baud rate clock.

Table 34-5. Possible Values for the Fi/Di Ratio

| Fi/Di | 372   | 558   | 774   | 1116  | 1488 | 1806  | 512   | 768  | 1024  | 1536 | 2048  |

|-------|-------|-------|-------|-------|------|-------|-------|------|-------|------|-------|

| 1     | 372   | 558   | 744   | 1116  | 1488 | 1860  | 512   | 768  | 1024  | 1536 | 2048  |

| 2     | 186   | 279   | 372   | 558   | 744  | 930   | 256   | 384  | 512   | 768  | 1024  |

| 4     | 93    | 139.5 | 186   | 279   | 372  | 465   | 128   | 192  | 256   | 384  | 512   |

| 8     | 46.5  | 69.75 | 93    | 139.5 | 186  | 232.5 | 64    | 96   | 128   | 192  | 256   |

| 16    | 23.25 | 34.87 | 46.5  | 69.75 | 93   | 116.2 | 32    | 48   | 64    | 96   | 128   |

| 32    | 11.62 | 17.43 | 23.25 | 34.87 | 46.5 | 58.13 | 16    | 24   | 32    | 48   | 64    |

| 12    | 31    | 46.5  | 62    | 93    | 124  | 155   | 42.66 | 64   | 85.33 | 128  | 170.6 |

| 20    | 18.6  | 27.9  | 37.2  | 55.8  | 74.4 | 93    | 25.6  | 38.4 | 51.2  | 76.8 | 102.4 |

If the USART is configured in ISO7816 Mode, the clock selected by the USCLKS field in the Mode Register (US\_MR) is first divided by the value programmed in the field CD in the Baud Rate Generator Register (US\_BRGR). The resulting clock can be provided to the SCK pin to feed the smart card clock inputs. This means that the CLKO bit can be set in US\_MR.

This clock is then divided by the value programmed in the FI\_DI\_RATIO field in the FI\_DI\_Ratio register (US\_FIDI). This is performed by the Sampling Divider, which performs a division by up to 2047 in ISO7816 Mode. The non-integer values of the Fi/Di Ratio are not supported and the user must program the FI\_DI\_RATIO field to a value as close as possible to the expected value.

The FI\_DI\_RATIO field resets to the value 0x174 (372 in decimal) and is the most common divider between the ISO7816 clock and the bit rate (Fi = 372, Di = 1).

Figure 34-5 shows the relation between the Elementary Time Unit, corresponding to a bit time, and the ISO 7816 clock.

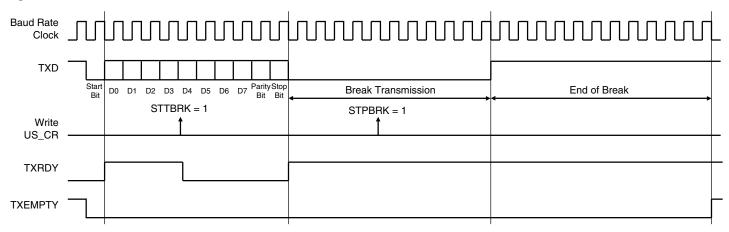

The transmitter considers the break as though it is a character, i.e. the STTBRK and STPBRK commands are taken into account only if the TXRDY bit in US\_CSR is at 1 and the start of the break condition clears the TXRDY and TXEMPTY bits as if a character is processed.

Writing US\_CR with the both STTBRK and STPBRK bits at 1 can lead to an unpredictable result. All STPBRK commands requested without a previous STTBRK command are ignored. A byte written into the Transmit Holding Register while a break is pending, but not started, is ignored.

After the break condition, the transmitter returns the TXD line to 1 for a minimum of 12 bit times. Thus, the transmitter ensures that the remote receiver detects correctly the end of break and the start of the next character. If the timeguard is programmed with a value higher than 12, the TXD line is held high for the timeguard period.

After holding the TXD line for this period, the transmitter resumes normal operations.

Figure 34-26 illustrates the effect of both the Start Break (STTBRK) and Stop Break (STPBRK) commands on the TXD line.

#### Figure 34-26. Break Transmission

#### 34.6.3.15 Receive Break

The receiver detects a break condition when all data, parity and stop bits are low. This corresponds to detecting a framing error with data at 0x00, but FRAME remains low.

When the low stop bit is detected, the receiver asserts the RXBRK bit in US\_CSR. This bit may be cleared by writing the Control Register (US\_CR) with the bit RSTSTA at 1.

An end of receive break is detected by a high level for at least 2/16 of a bit period in asynchronous operating mode or one sample at high level in synchronous operating mode. The end of break detection also asserts the RXBRK bit.

#### 34.6.3.16 Hardware Handshaking

The USART features a hardware handshaking out-of-band flow control. The RTS and CTS pins are used to connect with the remote device, as shown in Figure 34-27.

#### 35.8.14 SSC Interrupt Enable Register

| Name:        | SSC_IE   | -     |       |        |       |         |       |

|--------------|----------|-------|-------|--------|-------|---------|-------|

| Address:     | 0xFFFB   | C044  |       |        |       |         |       |

| Access Type: | Write-or | nly   |       |        |       |         |       |

| 31           | 30       | 29    | 28    | 27     | 26    | 25      | 24    |

| -            | -        | -     | -     | -      | -     | -       | -     |

| 23           | 22       | 21    | 20    | 19     | 18    | 17      | 16    |

| -            | _        | —     | _     | —      | —     | _       | _     |

| 15           | 14       | 13    | 12    | 11     | 10    | 9       | 8     |

| -            | _        | -     | -     | RXSYN  | TXSYN | CP1     | CP0   |

| 7            | 6        | 5     | 4     | 3      | 2     | 1       | 0     |

| RXBUFF       | ENDRX    | OVRUN | RXRDY | TXBUFE | ENDTX | TXEMPTY | TXRDY |

#### • TXRDY: Transmit Ready Interrupt Enable

0 = 0 = No effect.

1 = Enables the Transmit Ready Interrupt.

#### • TXEMPTY: Transmit Empty Interrupt Enable

0 = No effect.

1 = Enables the Transmit Empty Interrupt.

#### • ENDTX: End of Transmission Interrupt Enable

0 = No effect.

1 = Enables the End of Transmission Interrupt.

#### • TXBUFE: Transmit Buffer Empty Interrupt Enable

0 = No effect.

1 = Enables the Transmit Buffer Empty Interrupt

#### • RXRDY: Receive Ready Interrupt Enable

0 = No effect.

1 = Enables the Receive Ready Interrupt.

#### • OVRUN: Receive Overrun Interrupt Enable

0 = No effect.

1 = Enables the Receive Overrun Interrupt.

• ENDRX: End of Reception Interrupt Enable 0 = No effect.

1 = Enables the End of Reception Interrupt.

# AT91SAM9XE128/256/512 Preliminary

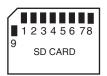

Figure 37-5. SD Memory Card Bus Topology

The SD Memory Card bus includes the signals listed in Table 37-3.

| Pin<br>Number | Name      | Type <sup>(1)</sup> | Description                  | MCI Pin Name <sup>(2)</sup><br>(Slot z) |

|---------------|-----------|---------------------|------------------------------|-----------------------------------------|

| 1             | CD/DAT[3] | I/O/PP              | Card detect/ Data line Bit 3 | MCDz3                                   |

| 2             | CMD       | PP                  | Command/response             | MCCDz                                   |

| 3             | VSS1      | S                   | Supply voltage ground        | VSS                                     |

| 4             | VDD       | S                   | Supply voltage               | VDD                                     |

| 5             | CLK       | I/O                 | Clock                        | MCCK                                    |

| 6             | VSS2      | S                   | Supply voltage ground        | VSS                                     |

| 7             | DAT[0]    | I/O/PP              | Data line Bit 0              | MCDz0                                   |

| 8             | DAT[1]    | I/O/PP              | Data line Bit 1 or Interrupt | MCDz1                                   |

| 9             | DAT[2]    | I/O/PP              | Data line Bit 2              | MCDz2                                   |

Table 37-3.

SD Memory Card Bus Signals

Notes: 1. I: input, O: output, PP: Push Pull, OD: Open Drain.

2. When several MCI (x MCI) are embedded in a product, MCCK refers to MCIx\_CK, MCCDA to MCIx\_CDA, MCCDB to MCIx\_CDB, MCDAy to MCIx\_DAy, MCDBy to MCIx\_DBy.

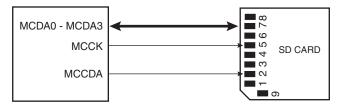

Figure 37-6. SD Card Bus Connections with One Slot

Note: When several MCI (x MCI) are embedded in a product, MCCK refers to MCIx\_CK, MCCDA to MCIx\_CDA MCDAy to MCIx\_DAy.

### 38.5 Ethernet MAC 10/100 (EMAC) User Interface

#### Table 38-6.Register Mapping

| Offset | Register                                | Name      | Access     | Reset       |

|--------|-----------------------------------------|-----------|------------|-------------|

| 0x00   | Network Control Register                | EMAC_NCR  | Read-write | 0           |

| 0x04   | Network Configuration Register          | EMAC_NCFG | Read-write | 0x800       |

| 0x08   | Network Status Register                 | EMAC_NSR  | Read-only  | -           |

| 0x0C   | Reserved                                |           |            |             |

| 0x10   | Reserved                                |           |            |             |

| 0x14   | Transmit Status Register                | EMAC_TSR  | Read-write | 0x0000_0000 |

| 0x18   | Receive Buffer Queue Pointer Register   | EMAC_RBQP | Read-write | 0x0000_0000 |

| 0x1C   | Transmit Buffer Queue Pointer Register  | EMAC_TBQP | Read-write | 0x0000_0000 |

| 0x20   | Receive Status Register                 | EMAC_RSR  | Read-write | 0x0000_0000 |

| 0x24   | Interrupt Status Register               | EMAC_ISR  | Read-write | 0x0000_0000 |

| 0x28   | Interrupt Enable Register               | EMAC_IER  | Write-only | -           |

| 0x2C   | Interrupt Disable Register              | EMAC_IDR  | Write-only | -           |

| 0x30   | Interrupt Mask Register                 | EMAC_IMR  | Read-only  | 0x0000_3FFF |

| 0x34   | Phy Maintenance Register                | EMAC_MAN  | Read-write | 0x0000_0000 |

| 0x38   | Pause Time Register                     | EMAC_PTR  | Read-write | 0x0000_0000 |

| 0x3C   | Pause Frames Received Register          | EMAC_PFR  | Read-write | 0x0000_0000 |

| 0x40   | Frames Transmitted Ok Register          | EMAC_FTO  | Read-write | 0x0000_0000 |

| 0x44   | Single Collision Frames Register        | EMAC_SCF  | Read-write | 0x0000_0000 |

| 0x48   | Multiple Collision Frames Register      | EMAC_MCF  | Read-write | 0x0000_0000 |

| 0x4C   | Frames Received Ok Register             | EMAC_FRO  | Read-write | 0x0000_0000 |

| 0x50   | Frame Check Sequence Errors Register    | EMAC_FCSE | Read-write | 0x0000_0000 |

| 0x54   | Alignment Errors Register               | EMAC_ALE  | Read-write | 0x0000_0000 |

| 0x58   | Deferred Transmission Frames Register   | EMAC_DTF  | Read-write | 0x0000_0000 |

| 0x5C   | Late Collisions Register                | EMAC_LCOL | Read-write | 0x0000_0000 |

| 0x60   | Excessive Collisions Register           | EMAC_ECOL | Read-write | 0x0000_0000 |

| 0x64   | Transmit Underrun Errors Register       | EMAC_TUND | Read-write | 0x0000_0000 |

| 0x68   | Carrier Sense Errors Register           | EMAC_CSE  | Read-write | 0x0000_0000 |

| 0x6C   | Receive Resource Errors Register        | EMAC_RRE  | Read-write | 0x0000_0000 |

| 0x70   | Receive Overrun Errors Register         | EMAC_ROV  | Read-write | 0x0000_0000 |

| 0x74   | Receive Symbol Errors Register          | EMAC_RSE  | Read-write | 0x0000_0000 |

| 0x78   | Excessive Length Errors Register        | EMAC_ELE  | Read-write | 0x0000_0000 |

| 0x7C   | Receive Jabbers Register                | EMAC_RJA  | Read-write | 0x0000_0000 |

| 0x80   | Undersize Frames Register               | EMAC_USF  | Read-write | 0x0000_0000 |

| 0x84   | SQE Test Errors Register                | EMAC_STE  | Read-write | 0x0000_0000 |

| 0x88   | Received Length Field Mismatch Register | EMAC_RLE  | Read-write | 0x0000_0000 |

# 674 AT91SAM9XE128/256/512 Preliminary

#### 38.5.26.5 Frames Received OK Register **Begister Name:** FMAC FRO

| negister maine: | EIVIAC_ | _FNU  |    |    |    |    |    |  |  |

|-----------------|---------|-------|----|----|----|----|----|--|--|

| Address:        | 0xFFF0  | C404C |    |    |    |    |    |  |  |

| Access Type:    | Read-w  | vrite |    |    |    |    |    |  |  |

| 31              | 30      | 29    | 28 | 27 | 26 | 25 | 24 |  |  |

| _               | _       | -     | -  | -  | -  | -  | -  |  |  |

| 23              | 22      | 21    | 20 | 19 | 18 | 17 | 16 |  |  |

|                 |         | FROK  |    |    |    |    |    |  |  |

| 15              | 14      | 13    | 12 | 11 | 10 | 9  | 8  |  |  |

|                 | FROK    |       |    |    |    |    |    |  |  |

| 7               | 6       | 5     | 4  | 3  | 2  | 1  | 0  |  |  |

|                 |         |       | FR | OK |    |    |    |  |  |

#### • FROK: Frames Received OK

A 24-bit register counting the number of good frames received, i.e., address recognized and successfully copied to memory. A good frame is of length 64 to 1518 bytes (1536 if bit 8 set in network configuration register) and has no FCS, alignment or receive symbol errors.

#### 38.5.26.6 Frames Check Sequence Errors Register

| Register Name | EMAC_  | EMAC_FCSE  |    |    |    |    |    |  |  |  |

|---------------|--------|------------|----|----|----|----|----|--|--|--|

| Address:      | 0xFFFC | 0xFFFC4050 |    |    |    |    |    |  |  |  |

| Access Type:  | Read-w | rite       |    |    |    |    |    |  |  |  |

| 31            | 30     | 29         | 28 | 27 | 26 | 25 | 24 |  |  |  |

| -             | -      | -          | -  | -  | -  | -  | -  |  |  |  |

| 23            | 22     | 21         | 20 | 19 | 18 | 17 | 16 |  |  |  |

| -             | —      | -          | -  | —  | —  | —  | —  |  |  |  |

| 15            | 14     | 13         | 12 | 11 | 10 | 9  | 8  |  |  |  |

| _             | _      | _          | -  | _  | _  | _  | -  |  |  |  |

| 7             | 6      | 5          | 4  | 3  | 2  | 1  | 0  |  |  |  |

|               |        |            | FC | SE |    |    |    |  |  |  |

#### • FCSE: Frame Check Sequence Errors

An 8-bit register counting frames that are an integral number of bytes, have bad CRC and are between 64 and 1518 bytes in length (1536 if bit 8 set in network configuration register). This register is also incremented if a symbol error is detected and the frame is of valid length and has an integral number of bytes.

#### 41.4.2 ISI Control 2 Register

| SI | CR2 |

|----|-----|

|    | SI  |

#### Address: 0xFFFC0004

Acess: Read-write

#### Reset: 0x0

| 31        | 30       | 29        | 28       | 27      | 26 | 25       | 24 |  |

|-----------|----------|-----------|----------|---------|----|----------|----|--|

| RGB_      | _CFG     | YCC_      | SWAP     | -       |    | IM_HSIZE |    |  |

| 23        | 22       | 21        | 20       | 19      | 18 | 17       | 16 |  |

|           | IM_HSIZE |           |          |         |    |          |    |  |

| 15        | 14       | 13        | 12       | 11      | 10 | 9        | 8  |  |

| COL_SPACE | RGB_SWAP | GRAYSCALE | RGB_MODE | GS_MODE |    | IM_VSIZE |    |  |

| 7         | 6        | 5         | 4        | 3       | 2  | 1        | 0  |  |

|           | IM_VSIZE |           |          |         |    |          |    |  |

#### • IM\_VSIZE: Vertical size of the Image sensor [0..2047]

Vertical size = IM\_VSIZE + 1

#### • GS\_MODE

0: 2 pixels per word

1: 1 pixel per word

#### • RGB\_MODE: RGB input mode

0: RGB 8:8:8 24 bits

1: RGB 5:6:5 16 bits

#### • GRAYSCALE

- 0: Grayscale mode is disabled

- 1: Input image is assumed to be grayscale coded

#### • RGB\_SWAP

0: D7 -> R7

1: D0 -> R7

The RGB\_SWAP has no effect when the grayscale mode is enabled.

#### • COL\_SPACE: Color space for the image data

0: YCbCr

1: RGB

• IM\_HSIZE: Horizontal size of the Image sensor [0..2047]

Horizontal size =  $IM_HSIZE + 1$

| Peripheral             | Consumption | Unit   |

|------------------------|-------------|--------|

| PIO Controller         | 10          |        |

| USART                  | 30          |        |

| UHP                    | 14          |        |

| UDP                    | 20          |        |

| ADC                    | 17          |        |

| тwi                    | 21          |        |

| SPI                    | 10          | μA/MHz |

| MCI                    | 30          |        |

| SSC                    | 20          |        |

| Timer Counter Channels | 6           |        |

| ISI                    | 8           |        |

| EMAC                   | 88          |        |

Table 43-6.

Power Consumption by Peripheral in Active Mode

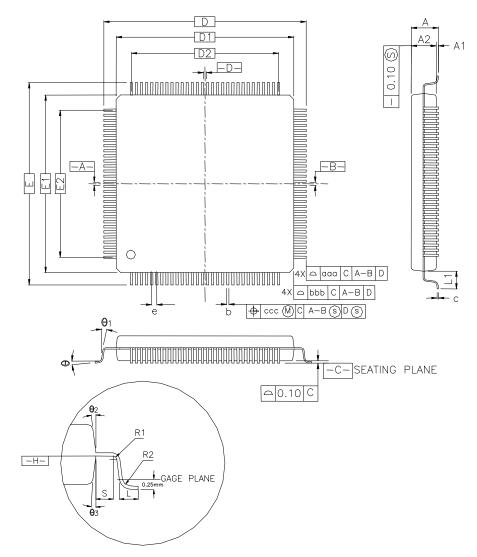

### Figure 44-2. 208-lead PQFP Package Drawing

| COTROL     | DIMENS    | IONS A  | RE IN  | MILLIME      | ETERS. |       |  |

|------------|-----------|---------|--------|--------------|--------|-------|--|

| SYMBOL     | М         | ILLIMET | ER     | INCH         |        |       |  |

| STMIDUL    | MIN.      | NOM.    | MAX.   | MIN.         | NOM.   | MAX.  |  |

| A          | —         | —       | 4.10   | —            |        | 0.161 |  |

| A1         | 0.25      |         |        | 0.010        | —      |       |  |

| A2         | 3.20      | 3.32    | 3.60   | 0.126        | 0.131  | 0.142 |  |

| D          | 31        | .20 BA  | SIC    | 1.2          | 28 BAS | SIC   |  |

| D1         | 28        | .00 BA  | SIC    | 1.1          | 02 BAS | SIC   |  |

| E          | 31        | .20 BA  | SIC    | 1.2          | 28 BAS | SIC   |  |

| E1         | 28        | .00 BA  | SIC    | 1.1          | 02 BAS | SIC   |  |

| R2         | 0.13      | —       | 0.30   | 0.005        | _      | 0.012 |  |

| R1         | 0.13      | —       | —      | 0.005        |        | —     |  |

| θ          | 0*        | —       | 7°     | 0*           | —      | 7°    |  |

| θ1         | 0*        |         |        | 0.           |        |       |  |

| θ2         |           | 8° REF  |        | 8º REF       |        |       |  |

| θз         |           | 8" REF  |        | 8" REF       |        |       |  |

| С          | 0.11      | 0.15    | 0.23   | 0.004        | 0.006  | 0.009 |  |

| L          | 0.73      | 0.88    | 1.03   | 0.029        | 0.035  | 0.041 |  |

| L 1        | 1         | .60 RE  | F      | 0.063 REF    |        |       |  |

| S          | 0.20      |         | —      | 0.008        |        |       |  |

| b          | 0.17      | 0.20    | 0.27   |              | 0.008  |       |  |

| е          | 0.50 BSC. |         |        | 0.020 BSC.   |        |       |  |

| D2         | 25.50     |         |        | 1.004        |        |       |  |

| E2         |           | 25.50   |        | 1.004        |        |       |  |

|            | JLERAN    |         | - FORM | AND POSITION |        |       |  |

| <u>aaa</u> |           | 0.25    |        | 0.010        |        |       |  |

| bbb        |           | 0.20    |        | 0.008        |        |       |  |

| CCC        |           | 0.08    |        |              | 0.003  |       |  |

Table 44-5.

Device and 208-lead PQFP Package Maximum Weight

| 5.5                                                       | g |

|-----------------------------------------------------------|---|

| Table 44-6.         208-lead PQFP Package Characteristics |   |

| Moisture Sensitivity Level                                | 3 |

| Table 44-7.         Package Reference                     |   |

| JEDEC Drawing Reference | MS-022 |

|-------------------------|--------|

| JESD97 Classification   | e3     |