# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                   |

|---------------------------------|----------------------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                             |

| Speed                           | 180MHz                                                                     |

| Co-Processors/DSP               | -                                                                          |

| RAM Controllers                 | SDRAM, SRAM                                                                |

| Graphics Acceleration           | No                                                                         |

| Display & Interface Controllers | LCD, Touchscreen                                                           |

| Ethernet                        | 10/100Mbps                                                                 |

| SATA                            | -                                                                          |

| USB                             | USB 2.0 (3)                                                                |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                           |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                          |

| Security Features               |                                                                            |

| Package / Case                  | 208-BFQFP                                                                  |

| Supplier Device Package         | 208-PQFP (28x28)                                                           |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/at91sam9xe512-qu |

|                                 |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 3-1. Signal Description List (Continued)

| Signal Name    | Function                          | Туре            | Active<br>Level | Reference<br>Voltage | Comments                          |

|----------------|-----------------------------------|-----------------|-----------------|----------------------|-----------------------------------|

|                |                                   | Ethernet 10/    | /100            |                      |                                   |

| ETXCK          | Transmit Clock or Reference Clock | Input           |                 | VDDIOP0              | MII only, REFCK in RMII           |

| ERXCK          | Receive Clock                     | Input           |                 | VDDIOP0              | MII only                          |

| ETXEN          | Transmit Enable                   | Output          |                 | VDDIOP0              |                                   |

| ETX0-ETX3      | Transmit Data                     | Output          |                 | VDDIOP0              | ETX0-ETX1 only in RMII            |

| ETXER          | Transmit Coding Error             | Output          |                 | VDDIOP0              | MII only                          |

| ERXDV          | Receive Data Valid                | Input           |                 | VDDIOP0              | RXDV in MII, CRSDV in RMII        |

| ERX0-ERX3      | Receive Data                      | Input           |                 | VDDIOP0              | ERX0-ERX1 only in RMII            |

| ERXER          | Receive Error                     | Input           |                 | VDDIOP0              |                                   |

| ECRS           | Carrier Sense and Data Valid      | Input           |                 | VDDIOP0              | MII only                          |

| ECOL           | Collision Detect                  | Input           |                 | VDDIOP0              | MII only                          |

| EMDC           | Management Data Clock             | Output          |                 | VDDIOP0              |                                   |

| EMDIO          | Management Data Input/Output      | I/O             |                 | VDDIOP0              |                                   |

| EF100          | Force 100Mbit/sec.                |                 | High            | VDDIOP0              |                                   |

|                | Ir                                | nage Sensor Ir  | nterface        |                      |                                   |

| ISI_D0-ISI_D11 | Image Sensor Data                 | Input           |                 | VDDIOP1              |                                   |

| ISI_MCK        | Image sensor Reference clock      | output          |                 | VDDIOP1              |                                   |

| ISI_HSYNC      | Image Sensor Horizontal Synchro   | input           |                 | VDDIOP1              |                                   |

| ISI_VSYNC      | Image Sensor Vertical Synchro     | input           |                 | VDDIOP1              |                                   |

| ISI_PCK        | Image Sensor Data clock           | input           |                 | VDDIOP1              |                                   |

|                | Ana                               | alog to Digital | Converter       |                      | 1                                 |

| AD0-AD3        | Analog Inputs                     | Analog          |                 | VDDANA               | Digital pulled-up inputs at reset |

| ADVREF         | Analog Positive Reference         | Analog          |                 | VDDANA               |                                   |

| ADTRG          | ADC Trigger                       | Input           |                 | VDDANA               |                                   |

|                | Fast Fl                           | ash Programm    | ning Interface  | )                    | 1                                 |

| PGMEN[3:0]     | Programming Enabling              | Input           |                 | VDDIOP0              |                                   |

| PGMNCMD        | Programming Command               | Input           | Low             | VDDIOP0              |                                   |

| PGMRDY         | Programming Ready                 | Output          | High            | VDDIOP0              |                                   |

| PGMNOE         | Programming Read                  | Input           | Low             | VDDIOP0              |                                   |

| PGMNVALID      | Data Direction                    | Output          | Low             | VDDIOP0              |                                   |

| PGMM[3:0]      | Programming Mode                  | Input           |                 | VDDIOP0              |                                   |

| PGMD[15:0]     | Programming Data                  | I/O             |                 | VDDIOP0              |                                   |

Notes: 1. Programming of this pull-up resistor is performed independently for each I/O line through the PIO Controllers. After reset, all the I/O lines default as inputs with pull-up resistors enabled, except those which are multiplexed with the External Bus Interface signals that require to be enabled as Peripheral at reset. This is explicitly indicated in the column "Reset State" of the peripheral multiplexing tables.

2. Refer to PIO Multiplexing (see Section 10.3 "Peripheral Signals Multiplexing on I/O Lines").

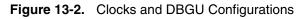

- 8. Initialization of the DBGU serial port (115200 bauds, 8, N, 1) only if OSCSEL = 1

- 9. Enable the user reset

- 10. Jump to SAM-BA Boot sequence

- 11. Disable the Watchdog

- 12. Initialization of the USB Device Port

All lock regions must be unlocked before the Full Erase command by using the CLB command. Otherwise, the erase command is aborted and no page is erased.

Table 14-9. Full Erase Command

| St | tep | Handshake Sequence | MODE[3:0] | DATA[15:0] |

|----|-----|--------------------|-----------|------------|

| 1  |     | Write handshaking  | CMDE      | EA         |

| 2  |     | Write handshaking  | DATA      | 0          |

#### 14.2.5.4 Flash Lock Commands

Lock bits can be set using WPL or EWPL commands. They can also be set by using the **Set** Lock command (SLB). With this command, several lock bits can be activated. A Bit Mask is provided as argument to the command. When bit 0 of the bit mask is set, then the first lock bit is activated.

In the same way, the **Clear Lock** command **(CLB)** is used to clear lock bits. All the lock bits are also cleared by the EA command.

Table 14-10. Set and Clear Lock Bit Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0] |

|------|--------------------|-----------|------------|

| 1    | Write handshaking  | CMDE      | SLB or CLB |

| 2    | Write handshaking  | DATA      | Bit Mask   |

Lock bits can be read using **Get Lock Bit** command **(GLB)**. The n<sup>th</sup> lock bit is active when the bit n of the bit mask is set..

|  | Table 14-11. | Get Lock Bit Command |

|--|--------------|----------------------|

|--|--------------|----------------------|

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]                                                             |

|------|--------------------|-----------|------------------------------------------------------------------------|

| 1    | Write handshaking  | CMDE      | GLB                                                                    |

| 2    | Read handshaking   | DATA      | Lock Bit Mask Status<br>0 = Lock bit is cleared<br>1 = Lock bit is set |

#### 14.2.5.5 Flash General-purpose NVM Commands

General-purpose NVM bits (GP NVM bits) can be set using the **Set GPNVM** command **(SGPB)**. This command also activates GP NVM bits. A bit mask is provided as argument to the command. When bit 0 of the bit mask is set, then the first GP NVM bit is activated.

In the same way, the **Clear GPNVM** command **(CGPB)** is used to clear general-purpose NVM bits. All the general-purpose NVM bits are also cleared by the EA command. The general-purpose NVM bit is deactivated when the corresponding bit in the pattern value is set to 1.

Table 14-12. Set/Clear GP NVM Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]               |

|------|--------------------|-----------|--------------------------|

| 1    | Write handshaking  | CMDE      | SGPB or CGPB             |

| 2    | Write handshaking  | DATA      | GP NVM bit pattern value |

#### 23.14.2 SMC Pulse Register

**Register Name:** SMC\_PULSE[0..7]

Addresses: 0xFFFEC04 [0], 0xFFFEC14 [1], 0xFFFEC24 [2], 0xFFFEC34 [3], 0xFFFEC44 [4], 0xFFFEC54 [5], 0xFFFEC64 [6], 0xFFFEC74 [7]

Access Type: Read-write

| 31 | 30 | 29           | 28 | 27           | 26 | 25 | 24 |

|----|----|--------------|----|--------------|----|----|----|

| -  |    |              |    | NCS_RD_PULSE |    |    |    |

| 23 | 22 | 21           | 20 | 19           | 18 | 17 | 16 |

| _  |    | NRD_PULSE    |    |              |    |    |    |

| 15 | 14 | 13           | 12 | 11           | 10 | 9  | 8  |

| -  |    | NCS_WR_PULSE |    |              |    |    |    |

| 7  | 6  | 5            | 4  | 3            | 2  | 1  | 0  |

| -  |    |              |    | NWE_PULSE    |    |    |    |

#### • NWE\_PULSE: NWE Pulse Length

The NWE signal pulse length is defined as:

NWE pulse length = (256\* NWE\_PULSE[6] + NWE\_PULSE[5:0]) clock cycles

The NWE pulse length must be at least 1 clock cycle.

#### • NCS\_WR\_PULSE: NCS Pulse Length in WRITE Access

In write access, the NCS signal pulse length is defined as:

NCS pulse length = (256\* NCS\_WR\_PULSE[6] + NCS\_WR\_PULSE[5:0]) clock cycles

The NCS pulse length must be at least 1 clock cycle.

#### NRD\_PULSE: NRD Pulse Length

In standard read access, the NRD signal pulse length is defined in clock cycles as:

NRD pulse length = (256\* NRD\_PULSE[6] + NRD\_PULSE[5:0]) clock cycles

The NRD pulse length must be at least 1 clock cycle.

In page mode read access, the NRD\_PULSE parameter defines the duration of the subsequent accesses in the page.

#### • NCS\_RD\_PULSE: NCS Pulse Length in READ Access

In standard read access, the NCS signal pulse length is defined as:

NCS pulse length = (256\* NCS\_RD\_PULSE[6] + NCS\_RD\_PULSE[5:0]) clock cycles

The NCS pulse length must be at least 1 clock cycle.

In page mode read access, the NCS\_RD\_PULSE parameter defines the duration of the first access to one page.

# AT91SAM9XE128/256/512 Preliminary

#### 30.5.9 Debug Unit Baud Rate Generator Register

| Name:        | DBGU_BRGR |            |    |    |    |    |    |  |

|--------------|-----------|------------|----|----|----|----|----|--|

| Address:     | 0xFFFF    | 0xFFFF220  |    |    |    |    |    |  |

| Access Type: | Read-w    | Read-write |    |    |    |    |    |  |

| 31           | 30        | 29         | 28 | 27 | 26 | 25 | 24 |  |

| _            | _         | —          | _  | _  | _  | _  | _  |  |

| 23           | 22        | 21         | 20 | 19 | 18 | 17 | 16 |  |

| —            | —         | -          | -  | _  | _  | _  | —  |  |

| 15           | 14        | 13         | 12 | 11 | 10 | 9  | 8  |  |

|              |           |            | С  | D  |    |    |    |  |

| 7            | 6         | 5          | 4  | 3  | 2  | 1  | 0  |  |

|              |           |            | С  | D  |    |    |    |  |

#### CD: Clock Divisor

| CD         | Baud Rate Clock |

|------------|-----------------|

| 0          | Disabled        |

| 1          | MCK             |

| 2 to 65535 | MCK / (CD x 16) |

#### • NVPSIZ2 Second Nonvolatile Program Memory Size

|   | NVPSIZ2 |   |   | Size        |

|---|---------|---|---|-------------|

| 0 | 0       | 0 | 0 | None        |

| 0 | 0       | 0 | 1 | 8K bytes    |

| 0 | 0       | 1 | 0 | 16K bytes   |

| 0 | 0       | 1 | 1 | 32K bytes   |

| 0 | 1       | 0 | 0 | Reserved    |

| 0 | 1       | 0 | 1 | 64K bytes   |

| 0 | 1       | 1 | 0 | Reserved    |

| 0 | 1       | 1 | 1 | 128K bytes  |

| 1 | 0       | 0 | 0 | Reserved    |

| 1 | 0       | 0 | 1 | 256K bytes  |

| 1 | 0       | 1 | 0 | 512K bytes  |

| 1 | 0       | 1 | 1 | Reserved    |

| 1 | 1       | 0 | 0 | 1024K bytes |

| 1 | 1       | 0 | 1 | Reserved    |

| 1 | 1       | 1 | 0 | 2048K bytes |

| 1 | 1       | 1 | 1 | Reserved    |

#### • SRAMSIZ: Internal SRAM Size

|   | SRAMSIZ |   |   | Size       |

|---|---------|---|---|------------|

| 0 | 0       | 0 | 0 | Reserved   |

| 0 | 0       | 0 | 1 | 1K bytes   |

| 0 | 0       | 1 | 0 | 2K bytes   |

| 0 | 0       | 1 | 1 | 6K bytes   |

| 0 | 1       | 0 | 0 | 112K bytes |

| 0 | 1       | 0 | 1 | 4K bytes   |

| 0 | 1       | 1 | 0 | 80K bytes  |

| 0 | 1       | 1 | 1 | 160K bytes |

| 1 | 0       | 0 | 0 | 8K bytes   |

| 1 | 0       | 0 | 1 | 16K bytes  |

| 1 | 0       | 1 | 0 | 32K bytes  |

| 1 | 0       | 1 | 1 | 64K bytes  |

| 1 | 1       | 0 | 0 | 128K bytes |

| 1 | 1       | 0 | 1 | 256K bytes |

| 1 | 1       | 1 | 0 | 96K bytes  |

| 1 | 1       | 1 | 1 | 512K bytes |

| Name:        | US_RHI  | R                                                                              |          |          |    |    |       |  |  |

|--------------|---------|--------------------------------------------------------------------------------|----------|----------|----|----|-------|--|--|

| Addresses:   | 0xFFFB  | 0xFFFB0018 (0), 0xFFFB4018 (1), 0xFFFB8018 (2), 0xFFFD0018 (3), 0xFFFD4018 (4) |          |          |    |    |       |  |  |

| Access Type: | Read-or | Read-only                                                                      |          |          |    |    |       |  |  |

| 31           | 30      | 29                                                                             | 28       | 27       | 26 | 25 | 24    |  |  |

| -            | —       | -                                                                              | -        | -        | —  | -  | -     |  |  |

| 23           | 22      | 21                                                                             | 20       | 19       | 18 | 17 | 16    |  |  |

| 15           | 14      | 13                                                                             | 12       | 11       | 10 | 9  | 8     |  |  |

| RXSYNH       | —       | -                                                                              | -        | -        | —  | -  | RXCHR |  |  |

| 7            | 6       | 5                                                                              | 4<br>RX0 | 3<br>CHR | 2  | 1  | 0     |  |  |

# 34.7.7 USART Receive Holding Register

#### • RXCHR: Received Character

Last character received if RXRDY is set.

#### • RXSYNH: Received Sync

0: Last Character received is a Data.

1: Last Character received is a Command.

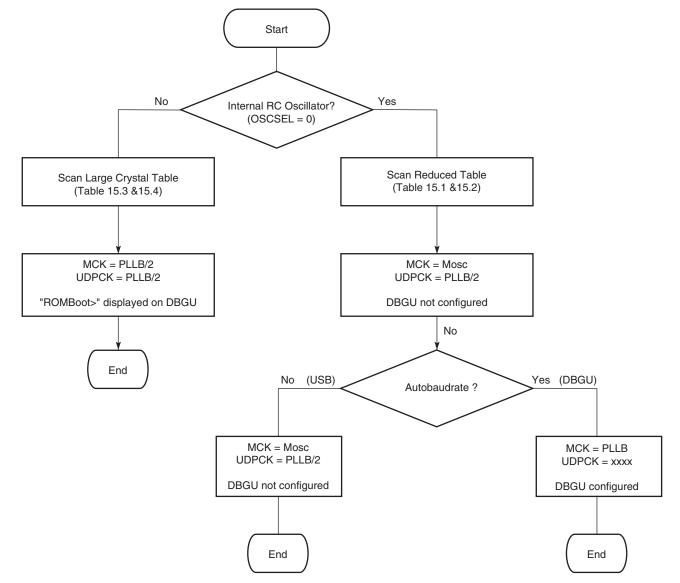

Figure 35-19. Time Slot Application Block Diagram

#### CKG: Receive Clock Gating Selection

| CKG | Receive Clock Gating                  |

|-----|---------------------------------------|

| 0x0 | None, continuous clock                |

| 0x1 | Receive Clock enabled only if RF Low  |

| 0x2 | Receive Clock enabled only if RF High |

| 0x3 | Reserved                              |

#### START: Receive Start Selection

| START   | Receive Start                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------|

| 0x0     | Continuous, as soon as the receiver is enabled, and immediately after the end of transfer of the previous data. |

| 0x1     | Transmit start                                                                                                  |

| 0x2     | Detection of a low level on RF signal                                                                           |

| 0x3     | Detection of a high level on RF signal                                                                          |

| 0x4     | Detection of a falling edge on RF signal                                                                        |

| 0x5     | Detection of a rising edge on RF signal                                                                         |

| 0x6     | Detection of any level change on RF signal                                                                      |

| 0x7     | Detection of any edge on RF signal                                                                              |

| 0x8     | Compare 0                                                                                                       |

| 0x9-0xF | Reserved                                                                                                        |

#### • STOP: Receive Stop Selection

0 = After completion of a data transfer when starting with a Compare 0, the receiver stops the data transfer and waits for a new compare 0.

1 = After starting a receive with a Compare 0, the receiver operates in a continuous mode until a Compare 1 is detected.

#### • STTDLY: Receive Start Delay

If STTDLY is not 0, a delay of STTDLY clock cycles is inserted between the start event and the actual start of reception. When the Receiver is programmed to start synchronously with the Transmitter, the delay is also applied.

Note: It is very important that STTDLY be set carefully. If STTDLY must be set, it should be done in relation to TAG (Receive Sync Data) reception.

#### • PERIOD: Receive Period Divider Selection

This field selects the divider to apply to the selected Receive Clock in order to generate a new Frame Sync Signal. If 0, no PERIOD signal is generated. If not 0, a PERIOD signal is generated each 2 x (PERIOD+1) Receive Clock.

#### 37.9.14 MCI Interrupt Mask Register

| Name: | MCI_IMR |

|-------|---------|

|-------|---------|

| xFFFA804C |

|-----------|

|           |

#### Access Type: Read-only

| 31     | 30     | 29      | 28   | 27    | 26    | 25       | 24       |

|--------|--------|---------|------|-------|-------|----------|----------|

| UNRE   | OVRE   | -       | -    | -     | -     | -        | -        |

| 23     | 22     | 21      | 20   | 19    | 18    | 17       | 16       |

| -      | DTOE   | DCRCE   | RTOE | RENDE | RCRCE | RDIRE    | RINDE    |

| 15     | 14     | 13      | 12   | 11    | 10    | 9        | 8        |

| TXBUFE | RXBUFF | -       | -    | -     | -     | SDIOIRQB | SDIOIRQA |

| 7      | 6      | 5       | 4    | 3     | 2     | 1        | 0        |

| ENDTX  | ENDRX  | NOTBUSY | DTIP | BLKE  | TXRDY | RXRDY    | CMDRDY   |

#### • CMDRDY: Command Ready Interrupt Mask

- RXRDY: Receiver Ready Interrupt Mask

- TXRDY: Transmit Ready Interrupt Mask

- BLKE: Data Block Ended Interrupt Mask

- DTIP: Data Transfer in Progress Interrupt Mask

- NOTBUSY: Data Not Busy Interrupt Mask

- ENDRX: End of Receive Buffer Interrupt Mask

- ENDTX: End of Transmit Buffer Interrupt Mask

- SDIOIRQA: SDIO Interrupt for Slot A Interrupt Mask

- SDIOIRQB: SDIO Interrupt for Slot B Interrupt Mask

- RXBUFF: Receive Buffer Full Interrupt Mask

- TXBUFE: Transmit Buffer Empty Interrupt Mask

- RINDE: Response Index Error Interrupt Mask

- RDIRE: Response Direction Error Interrupt Mask

- RCRCE: Response CRC Error Interrupt Mask

- RENDE: Response End Bit Error Interrupt Mask

- RTOE: Response Time-out Error Interrupt Mask

- DCRCE: Data CRC Error Interrupt Mask

- DTOE: Data Time-out Error Interrupt Mask

#### 38.4.1.3 Transmit Buffer List

Transmit data is read from areas of data (the buffers) in system memory These buffers are listed in another data structure that also resides in main memory. This data structure (Transmit Buffer Queue) is a sequence of descriptor entries (as defined in Table 38-2 on page 664) that points to this data structure.

To create this list of buffers:

- 1. Allocate a number (*n*) of buffers of between 1 and 2047 bytes of data to be transmitted in system memory. Up to 128 buffers per frame are allowed.

- 2. Allocate an area 2*n* words for the transmit buffer descriptor entry in system memory and create N entries in this list. Mark all entries in this list as owned by EMAC, i.e. bit 31 of word 1 set to 0.

- 3. If fewer than 1024 buffers are defined, the last descriptor must be marked with the wrap bit bit 30 in word 1 set to 1.

- 4. Write address of transmit buffer descriptor entry to EMAC register transmit\_buffer queue pointer.

- 5. The transmit circuits can then be enabled by writing to the network control register.

#### 38.4.1.4 Address Matching

The EMAC register-pair hash address and the four specific address register-pairs must be written with the required values. Each register-pair comprises a bottom register and top register, with the bottom register being written first. The address matching is disabled for a particular register-pair after the bottom-register has been written and re-enabled when the top register is written. See "Address Checking Block" on page 667. for details of address matching. Each register-pair may be written at any time, regardless of whether the receive circuits are enabled or disabled.

#### 38.4.1.5 Interrupts

There are 14 interrupt conditions that are detected within the EMAC. These are ORed to make a single interrupt. Depending on the overall system design, this may be passed through a further level of interrupt collection (interrupt controller). On receipt of the interrupt signal, the CPU enters the interrupt handler (Refer to the AIC programmer datasheet). To ascertain which interrupt has been generated, read the interrupt status register. Note that this register clears itself when read. At reset, all interrupts are disabled. To enable an interrupt, write to interrupt enable register with the pertinent interrupt bit set to 1. To disable an interrupt, write to interrupt disable register with the pertinent interrupt bit set to 1. To check whether an interrupt is enabled or disabled, read interrupt mask register: if the bit is set to 1, the interrupt is disabled.

#### 38.4.1.6 Transmitting Frames

To set up a frame for transmission:

- 1. Enable transmit in the network control register.

- 2. Allocate an area of system memory for transmit data. This does not have to be contiguous, varying byte lengths can be used as long as they conclude on byte borders.

- 3. Set-up the transmit buffer list.

- 4. Set the network control register to enable transmission and enable interrupts.

- 5. Write data for transmission into these buffers.

- 6. Write the address to transmit buffer descriptor queue pointer.

- 7. Write control and length to word one of the transmit buffer descriptor entry.

## 672 AT91SAM9XE128/256/512 Preliminary

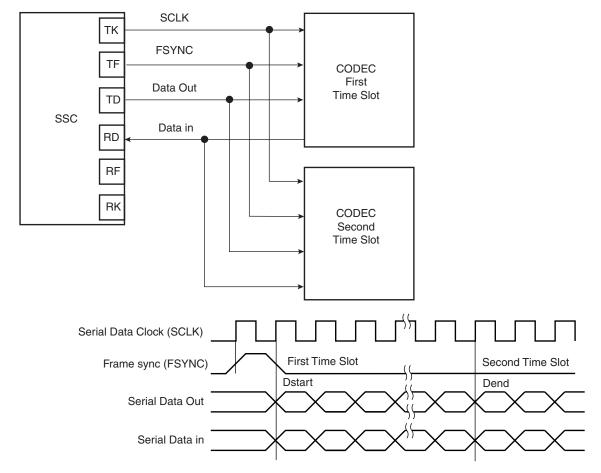

When using a ping-pong endpoint, the following procedures are required to perform Data IN transactions:

- 1. The microcontroller checks if it is possible to write in the FIFO by polling TXPKTRDY to be cleared in the endpoint's UDP\_CSRx register.

- 2. The microcontroller writes the first data payload to be sent in the FIFO (Bank 0), writing zero or more byte values in the endpoint's UDP\_FDRx register.

- 3. The microcontroller notifies the USB peripheral it has finished writing in Bank 0 of the FIFO by setting the TXPKTRDY in the endpoint's UDP\_CSRx register.

- 4. Without waiting for TXPKTRDY to be cleared, the microcontroller writes the second data payload to be sent in the FIFO (Bank 1), writing zero or more byte values in the endpoint's UDP\_FDRx register.

- 5. The microcontroller is notified that the first Bank has been released by the USB device when TXCOMP in the endpoint's UDP\_CSRx register is set. An interrupt is pending while TXCOMP is being set.

- 6. Once the microcontroller has received TXCOMP for the first Bank, it notifies the USB device that it has prepared the second Bank to be sent, raising TXPKTRDY in the endpoint's UDP\_CSRx register.

- 7. At this step, Bank 0 is available and the microcontroller can prepare a third data payload to be sent.

Figure 39-8. Data IN Transfer for Ping-pong Endpoint

**Warning:** There is software critical path due to the fact that once the second bank is filled, the driver has to wait for TX\_COMP to set TX\_PKTRDY. If the delay between receiving TX\_COMP is set and TX\_PKTRDY is set too long, some Data IN packets may be NACKed, reducing the bandwidth.

**Warning:** TX\_COMP must be cleared after TX\_PKTRDY has been set.

# 716 AT91SAM9XE128/256/512 Preliminary

The USB device sets this bit when a UDP resume signal is detected at its port.

After reset, the state of this bit is undefined, the application must clear this bit by setting the RXRSM flag in the UDP\_ICR register.

### EXTRSM: UDP External Resume Interrupt Status

0 = No UDP External Resume Interrupt pending.

1 = UDP External Resume Interrupt has been raised.

### • SOFINT: Start of Frame Interrupt Status

0 = No Start of Frame Interrupt pending.

1 = Start of Frame Interrupt has been raised.

This interrupt is raised each time a SOF token has been detected. It can be used as a synchronization signal by using

isochronous endpoints.

### • ENDBUSRES: End of BUS Reset Interrupt Status

0 = No End of Bus Reset Interrupt pending.

1 = End of Bus Reset Interrupt has been raised.

This interrupt is raised at the end of a UDP reset sequence. The USB device must prepare to receive requests on the endpoint 0. The host starts the enumeration, then performs the configuration.

### • WAKEUP: UDP Resume Interrupt Status

0 = No Wakeup Interrupt pending.

1 = A Wakeup Interrupt (USB Host Sent a RESUME or RESET) occurred since the last clear.

After reset the state of this bit is undefined, the application must clear this bit by setting the WAKEUP flag in the UDP\_ICR register

### 39.6.8 UDP Interrupt Clear Register

| Register Name | : UDP_IC | UDP_ICR    |           |        |        |       |        |  |  |  |

|---------------|----------|------------|-----------|--------|--------|-------|--------|--|--|--|

| Address:      | 0xFFFA   | 0xFFFA4020 |           |        |        |       |        |  |  |  |

| Access Type:  | Write-   | only       |           |        |        |       |        |  |  |  |

| 31            | 30       | 29         | 28        | 27     | 26     | 25    | 24     |  |  |  |

| -             | —        | -          | -         | —      | -      | -     | -      |  |  |  |

| 23            | 22       | 21         | 20        | 19     | 18     | 17    | 16     |  |  |  |

| -             | -        | —          | -         | -      | _      | _     | -      |  |  |  |

| 15            | 14       | 13         | 12        | 11     | 10     | 9     | 8      |  |  |  |

| -             | _        | WAKEUP     | ENDBUSRES | SOFINT | EXTRSM | RXRSM | RXSUSP |  |  |  |

| 7             | 6        | 5          | 4         | 3      | 2      | 1     | 0      |  |  |  |

| -             | —        | -          | -         | _      | —      | -     | -      |  |  |  |

#### RXSUSP: Clear UDP Suspend Interrupt

0 = No effect.

1 = Clears UDP Suspend Interrupt.

#### • RXRSM: Clear UDP Resume Interrupt

0 = No effect.

1 = Clears UDP Resume Interrupt.

#### • EXTRSM: Clear UDP External Resume Interrupt

0 = No effect.

1 = Clears UDP External Resume Interrupt.

#### • SOFINT: Clear Start Of Frame Interrupt

0 = No effect.

1 = Clears Start Of Frame Interrupt.

### • ENDBUSRES: Clear End of Bus Reset Interrupt

0 = No effect.

1 = Clears End of Bus Reset Interrupt.

#### • WAKEUP: Clear Wakeup Interrupt

0 = No effect.

1 = Clears Wakeup Interrupt.

|           |        |         |         |         |         | 5.0     |         |         |         |

|-----------|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| Mode      | Byte   | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      |

| RGB 8:8:8 | Byte 0 | R0(i)   | R1(i)   | R2(i)   | R3(i)   | R4(i)   | R5(i)   | R6(i)   | R7(i)   |

|           | Byte 1 | G0(i)   | G1(i)   | G2(i)   | G3(i)   | G4(i)   | G5(i)   | G6(i)   | G7(i)   |

|           | Byte 2 | B0(i)   | B1(i)   | B2(i)   | B3(i)   | B4(i)   | B5(i)   | B6(i)   | B7(i)   |

|           | Byte 3 | R0(i+1) | R1(i+1) | R2(i+1) | R3(i+1) | R4(i+1) | R5(i+1) | R6(i+1) | R7(i+1) |

| RGB 5:6:5 | Byte 0 | G3(i)   | G4(i)   | G5(i)   | R0(i)   | R1(i)   | R2(i)   | R3(i)   | R4(i)   |

|           | Byte 1 | B0(i)   | B1(i)   | B2(i)   | B3(i)   | B4(i)   | G0(i)   | G1(i)   | G2(i)   |

|           | Byte 2 | G3(i+1) | G4(i+1) | G5(i+1) | R0(i+1) | R1(i+1) | R2(i+1) | R3(i+1) | R4(i+1) |

|           | Byte 3 | B0(i+1) | B1(i+1) | B2(i+1) | B3(i+1) | B4(i+1) | G0(i+1) | G1(i+1) | G2(i+1) |

Table 41-5.

RGB Format in Default Mode, RGB\_CFG = 00, Swap Activated

The RGB 5:6:5 input format is processed to be displayed as RGB 5:5:5 format, compliant with the 16-bit mode of the LCD controller.

#### 41.3.3 Clocks

The sensor master clock (ISI\_MCK) can be generated either by the Advanced Power Management Controller (APMC) through a Programmable Clock output or by an external oscillator connected to the sensor.

None of the sensors embeds a power management controller, so providing the clock by the APMC is a simple and efficient way to control power consumption of the system.

Care must be taken when programming the system clock. The ISI has two clock domains, the system bus clock and the pixel clock provided by sensor. The two clock domains are not synchronized, but the system clock must be faster than pixel clock.

#### 41.4.2 ISI Control 2 Register

| SI | CR2 |

|----|-----|

|    | SI  |

### Address: 0xFFFC0004

Acess: Read-write

#### Reset: 0x0

| 31        | 30       | 29        | 28       | 27      | 26       | 25       | 24 |  |

|-----------|----------|-----------|----------|---------|----------|----------|----|--|

| RGB_      | _CFG     | YCC_      | SWAP     | -       | IM_HSIZE |          |    |  |

| 23        | 22       | 21        | 20       | 19      | 18       | 17       | 16 |  |

|           | IM_HSIZE |           |          |         |          |          |    |  |

| 15        | 14       | 13        | 12       | 11      | 10       | 9        | 8  |  |

| COL_SPACE | RGB_SWAP | GRAYSCALE | RGB_MODE | GS_MODE |          | IM_VSIZE |    |  |

| 7         | 6        | 5         | 4        | 3       | 2        | 1        | 0  |  |

|           |          |           | IM_V     | SIZE    |          |          |    |  |

#### • IM\_VSIZE: Vertical size of the Image sensor [0..2047]

Vertical size = IM\_VSIZE + 1

#### • GS\_MODE

0: 2 pixels per word

1: 1 pixel per word

#### • RGB\_MODE: RGB input mode

0: RGB 8:8:8 24 bits

1: RGB 5:6:5 16 bits

#### • GRAYSCALE

- 0: Grayscale mode is disabled

- 1: Input image is assumed to be grayscale coded

#### • RGB\_SWAP

0: D7 -> R7

1: D0 -> R7

The RGB\_SWAP has no effect when the grayscale mode is enabled.

### • COL\_SPACE: Color space for the image data

0: YCbCr

1: RGB

• IM\_HSIZE: Horizontal size of the Image sensor [0..2047]

Horizontal size =  $IM_HSIZE + 1$

#### 41.4.3 ISI Status Register

| Name: | ISI | SR |

|-------|-----|----|

|-------|-----|----|

Address: 0xFFFC0008

Acess: Read

#### Reset: 0x0

| 31       | 30       | 29       | 28      | 27      | 26      | 25     | 24       |

|----------|----------|----------|---------|---------|---------|--------|----------|

| _        | I        | —        | -       | —       | —       | Ι      | -        |

| 23       | 22       | 21       | 20      | 19      | 18      | 17     | 16       |

| _        | -        | -        | -       | -       | -       | -      | -        |

| 15       | 14       | 13       | 12      | 11      | 10      | 9      | 8        |

| _        | _        | —        | —       | —       | —       | FR_OVR | FO_C_EMP |

| 7        | 6        | 5        | 4       | 3       | 2       | 1      | 0        |

| FO_P_EMP | FO_P_OVF | FO_C_OVF | CRC_ERR | CDC_PND | SOFTRST | DIS    | SOF      |

#### • SOF: Start of frame

0: No start of frame has been detected.

1: A start of frame has been detected.

#### • DIS: Image Sensor Interface disable

0: The image sensor interface is enabled.

1: The image sensor interface is disabled and stops capturing data. The DMA controller and the core can still read the FIFOs.

#### • SOFTRST: Software reset

0: Software reset not asserted or not completed.

1: Software reset has completed successfully.

#### • CDC\_PND: Codec request pending

0: No request asserted.

1: A codec request is pending. If a codec request is asserted during a frame, the CDC\_PND bit rises until the start of a new frame. The capture is completed when the flag FO\_C\_EMP = 1.

#### • CRC\_ERR: CRC synchronization error

0: No crc error in the embedded synchronization frame (SAV/EAV)

1: The CRC\_SYNC is enabled in the control register and an error has been detected and not corrected. The frame is discarded and the ISI waits for a new one.

#### • FO\_C\_OVF: FIFO codec overflow

0: No overflow

1: An overrun condition has occurred in input FIFO on the codec path. The overrun happens when the FIFO is full and an attempt is made to write a new sample to the FIFO.

| 41.4.7   | <b>ISI Preview Register</b> |  |  |  |  |

|----------|-----------------------------|--|--|--|--|

| Name:    | ISI_PSIZE                   |  |  |  |  |

| Address: | 0xFFFC0020                  |  |  |  |  |

| Acess:   | Read-write                  |  |  |  |  |

| Reset:   | 0x0                         |  |  |  |  |

| 31 | 30         | 29 | 28 | 27 | 26 | 25         | 24 |  |  |

|----|------------|----|----|----|----|------------|----|--|--|

| _  | _          | —  | —  | _  | -  | PREV_HSIZE |    |  |  |

| 23 | 22         | 21 | 20 | 19 | 18 | 17         | 16 |  |  |

|    | PREV_HSIZE |    |    |    |    |            |    |  |  |

| 15 | 14         | 13 | 12 | 11 | 10 | 9          | 8  |  |  |

| _  | _          | —  | —  | _  | _  | PREV_VSIZE |    |  |  |

| 7  | 6          | 5  | 4  | 3  | 2  | 1          | 0  |  |  |

|    | PREV_VSIZE |    |    |    |    |            |    |  |  |

#### • PREV\_VSIZE: Vertical size for the preview path

Vertical Preview size = PREV\_VSIZE + 1 (480 max only in RGB mode).

#### • PREV\_HSIZE: Horizontal size for the preview path

Horizontal Preview size = PREV\_HSIZE + 1 (640 max only in RGB mode).

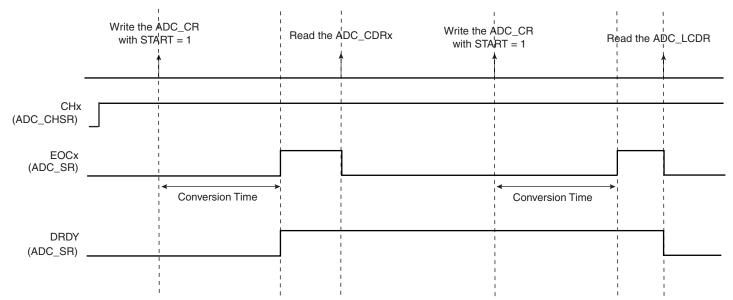

#### 42.5.4 Conversion Results

When a conversion is completed, the resulting 10-bit digital value is stored in the Channel Data Register (ADC\_CDR) of the current channel and in the ADC Last Converted Data Register (ADC\_LCDR).

The channel EOC bit in the Status Register (ADC\_SR) is set and the DRDY is set. In the case of a connected PDC channel, DRDY rising triggers a data transfer request. In any case, either EOC and DRDY can trigger an interrupt.

Reading one of the ADC\_CDR registers clears the corresponding EOC bit. Reading ADC\_LCDR clears the DRDY bit and the EOC bit corresponding to the last converted channel.

Figure 42-2. EOCx and DRDY Flag Behavior

# AT91SAM9XE128/256/512 Preliminary

| Rev                  | Comments                                                                                                                                                                                                | Change<br>Request<br>Ref. |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|                      | Overview:                                                                                                                                                                                               |                           |

| Doc.<br>Rev<br>6254B | "Features", "Ethernet MAC 10/100 Base-T", 128-byte FIFOs (typo corrected).                                                                                                                              | 5800                      |

|                      | Debug Unit (DBGU), added "mode for general purpose two-sire UART serial communication"                                                                                                                  | 5846                      |

|                      | Section 10.4.9 "Ethernet 10/100 MAC", 128-byte FIFOs (typo corrected).                                                                                                                                  | 5800                      |

|                      | Section 9.13 "Chip Identification", SAM9XE512 chip ID is 0x329AA3A0.                                                                                                                                    |                           |

|                      | Removed former Section 5.2 "Power Consumption".                                                                                                                                                         |                           |

|                      | Table 3-1, "Signal Description List", comment column updated in certain instances and "PIO Controller -         PIOA - PIOB - PIOC", has a foot note added to its comments column. SHDWN is active Low. | rfo                       |

|                      | Section 6. "I/O Line Considerations", unneeded paragraphs removed.                                                                                                                                      | rfo                       |

|                      | "Features", "Additional Embedded Memories" Fast Read Time: 45 ns.                                                                                                                                       |                           |

|                      | "Features" "Four Universal Synchronous/Asynchronous Receiver Transmitters (USART)", added Manchester Encoding/Decoding,                                                                                 | 5930                      |

|                      | Section 1. "AT91SAM9XE128/256/512 Description", 2nd and 3rd paragraphs improved.                                                                                                                        | rfo                       |

|                      | Section 6.3 "Shutdown Logic Pins", updated with external pull-up requirement.                                                                                                                           | rfo                       |

|                      | Debug and Test<br>Section 12.5 "JTAG Port Pins", added to Debug and Test.                                                                                                                               | rfo                       |

|                      | Boot Program:                                                                                                                                                                                           |                           |

|                      | Section 13.4.4 "In-Application Programming (IAP) Feature", added to datasheet.                                                                                                                          | 6190                      |

|                      | AIC:                                                                                                                                                                                                    |                           |

|                      | Section 29.6.3 "Interrupt Sources", Interrupt Source 1, OR-wiring description updated.                                                                                                                  | 5101                      |

|                      | Section 29.7.5 "Protect Mode", enabling Debug Control Protect Mode in AIC_DCR register updated.                                                                                                         | 5191                      |

|                      | Qualified/Internal on ATP                                                                                                                                                                               | 5193                      |

|                      | DBGU:                                                                                                                                                                                                   |                           |

|                      | Section 30.1 "Description", added to second paragraph; "two-pin UART can be used as stand-alone"                                                                                                        | 5846                      |

|                      | ECC:                                                                                                                                                                                                    |                           |

|                      | Section 25.4.3 "ECC Status Register 1" and Section 25.4.4 "ECC Status Register 2", ECCERRx renamed as                                                                                                   | 5542                      |

|                      | MULERRx on bitfields, 2, 18, 22, 26, 30.<br>Section 25.4.1 "ECC Control Register", added new bitfield: SRST                                                                                             | 5543                      |

|                      | EEFC:                                                                                                                                                                                                   | 50.10                     |

|                      | Section 20.4.2 "EEFC Flash Command Register", updated FARG bit field description                                                                                                                        | 5302                      |

|                      | ISI:                                                                                                                                                                                                    |                           |

|                      | Section 41.4.7 "ISI Preview Register", updated PREV_VSIZE and PREV_HSIZE with RGB only comments                                                                                                         |                           |

|                      | PMC:                                                                                                                                                                                                    |                           |

|                      | Section 28.7 "Programming Sequence", steps 5 and 6: "By default PRES parameter is set to 0"                                                                                                             | 5596                      |

|                      | RSTC:                                                                                                                                                                                                   |                           |

|                      |                                                                                                                                                                                                         | 5436                      |