Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 32MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, I2S, POR, PWM, WDT                                         |

| Number of I/O              | 11                                                                                 |

| Program Memory Size        | 32KB (32K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                        |

| Data Converters            | A/D 6x12b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                                    |

| Supplier Device Package    | PG-TSSOP-16-8                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc1100t016x0032abxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

# **Table of Contents**

| <br> .1<br> .2<br> .3<br> .4                                                                                                                                                                           | Summary of Features Ordering Information Device Types Device Type Features Chip Identification Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8<br>9<br>10                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.2.1<br>2.2.1<br>2.2.2<br>2.2.3                                                                                                                                                         | General Device Information       1         Logic Symbols       1         Pin Configuration and Definition       1         Package Pin Summary       1         Port I/O Function Description       2         Hardware Controlled I/O Function Description       2                                                                                                                                                                                                                                                                                                                                 | 13<br>15<br>18<br>20<br>22                                                 |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2.1<br>3.2.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.6.1<br>3.3.6.2<br>3.3.6.3 | Electrical Parameter  General Parameters Parameter Interpretation Absolute Maximum Ratings Pin Reliability in Overload Operating Conditions  DC Parameters Input/Output Characteristics Analog to Digital Converters (ADC) Temperature Sensor Characteristics Power Supply Current Flash Memory Parameters  AC Parameters Testing Waveforms Power-Up and Supply Monitoring Characteristics Serial Wire Debug Port (SW-DP) Timing SPD Timing Requirements Peripheral Timings Synchronous Serial Interface (USIC SSC) Timing Inter-IC (IIC) Interface Timing Inter-IC Sound (IIS) Interface Timing | 27<br>27<br>28<br>31<br>32<br>36<br>40<br>47<br>48<br>50<br>52<br>54<br>54 |

| <b>!</b><br>!.1<br>!.1.1<br>!.2                                                                                                                                                                        | Package and Reliability6Package Parameters6Thermal Considerations6Package Outlines6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61<br>61                                                                   |

|                                                                                                                                                                                                        | Quality Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 87                                                                         |

### **Summary of Features**

# 1 Summary of Features

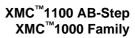

The XMC1100 devices are members of the XMC<sup>™</sup>1000 Family of microcontrollers based on the ARM Cortex-M0 processor core. The XMC1100 series devices are designed for general purpose applications.

Figure 1 System Block Diagram

### **CPU Subsystem**

- CPU Core

- High-performance 32-bit ARM Cortex-M0 CPU

- Most 16-bit Thumb and subset of 32-bit Thumb2 instruction set

- Single cycle 32-bit hardware multiplier

### **Summary of Features**

- Q: VQFN

- <PPP> package pin count

- <T> the temperature range:

- F: -40°C to 85°C

- X: -40°C to 105°C

- <FFFF> the Flash memory size.

For ordering codes for the XMC1100 please contact your sales representative or local distributor.

This document describes several derivatives of the XMC1100 series, some descriptions may not apply to a specific product. Please see **Table 1**.

For simplicity the term XMC1100 is used for all derivatives throughout this document.

### 1.2 Device Types

These device types are available and can be ordered through Infineon's direct and/or distribution channels.

Table 1 Synopsis of XMC1100 Device Types

| Derivative        | Package       | Flash<br>Kbytes | SRAM<br>Kbytes |

|-------------------|---------------|-----------------|----------------|

| XMC1100-T016F0008 | PG-TSSOP-16-8 | 8               | 16             |

| XMC1100-T016F0016 | PG-TSSOP-16-8 | 16              | 16             |

| XMC1100-T016F0032 | PG-TSSOP-16-8 | 32              | 16             |

| XMC1100-T016F0064 | PG-TSSOP-16-8 | 64              | 16             |

| XMC1100-T016X0016 | PG-TSSOP-16-8 | 16              | 16             |

| XMC1100-T016X0032 | PG-TSSOP-16-8 | 32              | 16             |

| XMC1100-T016X0064 | PG-TSSOP-16-8 | 64              | 16             |

| XMC1100-T038F0016 | PG-TSSOP-38-9 | 16              | 16             |

| XMC1100-T038F0032 | PG-TSSOP-38-9 | 32              | 16             |

| XMC1100-T038F0064 | PG-TSSOP-38-9 | 64              | 16             |

| XMC1100-T038X0064 | PG-TSSOP-38-9 | 64              | 16             |

| XMC1100-Q024F0008 | PG-VQFN-24-19 | 8               | 16             |

| XMC1100-Q024F0016 | PG-VQFN-24-19 | 16              | 16             |

| XMC1100-Q024F0032 | PG-VQFN-24-19 | 32              | 16             |

| XMC1100-Q024F0064 | PG-VQFN-24-19 | 64              | 16             |

| XMC1100-Q040F0016 | PG-VQFN-40-13 | 16              | 16             |

#### **General Device Information**

### 2 General Device Information

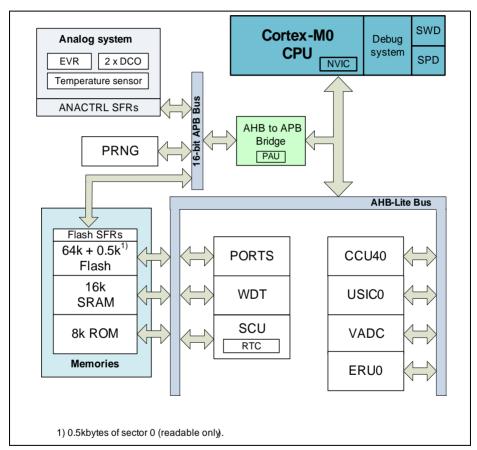

This section summarizes the logic symbols and package pin configurations with a detailed list of the functional I/O mapping.

### 2.1 Logic Symbols

Figure 2 XMC1100 Logic Symbol for TSSOP-38 and TSSOP-16

#### **General Device Information**

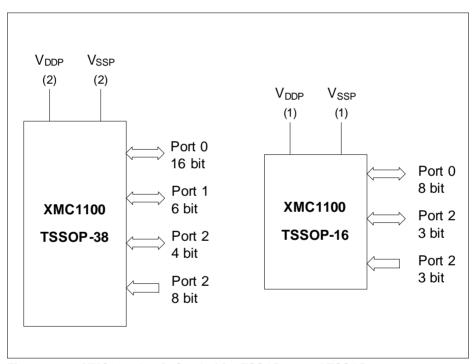

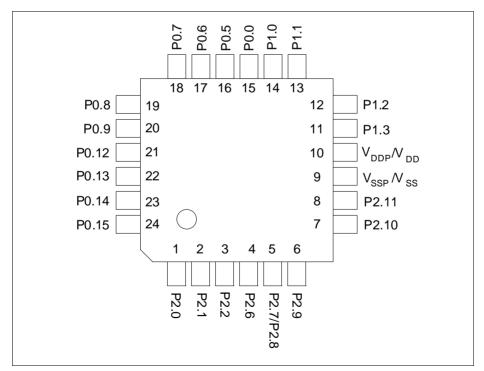

Figure 5 XMC1100 PG-TSSOP-16 Pin Configuration (top view)

Figure 6 XMC1100 PG-VQFN-24 Pin Configuration (top view)

| Function | Outputs |      |      | Inputs |        | Pull Control |            |            |  |  |  |

|----------|---------|------|------|--------|--------|--------------|------------|------------|--|--|--|

|          | HWO0    | HWO1 | HWI0 | HWI1   | HW0_PD | HW0_PU       | HW1_PD     | HW1_PU     |  |  |  |

| P2.5     |         |      |      |        |        |              |            |            |  |  |  |

| P2.6     |         |      |      |        |        |              | CCU40.OUT3 | CCU40.OUT3 |  |  |  |

| P2.7     |         |      |      |        |        |              | CCU40.OUT3 | CCU40.OUT3 |  |  |  |

| P2.8     |         |      |      |        |        |              | CCU40.OUT2 | CCU40.OUT2 |  |  |  |

| P2.9     |         |      |      |        |        |              | CCU40.OUT2 | CCU40.OUT2 |  |  |  |

| P2.10    |         |      |      |        |        |              |            |            |  |  |  |

| P2.11    |         |      |      |        |        |              |            |            |  |  |  |

If a pin current is outside of the **Operating Conditions** but within the overload conditions, then the parameters of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

Table 12 Overload Parameters

| Parameter                                                            | Symbol              |      | Values | 3    | Unit | Note /<br>Test Condition |

|----------------------------------------------------------------------|---------------------|------|--------|------|------|--------------------------|

|                                                                      |                     | Min. | Тур.   | Max. |      |                          |

| Input current on any port pin during overload condition              | I <sub>OV</sub> SR  | -5   | -      | 5    | mA   |                          |

| Absolute sum of all input circuit currents during overload condition | I <sub>OVS</sub> SR | _    | _      | 25   | mA   |                          |

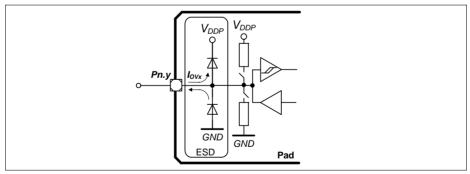

**Figure 9** shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\rm DDP}$  and ground are a simplified representation of these ESD protection structures.

Figure 9 Input Overload Current via ESD structures

**Table 13** and **Table 14** list input voltages that can be reached under overload conditions. Note that the absolute maximum input voltages as defined in the **Absolute Maximum Ratings** must not be exceeded during overload.

### Table 13 PN-Junction Characterisitics for positive Overload

| Pad Type                                | $I_{\rm OV}$ = 5 mA, $T_{\rm J}$ = -40 °C | $I_{ m OV}$ = 5 mA, $T_{ m J}$ = 115 °C |

|-----------------------------------------|-------------------------------------------|-----------------------------------------|

| Standard,<br>High-current,<br>AN/DIG_IN | $V_{IN} = V_{DDP} + 0.5 \; V$             | $V_{IN} = V_{DDP} + 0.5 \; V$           |

## Table 14 PN-Junction Characterisitics for negative Overload

| Pad Type                                | $I_{\rm OV}$ = 5 mA, $T_{\rm J}$ = -40 °C | $I_{\mathrm{OV}}$ = 5 mA, $T_{\mathrm{J}}$ = 115 °C |

|-----------------------------------------|-------------------------------------------|-----------------------------------------------------|

| Standard,<br>High-current,<br>AN/DIG_IN | $V_{IN} = V_{SS}$ - 0.5 V                 | $V_{IN} = V_{SS}$ - 0.5 V                           |

Table 16 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Symbol             |    | Limit Values |      | Unit | Test Conditions                                                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----|--------------|------|------|---------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |    | Min.         | Max. | -    |                                                                     |  |

| Pin capacitance (digital inputs/outputs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $C_{IO}$           | СС | _            | 10   | pF   |                                                                     |  |

| Pull-up resistor on port pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $R_{PUP}$          | CC | 20           | 50   | kohm | $V_{IN} = V_{SSP}$                                                  |  |

| Pull-down resistor on port pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $R_{PDP}$          | CC | 20           | 50   | kohm | $V_{IN} = V_{DDP}$                                                  |  |

| Input leakage current <sup>9)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $I_{OZP}$          | СС | -1           | 1    | μА   | $0 < V_{\rm IN} < V_{\rm DDP},$ $T_{\rm A} \le 105~{\rm ^{\circ}C}$ |  |

| Voltage on any pin during $V_{\rm DDP}$ power off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{PO}$           | SR | -            | 0.3  | V    | 10)                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $I_{MP}$           | SR | -10          | 11   | mA   | _                                                                   |  |

| Maximum current per high currrent pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $I_{MP1A}$         | SR | -10          | 50   | mA   | _                                                                   |  |

| $\begin{tabular}{ll} \hline & & & & \\ & & & & \\ & & & & \\ & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $I_{MVDD1}$        | SR | _            | 130  | mA   | 10)                                                                 |  |

| $\begin{tabular}{ll} \hline & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & $ | $I_{MVDD2}$        | SR | _            | 260  | mA   | 10)                                                                 |  |

| $\begin{tabular}{ll} \hline & & & & \\ & & & & \\ & & & & \\ & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $I_{MVSS1}$        | SR | _            | 130  | mA   | 10)                                                                 |  |

| $\begin{tabular}{ll} \hline & & & & \\ & & & & \\ & & & & \\ & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I <sub>MVSS2</sub> | SR | _            | 260  | mA   | 10)                                                                 |  |

<sup>1)</sup> Rise/Fall time parameters are taken with 10% - 90% of supply.

<sup>2)</sup> Additional rise/fall time valid for  $C_L$  = 50 pF -  $C_L$  = 100 pF @ 0.150 ns/pF at 5 V supply voltage.

<sup>3)</sup> Additional rise/fall time valid for  $C_L$  = 50 pF -  $C_L$  = 100 pF @ 0.205 ns/pF at 3.3 V supply voltage.

<sup>4)</sup> Additional rise/fall time valid for  $C_L = 50 \text{ pF} - C_L = 100 \text{ pF} @ 0.445 \text{ ns/pF}$  at 1.8 V supply voltage.

<sup>5)</sup> Additional rise/fall time valid for C<sub>1</sub> = 50 pF - C<sub>1</sub> = 100 pF @ 0.225 ns/pF at 5 V supply voltage.

<sup>6)</sup> Additional rise/fall time valid for  $C_L$  = 50 pF -  $C_L$  = 100 pF @ 0.288 ns/pF at 3.3 V supply voltage.

<sup>7)</sup> Additional rise/fall time valid for C<sub>1</sub> = 50 pF - C<sub>1</sub> = 100 pF @ 0.588 ns/pF at 1.8 V supply voltage.

- 8) Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

- 9) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin.

- 10) However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when  $V_{\rm DDP}$  is powered off.

Table 19 Power Supply Parameters; V<sub>DDP</sub> = 5V

| Parameter                                                           | Symbol                |     | Value              | s    | Unit   | Note /         |  |

|---------------------------------------------------------------------|-----------------------|-----|--------------------|------|--------|----------------|--|

|                                                                     |                       | Min | Typ. <sup>1)</sup> | Max. | -      | Test Condition |  |

|                                                                     |                       | •   |                    |      |        |                |  |

| Sleep mode current                                                  | $I_{DDPSD}CC$         | _   | 1.8                | _    | mA     | 32 / 64        |  |

| Peripherals clock disabled Flash active                             |                       |     | 1.7                | -    | mA     | 24 / 48        |  |

| $f_{\text{MCLK}}/f_{\text{PCLK}}$ in MHz <sup>5)</sup>              |                       |     | 1.6                | _    | mA     | 16 / 32        |  |

| J WOLK - J FOLK                                                     |                       |     | 1.5                | _    | mA     | 8 / 16         |  |

|                                                                     |                       |     | 1.4                | _    | mA     | 1/1            |  |

| Sleep mode current                                                  | I <sub>DDPSR</sub> CC | _   | 1.2                | _    | mA     | 32 / 64        |  |

| Peripherals clock disabled                                          |                       |     | 1.1                | _    | mA     | 24 / 48        |  |

| Flash powered down $f_{\rm MCLK}/f_{\rm PCLK}$ in MHz <sup>6)</sup> |                       |     | 1.0                | _    | mA     | 16 / 32        |  |

| JINGLA J POLK                                                       |                       |     | 0.8                | _    | mA     | 8 / 16         |  |

|                                                                     |                       |     | 0.7                | _    | mA     | 1 / 1          |  |

| Deep Sleep mode current <sup>7)</sup>                               | $I_{DDPDS}CC$         | _   | 0.24               | _    | mA     |                |  |

| Wake-up time from Sleep to Active mode <sup>8)</sup>                | t <sub>SSA</sub> CC   | _   | 6                  | _    | cycles |                |  |

| Wake-up time from Deep<br>Sleep to Active mode <sup>9)</sup>        | t <sub>DSA</sub> CC   | _   | 280                | _    | μsec   |                |  |

- 1) The typical values are measured at  $T_A$  = + 25 °C and  $V_{DDP}$  = 5 V.

- 2) CPU and all peripherals clock enabled, Flash is in active mode.

- 3) CPU enabled, all peripherals clock disabled, Flash is in active mode.

- 4) CPU in sleep, all peripherals clock enabled and Flash is in active mode.

- 5) CPU in sleep, Flash is in active mode.

- 6) CPU in sleep, Flash is powered down and code executed from RAM after wake-up.

- 7) CPU in sleep, peripherals clock disabled, Flash is powered down and code executed from RAM after wake-up.

- 8) CPU in sleep, Flash is in active mode during sleep mode.

- 9) CPU in sleep, Flash is in powered down mode during deep sleep mode.

Table 22 Power-Up and Supply Monitoring Parameters (Operating Conditions apply)<sup>1)</sup> (cont'd)

| Parameter                                               | Symbol              |      | Values |      | Unit | Note /                                                                                           |

|---------------------------------------------------------|---------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------|

|                                                         |                     | Min. | Тур.   | Max. |      | Test Condition                                                                                   |

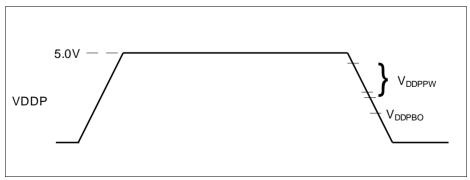

| $\overline{V_{\mathrm{DDP}}}$ brownout reset voltage    | $V_{DDPBO}$ CC      | 1.55 | 1.62   | 1.75 | V    | calibrated, before user code starts running                                                      |

| $V_{\mathrm{DDP}}$ voltage to ensure defined pad states | $V_{DDPPA}$ CC      | _    | 1.0    | _    | V    |                                                                                                  |

| Start-up time from power-on reset                       | t <sub>SSW</sub> SR | _    | 320    | _    | μS   | Time to the first<br>user code<br>instruction in all<br>start-up modes <sup>4)</sup>             |

| BMI program time                                        | t <sub>BMI</sub> SR | -    | 8.25   | _    | ms   | Time taken from a<br>user-triggered<br>system reset after<br>BMI installation is<br>is requested |

- 1) Not all parameters are 100% tested, but are verified by design/characterisation.

- A capacitor of at least 100 nF has to be added between V<sub>DDP</sub> and V<sub>SSP</sub> to fulfill the requirement as stated for this parameter.

- 3) Valid for a 100 nF buffer capacitor connected to supply pin where current from capacitor is forwarded only to the chip. A larger capacitor value has to be chosen if the power source sink a current.

- 4) This values does not include the ramp-up time. During startup firmware execution, MCLK is running at 32 MHz and the clocks to peripheral as specified in register CGATSTATO are gated.

Figure 16 Supply Threshold Parameters

### 3.3.5 SPD Timing Requirements

The optimum SPD decision time between  $0_B$  and  $1_B$  is 0.75  $\mu$ s. With this value the system has maximum robustness against frequency deviations of the sampling clock on tool and on device side. However it is not always possible to exactly match this value with the given constraints for the sample clock. For instance for a oversampling rate of 4, the sample clock will be 8 MHz and in this case the closest possible effective decision time is 5.5 clock cycles (0.69  $\mu$ s).

Table 26 Optimum Number of Sample Clocks for SPD

| Sample<br>Freq. | Sampling<br>Factor |        | Sample<br>Clocks 1 <sub>B</sub> | Effective<br>Decision<br>Time <sup>1)</sup> | Remark                                                                             |

|-----------------|--------------------|--------|---------------------------------|---------------------------------------------|------------------------------------------------------------------------------------|

| 8 MHz           | 4                  | 1 to 5 | 6 to 12                         | 0.69 µs                                     | The other closest option (0.81 µs) for the effective decision time is less robust. |

<sup>1)</sup> Nominal sample frequency period multiplied with 0.5 + (max. number of 0<sub>R</sub> sample clocks)

For a balanced distribution of the timing robustness of SPD between tool and device, the timing requirements for the tool are:

- Frequency deviation of the sample clock is +/- 5%

- Effective decision time is between 0.69  $\mu s$  and 0.75  $\mu s$  (calculated with nominal sample frequency)

# 3.3.6 Peripheral Timings

Note: These parameters are not subject to production test, but verified by design and/or characterization.

### 3.3.6.1 Synchronous Serial Interface (USIC SSC) Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: Operating Conditions apply.

Table 27 USIC SSC Master Mode Timing

| Parameter                                                         | Symbo                    | ı    | Values | S    | Unit | Note /         |

|-------------------------------------------------------------------|--------------------------|------|--------|------|------|----------------|

|                                                                   |                          | Min. | Тур.   | Max. |      | Test Condition |

| SCLKOUT master clock period                                       | t <sub>CLK</sub> CC      | 62.5 | -      | _    | ns   |                |

| Slave select output SELO active to first SCLKOUT transmit edge    | t <sub>1</sub> CC        | 80   | -      | -    | ns   |                |

| Slave select output SELO inactive after last SCLKOUT receive edge | t <sub>2</sub> CC        | 0    | _      | _    | ns   |                |

| Data output DOUT[3:0] valid time                                  | <i>t</i> <sub>3</sub> CC | -10  | -      | 10   | ns   |                |

| Receive data input DX0/DX[5:3] setup time to SCLKOUT receive edge | t <sub>4</sub> SF        | 80   | _      | -    | ns   |                |

| Data input DX0/DX[5:3]<br>hold time from SCLKOUT<br>receive edge  | t <sub>5</sub> SF        | 0    | -      | -    | ns   |                |

# 3.3.6.2 Inter-IC (IIC) Interface Timing

The following parameters are applicable for a USIC channel operated in IIC mode.

Note: Operating Conditions apply.

Table 29 USIC IIC Standard Mode Timing<sup>1)</sup>

| Parameter                                        | Symbol                   | Values |      |      | Unit | Note /         |

|--------------------------------------------------|--------------------------|--------|------|------|------|----------------|

|                                                  |                          | Min.   | Тур. | Max. |      | Test Condition |

| Fall time of both SDA and SCL                    | t <sub>1</sub><br>CC/SR  | -      | -    | 300  | ns   |                |

| Rise time of both SDA and SCL                    | t <sub>2</sub><br>CC/SR  | -      | -    | 1000 | ns   |                |

| Data hold time                                   | t <sub>3</sub><br>CC/SR  | 0      | -    | -    | μs   |                |

| Data set-up time                                 | t <sub>4</sub><br>CC/SR  | 250    | -    | -    | ns   |                |

| LOW period of SCL clock                          | t <sub>5</sub><br>CC/SR  | 4.7    | -    | -    | μs   |                |

| HIGH period of SCL clock                         | t <sub>6</sub><br>CC/SR  | 4.0    | -    | -    | μs   |                |

| Hold time for (repeated)<br>START condition      | t <sub>7</sub><br>CC/SR  | 4.0    | -    | -    | μs   |                |

| Set-up time for repeated START condition         | t <sub>8</sub><br>CC/SR  | 4.7    | -    | -    | μs   |                |

| Set-up time for STOP condition                   | t <sub>9</sub><br>CC/SR  | 4.0    | -    | -    | μs   |                |

| Bus free time between a STOP and START condition | t <sub>10</sub><br>CC/SR | 4.7    | -    | -    | μs   |                |

| Capacitive load for each bus line                | $C_{b}SR$                | -      | -    | 400  | pF   |                |

Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

Figure 20 USIC IIC Stand and Fast Mode Timing

## 3.3.6.3 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode.  $\label{eq:using_parameters}$

Note: Operating Conditions apply.

Table 31 USIC IIS Master Transmitter Timing

| Parameter       | Symbol            | Values              |      |            | Unit | Note /              |

|-----------------|-------------------|---------------------|------|------------|------|---------------------|

|                 |                   | Min.                | Тур. | Max.       |      | Test Condition      |

| Clock period    | t <sub>1</sub> CC | $2/f_{MCLK}$        | -    | -          | ns   | $V_{DDP} \geq 3\;V$ |

|                 |                   | 4/f <sub>MCLK</sub> | -    | -          | ns   | $V_{DDP}\!<\!3\;V$  |

| Clock HIGH      | t <sub>2</sub> CC | 0.35 x              | -    | -          | ns   |                     |

|                 |                   | $t_{1min}$          |      |            |      |                     |

| Clock Low       | t <sub>3</sub> CC | 0.35 x              | -    | -          | ns   |                     |

|                 |                   | $t_{1min}$          |      |            |      |                     |

| Hold time       | t <sub>4</sub> CC | 0                   | -    | -          | ns   |                     |

| Clock rise time | t <sub>5</sub> CC | -                   | -    | 0.15 x     | ns   |                     |

|                 |                   |                     |      | $t_{1min}$ |      |                     |

### Package and Reliability

The internal power consumption is defined as  $P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} - V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\mathsf{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\rm DDP}$ , if possible in the system

- · Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers

### Package and Reliability

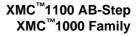

Figure 24 PG-TSSOP-16-8

### Package and Reliability

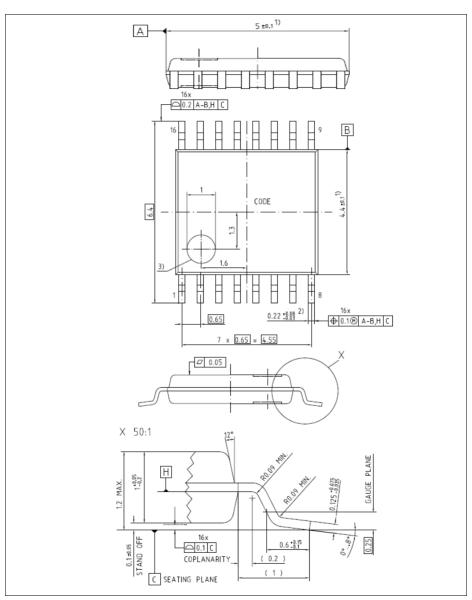

Figure 25 PG-VQFN-24-19

www.infineon.com

Published by Infineon Technologies AG