Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 32MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 26                                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K × 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                        |

| Data Converters            | A/D 12x12b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

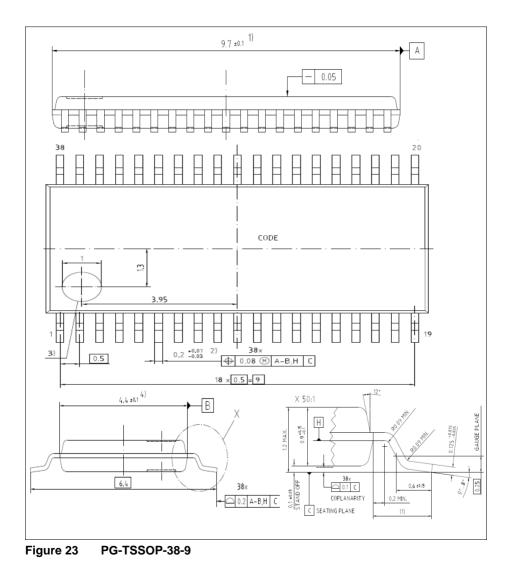

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                                    |

| Supplier Device Package    | PG-TSSOP-38-9                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc1100t038f0064abxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## XMC1100 Data Sheet

## Revision History: V1.7 2016-08

| Previous V | /ersion: V1.6                                                                                                                                                                                                                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page       | Subjects                                                                                                                                                                                                                                                                                                         |

| many       | Added XMC <sup>™</sup> trademark                                                                                                                                                                                                                                                                                 |

| Page 23    | Removed ADC channels from Port I/O Functions table, which are not available in XMC1100 (G1CH0, G1CH2, G1CH3, G1CH4).                                                                                                                                                                                             |

| Page 36    | Removed auxiliary $V_{\text{REFGND}}$ for G1CH0, as this channel is not available in XMC1100.                                                                                                                                                                                                                    |

| Page 36    | Adjusted ADC sample time and sample rate to configurable limits.                                                                                                                                                                                                                                                 |

| Page 46    | <ul> <li>Flash Memory Parameters Table:</li> <li>Erase time per page parameter is renamed to Erase time per page / sector.</li> <li>Erase cycles parameter is renamed to include test condition of sum of page and sector erase cycles.</li> <li>Added parameter for fixed wait states configuration.</li> </ul> |

## Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, XMC<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

ARM<sup>®</sup>, ARM Powered<sup>®</sup> and AMBA<sup>®</sup> are registered trademarks of ARM, Limited.

Cortex<sup>®</sup>, CoreSight<sup>TM</sup>, ETM<sup>TM</sup>, Embedded Trace Macrocell<sup>TM</sup> and Embedded Trace Buffer<sup>TM</sup> are trademarks of ARM, Limited.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

#### About this Document

## About this Document

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC1100 series devices.

The document describes the characteristics of a superset of the XMC1100 series devices. For simplicity, the various device types are referred to by the collective term XMC1100 throughout this document.

## XMC<sup>™</sup>1000 Family User Documentation

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

# Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by Users Guides and Application Notes.

Please refer to http://www.infineon.com/xmc1000 to get access to the latest versions of those documents.

#### **Summary of Features**

## Table 1Synopsis of XMC1100 Device Types (cont'd)

| Derivative        | Package       | Flash<br>Kbytes | SRAM<br>Kbytes |

|-------------------|---------------|-----------------|----------------|

| XMC1100-Q040F0032 | PG-VQFN-40-13 | 32              | 16             |

| XMC1100-Q040F0064 | PG-VQFN-40-13 | 64              | 16             |

## 1.3 Device Type Features

The following table lists the available features per device type.

#### Table 2 Features of XMC1100 Device Types<sup>1)</sup>

| Derivative   | ADC channel |

|--------------|-------------|

| XMC1100-T016 | 6           |

| XMC1100-T038 | 12          |

| XMC1100-Q024 | 8           |

| XMC1100-Q040 | 12          |

1) Features that are not included in this table are available in all the derivatives

| Package     | VADC0 G0 | VADC0 G1     |

|-------------|----------|--------------|

| PG-TSSOP-16 | CH0CH5   | -            |

| PG-TSSOP-38 | CH0CH7   | CH1, CH5 CH7 |

| PG-VQFN-24  | CH0CH7   | -            |

| PG-VQFN-40  | CH0CH7   | CH1, CH5 CH7 |

## 1.4 Chip Identification Number

The Chip Identification Number allows software to identify the marking. It is a 8 words value with the most significant 7 words stored in Flash configuration sector 0 (CS0) at address location : 1000 0F00<sub>H</sub> (MSB) - 1000 0F1B<sub>H</sub> (LSB). The least significant word and most significant word of the Chip Identification Number are the value of registers DBGROMID and IDCHIP, respectively.

## 2.2 Pin Configuration and Definition

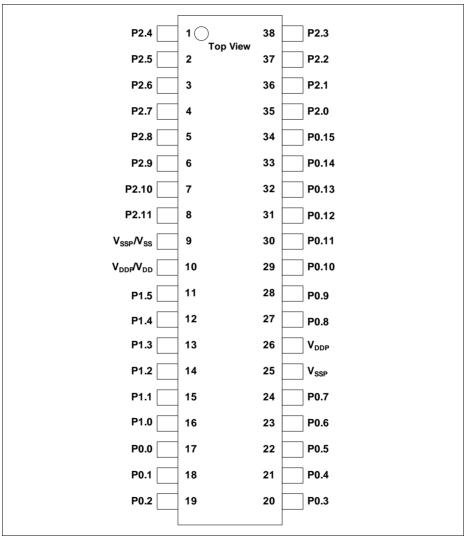

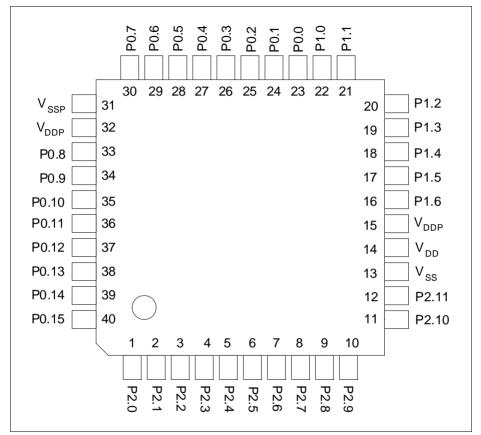

The following figures summarize all pins, showing their locations on the different packages.

Figure 4 XMC1100 PG-TSSOP-38 Pin Configuration (top view)

## XMC<sup>™</sup>1100 AB-Step XMC<sup>™</sup>1000 Family

## **General Device Information**

## 2.2.1 Package Pin Summary

The following general building block is used to describe each pin:

## Table 5 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad Type |

|----------|-----------|-----------|--------------|

| Px.y     | Ν         | Ν         | Pad Class    |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type:

- STD\_INOUT (standard bi-directional pads)

- STD\_INOUT/AN (standard bi-directional pads with analog input)

- High Current (high current bi-directional pads)

- STD\_IN/AN (standard input pads with analog input)

- Power (power supply)

Details about the pad properties are defined in the Electrical Parameters.

| Function | VQFN<br>40 | TSSOP<br>38 | VQFN<br>24 | TSSOP<br>16 | Pad Type  | Notes |

|----------|------------|-------------|------------|-------------|-----------|-------|

| P0.0     | 23         | 17          | 15         | 7           | STD_INOUT |       |

| P0.1     | 24         | 18          | -          | -           | STD_INOUT |       |

| P0.2     | 25         | 19          | -          | -           | STD_INOUT |       |

| P0.3     | 26         | 20          | -          | -           | STD_INOUT |       |

| P0.4     | 27         | 21          | -          | -           | STD_INOUT |       |

| P0.5     | 28         | 22          | 16         | 8           | STD_INOUT |       |

| P0.6     | 29         | 23          | 17         | 9           | STD_INOUT |       |

| P0.7     | 30         | 24          | 18         | 10          | STD_INOUT |       |

| P0.8     | 33         | 27          | 19         | 11          | STD_INOUT |       |

| P0.9     | 34         | 28          | 20         | 12          | STD_INOUT |       |

| P0.10    | 35         | 29          | -          | -           | STD_INOUT |       |

| P0.11    | 36         | 30          | -          | -           | STD_INOUT |       |

| P0.12    | 37         | 31          | 21         | -           | STD_INOUT |       |

## Table 6 Package Pin Mapping

| Table 6Package Pin Mapping (cont'd) |            |             |    |             |                  |                                                                   |  |

|-------------------------------------|------------|-------------|----|-------------|------------------|-------------------------------------------------------------------|--|

| Function                            | VQFN<br>40 | TSSOP<br>38 |    | TSSOP<br>16 | Pad Type         | Notes                                                             |  |

| P0.13                               | 38         | 32          | 22 | -           | STD_INOUT        |                                                                   |  |

| P0.14                               | 39         | 33          | 23 | 13          | STD_INOUT        |                                                                   |  |

| P0.15                               | 40         | 34          | 24 | 14          | STD_INOUT        |                                                                   |  |

| P1.0                                | 22         | 16          | 14 | -           | High Current     |                                                                   |  |

| P1.1                                | 21         | 15          | 13 | -           | High Current     |                                                                   |  |

| P1.2                                | 20         | 14          | 12 | -           | High Current     |                                                                   |  |

| P1.3                                | 19         | 13          | 11 | -           | High Current     |                                                                   |  |

| P1.4                                | 18         | 12          | -  | -           | High Current     |                                                                   |  |

| P1.5                                | 17         | 11          | -  | -           | High Current     |                                                                   |  |

| P1.6                                | 16         | -           | -  | -           | STD_INOUT        |                                                                   |  |

| P2.0                                | 1          | 35          | 1  | 15          | STD_INOUT/<br>AN |                                                                   |  |

| P2.1                                | 2          | 36          | 2  | -           | STD_INOUT/<br>AN |                                                                   |  |

| P2.2                                | 3          | 37          | 3  | -           | STD_IN/AN        |                                                                   |  |

| P2.3                                | 4          | 38          | -  | -           | STD_IN/AN        |                                                                   |  |

| P2.4                                | 5          | 1           | -  | -           | STD_IN/AN        |                                                                   |  |

| P2.5                                | 6          | 2           | -  | -           | STD_IN/AN        |                                                                   |  |

| P2.6                                | 7          | 3           | 4  | 16          | STD_IN/AN        |                                                                   |  |

| P2.7                                | 8          | 4           | 5  | 1           | STD_IN/AN        |                                                                   |  |

| P2.8                                | 9          | 5           | 5  | 1           | STD_IN/AN        |                                                                   |  |

| P2.9                                | 10         | 6           | 6  | 2           | STD_IN/AN        |                                                                   |  |

| P2.10                               | 11         | 7           | 7  | 3           | STD_INOUT/<br>AN |                                                                   |  |

| P2.11                               | 12         | 8           | 8  | 4           | STD_INOUT/<br>AN |                                                                   |  |

| VSS                                 | 13         | 9           | 9  | 5           | Power            | Supply GND, ADC reference GND                                     |  |

| VDD                                 | 14         | 10          | 10 | 6           | Power            | Supply VDD, ADC<br>reference voltage/<br>ORC reference<br>voltage |  |

## Table 6 Package Pin Mapping (cont'd)

| l able 6 | ible 6 Package Pin Mapping (cont d) |             |             |             |          |                                                                                                                                                                                                                                                                              |  |  |

|----------|-------------------------------------|-------------|-------------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Function | VQFN<br>40                          | TSSOP<br>38 | VQFN<br>24  | TSSOP<br>16 | Pad Type | Notes                                                                                                                                                                                                                                                                        |  |  |

| VDDP     | 15                                  | 10          | 10          | 6           | Power    | When VDD is<br>supplied, VDDP has<br>to be supplied with the<br>same voltage.                                                                                                                                                                                                |  |  |

| VSSP     | 31                                  | 25          | -           | -           | Power    | I/O port ground                                                                                                                                                                                                                                                              |  |  |

| VDDP     | 32                                  | 26          | -           | -           | Power    | I/O port supply                                                                                                                                                                                                                                                              |  |  |

| VSSP     | Exp.<br>Pad                         | -           | Exp.<br>Pad | -           | Power    | <b>Exposed Die Pad</b><br>The exposed die pad<br>is connected internally<br>to VSSP. For proper<br>operation, it is<br>mandatory to connect<br>the exposed pad to<br>the board ground. For<br>thermal aspects,<br>please refer to the<br>Package and<br>Reliability chapter. |  |  |

## Table 6 Package Pin Mapping (cont'd)

## 2.2.2 Port I/O Function Description

The following general building block is used to describe the I/O functions of each PORT pin:

## Table 7 Port I/O Function Description

| Function | Outputs  |          | Inputs   |          |

|----------|----------|----------|----------|----------|

|          | ALT1     | ALTn     | Input    | Input    |

| P0.0     |          | MODA.OUT | MODC.INA |          |

| Pn.y     | MODA.OUT |          | MODA.INA | MODC.INB |

## Table 10 Hardware Controlled I/O Functions

| Function |      | Outputs          |      | Inputs           | Pull Control |        |            |            |  |

|----------|------|------------------|------|------------------|--------------|--------|------------|------------|--|

|          | HWO0 | HWO1             | HWIO | HWI1             | HW0_PD       | HW0_PU | HW1_PD     | HW1_PU     |  |

| P0.0     |      |                  |      |                  |              |        |            |            |  |

| P0.1     |      |                  |      |                  |              |        |            |            |  |

| P0.2     |      |                  |      |                  |              |        |            |            |  |

| P0.3     |      |                  |      |                  |              |        |            |            |  |

| P0.4     |      |                  |      |                  |              |        |            |            |  |

| P0.5     |      |                  |      |                  |              |        |            |            |  |

| P0.6     |      |                  |      |                  |              |        |            |            |  |

| P0.7     |      |                  |      |                  |              |        |            |            |  |

| P0.8     |      |                  |      |                  |              |        |            |            |  |

| P0.9     |      |                  |      |                  |              |        |            |            |  |

| P0.10    |      |                  |      |                  |              |        |            |            |  |

| P0.11    |      |                  |      |                  |              |        |            |            |  |

| P0.12    |      |                  |      |                  |              |        |            |            |  |

| P0.13    |      |                  |      |                  |              |        |            |            |  |

| P0.14    |      |                  |      |                  |              |        |            |            |  |

| P0.15    |      |                  |      |                  |              |        |            |            |  |

| P1.0     |      | USIC0_CH0. DOUT0 |      | USIC0_CH0. HWIN0 |              |        |            |            |  |

| P1.1     |      | USIC0_CH0. DOUT1 |      | USIC0_CH0. HWIN1 |              |        |            |            |  |

| P1.2     |      | USIC0_CH0. DOUT2 |      | USIC0_CH0. HWIN2 |              |        |            |            |  |

| P1.3     |      | USIC0_CH0. DOUT3 |      | USIC0_CH0. HWIN3 |              |        |            |            |  |

| P1.4     |      |                  |      |                  |              |        |            |            |  |

| P1.5     |      |                  |      |                  |              |        |            |            |  |

| P1.6     |      |                  |      |                  |              |        |            |            |  |

| P2.0     |      |                  |      |                  |              |        |            |            |  |

| P2.1     |      |                  |      |                  |              |        |            |            |  |

| P2.2     |      |                  |      |                  |              |        | CCU40.OUT3 | CCU40.OUT3 |  |

| P2.3     |      |                  |      |                  |              |        |            |            |  |

| P2.4     |      |                  |      |                  |              |        |            |            |  |

Infineon

XMC<sup>™</sup>1100 AB-Step XMC<sup>™</sup>1000 Family

25

Data Sheet

V1.7, 2016-08 Subject to Agreement on the Use of Product Information

## 3 Electrical Parameter

This section provides the electrical parameter which are implementation-specific for the XMC1100.

## 3.1 General Parameters

## 3.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XMC1100 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

• CC

Such parameters indicate **C**ontroller **C**haracteristics, which are distinctive feature of the XMC1100 and must be regarded for a system design.

SR

Such parameters indicate **S**ystem **R**equirements, which must be provided by the application system in which the XMC1100 is designed in.

| Table 13                                | PN-Junction Characterisitics for positive Overload |                                           |  |  |  |  |  |  |

|-----------------------------------------|----------------------------------------------------|-------------------------------------------|--|--|--|--|--|--|

| Pad Type                                | $I_{\rm OV}$ = 5 mA, $T_{\rm J}$ = -40 °C          | $I_{\rm OV}$ = 5 mA, $T_{\rm J}$ = 115 °C |  |  |  |  |  |  |

| Standard,<br>High-current,<br>AN/DIG_IN | $V_{\rm IN} = V_{\rm DDP}$ + 0.5 V                 | $V_{\rm IN} = V_{\rm DDP}$ + 0.5 V        |  |  |  |  |  |  |

#### Table 14 **PN-Junction Characterisitics for negative Overload**

| Pad Type                                | I <sub>ov</sub> = 5 mA, T <sub>J</sub> = -40 °C | I <sub>ον</sub> = 5 mA, T <sub>J</sub> = 115 °C |

|-----------------------------------------|-------------------------------------------------|-------------------------------------------------|

| Standard,<br>High-current,<br>AN/DIG_IN | $V_{\rm IN}$ = $V_{\rm SS}$ - 0.5 V             | $V_{\rm IN}$ = $V_{\rm SS}$ - 0.5 V             |

## Table 16 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                | Symbol            |                   | Limit Values                                            |                          | Unit | Test Conditions                                  |  |

|----------------------------------------------------------|-------------------|-------------------|---------------------------------------------------------|--------------------------|------|--------------------------------------------------|--|

|                                                          |                   |                   | Min.                                                    | Max.                     |      |                                                  |  |

| Input low voltage on port<br>pins<br>(Large Hysteresis)  | V <sub>ILPL</sub> | SR                | -                                                       | $0.08 \times V_{ m DDP}$ | V    | CMOS Mode<br>(5 V, 3.3 V & 2.2 V) <sup>10)</sup> |  |

| Input high voltage on<br>port pins<br>(Large Hysteresis) | $V_{IHPL}$        | SR                | $0.85 \times V_{ m DDP}$                                | -                        | V    | CMOS Mode<br>(5 V, 3.3 V & 2.2 V) <sup>10)</sup> |  |

| Rise time on High                                        | t <sub>HCPR</sub> | CC                | _                                                       | 9                        | ns   | 50 pF @ 5 V <sup>2)</sup>                        |  |

| Current Pad <sup>1)</sup>                                |                   |                   | _                                                       | 12                       | ns   | 50 pF @ 3.3 V <sup>3)</sup>                      |  |

|                                                          |                   |                   | -                                                       | 25                       | ns   | 50 pF @ 1.8 V <sup>4)</sup>                      |  |

| Fall time on High                                        | t <sub>HCPF</sub> | CC                | _                                                       | 9                        | ns   | 50 pF @ 5 V <sup>2)</sup>                        |  |

| Current Pad <sup>1)</sup>                                |                   |                   | _                                                       | 12                       | ns   | 50 pF @ 3.3 V <sup>3)</sup>                      |  |

|                                                          |                   |                   | -                                                       | 25                       | ns   | 50 pF @ 1.8 V <sup>4)</sup>                      |  |

| Rise time on Standard                                    | t <sub>R</sub>    | CC                | -                                                       | 12                       | ns   | 50 pF @ 5 V <sup>5)</sup>                        |  |

| Pad <sup>1)</sup>                                        |                   |                   | -                                                       | 15                       | ns   | 50 pF @ 3.3 V <sup>6)</sup>                      |  |

|                                                          |                   |                   | -                                                       | 31                       | ns   | 50 pF @ 1.8 V <sup>7)</sup>                      |  |

| Fall time on Standard                                    | t <sub>F</sub> C  | t <sub>F</sub> CC | -                                                       | 12                       | ns   | 50 pF @ 5 V <sup>5)</sup>                        |  |

| Pad <sup>1)</sup>                                        |                   |                   | -                                                       | 15                       | ns   | 50 pF @ 3.3 V <sup>6)</sup>                      |  |

|                                                          |                   |                   | -                                                       | 31                       | ns   | 50 pF @ 1.8 V <sup>7)</sup>                      |  |

| Input Hysteresis <sup>8)</sup>                           | HYS CO            | СС                | $\begin{array}{c} 0.08 \times \ V_{ m DDP} \end{array}$ | -                        | V    | CMOS Mode (5 V),<br>Standard Hysteresis          |  |

|                                                          |                   |                   | $0.03 	imes V_{ m DDP}$                                 | -                        | V    | CMOS Mode (3.3 V),<br>Standard Hysteresis        |  |

|                                                          |                   |                   | $0.02 	imes V_{ m DDP}$                                 | -                        | V    | CMOS Mode (2.2 V),<br>Standard Hysteresis        |  |

|                                                          |                   |                   | $0.5 	imes V_{ m DDP}$                                  | $0.75 	imes V_{ m DDP}$  | V    | CMOS Mode(5 V),<br>Large Hysteresis              |  |

|                                                          |                   |                   | $0.4 	imes V_{ m DDP}$                                  | $0.75 	imes V_{ m DDP}$  | V    | CMOS Mode(3.3 V),<br>Large Hysteresis            |  |

|                                                          |                   |                   | $0.2 	imes V_{ m DDP}$                                  | $0.65 \times V_{ m DDP}$ | V    | CMOS Mode(2.2 V),<br>Large Hysteresis            |  |

- Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

- 9) An additional error current  $(I_{INJ})$  will flow if an overload current flows through an adjacent pin.

- 10) However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when  $V_{\text{DDP}}$  is powered off.

| Table 17 ADC Cha                                 | (Operating Conditions apply)'' (cont'd) |      |       |                            |           |                                                                                              |

|--------------------------------------------------|-----------------------------------------|------|-------|----------------------------|-----------|----------------------------------------------------------------------------------------------|

| Parameter                                        | Symbol                                  |      | Value | s                          | Unit      | Note /                                                                                       |

|                                                  |                                         | Min. | Тур.  | Max.                       |           | Test Condition                                                                               |

| Maximum sample rate in 8-bit mode <sup>3)</sup>  | $f_{C8}$ CC                             | -    | -     | f <sub>ADC</sub> /<br>38.5 | -         | 1 sample<br>pending                                                                          |

|                                                  |                                         | -    | -     | f <sub>ADC</sub> /<br>54.5 | -         | 2 samples<br>pending                                                                         |

| RMS noise <sup>4)</sup>                          | EN <sub>RMS</sub> CC                    | -    | 1.5   | -                          | LSB<br>12 | DC input,<br>$V_{DD} = 5.0 \text{ V},$<br>$V_{AIN} = 2.5 \text{ V},$<br>$25^{\circ}\text{C}$ |

| DNL error                                        | EA <sub>DNL</sub> CC                    | -    | ±2.0  | -                          | LSB<br>12 |                                                                                              |

| INL error                                        | EA <sub>INL</sub> CC                    | -    | ±4.0  | -                          | LSB<br>12 |                                                                                              |

| Gain error with external reference               | EA <sub>GAIN</sub> CC                   | -    | ±0.5  | -                          | %         | SHSCFG.AREF = 00 <sub>B</sub> (calibrated)                                                   |

| Gain error with internal reference <sup>5)</sup> | EA <sub>GAIN</sub> CC                   | -    | ±3.6  | -                          | %         | SHSCFG.AREF =<br>1X <sub>B</sub> (calibrated),<br>-40°C - 105°C                              |

|                                                  |                                         | -    | ±2.0  | -                          | %         | SHSCFG.AREF = $1X_B$ (calibrated), $0^{\circ}C - 85^{\circ}C$                                |

| Offset error                                     | EA <sub>OFF</sub> CC                    | -    | ±8.0  | -                          | mV        | Calibrated,<br>$V_{\rm DD}$ = 5.0 V                                                          |

## Table 17 ADC Characteristics (Operating Conditions apply)<sup>1)</sup> (cont'd)

1) The parameters are defined for ADC clock frequency  $f_{SH}$  = 32MHz.

2) No pending samples assumed, excluding sampling time and calibration.

3) Includes synchronization and calibration (average of gain and offset calibration).

4) This parameter can also be defined as an SNR value: SNR[dB] =  $20 \times \log(A_{MAXeff} / N_{RMS})$ . With  $A_{MAXeff} = 2^N / 2$ , SNR[dB] =  $20 \times \log (2048 / N_{RMS})$  [N = 12].  $N_{RMS} = 1.5$  LSB12, therefore, equals SNR =  $20 \times \log (2048 / 1.5) = 62.7$  dB.

5) Includes error from the reference voltage.

## 3.2.3 Temperature Sensor Characteristics

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                     | Symbol                              | Values |      |      | Unit | Note /                                  |

|-------------------------------|-------------------------------------|--------|------|------|------|-----------------------------------------|

|                               |                                     | Min.   | Тур. | Max. |      | Test Condition                          |

| Measurement time              | t <sub>M</sub> CC                   | _      | -    | 10   | ms   |                                         |

| Temperature sensor range      | $T_{\rm SR}{ m SR}$                 | -40    | _    | 115  | °C   |                                         |

| Sensor Accuracy <sup>1)</sup> | $T_{\text{TSAL}} \operatorname{CC}$ | -6     | -    | 6    | °C   | <i>T</i> <sub>J</sub> > 20°C            |

|                               |                                     | -10    | —    | 10   | °C   | $0^{\circ}C \le T_{J} \le 20^{\circ}C$  |

|                               |                                     | -18    | -    | 18   | °C   | $-25^{\circ}C \le T_{J} < 0^{\circ}C$   |

|                               |                                     | -31    | -    | 31   | °C   | $-40^{\circ}C \le T_{J} < -25^{\circ}C$ |

| Start-up time after enabling  | t <sub>TSSTE</sub> SR               | -      | -    | 15   | μS   |                                         |

## Table 18 Temperature Sensor Characteristics

1) The temperature sensor accuracy is independent of the supply voltage.

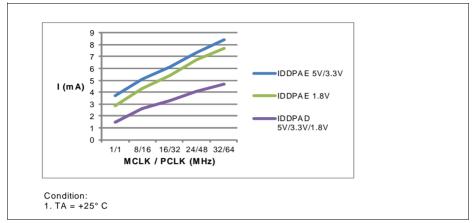

**Figure 11** shows typical graphs for active mode supply current for  $V_{DDP} = 5V$ ,  $V_{DDP} = 3.3V$ ,  $V_{DDP} = 1.8V$  across different clock frequencies.

Figure 11 Active mode, a) peripherals clocks enabled, b) peripherals clocks disabled: Supply current I<sub>DDPA</sub> over supply voltage V<sub>DDP</sub> for different clock frequencies

43

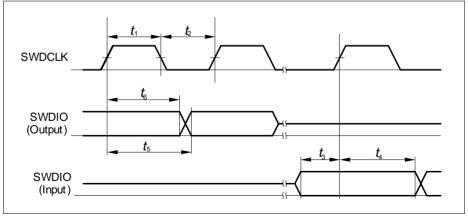

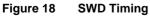

## 3.3.4 Serial Wire Debug Port (SW-DP) Timing

The following parameters are applicable for communication through the SW-DP interface.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                      | Symbol            | Values |      |        | Unit | Note /                 |

|------------------------------------------------|-------------------|--------|------|--------|------|------------------------|

|                                                |                   | Min.   | Тур. | Max.   |      | Test Condition         |

| SWDCLK high time                               | t <sub>1</sub> SR | 50     | -    | 500000 | ns   | -                      |

| SWDCLK low time                                | t <sub>2</sub> SR | 50     | _    | 500000 | ns   | -                      |

| SWDIO input setup to SWDCLK rising edge        | t <sub>3</sub> SR | 10     | -    | -      | ns   | -                      |

| SWDIO input hold<br>after SWDCLK rising edge   | t <sub>4</sub> SR | 10     | -    | -      | ns   | -                      |

| SWDIO output valid time                        | t <sub>5</sub> CC | -      | -    | 68     | ns   | C <sub>L</sub> = 50 pF |

| after SWDCLK rising edge                       |                   | -      | -    | 62     | ns   | C <sub>L</sub> = 30 pF |

| SWDIO output hold time from SWDCLK rising edge | t <sub>6</sub> CC | 4      | -    | -      | ns   |                        |

| Table 25 | <b>SWD Interface Timing Parameters</b> (Operating Conditions apply) |

|----------|---------------------------------------------------------------------|

|          |                                                                     |

52

## Table 30 USIC IIC Fast Mode Timing<sup>1)</sup>

| Parameter                                              | Symbol                   |                            | Values | 5    | Unit | Note /<br>Test Condition |

|--------------------------------------------------------|--------------------------|----------------------------|--------|------|------|--------------------------|

|                                                        |                          | Min.                       | Тур.   | Max. |      |                          |

| Fall time of both SDA and SCL                          | t <sub>1</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -      | 300  | ns   |                          |

| Rise time of both SDA and SCL                          | t <sub>2</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -      | 300  | ns   |                          |

| Data hold time                                         | t <sub>3</sub><br>CC/SR  | 0                          | -      | -    | μs   |                          |

| Data set-up time                                       | t <sub>4</sub><br>CC/SR  | 100                        | -      | -    | ns   |                          |

| LOW period of SCL clock                                | t <sub>5</sub><br>CC/SR  | 1.3                        | -      | -    | μs   |                          |

| HIGH period of SCL clock                               | t <sub>6</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Hold time for (repeated)<br>START condition            | t <sub>7</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Set-up time for repeated START condition               | t <sub>8</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Set-up time for STOP condition                         | t <sub>9</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Bus free time between a<br>STOP and START<br>condition | t <sub>10</sub><br>CC/SR | 1.3                        | -      | -    | μs   |                          |

| Capacitive load for each bus line                      | $C_{\rm b}{\rm SR}$      | -                          | -      | 400  | pF   |                          |

1) Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

2) C<sub>b</sub> refers to the total capacitance of one bus line in pF.

Package and Reliability

## 4.2 Package Outlines

## **Quality Declaration**

## 5 Quality Declaration

Table 34 shows the characteristics of the quality parameters in the XMC1100.

## Table 34 Quality Parameters

| Parameter                                                             | Symbol                 | Limit V | alues | Unit | Notes                                       |  |

|-----------------------------------------------------------------------|------------------------|---------|-------|------|---------------------------------------------|--|

|                                                                       |                        | Min.    | Max.  |      |                                             |  |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub><br>SR | -       | 2000  | V    | Conforming to<br>EIA/JESD22-<br>A114-B      |  |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | $V_{\rm CDM}$ SR       | -       | 500   | V    | Conforming to<br>JESD22-C101-C              |  |

| Moisture sensitivity level                                            | MSL<br>CC              | -       | 3     | -    | JEDEC<br>J-STD-020D                         |  |

| Soldering temperature                                                 | $T_{ m SDR}$<br>SR     | -       | 260   | °C   | Profile according<br>to JEDEC<br>J-STD-020D |  |