Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 30/20MHz                                                                 |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c51rb2-lcb |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4. SFR Mapping

The Special Function Registers (SFRs) of the TS80C51Rx2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3, P4, P5

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- HDW Watchdog Timer Reset: WDTRST, WDTPRG

- PCA registers: CL, CH, CCAPiL, CCAPiH, CCON, CMOD, CCAPMi

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

#### Table 1. All SFRs with their address and their reset value

|     | Bit<br>addressable                 |                    | Non Bit addressable |                     |                      |                      |                      |                                     |     |  |  |  |

|-----|------------------------------------|--------------------|---------------------|---------------------|----------------------|----------------------|----------------------|-------------------------------------|-----|--|--|--|

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |  |  |

| F8h |                                    | CH<br>0000 0000    | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAPL2H<br>XXXX XXXX | CCAPL3H<br>XXXX XXXX | CCAPL4H<br>XXXX XXXX |                                     | FFh |  |  |  |

| F0h | B<br>0000 0000                     |                    |                     |                     |                      |                      |                      |                                     | F7h |  |  |  |

| E8h | P5 bit<br>addressable<br>1111 1111 | CL<br>0000 0000    | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                                     | EFh |  |  |  |

| E0h | ACC<br>0000 0000                   |                    |                     |                     |                      |                      |                      |                                     | E7h |  |  |  |

| D8h | CCON<br>00X0 0000                  | CMOD<br>00XX X000  | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                                     | DFh |  |  |  |

| D0h | PSW<br>0000 0000                   |                    |                     |                     |                      |                      |                      |                                     | D7h |  |  |  |

| C8h | T2CON<br>0000 0000                 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                                     | CFh |  |  |  |

| C0h | P4 bit<br>addressable<br>1111 1111 |                    |                     |                     |                      |                      |                      | P5 byte<br>addressable<br>1111 1111 | C7h |  |  |  |

| B8h | IP<br>X000 000                     | SADEN<br>0000 0000 |                     |                     |                      |                      |                      |                                     | BFh |  |  |  |

| B0h | P3<br>1111 1111                    |                    |                     |                     |                      |                      |                      | IPH<br>X000 0000                    | B7h |  |  |  |

| A8h | IE<br>0000 0000                    | SADDR<br>0000 0000 |                     |                     |                      |                      |                      |                                     | AFh |  |  |  |

| A0h | P2<br>1111 1111                    |                    | AUXR1<br>XXXX0XX0   |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000                 | A7h |  |  |  |

| 98h | SCON<br>0000 0000                  | SBUF<br>XXXX XXXX  |                     |                     |                      |                      |                      |                                     | 9Fh |  |  |  |

| 90h | P1<br>1111 1111                    |                    |                     |                     |                      |                      |                      |                                     | 97h |  |  |  |

| 88h | TCON<br>0000 0000                  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XXXXXX00     | CKCON<br>XXXX XXX0                  | 8Fh |  |  |  |

| 80h | P0<br>1111 1111                    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000                   | 87h |  |  |  |

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |  |  |

|     | macaminad                          |                    |                     |                     |                      |                      |                      |                                     |     |  |  |  |

reserved

| Reset | 9 | 10 | 4 | Ι | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ . If the hardware watchdog reaches its time-out, the reset pin becomes an output during the time the internal reset is |

|-------|---|----|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |   |    |   |   | activated.                                                                                                                                                                                                                                                                                                                                         |

### **5.1. Pin Description for 64/68 pin Packages**

Port 4 and Port 5 are 8-bit bidirectional I/O ports with internal pull-ups. Pins that have 1 written to them are pulled high by the internal pull ups and can be used as inputs.

As inputs, pins that are externally pulled low will source current because of the internal pull-ups.

Refer to the previous pin description for other pins.

|      | PLCC68 | SQUARE VQFP64<br>1.4 |

|------|--------|----------------------|

| VSS  | 51     | 9/40                 |

| VCC  | 17     | 8                    |

| P0.0 | 15     | 6                    |

| P0.1 | 14     | 5                    |

| P0.2 | 12     | 3                    |

| P0.3 | 11     | 2                    |

| P0.4 | 9      | 64                   |

| P0.5 | 6      | 61                   |

| P0.6 | 5      | 60                   |

| P0.7 | 3      | 59                   |

| P1.0 | 19     | 10                   |

| P1.1 | 21     | 12                   |

| P1.2 | 22     | 13                   |

| P1.3 | 23     | 14                   |

| P1.4 | 25     | 16                   |

| P1.5 | 27     | 18                   |

| P1.6 | 28     | 19                   |

| P1.7 | 29     | 20                   |

| P2.0 | 54     | 43                   |

| P2.1 | 55     | 44                   |

| P2.2 | 56     | 45                   |

| P2.3 | 58     | 47                   |

| P2.4 | 59     | 48                   |

| P2.5 | 61     | 50                   |

| P2.6 | 64     | 53                   |

| P2.7 | 65     | 54                   |

| P3.0 | 34     | 25                   |

| P3.1 | 39     | 28                   |

#### Table 3. CKCON Register

#### CKCON - Clock Control Register (8Fh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|---|---|---|---|---|---|---|----|

| - | - | - | - | - | - | - | X2 |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                     |  |  |  |  |  |  |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |  |  |  |  |  |  |

| 6          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |  |  |  |  |  |  |

| 5          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |  |  |  |  |  |  |

| 4          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |  |  |  |  |  |  |

| 3          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |  |  |  |  |  |  |

| 2          | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |  |  |  |  |  |  |

| 1          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |  |  |  |  |  |  |

| 0          | X2              | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |  |  |  |  |  |  |

Reset Value = XXXX XXX0b Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel-wm.com)

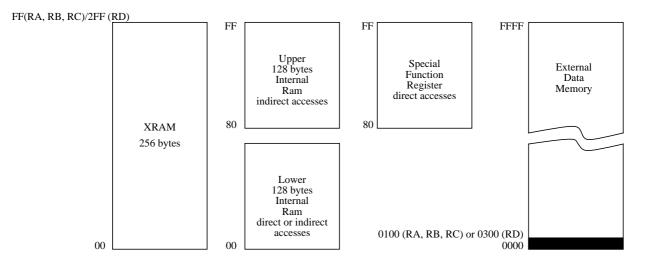

## 6.3. Expanded RAM (XRAM)

The TS80C51Rx2 provide additional Bytes of ramdom access memory (RAM) space for increased data parameter handling and high level language usage.

RA2, RB2 and RC2 devices have 256 bytes of expanded RAM, from 00H to FFH in external data space; RD2 devices have 768 bytes of expanded RAM, from 00H to 2FFH in external data space.

The TS80C51Rx2 has internal data memory that is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register. (See Table 5.)

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

- Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data ,accesses the SFR at location 0A0H (which is P2).

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

- The 256 or 768 XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first 256 or 768 bytes of external data memory.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 ( $\overline{WR}$ ) and P3.7 ( $\overline{RD}$ ). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than FFH (i.e. 0100H to FFFFH) (higher than 2FFH (i.e. 0300H to FFFFH for RD devices) will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, so with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Refer to Figure . For RD devices, accesses to expanded RAM from 100H to 2FFH can only be done thanks to the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @Ri and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ Ri and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

Figure 4. Internal and External Data Memory Address

| Ad | AUXR<br>Address 08EH |             |                                                           | -                                            | -           | -                | -          | -          | EXTRA<br>M   | AO       |  |

|----|----------------------|-------------|-----------------------------------------------------------|----------------------------------------------|-------------|------------------|------------|------------|--------------|----------|--|

|    | Reset                | value       | Х                                                         | Х                                            | Х           | X                | Х          | Х          | 0            | 0        |  |

|    | Symbol               |             |                                                           |                                              |             | Function         | ı          |            |              |          |  |

|    | -                    | Not imple   | mented, 1                                                 | eserved fo                                   | or future u | se. <sup>a</sup> |            |            |              |          |  |

|    | AO                   | Disable/E1  | nable AL                                                  | E                                            |             |                  |            |            |              |          |  |

|    |                      | AO          | Ope                                                       | Operating Mode                               |             |                  |            |            |              |          |  |

|    |                      | 0           |                                                           | E is emitte<br>mode is u                     |             | istant rate      | of 1/6 the | oscillator | frequency (o | r 1/3 if |  |

|    |                      | 1           | ALI                                                       | E is active                                  | only duri   | ng a MOV         | X or MO    | VC instruc | tion         |          |  |

|    | EXTRAM               | Internal/E: | nal/External RAM (00H-FFH) access using MOVX @ Ri/ @ DPTR |                                              |             |                  |            |            |              |          |  |

|    |                      | EXTRA       | M Ope                                                     | Operating Mode                               |             |                  |            |            |              |          |  |

|    |                      | 0           | Inte                                                      | Internal XRAM access using MOVX @ Ri/ @ DPTR |             |                  |            |            |              |          |  |

|    |                      | 1           | Exte                                                      | External data memory access                  |             |                  |            |            |              |          |  |

Table 5. Auxiliary Register AUXR

a. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

### Table 6. T2CON Register

### T2CON - Timer 2 Control Register (C8h)

| 7          | 6               | 5                                                                                                                                                                                                                                                                                            | 4                                                                                                                                                                                                                                                                                                                          | 3                                           | 2    | 1                    | 0                   |  |  |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|----------------------|---------------------|--|--|

| TF2        | EXF2            | RCLK                                                                                                                                                                                                                                                                                         | TCLK                                                                                                                                                                                                                                                                                                                       | EXEN2                                       | TR2  | C/T2#                | CP/RL2#             |  |  |

| Bit Number | Bit<br>Mnemonic |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            | Descrip                                     | tion |                      |                     |  |  |

| 7          | TF2             | Must be cleared                                                                                                                                                                                                                                                                              | imer 2 overflow Flag<br>Must be cleared by software.<br>Set by hardware on timer 2 overflow, if RCLK = 0 and TCLK = 0.                                                                                                                                                                                                     |                                             |      |                      |                     |  |  |

| 6          | EXF2            | Set when a captu<br>When set, causes                                                                                                                                                                                                                                                         | imer 2 External Flag<br>Set when a capture or a reload is caused by a negative transition on T2EX pin if EXEN2=1.<br>When set, causes the CPU to vector to timer 2 interrupt routine when timer 2 interrupt is enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down counter mode (DCEN = 1) |                                             |      |                      |                     |  |  |

| 5          | RCLK            |                                                                                                                                                                                                                                                                                              | Receive Clock bit<br>Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                                                                                        |                                             |      |                      |                     |  |  |

| 4          | TCLK            |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            | nsmit clock for ser<br>mit clock for seria  |      |                      |                     |  |  |

| 3          | EXEN2           |                                                                                                                                                                                                                                                                                              | vents on T2EX pin                                                                                                                                                                                                                                                                                                          | n for timer 2 operat<br>en a negative trans |      | is detected, if time | er 2 is not used to |  |  |

| 2          | TR2             | Timer 2 Run control bit<br>Clear to turn off timer 2.<br>Set to turn on timer 2.                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                            |                                             |      |                      |                     |  |  |

| 1          | C/T2#           | Timer/Counter 2 select bit         Clear for timer operation (input from internal clock system: F <sub>OSC</sub> ).         Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0 for clock out mode.                                                         |                                                                                                                                                                                                                                                                                                                            |                                             |      |                      |                     |  |  |

| 0          | CP/RL2#         | Timer 2 Capture/Reload bit<br>If RCLK=1 or TCLK=1, CP/RL2# is ignored and timer is forced to auto-reload on timer 2 overflow.<br>Clear to auto-reload on timer 2 overflows or negative transitions on T2EX pin if EXEN2=1.<br>Set to capture on negative transitions on T2EX pin if EXEN2=1. |                                                                                                                                                                                                                                                                                                                            |                                             |      |                      |                     |  |  |

Reset Value = 0000 0000b Bit addressable

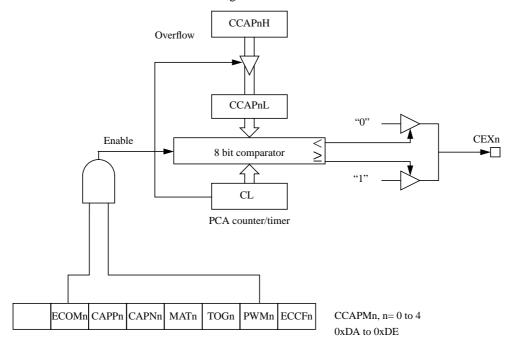

• The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

### 6.5.4. Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 12 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

Figure 12. PCA PWM Mode

## 6.5.5. PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 10 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. periodically change the compare value so it will never match the PCA timer,

- 2. periodically change the PCA timer value so it will never match the compare values, or

- 3. disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

## Table 16. SCON Register

#### SCON - Serial Control Register (98h)

| 7          | 6               | 5                           |                                                                                                                                                                                                                                                       | 4                                      | 3                                                             | 2                                      | 1                               | 0                  |  |  |

|------------|-----------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------|----------------------------------------|---------------------------------|--------------------|--|--|

| FE/SM0     | SM1             | SM2 REN TB8 RB8 TI          |                                                                                                                                                                                                                                                       |                                        |                                                               |                                        |                                 |                    |  |  |

| Bit Number | Bit<br>Mnemonic |                             |                                                                                                                                                                                                                                                       |                                        | Descrip                                                       | tion                                   | -                               |                    |  |  |

| 7          | FE              | Clear to<br>Set by h        | Framing Error bit (SMOD0=1)<br>Clear to reset the error state, not cleared by a valid stop bit.<br>Set by hardware when an invalid stop bit is detected.<br>SMOD0 must be set to enable access to the FE bit                                          |                                        |                                                               |                                        |                                 |                    |  |  |

|            | SM0             |                             | SM1 for                                                                                                                                                                                                                                               | serial port mode                       | selection.<br>access to the SM0                               | bit                                    |                                 |                    |  |  |

|            |                 | Serial port I<br><u>SM0</u> | Mode bit<br><u>SM1</u>                                                                                                                                                                                                                                |                                        | Descripti                                                     | on Baud Rate                           | 2                               |                    |  |  |

| 6          | SM1             | 0<br>0<br>1<br>1            | 0<br>1<br>0<br>1                                                                                                                                                                                                                                      | 0<br>1<br>2<br>3                       | Shift Reg<br>8-bit UAI<br>9-bit UAI<br>9-bit UAI              | RT Variable<br>RT F <sub>XTAL</sub> /6 | 4 or F <sub>XTAL</sub> /32 (/32 |                    |  |  |

| 5          | SM2             | Clear to<br>Set to en       | disable n                                                                                                                                                                                                                                             | nultiprocessor cor<br>tiprocessor comm | cessor Communic<br>nmunication featur<br>unication feature ir | e.                                     | l eventually mode               | 1. This bit should |  |  |

| 4          | REN             |                             | disable s                                                                                                                                                                                                                                             | t<br>erial reception.<br>al reception. |                                                               |                                        |                                 |                    |  |  |

| 3          | TB8             | Clear to                    | transmit                                                                                                                                                                                                                                              | a logic 0 in the 9t logic 1 in the 9t  |                                                               | d 3.                                   |                                 |                    |  |  |

| 2          | RB8             | Cleared<br>Set by h         | Receiver Bit 8 / Ninth bit received in modes 2 and 3<br>Cleared by hardware if 9th bit received is a logic 0.<br>Set by hardware if 9th bit received is a logic 1.<br>In mode 1, if SM2 = 0, RB8 is the received stop bit. In mode 0 RB8 is not used. |                                        |                                                               |                                        |                                 |                    |  |  |

| 1          | TI              | Clear to                    | <b>Transmit Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the stop bit in the other modes.                                                                 |                                        |                                                               |                                        |                                 |                    |  |  |

| 0          | RI              |                             | acknowle                                                                                                                                                                                                                                              | edge interrupt.                        | th bit time in mode                                           | 0, see Figure 14.                      | and Figure 15. in               | the other modes.   |  |  |

Reset Value = 0000 0000b Bit addressable

### Table 17. PCON Register

#### PCON - Power Control Register (87h)

| 7          | 7 6             |                                                                                                | 4                                                                                                            |         | 3                  | 2                    | 1                   | 0   |  |

|------------|-----------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------|--------------------|----------------------|---------------------|-----|--|

| SMOD1      | SMOD            | ) -                                                                                            | POI                                                                                                          | F       | GF1                | GF0                  | PD                  | IDL |  |

| Bit Number | Bit<br>Mnemonic | c Description                                                                                  |                                                                                                              |         |                    |                      |                     |     |  |

| 7          | SMOD1           | Serial port Mo<br>Set to sele                                                                  | <b>de bit 1</b><br>ct double baud ra                                                                         | te in m | ode 1, 2 or 3.     |                      |                     |     |  |

| 6          | SMOD0           |                                                                                                | <b>de bit 0</b><br>ect SM0 bit in S0<br>lect FE bit in SC0                                                   |         |                    |                      |                     |     |  |

| 5          | -               | Reserved<br>The value                                                                          | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                              |         |                    |                      |                     |     |  |

| 4          | POF             |                                                                                                | cognize next reset                                                                                           |         | rom 0 to its nomin | al voltage. Can also | o be set by softwar | re. |  |

| 3          | GF1             |                                                                                                | se Flag<br>user for general j<br>for general purp                                                            |         |                    |                      |                     |     |  |

| 2          | GF0             | Cleared by                                                                                     | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage. |         |                    |                      |                     |     |  |

| 1          | PD              | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode. |                                                                                                              |         |                    |                      |                     |     |  |

| 0          | IDL             | Idle mode bit<br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode.  |                                                                                                              |         |                    |                      |                     |     |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

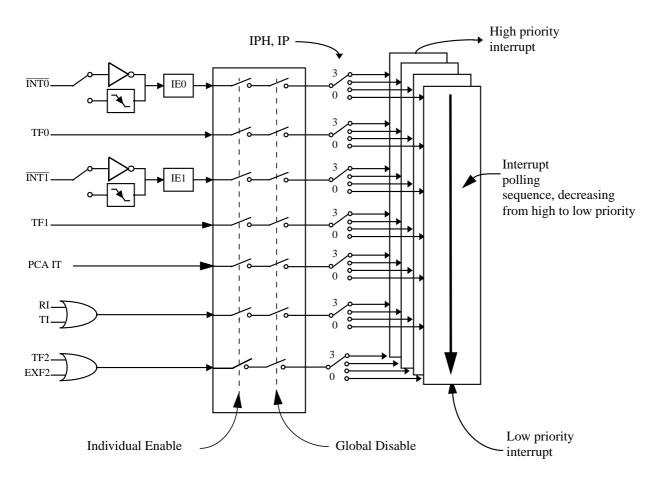

### 6.7. Interrupt System

The TS80C51Rx2 has a total of 7 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), three timer interrupts (timers 0, 1 and 2), the serial port interrupt and the PCA global interrupt. These interrupts are shown in Figure 16.

WARNING: Note that in the first version of RC devices, the PCA interrupt is in the lowest priority. Thus the order in INTO, TF0, INT1, TF1, RI or TI, TF2 or EXF2, PCA.

#### Figure 16. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 19.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 20.) and in the Interrupt Priority High register (See Table 21.). shows the bit values and priority levels associated with each combination.

The PCA interrupt vector is located at address 0033H. All other vector addresses are the same as standard C52 devices.

| Table 22. | The state of | ports during | idle and | power-down mode |

|-----------|--------------|--------------|----------|-----------------|

|-----------|--------------|--------------|----------|-----------------|

| Mode       | Program<br>Memory | ALE | PSEN | PORT0      | PORT1     | PORT2     | PORT3     |

|------------|-------------------|-----|------|------------|-----------|-----------|-----------|

| Idle       | Internal          | 1   | 1    | Port Data* | Port Data | Port Data | Port Data |

| Idle       | External          | 1   | 1    | Floating   | Port Data | Address   | Port Data |

| Power Down | Internal          | 0   | 0    | Port Data* | Port Data | Port Data | Port Data |

| Power Down | External          | 0   | 0    | Floating   | Port Data | Port Data | Port Data |

\* Port 0 can force a "zero" level. A "one" will leave port floating.

### 6.13. Reduced EMI Mode

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

#### Table 27. AUXR Register

#### AUXR - Auxiliary Register (8Eh)

| 7          | 6               | 5                          | 4                                                                                                                                  | 3                   | 2             | 1      | 0  |  |  |  |  |  |

|------------|-----------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------|--------|----|--|--|--|--|--|

| -          | -               | -                          | -                                                                                                                                  | -                   | -             | EXTRAM | AO |  |  |  |  |  |

| Bit Number | Bit<br>Mnemonic |                            | Description                                                                                                                        |                     |               |        |    |  |  |  |  |  |

| 7          | -               | Reserved<br>The value read | eserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                     |                     |               |        |    |  |  |  |  |  |

| 6          | -               | Reserved<br>The value read | from this bit is inde                                                                                                              | terminate. Do not s | set this bit. |        |    |  |  |  |  |  |

| 5          | -               | Reserved<br>The value read | from this bit is inde                                                                                                              | terminate. Do not s | set this bit. |        |    |  |  |  |  |  |

| 4          | -               | Reserved<br>The value read | from this bit is inde                                                                                                              | terminate. Do not s | set this bit. |        |    |  |  |  |  |  |

| 3          | -               | Reserved<br>The value read | from this bit is inde                                                                                                              | terminate. Do not s | set this bit. |        |    |  |  |  |  |  |

| 2          | -               | Reserved<br>The value read | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                    |                     |               |        |    |  |  |  |  |  |

| 1          | EXTRAM          | EXTRAM bit<br>See Table 5. |                                                                                                                                    |                     |               |        |    |  |  |  |  |  |

| 0          | AO              |                            | ALE Output bit<br>Clear to restore ALE operation during internal fetches.<br>Set to disable ALE operation during internal fetches. |                     |               |        |    |  |  |  |  |  |

Reset Value = XXXX XX00b Not bit addressable

# **10. Electrical Characteristics**

## 10.1. Absolute Maximum Ratings <sup>(1)</sup>

| Ambiant Temperature Under Bias:               |                                    |

|-----------------------------------------------|------------------------------------|

| C = commercial                                | 0°C to 70°C                        |

| I = industrial                                | -40°C to 85°C                      |

| Storage Temperature                           | $-65^{\circ}C$ to $+ 150^{\circ}C$ |

| Voltage on V <sub>CC</sub> to V <sub>SS</sub> | -0.5 V to + 7 V                    |

| Voltage on V <sub>PP</sub> to V <sub>SS</sub> | -0.5 V to + 13 V                   |

| Voltage on Any Pin to V <sub>SS</sub>         | -0.5 V to $V_{CC}$ + 0.5 V         |

| Power Dissipation                             | $1 W^{(2)}$                        |

NOTES

1. Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

2. This value is based on the maximum allowable die temperature and the thermal resistance of the package.

### 10.2. Power consumption measurement

Since the introduction of the first C51 devices, every manufacturer made operating Icc measurements under reset, which made sense for the designs were the CPU was running under reset. In Atmel Wireless & Microcontrollers new devices, the CPU is no more active during reset, so the power consumption is very low but is not really representative of what will happen in the customer system. That's why, while keeping measurements under Reset, Atmel Wireless & Microcontrollers presents a new way to measure the operating Icc:

Using an internal test ROM, the following code is executed:

Label: SJMP Label (80 FE)

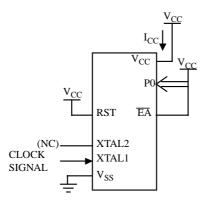

Ports 1, 2, 3 are disconnected, Port 0 is tied to FFh, EA = Vcc, RST = Vss, XTAL2 is not connected and XTAL1 is driven by the clock.

This is much more representative of the real operating Icc.

| Symbol                  | Parameter                                                    | Min | Тур | Max                                                | Unit | Test Conditions        |

|-------------------------|--------------------------------------------------------------|-----|-----|----------------------------------------------------|------|------------------------|

| I <sub>CC</sub><br>idle | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |     |     | 0.15 Freq<br>(MHz) + 0.2<br>@12MHz 2<br>@16MHz 2.6 | mA   | $V_{CC} = 3.3 V^{(2)}$ |

NOTES

1.  $I_{CC}$  under reset is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns (see Figure 24.),  $V_{IL} = V_{SS} + 0.5$  V,  $V_{IH} = V_{CC} - 0.5$ V; XTAL2 N.C.;  $\overline{EA} = RST = Port \ 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used.

2. Idle  $I_{CC}$  is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns,  $V_{IL} = V_{SS} + 0.5$  V,  $V_{IH} = V_{CC} - 0.5$  V; XTAL2 N.C; Port  $0 = V_{CC}$ ;  $\overline{EA} = RST = V_{SS}$  (see Figure 22.).

3. Power Down  $I_{CC}$  is measured with all output pins disconnected;  $\overline{EA} = V_{SS}$ , PORT  $0 = V_{CC}$ ; XTAL2 NC.; RST =  $V_{SS}$  (see Figure 23.).

4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the  $V_{OL}s$  of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi  $V_{OL}$  peak 0.6V. A Schmitt Trigger use is not necessary.

5. Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

6. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port:

Port 0: 26 mA

Ports 1, 2, 3 and 4 and 5 when available: 15 mA

Maximum total I<sub>OL</sub> for all output pins: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions. 7. For other values, please contact your sales office.

8. Operating  $I_{CC}$  is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns (see Figure 24.),  $V_{IL} = V_{SS} + 0.5$  V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ . The internal ROM runs the code 80 FE (label: SJMP label).  $I_{CC}$  would be slightly higher if a crystal oscillator is used. Measurements are made with OTP products when possible, which is the worst case.

All other pins are disconnected.

Figure 20. I<sub>CC</sub> Test Condition, under reset

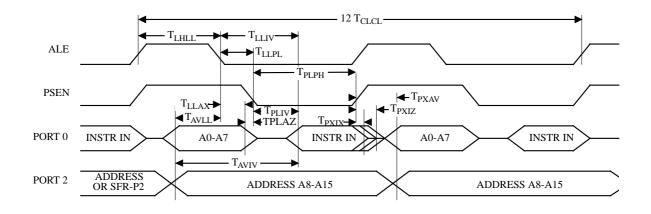

## **10.5.2. External Program Memory Characteristics**

| Table | 36. | Symbol | Description |

|-------|-----|--------|-------------|

|-------|-----|--------|-------------|

| Symbol            | Parameter                         |

|-------------------|-----------------------------------|

| Т                 | Oscillator clock period           |

| T <sub>LHLL</sub> | ALE pulse width                   |

| T <sub>AVLL</sub> | Address Valid to ALE              |

| T <sub>LLAX</sub> | Address Hold After ALE            |

| T <sub>LLIV</sub> | ALE to Valid Instruction In       |

| T <sub>LLPL</sub> | ALE to PSEN                       |

| T <sub>PLPH</sub> | PSEN Pulse Width                  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In      |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN |

| T <sub>PXIZ</sub> | Input Instruction FloatAfter PSEN |

| T <sub>PXAV</sub> | PSEN to Address Valid             |

| T <sub>AVIV</sub> | Address to Valid Instruction In   |

| T <sub>PLAZ</sub> | PSEN Low to Address Float         |

### Table 37. AC Parameters for Fix Clock

| Speed             |     | M<br>MHz | X2 1<br>30 1 | V<br>node<br>MHz<br>z equiv. | standar | V<br>rd mode<br>MHz | -L<br>X2 mode<br>20 MHz<br>40 MHz equiv. |     | X2 mode standard mode<br>20 MHz 30 MHz |     | Units |

|-------------------|-----|----------|--------------|------------------------------|---------|---------------------|------------------------------------------|-----|----------------------------------------|-----|-------|

| Symbol            | Min | Max      | Min          | Max                          | Min     | Max                 | Min                                      | Max | Min                                    | Max |       |

| Т                 | 25  |          | 33           |                              | 25      |                     | 50                                       |     | 33                                     |     | ns    |

| T <sub>LHLL</sub> | 40  |          | 25           |                              | 42      |                     | 35                                       |     | 52                                     |     | ns    |

| T <sub>AVLL</sub> | 10  |          | 4            |                              | 12      |                     | 5                                        |     | 13                                     |     | ns    |

| T <sub>LLAX</sub> | 10  |          | 4            |                              | 12      |                     | 5                                        |     | 13                                     |     | ns    |

| T <sub>LLIV</sub> |     | 70       |              | 45                           |         | 78                  |                                          | 65  |                                        | 98  | ns    |

| T <sub>LLPL</sub> | 15  |          | 9            |                              | 17      |                     | 10                                       |     | 18                                     |     | ns    |

| T <sub>PLPH</sub> | 55  |          | 35           |                              | 60      |                     | 50                                       |     | 75                                     |     | ns    |

| T <sub>PLIV</sub> |     | 35       |              | 25                           |         | 50                  |                                          | 30  |                                        | 55  | ns    |

| T <sub>PXIX</sub> | 0   |          | 0            |                              | 0       |                     | 0                                        |     | 0                                      |     | ns    |

| T <sub>PXIZ</sub> |     | 18       |              | 12                           |         | 20                  |                                          | 10  |                                        | 18  | ns    |

| T <sub>AVIV</sub> |     | 85       |              | 53                           |         | 95                  |                                          | 80  |                                        | 122 | ns    |

| T <sub>PLAZ</sub> |     | 10       |              | 10                           |         | 10                  |                                          | 10  |                                        | 10  | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -M | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10 | 8  | 15 | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30 | 22 | 35 | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20 | 15 | 25 | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40 | 25 | 45 | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7  | 5  | 15 | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40 | 30 | 45 | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10 | 10 | 10 | ns    |

Table 38. AC Parameters for a Variable Clock: derating formula

## 10.5.3. External Program Memory Read Cycle

Figure 25. External Program Memory Read Cycle

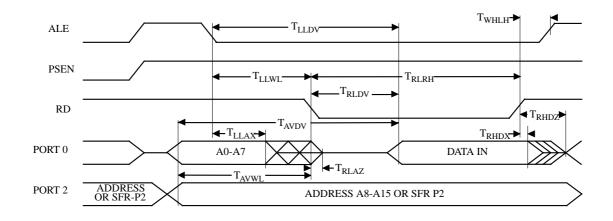

### **10.5.4. External Data Memory Characteristics**

| Parameter                                     |

|-----------------------------------------------|

| RD Pulse Width                                |

| WR Pulse Width                                |

| RD to Valid Data In                           |

| Data Hold After RD                            |

| Data Float After RD                           |

| ALE to Valid Data In                          |

| Address to Valid Data In                      |

| ALE to $\overline{WR}$ or $\overline{RD}$     |

| Address to $\overline{WR}$ or $\overline{RD}$ |

| Data Valid to $\overline{WR}$ Transition      |

| Data set-up to WR High                        |

| Data Hold After $\overline{WR}$               |

| RD Low to Address Float                       |

| RD or WR High to ALE high                     |

|                                               |

### Table 39. Symbol Description

### 10.5.6. External Data Memory Read Cycle

Figure 27. External Data Memory Read Cycle

### 10.5.7. Serial Port Timing - Shift Register Mode

### Table 42. Symbol Description

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

Table 43. AC Parameters for a Fix Clock

| Speed             | -M<br>40 MHz |     | -V<br>X2 mode<br>30 MHz<br>60 MHz equiv. |     | -V<br>standard mode<br>40 MHz |     | -L<br>X2 mode<br>20 MHz<br>40 MHz equiv. |     | -L<br>standard mode<br>30 MHz |     | Units |

|-------------------|--------------|-----|------------------------------------------|-----|-------------------------------|-----|------------------------------------------|-----|-------------------------------|-----|-------|

| Symbol            | Min          | Max | Min                                      | Max | Min                           | Max | Min                                      | Max | Min                           | Max |       |

| T <sub>XLXL</sub> | 300          |     | 200                                      |     | 300                           |     | 300                                      |     | 400                           |     | ns    |

| T <sub>QVHX</sub> | 200          |     | 117                                      |     | 200                           |     | 200                                      |     | 283                           |     | ns    |

| T <sub>XHQX</sub> | 30           |     | 13                                       |     | 30                            |     | 30                                       |     | 47                            |     | ns    |

| T <sub>XHDX</sub> | 0            |     | 0                                        |     | 0                             |     | 0                                        |     | 0                             |     | ns    |

| T <sub>XHDV</sub> |              | 117 |                                          | 34  |                               | 117 |                                          | 117 |                               | 200 | ns    |