Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40/20MHz                                                                 |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIL                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c51rb2-mca |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **5.1. Pin Description for 64/68 pin Packages**

Port 4 and Port 5 are 8-bit bidirectional I/O ports with internal pull-ups. Pins that have 1 written to them are pulled high by the internal pull ups and can be used as inputs.

As inputs, pins that are externally pulled low will source current because of the internal pull-ups.

Refer to the previous pin description for other pins.

|      | PLCC68 | SQUARE VQFP64<br>1.4 |

|------|--------|----------------------|

| VSS  | 51     | 9/40                 |

| VCC  | 17     | 8                    |

| P0.0 | 15     | 6                    |

| P0.1 | 14     | 5                    |

| P0.2 | 12     | 3                    |

| P0.3 | 11     | 2                    |

| P0.4 | 9      | 64                   |

| P0.5 | 6      | 61                   |

| P0.6 | 5      | 60                   |

| P0.7 | 3      | 59                   |

| P1.0 | 19     | 10                   |

| P1.1 | 21     | 12                   |

| P1.2 | 22     | 13                   |

| P1.3 | 23     | 14                   |

| P1.4 | 25     | 16                   |

| P1.5 | 27     | 18                   |

| P1.6 | 28     | 19                   |

| P1.7 | 29     | 20                   |

| P2.0 | 54     | 43                   |

| P2.1 | 55     | 44                   |

| P2.2 | 56     | 45                   |

| P2.3 | 58     | 47                   |

| P2.4 | 59     | 48                   |

| P2.5 | 61     | 50                   |

| P2.6 | 64     | 53                   |

| P2.7 | 65     | 54                   |

| P3.0 | 34     | 25                   |

| P3.1 | 39     | 28                   |

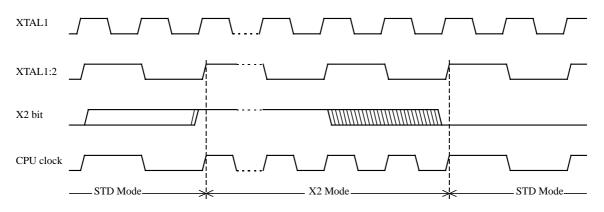

The X2 bit in the CKCON register (See Table 3.) allows to switch from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature (X2 mode).

#### CAUTION

In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals using clock frequency as time reference (UART, timers, PCA...) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. UART with 4800 baud rate will have 9600 baud rate.

#### Table 3. CKCON Register

#### CKCON - Clock Control Register (8Fh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|---|---|---|---|---|---|---|----|

| - | - | - | - | - | - | - | X2 |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                     |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 6          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 5          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 4          | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 3          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 2          | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 1          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 0          | X2              | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |

Reset Value = XXXX XXX0b Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel-wm.com)

### ASSEMBLY LANGUAGE

; Block move using dual data pointers ; Destroys DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added

| 00A2                                         | AUXR1 EQU 0A2H                                  |                                                                                                              |

|----------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| ;<br>0000 909000<br>0003 05A2<br>0005 90A000 | MOV DPTR,#SOURCE<br>INC AUXR1<br>MOV DPTR,#DEST | ; address of SOURCE<br>; switch data pointers<br>; address of DEST                                           |

| 0008<br>0008 05A2<br>000A E0                 | LOOP:<br>INC AUXR1<br>MOVX A,@DPTR              | ; switch data pointers<br>; get a byte from SOURCE                                                           |

| 000B A3<br>000C 05A2<br>000E F0              | INC DPTR<br>INC AUXR1<br>MOVX @DPTR.A           | ; increment SOURCE address<br>; switch data pointers<br>; write the byte to DEST                             |

| 000E F0<br>000F A3<br>0010 70F6<br>0012 05A2 | INC DPTR<br>JNZ LOOP<br>INC AUXR1               | ; write the byte to DEST<br>; increment DEST address<br>; check for 0 terminator<br>; (optional) restore DPS |

|                                              |                                                 |                                                                                                              |

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

## 6.3. Expanded RAM (XRAM)

The TS80C51Rx2 provide additional Bytes of ramdom access memory (RAM) space for increased data parameter handling and high level language usage.

RA2, RB2 and RC2 devices have 256 bytes of expanded RAM, from 00H to FFH in external data space; RD2 devices have 768 bytes of expanded RAM, from 00H to 2FFH in external data space.

The TS80C51Rx2 has internal data memory that is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register. (See Table 5.)

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

- Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data ,accesses the SFR at location 0A0H (which is P2).

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

- The 256 or 768 XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first 256 or 768 bytes of external data memory.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 ( $\overline{WR}$ ) and P3.7 ( $\overline{RD}$ ). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than FFH (i.e. 0100H to FFFFH) (higher than 2FFH (i.e. 0300H to FFFFH for RD devices) will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, so with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Refer to Figure . For RD devices, accesses to expanded RAM from 100H to 2FFH can only be done thanks to the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @Ri and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ Ri and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

## 6.5. Programmable Counter Array PCA

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/ capture modules. Its clock input can be programmed to count any one of the following signals:

- Oscillator frequency  $\div$  12 ( $\div$  6 in X2 mode)

- Oscillator frequency  $\div$  4 ( $\div$  2 in X2 mode)

- Timer 0 overflow

- External input on ECI (P1.2)

Each compare/capture modules can be programmed in any one of the following modes:

- rising and/or falling edge capture,

- software timer,

- high-speed output, or

- pulse width modulator.

Module 4 can also be programmed as a watchdog timer (See Section "PCA Watchdog Timer", page 33).

When the compare/capture modules are programmed in the capture mode, software timer, or high speed output mode, an interrupt can be generated when the module executes its function. All five modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If the port is not used for the PCA, it can still be used for standard I/O.

| PCA component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2 / ECI       |

| 16-bit Module 0 | P1.3 / CEX0      |

| 16-bit Module 1 | P1.4 / CEX1      |

| 16-bit Module 2 | P1.5 / CEX2      |

| 16-bit Module 3 | P1.6 / CEX3      |

| 16-bit Module 4 | P1.7 / CEX4      |

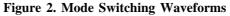

**The PCA timer** is a common time base for all five modules (See Figure 7). The timer count source is determined from the CPS1 and CPS0 bits in the **CMOD SFR** (See Table 8) and can be programmed to run at:

- 1/12 the oscillator frequency. (Or 1/6 in X2 Mode)

- 1/4 the oscillator frequency. (Or 1/2 in X2 Mode)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

Figure 7. PCA Timer/Counter

| Table | 8. | CMOD:   | PCA | Counter | Mode    | Register |

|-------|----|---------|-----|---------|---------|----------|

|       | ~  | 0112021 |     | 0000000 | 1.10000 |          |

|      | CMOD<br>Address 0D9H |                                                        | СІ                                                                                                                                                     | DL                                                       | WDTE        | -                        | -                         | -          | CPS1       | CPS0      | ECF        |

|------|----------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------|--------------------------|---------------------------|------------|------------|-----------|------------|

|      | Rese                 | et value                                               | (                                                                                                                                                      | 0                                                        | 0           | X                        | Х                         | Х          | 0          | 0         | 0          |

| Syı  | mbol                 | Funct                                                  | Function                                                                                                                                               |                                                          |             |                          |                           |            |            |           |            |

| CIDL |                      | 1                                                      | Counter Idle control: $CIDL = 0$ programs the PCA Counter to continue functioning during dle Mode. $CIDL = 1$ programs it to be gated off during idle. |                                                          |             |                          |                           |            |            |           |            |

| WDTH | E                    | 1                                                      | Watchdog Timer Enable: WDTE = 0 disables Watchdog Timer function on PCA Module 4. WDTE = 1 enables it.                                                 |                                                          |             |                          |                           |            |            |           |            |

| -    |                      | Not implemented, reserved for future use. <sup>a</sup> |                                                                                                                                                        |                                                          |             |                          |                           |            |            |           |            |

| CPS1 |                      | PCA Co                                                 | ount Puls                                                                                                                                              | se Sel                                                   | lect bit 1. |                          |                           |            |            |           |            |

| CPS0 |                      | PCA Co                                                 | ount Puls                                                                                                                                              | se Sel                                                   | lect bit 0. |                          |                           |            |            |           |            |

|      |                      | CPS1                                                   | CPS0                                                                                                                                                   | Sele                                                     | cted PCA    | input. <sup>b</sup>      |                           |            |            |           |            |

|      |                      | 0                                                      | 0                                                                                                                                                      | Inter                                                    | nal clock   | $f_{osc}/12$ ( C         | Dr f <sub>osc</sub> /6 in | X2 Mode    | e).        |           |            |

|      |                      | 0                                                      | 1                                                                                                                                                      | Inter                                                    | nal clock   | f <sub>osc</sub> /4 ( Or | f <sub>osc</sub> /2 in    | X2 Mode)   |            |           |            |

|      |                      | 1                                                      | 0                                                                                                                                                      | Timer 0 Overflow                                         |             |                          |                           |            |            |           |            |

|      |                      | 1                                                      | 1                                                                                                                                                      | External clock at ECI/P1.2 pin (max rate = $f_{osc}/8$ ) |             |                          |                           |            |            |           |            |

| ECF  |                      | 1                                                      |                                                                                                                                                        |                                                          |             | interrupt:<br>t function |                           | enables Cl | F bit in C | CON to ge | enerate an |

User software should not write 1s to reserved bits. These bits may be used in future 8051 family a. products to invoke new features. In that case, the reserved on analyzed in rule of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate. b.  $f_{osc} = oscillator frequency$

The CMOD SFR includes three additional bits associated with the PCA (See Figure 7 and Table 8).

- The CIDL bit which allows the PCA to stop during idle mode. •

- The WDTE bit which enables or disables the watchdog function on module 4. •

**The CCON SFR** contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 9).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

- Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

| CCON<br>Address 0D8H |      | CF                  | CR                                                                                                                                                                                                               | -          | CCF4      | CCF3       | CCF2       | CCF1       | CCF0       |           |  |

|----------------------|------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|------------|------------|------------|------------|-----------|--|

|                      | Rese | et value            | 0                                                                                                                                                                                                                | 0          | X         | 0          | 0          | 0          | 0          | 0         |  |

| Sy                   | nbol | Function            | Function                                                                                                                                                                                                         |            |           |            |            |            |            |           |  |

| CF                   |      | an interrup         | PCA Counter Overflow flag. Set by hardware when the counter rolls over. CF flags<br>an interrupt if bit ECF in CMOD is set. CF may be set by either hardware or software but<br>can only be cleared by software. |            |           |            |            |            |            |           |  |

| CR                   |      | 1                   | PCA Counter Run control bit. Set by software to turn the PCA counter on. Must be cleared by software to turn the PCA counter off.                                                                                |            |           |            |            |            |            |           |  |

| -                    |      | Not implen          | Not implemented, reserved for future use. <sup>a</sup>                                                                                                                                                           |            |           |            |            |            |            |           |  |

| CCF4                 |      | 1                   | PCA Module 4 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                        |            |           |            |            |            |            |           |  |

| CCF3                 |      | 1                   | PCA Module 3 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                        |            |           |            |            |            |            |           |  |

| CCF2                 |      |                     | PCA Module 2 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                        |            |           |            |            |            |            |           |  |

| CCF1                 |      | 1                   | PCA Module 1 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                        |            |           |            |            |            |            |           |  |

| CCF0                 |      | PCA Modu cleared by |                                                                                                                                                                                                                  | rupt flag. | Set by ha | ardware wł | nen a matc | h or captu | are occurs | . Must be |  |

Table 9. CCON: PCA Counter Control Register

a. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

The watchdog timer function is implemented in module 4 (See Figure 10).

The PCA interrupt system is shown in Figure 8

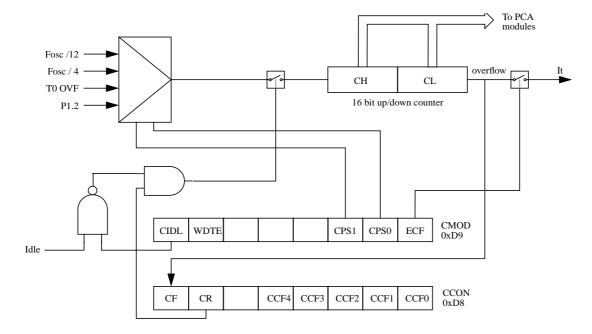

## 6.5.3. High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (See Figure 11).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

Figure 11. PCA High Speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

### 6.6. TS80C51Rx2 Serial I/O Port

The serial I/O port in the TS80C51Rx2 is compatible with the serial I/O port in the 80C52. It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous

Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- Automatic address recognition

### 6.6.1. Framing Error Detection

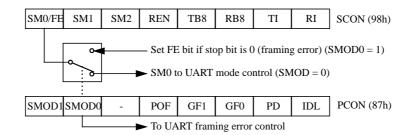

Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 13).

### Figure 13. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 16.) bit is set.

### 6.7. Interrupt System

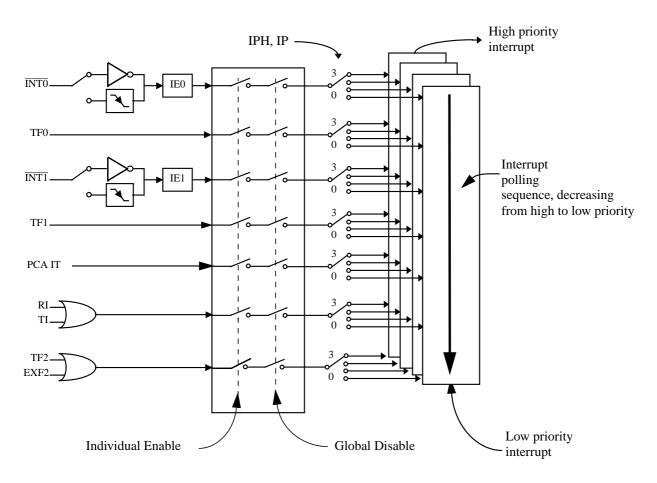

The TS80C51Rx2 has a total of 7 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), three timer interrupts (timers 0, 1 and 2), the serial port interrupt and the PCA global interrupt. These interrupts are shown in Figure 16.

WARNING: Note that in the first version of RC devices, the PCA interrupt is in the lowest priority. Thus the order in INTO, TF0, INT1, TF1, RI or TI, TF2 or EXF2, PCA.

#### Figure 16. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 19.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 20.) and in the Interrupt Priority High register (See Table 21.). shows the bit values and priority levels associated with each combination.

The PCA interrupt vector is located at address 0033H. All other vector addresses are the same as standard C52 devices.

### 6.10. Hardware Watchdog Timer

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upset. The WDT consists of a 14-bit counter and the WatchDog Timer ReSeT (WDTRST) SFR. The WDT is by default disabled from exiting reset. To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST-pin.

### 6.10.1. Using the WDT

To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, the user needs to service it by writing to 01EH and 0E1H to WDTRST to avoid WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH) and this will reset the device. When WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must reset the WDT at least every 16383 machine cycle. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST-pin. The RESET pulse duration is 96 x  $T_{OSC}$ , where  $T_{OSC} = 1/F_{OSC}$ . To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

To have a more powerful WDT, a  $2^7$  counter has been added to extend the Time-out capability, ranking from 16ms to 2s @  $F_{OSC} = 12$ MHz. To manage this feature, refer to WDTPRG register description, Table 24. (SFR0A7h).

#### Table 23. WDTRST Register

#### WDTRST Address (0A6h)

|             | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|-------------|---|---|---|---|---|---|---|

| Reset value | Х | Х | Х | Х | Х | Х | Х |

Write only, this SFR is used to reset/enable the WDT by writing 01EH then 0E1H in sequence.

#### Table 24. WDTPRG Register

| 7          | 6               | 5 4 3 2 1                                              |                                              |                                                       |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

|------------|-----------------|--------------------------------------------------------|----------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------|-----------|--|--|--|--|--|

| T4         | T3              |                                                        | T2                                           | T1                                                    | TO                                                                                                                                                                                                 | <u>82</u>                                                                                                  | <u>81</u> | <b>S0</b> |  |  |  |  |  |

| Bit Number | Bit<br>Mnemonic |                                                        | Description                                  |                                                       |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

| 7          | T4              |                                                        |                                              |                                                       |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

| 6          | Т3              |                                                        |                                              |                                                       |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

| 5          | T2              | Reserve<br>Do 1                                        |                                              | or clear this bit.                                    |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

| 4          | T1              |                                                        |                                              |                                                       |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

| 3          | TO              |                                                        |                                              |                                                       |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

| 2          | S2              | WDT Ti                                                 | ime-out sele                                 | ct bit 2                                              |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

| 1          | S1              | WDT Ti                                                 | ime-out sele                                 | ct bit 1                                              |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

| 0          | SO              | WDT Ti                                                 | ime-out sele                                 | ct bit 0                                              |                                                                                                                                                                                                    |                                                                                                            |           |           |  |  |  |  |  |

|            |                 | $\frac{S2}{0}$<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1 | <u>S1</u><br>0<br>1<br>1<br>0<br>0<br>1<br>1 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | d Time-out<br>) machine cycles, 1<br>) machine cycles, 3<br>) machine cycles, 6<br>) machine cycles, 1<br>) machine cycles, 2<br>) machine cycles, 5<br>) machine cycles, 1<br>) machine cycles, 2 | 2.7 ms @ 12 MHz<br>5.5 ms @ 12 MHz<br>31 ms @ 12 MHz<br>62 ms @ 12 MHz<br>42 ms @ 12 MHz<br>.05 s @ 12 MHz |           |           |  |  |  |  |  |

Reset value XXXX X000

### 6.10.2. WDT during Power Down and Idle

In Power Down mode the oscillator stops, which means the WDT also stops. While in Power Down mode the user does not need to service the WDT. There are 2 methods of exiting Power Down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power Down mode. When Power Down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the TS80C51Rx2 is reset. Exiting Power Down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is best to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the TS80C51Rx2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

### WDTPRG Address (0A7h)

### 6.13. Reduced EMI Mode

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

#### Table 27. AUXR Register

#### AUXR - Auxiliary Register (8Eh)

| 7          | 6               | 5                                                                                                                                  | 4                                                                               | 3 | 2 | 1      | 0  |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---|---|--------|----|

| -          | -               | -                                                                                                                                  | -                                                                               | - | - | EXTRAM | AO |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                        |                                                                                 |   |   |        |    |

| 7          | -               | Reserved<br>The value read                                                                                                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |   |   |        |    |

| 6          | -               | Reserved<br>The value read                                                                                                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |   |   |        |    |

| 5          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                    |                                                                                 |   |   |        |    |

| 4          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                    |                                                                                 |   |   |        |    |

| 3          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                    |                                                                                 |   |   |        |    |

| 2          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                    |                                                                                 |   |   |        |    |

| 1          | EXTRAM          | EXTRAM bit<br>See Table 5.                                                                                                         |                                                                                 |   |   |        |    |

| 0          | AO              | ALE Output bit<br>Clear to restore ALE operation during internal fetches.<br>Set to disable ALE operation during internal fetches. |                                                                                 |   |   |        |    |

Reset Value = XXXX XX00b Not bit addressable

## 9. Signature Bytes

The TS83/87C51RB2/RC2/RD2 has four signature bytes in location 30h, 31h, 60h and 61h. To read these bytes follow the procedure for EPROM verify but activate the control lines provided in Table 31. for Read Signature Bytes. Table 31. shows the content of the signature byte for the TS87C51RB2/RC2/RD2.

| Location | Contents                     | Comment                                              |

|----------|------------------------------|------------------------------------------------------|

| 30h      | 58h                          | Manufacturer Code: Atmel Wireless & Microcontrollers |

| 31h      | 57h                          | Family Code: C51 X2                                  |

| 60h      | 7Ch                          | Product name: TS83C51RD2                             |

| 60h      | FCh                          | Product name: TS87C51RD2                             |

| 60h      | 37h                          | Product name: TS83C51RC2                             |

| 60h      | B7h                          | Product name: TS87C51RC2                             |

| 60h      | 3Bh Product name: TS83C51RB2 |                                                      |

| 60h      | BBh Product name: TS87C51RB2 |                                                      |

| 61h      | FFh                          | Product revision number                              |

#### Table 31. Signature Bytes Content

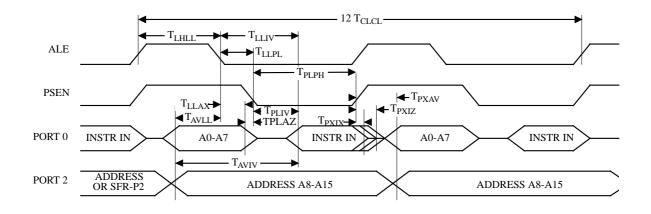

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -M | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10 | 8  | 15 | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30 | 22 | 35 | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20 | 15 | 25 | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40 | 25 | 45 | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7  | 5  | 15 | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40 | 30 | 45 | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10 | 10 | 10 | ns    |

Table 38. AC Parameters for a Variable Clock: derating formula

## 10.5.3. External Program Memory Read Cycle

Figure 25. External Program Memory Read Cycle

### **10.5.4. External Data Memory Characteristics**

| Parameter                                     |

|-----------------------------------------------|

| RD Pulse Width                                |

| WR Pulse Width                                |

| RD to Valid Data In                           |

| Data Hold After RD                            |

| Data Float After RD                           |

| ALE to Valid Data In                          |

| Address to Valid Data In                      |

| ALE to $\overline{WR}$ or $\overline{RD}$     |

| Address to $\overline{WR}$ or $\overline{RD}$ |

| Data Valid to $\overline{WR}$ Transition      |

| Data set-up to WR High                        |

| Data Hold After $\overline{WR}$               |

| RD Low to Address Float                       |

| RD or WR High to ALE high                     |

|                                               |

### Table 39. Symbol Description

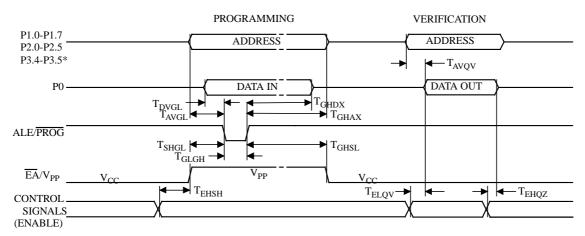

### **10.5.9. EPROM Programming and Verification Characteristics**

TA = 21°C to 27°C;  $V_{SS} = 0V$ ;  $V_{CC} = 5V \pm 10\%$  while programming.  $V_{CC} =$  operating range while verifying

| Symbol              | Parameter                         | Min                  | Max                  | Units |

|---------------------|-----------------------------------|----------------------|----------------------|-------|

| V <sub>PP</sub>     | Programming Supply Voltage        | 12.5                 | 13                   | v     |

| I <sub>PP</sub>     | Programming Supply Current        |                      | 75                   | mA    |

| 1/T <sub>CLCL</sub> | Oscillator Frquency               | 4                    | 6                    | MHz   |

| T <sub>AVGL</sub>   | Address Setup to PROG Low         | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHAX</sub>   | Adress Hold after PROG            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>DVGL</sub>   | Data Setup to PROG Low            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHDX</sub>   | Data Hold after PROG              | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>EHSH</sub>   | (Enable) High to V <sub>PP</sub>  | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low | 10                   |                      | μs    |

| T <sub>GHSL</sub>   | V <sub>PP</sub> Hold after PROG   | 10                   |                      | μs    |

| T <sub>GLGH</sub>   | PROG Width                        | 90                   | 110                  | μs    |

| T <sub>AVQV</sub>   | Address to Valid Data             |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>ELQV</sub>   | ENABLE Low to Data Valid          |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>EHQZ</sub>   | Data Float after ENABLE           | 0                    | 48 T <sub>CLCL</sub> |       |

#### Table 45. EPROM Programming Parameters

### **10.5.10. EPROM Programming and Verification Waveforms**

\* 8KB: up to P2.4, 16KB: up to P2.5, 32KB: up to P3.4, 64KB: up to P3.5

#### Figure 29. EPROM Programming and Verification Waveforms

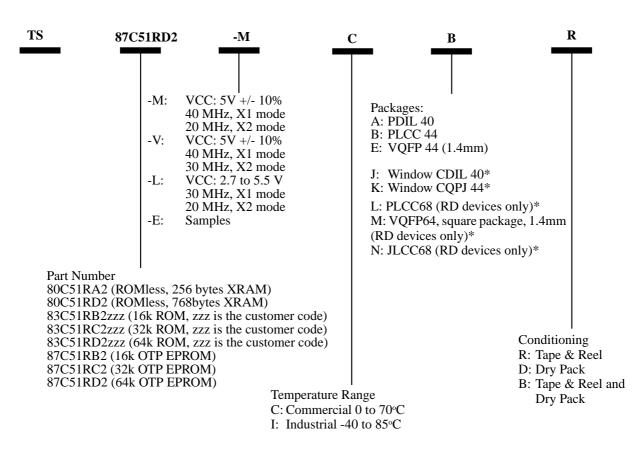

# 11. Ordering Information

(\*) Check with Atmel Wireless & Microcontrollers Sales Office for availability. Ceramic packages (J, K, N) are available for proto typing, not for volume production. Ceramic packages are available for OTP only.

| Code                                   | -M | -V        | -L        | Unit |

|----------------------------------------|----|-----------|-----------|------|

| Standard Mode, oscillator frequency    | 40 | 40        | 30        | MHz  |

| Standard Mode, internal frequency      | 40 | 40        | 30        |      |

| X2 Mode, oscillator frequency          | 20 | 30        | 20        | MHz  |

| X2 Mode, internal equivalent frequency | 40 | <b>60</b> | <b>40</b> |      |

|      | TS80C51RA2/RD2 ROMless | TS83C51RB2/RC2/RD2zzz<br>ROM | TS87C51RB2/RC2/RD2 OTP |

|------|------------------------|------------------------------|------------------------|

| -MCA | X                      | Х                            | X                      |

| -MCB | X                      | Х                            | X                      |

| -MCE | X                      | Х                            | X                      |

| -MCL | RD2 only               | RD2 only                     | RD2 only               |

| -MCM | RD2 only               | RD2 only                     | RD2 only               |

| -VCA | Х                      | Х                            | Х                      |

| -VCB | X                      | Х                            | X                      |

| -VCE | Х                      | X                            | X                      |

| -VCL | RD2 only               | RD2 only                     | RD2 only               |

| -VCM | RD2 only               | RD2 only                     | RD2 only               |

| -LCA | Х                      | Х                            | X                      |

| -LCB | X                      | Х                            | X                      |

| -LCE | X                      | X                            | X                      |

| -LCL | RD2 only               | RD2 only                     | RD2 only               |

| -LCM | RD2 only               | RD2 only                     | RD2 only               |

| -MIA | Х                      | Х                            | X                      |

| -MIB | X                      | Х                            | X                      |

| -MIE | Х                      | X                            | X                      |

| -MIL | RD2 only               | RD2 only                     | RD2 only               |

| -MIM | RD2 only               | RD2 only                     | RD2 only               |

| -VIA | Х                      | Х                            | X                      |

| -VIB | X                      | Х                            | X                      |

| -VIE | X                      | X                            | X                      |

| -VIL | RD2 only               | RD2 only                     | RD2 only               |

| -VIM | RD2 only               | RD2 only                     | RD2 only               |

| -LIA | Х                      | Х                            | X                      |

| -LIB | X                      | Х                            | X                      |

| -LIE | X                      | Х                            | X                      |

| -LIL | RD2 only               | RD2 only                     | RD2 only               |

| -LIM | RD2 only               | RD2 only                     | RD2 only               |

| -EA  | Х                      |                              | Х                      |

| -EB  | X                      |                              | X                      |

| -EE  | X                      |                              | X                      |

| -EL  | RD2 only               |                              | RD2 only               |

| -EM  | RD2 only               |                              | RD2 only               |

| -EJ  |                        |                              | RC2 and RD2 only       |

| -EK  |                        |                              | RC2 and RD2 only       |

| -EN  |                        |                              | RD2 only               |

### Table 48. Possible Ordering Entries

• -Ex for samples

- Tape and Reel available for B, E, L and M packages

- Dry pack mandatory for E and M packages