Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 30/20MHz                                                                 |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-QFP                                                                   |

| Supplier Device Package    | 44-VQFP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c51rc2-lce |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4. SFR Mapping

The Special Function Registers (SFRs) of the TS80C51Rx2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3, P4, P5

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- HDW Watchdog Timer Reset: WDTRST, WDTPRG

- PCA registers: CL, CH, CCAPiL, CCAPiH, CCON, CMOD, CCAPMi

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

### Table 1. All SFRs with their address and their reset value

|     | Bit<br>addressable                 | Non Bit addressable |                     |                     |                      |                      |                      |                                     |     |

|-----|------------------------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|-------------------------------------|-----|

|     | 0/8                                | 1/9                 | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |

| F8h |                                    | CH<br>0000 0000     | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAPL2H<br>XXXX XXXX | CCAPL3H<br>XXXX XXXX | CCAPL4H<br>XXXX XXXX |                                     | FFh |

| F0h | B<br>0000 0000                     |                     |                     |                     |                      |                      |                      |                                     | F7h |

| E8h | P5 bit<br>addressable<br>1111 1111 | CL<br>0000 0000     | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                                     | EFh |

| E0h | ACC<br>0000 0000                   |                     |                     |                     |                      |                      |                      |                                     | E7h |

| D8h | CCON<br>00X0 0000                  | CMOD<br>00XX X000   | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                                     | DFh |

| D0h | PSW<br>0000 0000                   |                     |                     |                     |                      |                      |                      |                                     | D7h |

| C8h | T2CON<br>0000 0000                 | T2MOD<br>XXXX XX00  | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                                     | CFh |

| C0h | P4 bit<br>addressable<br>1111 1111 |                     |                     |                     |                      |                      |                      | P5 byte<br>addressable<br>1111 1111 | C7h |

| B8h | IP<br>X000 000                     | SADEN<br>0000 0000  |                     |                     |                      |                      |                      |                                     | BFh |

| B0h | P3<br>1111 1111                    |                     |                     |                     |                      |                      |                      | IPH<br>X000 0000                    | B7h |

| A8h | IE<br>0000 0000                    | SADDR<br>0000 0000  |                     |                     |                      |                      |                      |                                     | AFh |

| A0h | P2<br>1111 1111                    |                     | AUXR1<br>XXXX0XX0   |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000                 | A7h |

| 98h | SCON<br>0000 0000                  | SBUF<br>XXXX XXXX   |                     |                     |                      |                      |                      |                                     | 9Fh |

| 90h | P1<br>1111 1111                    |                     |                     |                     |                      |                      |                      |                                     | 97h |

| 88h | TCON<br>0000 0000                  | TMOD<br>0000 0000   | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XXXXXX00     | CKCON<br>XXXX XXX0                  | 8Fh |

| 80h | P0<br>1111 1111                    | SP<br>0000 0111     | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000                   | 87h |

|     | 0/8                                | 1/9                 | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |

|     | macaminad                          |                     |                     |                     |                      |                      |                      |                                     |     |

reserved

### Table 3. CKCON Register

### CKCON - Clock Control Register (8Fh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|---|---|---|---|---|---|---|----|

| - | - | - | - | - | - | - | X2 |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                     |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 6          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 5          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 4          | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 3          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 2          | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 1          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 0          | X2              | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |

Reset Value = XXXX XXX0b Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel-wm.com)

## ASSEMBLY LANGUAGE

; Block move using dual data pointers ; Destroys DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added

| 00A2                                         | AUXR1 EQU 0A2H                                  |                                                                                                              |

|----------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| ;<br>0000 909000<br>0003 05A2<br>0005 90A000 | MOV DPTR,#SOURCE<br>INC AUXR1<br>MOV DPTR,#DEST | ; address of SOURCE<br>; switch data pointers<br>; address of DEST                                           |

| 0008<br>0008 05A2<br>000A E0                 | LOOP:<br>INC AUXR1<br>MOVX A,@DPTR              | ; switch data pointers<br>; get a byte from SOURCE                                                           |

| 000B A3<br>000C 05A2<br>000E F0              | INC DPTR<br>INC AUXR1<br>MOVX @DPTR.A           | ; increment SOURCE address<br>; switch data pointers<br>; write the byte to DEST                             |

| 000E F0<br>000F A3<br>0010 70F6<br>0012 05A2 | INC DPTR<br>JNZ LOOP<br>INC AUXR1               | ; write the byte to DEST<br>; increment DEST address<br>; check for 0 terminator<br>; (optional) restore DPS |

|                                              |                                                 |                                                                                                              |

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

# 6.3. Expanded RAM (XRAM)

The TS80C51Rx2 provide additional Bytes of ramdom access memory (RAM) space for increased data parameter handling and high level language usage.

RA2, RB2 and RC2 devices have 256 bytes of expanded RAM, from 00H to FFH in external data space; RD2 devices have 768 bytes of expanded RAM, from 00H to 2FFH in external data space.

The TS80C51Rx2 has internal data memory that is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register. (See Table 5.)

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

- Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data ,accesses the SFR at location 0A0H (which is P2).

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

- The 256 or 768 XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first 256 or 768 bytes of external data memory.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 ( $\overline{WR}$ ) and P3.7 ( $\overline{RD}$ ). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than FFH (i.e. 0100H to FFFFH) (higher than 2FFH (i.e. 0300H to FFFFH for RD devices) will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, so with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Refer to Figure . For RD devices, accesses to expanded RAM from 100H to 2FFH can only be done thanks to the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @Ri and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ Ri and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

# 6.5. Programmable Counter Array PCA

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/ capture modules. Its clock input can be programmed to count any one of the following signals:

- Oscillator frequency  $\div$  12 ( $\div$  6 in X2 mode)

- Oscillator frequency  $\div$  4 ( $\div$  2 in X2 mode)

- Timer 0 overflow

- External input on ECI (P1.2)

Each compare/capture modules can be programmed in any one of the following modes:

- rising and/or falling edge capture,

- software timer,

- high-speed output, or

- pulse width modulator.

Module 4 can also be programmed as a watchdog timer (See Section "PCA Watchdog Timer", page 33).

When the compare/capture modules are programmed in the capture mode, software timer, or high speed output mode, an interrupt can be generated when the module executes its function. All five modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If the port is not used for the PCA, it can still be used for standard I/O.

| PCA component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2 / ECI       |

| 16-bit Module 0 | P1.3 / CEX0      |

| 16-bit Module 1 | P1.4 / CEX1      |

| 16-bit Module 2 | P1.5 / CEX2      |

| 16-bit Module 3 | P1.6 / CEX3      |

| 16-bit Module 4 | P1.7 / CEX4      |

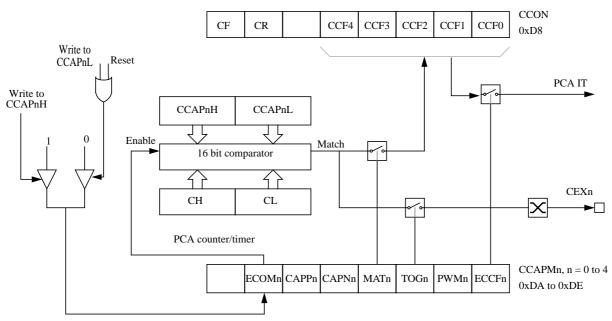

**The PCA timer** is a common time base for all five modules (See Figure 7). The timer count source is determined from the CPS1 and CPS0 bits in the **CMOD SFR** (See Table 8) and can be programmed to run at:

- 1/12 the oscillator frequency. (Or 1/6 in X2 Mode)

- 1/4 the oscillator frequency. (Or 1/2 in X2 Mode)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

**The CCON SFR** contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 9).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

- Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

| CCON<br>Address 0D8H |      | CF                                                                                                     | CR                                                                                                                                                                                                              | -          | CCF4       | CCF3            | CCF2        | CCF1       | CCF0       |            |

|----------------------|------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------------|-------------|------------|------------|------------|

|                      | Rese | et value                                                                                               | 0                                                                                                                                                                                                               | 0          | X          | 0               | 0           | 0          | 0          | 0          |

| Sy                   | nbol | Function                                                                                               | ı                                                                                                                                                                                                               |            |            |                 |             |            |            |            |

| CF                   |      | an interrup                                                                                            | PCA Counter Overflow flag. Set by hardware when the counter rolls over. CF flags<br>in interrupt if bit ECF in CMOD is set. CF may be set by either hardware or software but<br>an only be cleared by software. |            |            |                 |             |            |            |            |

| CR                   |      | PCA Coun<br>by software                                                                                |                                                                                                                                                                                                                 |            | •          |                 | Irn the PCA | A counter  | on. Must   | be cleared |

| -                    |      | Not implen                                                                                             | nented, res                                                                                                                                                                                                     | erved for  | future use | e. <sup>a</sup> |             |            |            |            |

| CCF4                 |      | PCA Modu cleared by                                                                                    |                                                                                                                                                                                                                 | rupt flag. | Set by ha  | ardware wh      | nen a matc  | h or captu | are occurs | . Must be  |

| CCF3                 |      | PCA Modu cleared by                                                                                    |                                                                                                                                                                                                                 | rupt flag. | Set by ha  | ardware wł      | nen a matc  | h or captu | are occurs | . Must be  |

| CCF2                 |      | PCA Module 2 interrupt flag. Set by hardware when a match or capture occurs. Must cleared by software. |                                                                                                                                                                                                                 |            |            |                 |             |            | . Must be  |            |

| CCF1                 |      | PCA Modu cleared by                                                                                    |                                                                                                                                                                                                                 | rupt flag. | Set by ha  | ardware wł      | nen a matc  | h or captu | are occurs | . Must be  |

| CCF0                 |      | PCA Modu cleared by                                                                                    |                                                                                                                                                                                                                 | rupt flag. | Set by ha  | ardware wł      | nen a matc  | h or captu | are occurs | . Must be  |

Table 9. CCON: PCA Counter Control Register

a. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

The watchdog timer function is implemented in module 4 (See Figure 10).

The PCA interrupt system is shown in Figure 8

# 6.5.3. High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (See Figure 11).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

Figure 11. PCA High Speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

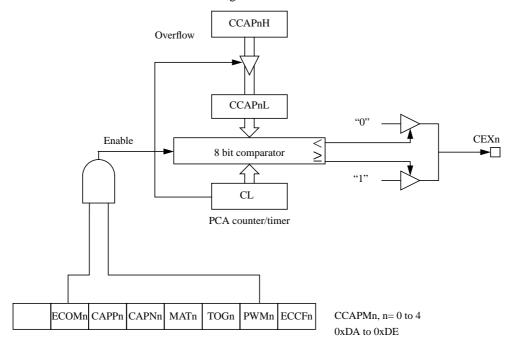

## 6.5.4. Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 12 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

Figure 12. PCA PWM Mode

# 6.5.5. PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 10 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. periodically change the compare value so it will never match the PCA timer,

- 2. periodically change the PCA timer value so it will never match the compare values, or

- 3. disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

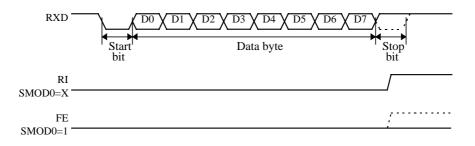

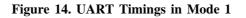

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 14. and Figure 15.).

Figure 15. UART Timings in Modes 2 and 3

### 6.6.2. Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, you may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit.

To support automatic address recognition, a device is identified by a given address and a broadcast address.

NOTE: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

### Table 20. IP Register

### **IP - Interrupt Priority Register (B8h)**

| 7 | 6   | 5   | 4  | 3   | 2   | 1   | 0   |

|---|-----|-----|----|-----|-----|-----|-----|

| - | PPC | PT2 | PS | PT1 | PX1 | PT0 | PX0 |

| Bit Number | Bit<br>Mnemonic |                                                                              | Description                                                                         |                  |               |  |  |  |  |  |

|------------|-----------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|---------------|--|--|--|--|--|

| 7          | -               | Reserved<br>The value read from                                              | this bit is indet                                                                   | erminate. Do not | set this bit. |  |  |  |  |  |

| 6          | PPC             | PCA interrupt priority<br>Refer to PPCH for pr                               |                                                                                     |                  |               |  |  |  |  |  |

| 5          | PT2             |                                                                              | mer 2 overflow interrupt Priority bit<br>Refer to PT2H for priority level.          |                  |               |  |  |  |  |  |

| 4          | PS              | Serial port Priority bit<br>Refer to PSH for prio                            | ferial port Priority bit<br>Refer to PSH for priority level.                        |                  |               |  |  |  |  |  |

| 3          | PT1             |                                                                              | Fimer 1 overflow interrupt Priority bit           Refer to PT1H for priority level. |                  |               |  |  |  |  |  |

| 2          | PX1             | External interrupt 1 Pri<br>Refer to PX1H for pr                             |                                                                                     |                  |               |  |  |  |  |  |

| 1          | PT0             | Fimer 0 overflow interrupt Priority bit<br>Refer to PT0H for priority level. |                                                                                     |                  |               |  |  |  |  |  |

| 0          | PX0             | External interrupt 0 Pri<br>Refer to PX0H for pr                             |                                                                                     |                  |               |  |  |  |  |  |

Reset Value = X000 0000b Bit addressable

| Table 22. | The state of | ports during | idle and | power-down mode |

|-----------|--------------|--------------|----------|-----------------|

|-----------|--------------|--------------|----------|-----------------|

| Mode       | Program<br>Memory | ALE | PSEN | PORT0      | PORT1     | PORT2     | PORT3     |

|------------|-------------------|-----|------|------------|-----------|-----------|-----------|

| Idle       | Internal          | 1   | 1    | Port Data* | Port Data | Port Data | Port Data |

| Idle       | External          | 1   | 1    | Floating   | Port Data | Address   | Port Data |

| Power Down | Internal          | 0   | 0    | Port Data* | Port Data | Port Data | Port Data |

| Power Down | External          | 0   | 0    | Floating   | Port Data | Port Data | Port Data |

\* Port 0 can force a "zero" level. A "one" will leave port floating.

## 6.10. Hardware Watchdog Timer

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upset. The WDT consists of a 14-bit counter and the WatchDog Timer ReSeT (WDTRST) SFR. The WDT is by default disabled from exiting reset. To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST-pin.

## 6.10.1. Using the WDT

To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, the user needs to service it by writing to 01EH and 0E1H to WDTRST to avoid WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH) and this will reset the device. When WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must reset the WDT at least every 16383 machine cycle. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST-pin. The RESET pulse duration is 96 x  $T_{OSC}$ , where  $T_{OSC} = 1/F_{OSC}$ . To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

To have a more powerful WDT, a  $2^7$  counter has been added to extend the Time-out capability, ranking from 16ms to 2s @  $F_{OSC} = 12$ MHz. To manage this feature, refer to WDTPRG register description, Table 24. (SFR0A7h).

### Table 23. WDTRST Register

### WDTRST Address (0A6h)

|             | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|-------------|---|---|---|---|---|---|---|

| Reset value | Х | Х | Х | Х | Х | Х | Х |

Write only, this SFR is used to reset/enable the WDT by writing 01EH then 0E1H in sequence.

# 6.11. ONCE<sup>TM</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS80C51Rx2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C51Rx2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and  $\overline{\text{PSEN}}$  is high.

- Hold ALE low as RST is deactivated.

While the TS80C51Rx2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

### Table 25. External Pin Status during ONCE Mode

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

# 7. TS83C51RB2/RC2/RD2 ROM

# 7.1. ROM Structure

The TS83C51RB2/RC2/RD2 ROM memory is divided in three different arrays:

| • | the code array:       | . 16/32/64 Kbytes. |

|---|-----------------------|--------------------|

| • | the encryption array: | 64 bytes.          |

| ٠ | the signature array:  | 4 bytes.           |

# 7.2. ROM Lock System

The program Lock system, when programmed, protects the on-chip program against software piracy.

## 7.2.1. 7.2.1. Encryption Array

Within the ROM array are 64 bytes of encryption array that are initially unprogrammed (all FF's). Every time a byte is addressed during program verify, 6 address lines are used to select a byte of the encryption array. This byte is then exclusive-NOR'ed (XNOR) with the code byte, creating an encrypted verify byte. The algorithm, with the encryption array in the unprogrammed state, will return the code in its original, unmodified form.

When using the encryption array, one important factor needs to be considered. If a byte has the value FFh, verifying the byte will produce the encryption byte value. If a large block (>64 bytes) of code is left unprogrammed, a verification routine will display the content of the encryption array. For this reason all the unused code bytes should be programmed with random values. This will ensure program protection.

## 7.2.2. Program Lock Bits

The lock bits when programmed according to Table 28. will provide different level of protection for the on-chip code and data.

|                   | Program | Lock Bits |     |                                                                                                                                                                                                 |  |

|-------------------|---------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Security<br>level | LB1     | LB2       | LB3 | Protection description                                                                                                                                                                          |  |

| 1                 | U       | U         | U   | No program lock features enabled. Code verify will still be encrypted by the encryption array if programmed. MOVC instruction executed from external program memory returns non encrypted data. |  |

| 2                 | Р       | U         | U   | MOVC instruction executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on reset.                             |  |

| 3                 | U       | Р         | U   | Same as level 1+ Verify disable.<br>This security level is only available for 51RDX2 devices.                                                                                                   |  |

| Table | 28. | Program | Lock | bits |

|-------|-----|---------|------|------|

| Lanc  | 40. | Trogram | LUCK | DILS |

U: unprogrammed

P: programmed

## 7.2.3. Signature bytes

The TS83C51RB2/RC2/RD2 contains 4 factory programmed signatures bytes. To read these bytes, perform the process described in section 8.3.

### 7.2.4. Verify Algorithm

Refer to 8.3.4.

# 8. TS87C51RB2/RC2/RD2 EPROM

## 8.1. EPROM Structure

The TS87C51RB2/RC2/RD2 EPROM is divided in two different arrays:

| •  | the code array:                                         |

|----|---------------------------------------------------------|

| •  | the encryption array:                                   |

| In | addition a third non programmable array is implemented: |

| •  | the signature array:                                    |

# 8.2. EPROM Lock System

The program Lock system, when programmed, protects the on-chip program against software piracy.

## 8.2.1. Encryption Array

Within the EPROM array are 64 bytes of encryption array that are initially unprogrammed (all FF's). Every time a byte is addressed during program verify, 6 address lines are used to select a byte of the encryption array. This byte is then exclusive-NOR'ed (XNOR) with the code byte, creating an encrypted verify byte. The algorithm, with the encryption array in the unprogrammed state, will return the code in its original, unmodified form.

When using the encryption array, one important factor needs to be considered. If a byte has the value FFh, verifying the byte will produce the encryption byte value. If a large block (>64 bytes) of code is left unprogrammed, a verification routine will display the content of the encryption array. For this reason all the unused code bytes should be programmed with random values. This will ensure program protection.

### 8.2.2. Program Lock Bits

The three lock bits, when programmed according to Table 29.8.2.3., will provide different level of protection for the on-chip code and data.

| P              | Program Lock Bits |     |     | Protection description                                                                                                                                                                                                |  |  |

|----------------|-------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Security level | LB1               | LB2 | LB3 | Troccion description                                                                                                                                                                                                  |  |  |

| 1              | U                 | U   | U   | No program lock features enabled. Code verify will still be encrypted by the encryption array if programmed. MOVC instruction executed from external program memory returns non encrypted data.                       |  |  |

| 2              | Р                 | U   | U   | MOVC instruction executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on reset, and further programming of the EPROM is disabled. |  |  |

| 3              | U                 | Р   | U   | Same as 2, also verify is disabled.                                                                                                                                                                                   |  |  |

| 4              | U                 | U   | Р   | Same as 3, also external execution is disabled.                                                                                                                                                                       |  |  |

| Table 29. | Program | Lock | bits |

|-----------|---------|------|------|

|-----------|---------|------|------|

U: unprogrammed,

P: programmed

WARNING: Security level 2 and 3 should only be programmed after EPROM and Core verification.

## 8.2.3. Signature bytes

The TS87C51RB2/RC2/RD2 contains 4 factory programmed signatures bytes. To read these bytes, perform the process described in section 8.3.

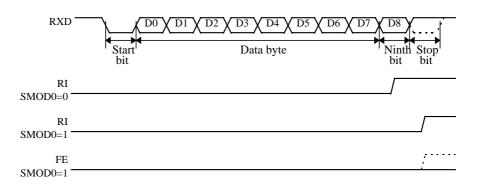

Figure 19. Programming and Verification Signal's Waveform

## 8.4. EPROM Erasure (Windowed Packages Only)

Erasing the EPROM erases the code array, the encryption array and the lock bits returning the parts to full functionality.

Erasure leaves all the EPROM cells in a 1's state (FF).

## 8.4.1. Erasure Characteristics

The recommended erasure procedure is exposure to ultraviolet light (at 2537 Å) to an integrated dose at least 15 W-sec/cm<sup>2</sup>. Exposing the EPROM to an ultraviolet lamp of 12,000  $\mu$ W/cm<sup>2</sup> rating for 30 minutes, at a distance of about 25 mm, should be sufficient. An exposure of 1 hour is recommended with most of standard erasers.

Erasure of the EPROM begins to occur when the chip is exposed to light with wavelength shorter than approximately 4,000 Å. Since sunlight and fluorescent lighting have wavelengths in this range, exposure to these light sources over an extended time (about 1 week in sunlight, or 3 years in room-level fluorescent lighting) could cause inadvertent erasure. If an application subjects the device to this type of exposure, it is suggested that an opaque label be placed over the window.

## **10.5. AC Parameters**

### 10.5.1. Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

Example:  $T_{AVLL}$  = Time for Address Valid to ALE Low.  $T_{LLPL}$  = Time for ALE Low to PSEN Low.

TA = 0 to +70°C (commercial temperature range);  $V_{SS} = 0$  V;  $V_{CC} = 5$  V ± 10%; -M and -V ranges. TA = -40°C to +85°C (industrial temperature range);  $V_{SS} = 0$  V;  $V_{CC} = 5$  V ± 10%; -M and -V ranges. TA = 0 to +70°C (commercial temperature range);  $V_{SS} = 0$  V; 2.7 V <  $V_{CC} < 5.5$  V; -L range. TA = -40°C to +85°C (industrial temperature range);  $V_{SS} = 0$  V; 2.7 V <  $V_{CC} < 5.5$  V; -L range.

Table 34. gives the maximum applicable load capacitance for Port 0, Port 1, 2 and 3, and ALE and  $\overline{\text{PSEN}}$  signals. Timings will be guaranteed if these capacitances are respected. Higher capacitance values can be used, but timings will then be degraded.

|              | -M  | -V | -L  |

|--------------|-----|----|-----|

| Port 0       | 100 | 50 | 100 |

| Port 1, 2, 3 | 80  | 50 | 80  |

| ALE / PSEN   | 100 | 30 | 100 |

| Table 34 | . Load | Capacitance | versus | speed | range. | in | рF |

|----------|--------|-------------|--------|-------|--------|----|----|

|          |        | Capacitanee |        | peed  |        |    | r- |

Table 36., Table 39. and Table 42. give the description of each AC symbols.

Table 37., Table 40. and Table 43. give for each range the AC parameter.

Table 38., Table 41. and Table 44. give the frequency derating formula of the AC parameter. To calculate each AC symbols, take the x value corresponding to the speed grade you need (-M, -V or -L) and replace this value in the formula. Values of the frequency must be limited to the corresponding speed grade:

Table 35. Max frequency for derating formula regarding the speed grade

|            | -M X1 mode | -M X2 mode | -V X1 mode | -V X2 mode | -L X1 mode | -L X2 mode |

|------------|------------|------------|------------|------------|------------|------------|

| Freq (MHz) | 40         | 20         | 40         | 30         | 30         | 20         |

| T (ns)     | 25         | 50         | 25         | 33.3       | 33.3       | 50         |

Example:

$T_{LLIV}$  in X2 mode for a -V part at 20 MHz (T =  $1/20^{E6}$  = 50 ns):

x= 22 (Table 38.)

T=50ns

$T_{LLIV}$ = 2T - x = 2 x 50 - 22 = 78ns

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

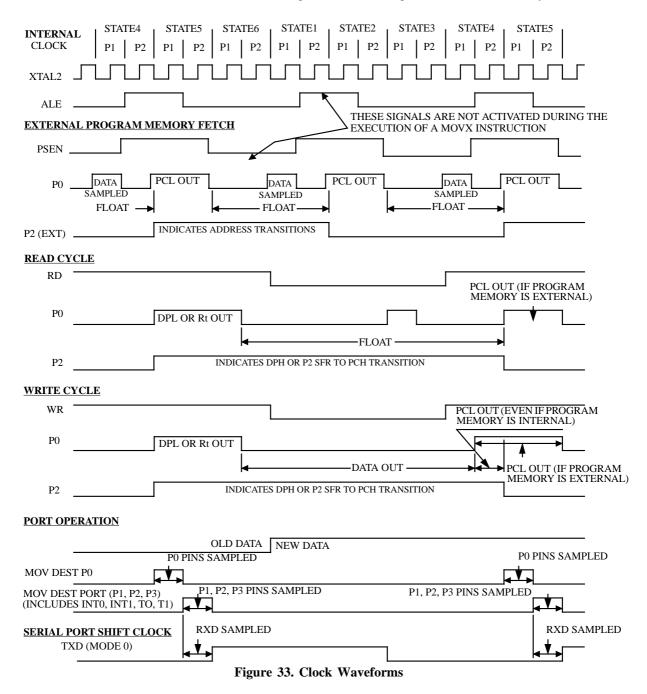

### 10.5.15. Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 signal must be changed to XTAL2 divided by two.

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

|      | TS80C51RA2/RD2 ROMless | TS83C51RB2/RC2/RD2zzz<br>ROM | TS87C51RB2/RC2/RD2 OTP |

|------|------------------------|------------------------------|------------------------|

| -MCA | X                      | Х                            | X                      |

| -MCB | X                      | Х                            | X                      |

| -MCE | X                      | Х                            | X                      |

| -MCL | RD2 only               | RD2 only                     | RD2 only               |

| -MCM | RD2 only               | RD2 only                     | RD2 only               |

| -VCA | Х                      | Х                            | Х                      |

| -VCB | X                      | Х                            | X                      |

| -VCE | Х                      | X                            | X                      |

| -VCL | RD2 only               | RD2 only                     | RD2 only               |

| -VCM | RD2 only               | RD2 only                     | RD2 only               |

| -LCA | Х                      | Х                            | X                      |

| -LCB | X                      | Х                            | X                      |

| -LCE | Х                      | Х                            | X                      |

| -LCL | RD2 only               | RD2 only                     | RD2 only               |

| -LCM | RD2 only               | RD2 only                     | RD2 only               |

| -MIA | Х                      | Х                            | Х                      |

| -MIB | X                      | Х                            | X                      |

| -MIE | Х                      | X                            | X                      |

| -MIL | RD2 only               | RD2 only                     | RD2 only               |

| -MIM | RD2 only               | RD2 only                     | RD2 only               |

| -VIA | Х                      | Х                            | X                      |

| -VIB | X                      | Х                            | X                      |

| -VIE | X                      | X                            | X                      |

| -VIL | RD2 only               | RD2 only                     | RD2 only               |

| -VIM | RD2 only               | RD2 only                     | RD2 only               |

| -LIA | Х                      | Х                            | X                      |

| -LIB | X                      | Х                            | X                      |

| -LIE | X                      | Х                            | X                      |

| -LIL | RD2 only               | RD2 only                     | RD2 only               |

| -LIM | RD2 only               | RD2 only                     | RD2 only               |

| -EA  | Х                      |                              | X                      |

| -EB  | X                      |                              | X                      |

| -EE  | X                      |                              | X                      |

| -EL  | RD2 only               |                              | RD2 only               |

| -EM  | RD2 only               |                              | RD2 only               |

| -EJ  |                        |                              | RC2 and RD2 only       |

| -EK  |                        |                              | RC2 and RD2 only       |

| -EN  |                        |                              | RD2 only               |

### Table 48. Possible Ordering Entries

• -Ex for samples

- Tape and Reel available for B, E, L and M packages

- Dry pack mandatory for E and M packages