#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40/30MHz                                                                 |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIL                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c51rc2-vca |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| PDIL40<br>PLCC44                       | ROM (bytes) | EPROM (bytes) | XRAM (bytes) | TOTAL RAM<br>(bytes) | I/O      |

|----------------------------------------|-------------|---------------|--------------|----------------------|----------|

| VQFP44 1.4<br>TS80C51RA2<br>TS80C51RD2 | 0 0         | 0 0           | 256<br>768   | 512<br>1024          | 32<br>32 |

| TS83C51RB2                             | 16k         | 0             | 256          | 512                  | 32       |

| TS83C51RC2                             | 32k         | 0             | 256          | 512                  | 32       |

| TS83C51RD2                             | 64k         | 0             | 768          | 1024                 | 32       |

| TS87C51RB2                             | 0           | 16k           | 256          | 512                  | 32       |

| TS87C51RC2                             | 0           | 32k           | 256          | 512                  | 32       |

| TS87C51RD2                             | 0           | 64k           | 768          | 1024                 | 32       |

| PLCC68<br>VQFP64 1.4 | ROM (bytes) | EPROM (bytes) | XRAM (bytes) | TOTAL RAM<br>(bytes) | I/O |

|----------------------|-------------|---------------|--------------|----------------------|-----|

| TS80C51RD2           | 0           | 0             | 768          | 1024                 | 48  |

| TS83C51RD2           | 64k         | 0             | 768          | 1024                 | 48  |

| TS87C51RD2           | 0           | 64k           | 768          | 1024                 | 48  |

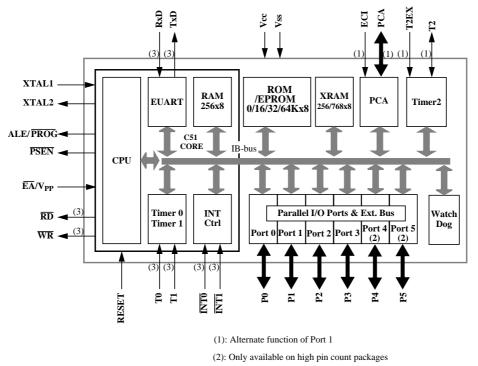

# 3. Block Diagram

# 4. SFR Mapping

The Special Function Registers (SFRs) of the TS80C51Rx2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3, P4, P5

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- HDW Watchdog Timer Reset: WDTRST, WDTPRG

- PCA registers: CL, CH, CCAPiL, CCAPiH, CCON, CMOD, CCAPMi

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

#### Table 1. All SFRs with their address and their reset value

|     | Bit<br>addressable                 |                    | Non Bit addressable |                     |                      |                      |                      |                                     |     |  |

|-----|------------------------------------|--------------------|---------------------|---------------------|----------------------|----------------------|----------------------|-------------------------------------|-----|--|

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |

| F8h |                                    | CH<br>0000 0000    | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAPL2H<br>XXXX XXXX | CCAPL3H<br>XXXX XXXX | CCAPL4H<br>XXXX XXXX |                                     | FFh |  |

| F0h | B<br>0000 0000                     |                    |                     |                     |                      |                      |                      |                                     | F7h |  |

| E8h | P5 bit<br>addressable<br>1111 1111 | CL<br>0000 0000    | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                                     | EFh |  |

| E0h | ACC<br>0000 0000                   |                    |                     |                     |                      |                      |                      |                                     | E7h |  |

| D8h | CCON<br>00X0 0000                  | CMOD<br>00XX X000  | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                                     | DFh |  |

| D0h | PSW<br>0000 0000                   |                    |                     |                     |                      |                      |                      |                                     | D7h |  |

| C8h | T2CON<br>0000 0000                 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                                     | CFh |  |

| C0h | P4 bit<br>addressable<br>1111 1111 |                    |                     |                     |                      |                      |                      | P5 byte<br>addressable<br>1111 1111 | C7h |  |

| B8h | IP<br>X000 000                     | SADEN<br>0000 0000 |                     |                     |                      |                      |                      |                                     | BFh |  |

| B0h | P3<br>1111 1111                    |                    |                     |                     |                      |                      |                      | IPH<br>X000 0000                    | B7h |  |

| A8h | IE<br>0000 0000                    | SADDR<br>0000 0000 |                     |                     |                      |                      |                      |                                     | AFh |  |

| A0h | P2<br>1111 1111                    |                    | AUXR1<br>XXXX0XX0   |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000                 | A7h |  |

| 98h | SCON<br>0000 0000                  | SBUF<br>XXXX XXXX  |                     |                     |                      |                      |                      |                                     | 9Fh |  |

| 90h | P1<br>1111 1111                    |                    |                     |                     |                      |                      |                      |                                     | 97h |  |

| 88h | TCON<br>0000 0000                  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XXXXXX00     | CKCON<br>XXXX XXX0                  | 8Fh |  |

| 80h | P0<br>1111 1111                    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000                   | 87h |  |

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |

|     | macaminad                          |                    |                     |                     |                      |                      |                      |                                     |     |  |

reserved

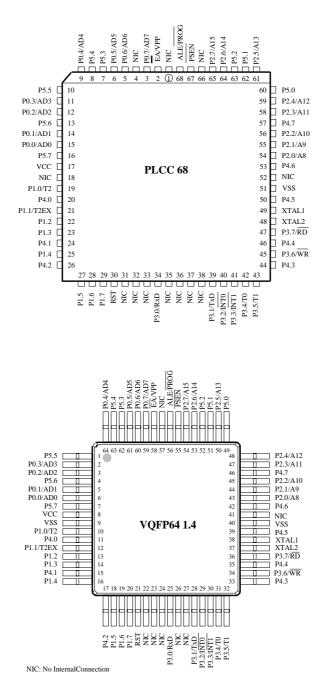

|          | PLCC68 | SQUARE VQFP64<br>1.4 |

|----------|--------|----------------------|

| P3.2     | 40     | 29                   |

| P3.3     | 41     | 30                   |

| P3.4     | 42     | 31                   |

| P3.5     | 43     | 32                   |

| P3.6     | 45     | 34                   |

| P3.7     | 47     | 36                   |

| RESET    | 30     | 21                   |

| ALE/PROG | 68     | 56                   |

| PSEN     | 67     | 55                   |

| EA/VPP   | 2      | 58                   |

| XTAL1    | 49     | 38                   |

| XTAL2    | 48     | 37                   |

| P4.0     | 20     | 11                   |

| P4.1     | 24     | 15                   |

| P4.2     | 26     | 17                   |

| P4.3     | 44     | 33                   |

| P4.4     | 46     | 35                   |

| P4.5     | 50     | 39                   |

| P4.6     | 53     | 42                   |

| P4.7     | 57     | 46                   |

| P5.0     | 60     | 49                   |

| P5.1     | 62     | 51                   |

| P5.2     | 63     | 52                   |

| P5.3     | 7      | 62                   |

| P5.4     | 8      | 63                   |

| P5.5     | 10     | 1                    |

| P5.6     | 13     | 4                    |

| P5.7     | 16     | 7                    |

## 6. TS80C51Rx2 Enhanced Features

In comparison to the original 80C52, the TS80C51Rx2 implements some new features, which are:

- The X2 option.

- The Dual Data Pointer.

- The extended RAM.

- The Programmable Counter Array (PCA).

- The Watchdog.

- The 4 level interrupt priority system.

- The power-off flag.

- The ONCE mode.

- The ALE disabling.

- Some enhanced features are also located in the UART and the timer 2.

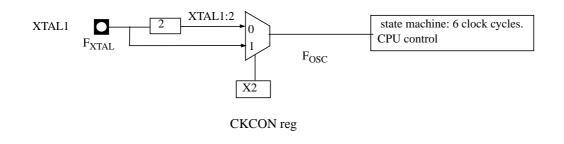

### 6.1. X2 Feature

The TS80C51Rx2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

#### 6.1.1. Description

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 1. shows the clock generation block diagram. X2 bit is validated on XTAL1÷2 rising edge to avoid glitches when switching from X2 to STD mode. Figure 2. shows the mode switching waveforms.

Figure 1. Clock Generation Diagram

### 6.3. Expanded RAM (XRAM)

The TS80C51Rx2 provide additional Bytes of ramdom access memory (RAM) space for increased data parameter handling and high level language usage.

RA2, RB2 and RC2 devices have 256 bytes of expanded RAM, from 00H to FFH in external data space; RD2 devices have 768 bytes of expanded RAM, from 00H to 2FFH in external data space.

The TS80C51Rx2 has internal data memory that is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register. (See Table 5.)

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

- Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data ,accesses the SFR at location 0A0H (which is P2).

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

- The 256 or 768 XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first 256 or 768 bytes of external data memory.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 ( $\overline{WR}$ ) and P3.7 ( $\overline{RD}$ ). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than FFH (i.e. 0100H to FFFFH) (higher than 2FFH (i.e. 0300H to FFFFH for RD devices) will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, so with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Refer to Figure . For RD devices, accesses to expanded RAM from 100H to 2FFH can only be done thanks to the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @Ri and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ Ri and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

#### Table 7. T2MOD Register

T2MOD - Timer 2 Mode Control Register (C9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|---|---|---|---|---|---|------|------|

| - | - | - | - | - | - | T2OE | DCEN |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                  |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| 7          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |

| 6          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |

| 5          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |

| 4          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |

| 3          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |

| 2          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |

| 1          | T2OE            | Timer 2 Output Enable bit<br>Clear to program P1.0/T2 as clock input or I/O port.<br>Set to program P1.0/T2 as clock output. |

| 0          | DCEN            | Down Counter Enable bit<br>Clear to disable timer 2 as up/down counter.<br>Set to enable timer 2 as up/down counter.         |

Reset Value = XXXX XX00b Not bit addressable

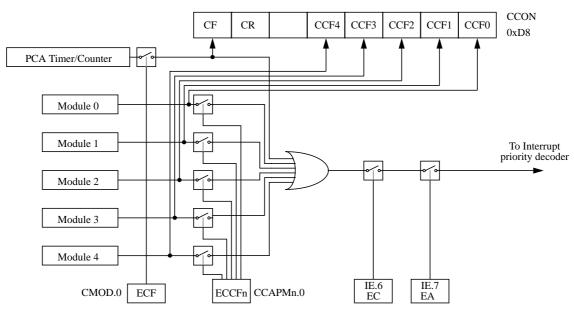

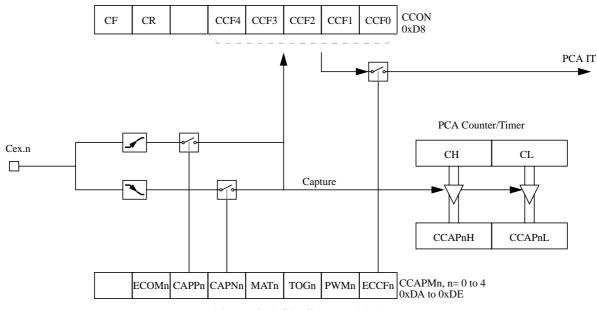

Figure 8. PCA Interrupt System

PCA Modules: each one of the five compare/capture modules has six possible functions. It can perform:

- 16-bit Capture, positive-edge triggered,

- 16-bit Capture, negative-edge triggered,

- 16-bit Capture, both positive and negative-edge triggered,

- 16-bit Software Timer,

- 16-bit High Speed Output,

- 8-bit Pulse Width Modulator.

In addition, module 4 can be used as a Watchdog Timer.

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (See Table 10). The registers contain the bits that control the mode that each module will operate in.

- The ECCF bit (CCAPMn.0 where n=0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module.

- PWM (CCAPMn.1) enables the pulse width modulation mode.

- The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register.

- The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

- The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition.

- The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function.

Table 11 shows the CCAPMn settings for the various PCA functions.

### 6.5.1. PCA Capture Mode

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (Refer to Figure 9).

Figure 9. PCA Capture Mode

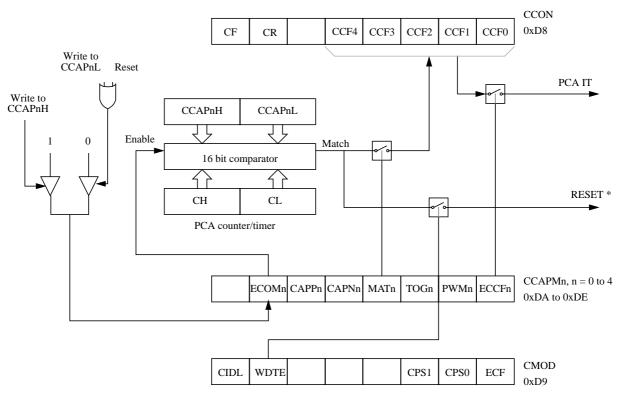

### 6.5.2. 16-bit Software Timer / Compare Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (See Figure 10).

\* Only for Module 4

#### Figure 10. PCA Compare Mode and PCA Watchdog Timer

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen. Writing to CCAPnH will set the ECOM bit.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

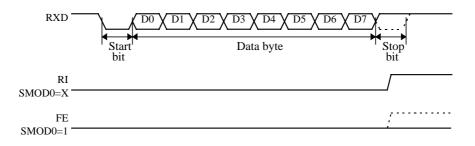

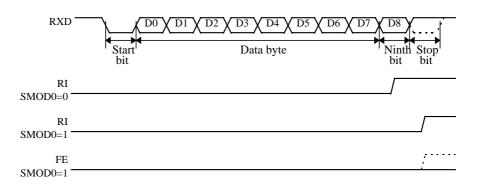

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 14. and Figure 15.).

Figure 15. UART Timings in Modes 2 and 3

### 6.6.2. Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, you may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit.

To support automatic address recognition, a device is identified by a given address and a broadcast address.

NOTE: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

#### 6.6.3. Given Address

Each device has an individual address that is specified in SADDR register; the SADEN register is a mask byte that contains don't-care bits (defined by zeros) to form the device's given address. The don't-care bits provide the flexibility to address one or more slaves at a time. The following example illustrates how a given address is formed. To address a device by its individual address, the SADEN mask byte must be 1111 1111b. For example:

| SADDR | 0101 0110b        |

|-------|-------------------|

| SADEN | <u>1111 1100b</u> |

| Given | 0101 01XXb        |

The following is an example of how to use given addresses to address different slaves:

| Slave A: | SADDR<br><u>SADEN</u><br>Given | 1111 0001b<br><u>1111 1010b</u><br>1111 0X0Xb |

|----------|--------------------------------|-----------------------------------------------|

| Slave B: | SADDR<br><u>SADEN</u><br>Given | 1111 0011b<br><u>1111 1001b</u><br>1111 0XX1b |

| Slave C: | SADDR<br><u>SADEN</u><br>Given | 1111 0010b<br><u>1111 1101b</u><br>1111 00X1b |

The SADEN byte is selected so that each slave may be addressed separately.

For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1. To communicate with slave A only, the master must send an address where bit 0 is clear (e.g. 1111 0000b).

For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

### 6.6.4. Broadcast Address

A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

| 0101 0110b |

|------------|

| 1111 1100b |

| 1111 111Xb |

|            |

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

| Slave A: | SADDR<br><u>SADEN</u><br>Broadcast  | 1111 0001b<br><u>1111 1010b</u><br>1111 1X11b, |

|----------|-------------------------------------|------------------------------------------------|

| Slave B: | SADDR<br><u>SADEN</u><br>Broadcast  | 1111 0011b<br><u>1111 1001b</u><br>1111 1X11B, |

| Slave C: | SADDR=<br><u>SADEN</u><br>Broadcast | 1111 0010b<br><u>1111 1101b</u><br>1111 1111b  |

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

### Table 16. SCON Register

#### SCON - Serial Control Register (98h)

| 7          | 6               | 5                           |                                                                                                                                                                                                                                                       | 4                                      | 3                                                             | 2                                      | 1                               | 0                  |

|------------|-----------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------|----------------------------------------|---------------------------------|--------------------|

| FE/SM0     | SM1             | SN                          | 12                                                                                                                                                                                                                                                    | REN                                    | TB8                                                           | RB8                                    | TI                              | RI                 |

| Bit Number | Bit<br>Mnemonic |                             |                                                                                                                                                                                                                                                       |                                        | Descrip                                                       | tion                                   | -                               |                    |

| 7          | FE              | Clear to<br>Set by h        | raming Error bit (SMOD0=1)<br>Clear to reset the error state, not cleared by a valid stop bit.<br>Set by hardware when an invalid stop bit is detected.<br>SMOD0 must be set to enable access to the FE bit                                           |                                        |                                                               |                                        |                                 |                    |

|            | SM0             |                             | SM1 for                                                                                                                                                                                                                                               | serial port mode                       | selection.<br>access to the SM0                               | bit                                    |                                 |                    |

|            |                 | Serial port I<br><u>SM0</u> | Mode bit<br><u>SM1</u>                                                                                                                                                                                                                                |                                        | Descripti                                                     | on Baud Rate                           | 2                               |                    |

| 6          | SM1             | 0<br>0<br>1<br>1            | 0<br>1<br>0<br>1                                                                                                                                                                                                                                      | 0<br>1<br>2<br>3                       | Shift Reg<br>8-bit UAI<br>9-bit UAI<br>9-bit UAI              | RT Variable<br>RT F <sub>XTAL</sub> /6 | 4 or F <sub>XTAL</sub> /32 (/32 |                    |

| 5          | SM2             | Clear to<br>Set to en       | disable n                                                                                                                                                                                                                                             | nultiprocessor cor<br>tiprocessor comm | cessor Communic<br>nmunication featur<br>unication feature ir | e.                                     | l eventually mode               | 1. This bit should |

| 4          | REN             |                             | disable s                                                                                                                                                                                                                                             | t<br>erial reception.<br>al reception. |                                                               |                                        |                                 |                    |

| 3          | TB8             | Clear to                    | transmit                                                                                                                                                                                                                                              | a logic 0 in the 9t logic 1 in the 9t  |                                                               | d 3.                                   |                                 |                    |

| 2          | RB8             | Cleared<br>Set by h         | Receiver Bit 8 / Ninth bit received in modes 2 and 3<br>Cleared by hardware if 9th bit received is a logic 0.<br>Set by hardware if 9th bit received is a logic 1.<br>In mode 1, if SM2 = 0, RB8 is the received stop bit. In mode 0 RB8 is not used. |                                        |                                                               |                                        |                                 |                    |

| 1          | TI              | Clear to                    | <b>Transmit Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the stop bit in the other modes.                                                                 |                                        |                                                               |                                        |                                 |                    |

| 0          | RI              |                             | acknowle                                                                                                                                                                                                                                              | edge interrupt.                        | th bit time in mode                                           | 0, see Figure 14.                      | and Figure 15. in               | the other modes.   |

Reset Value = 0000 0000b Bit addressable

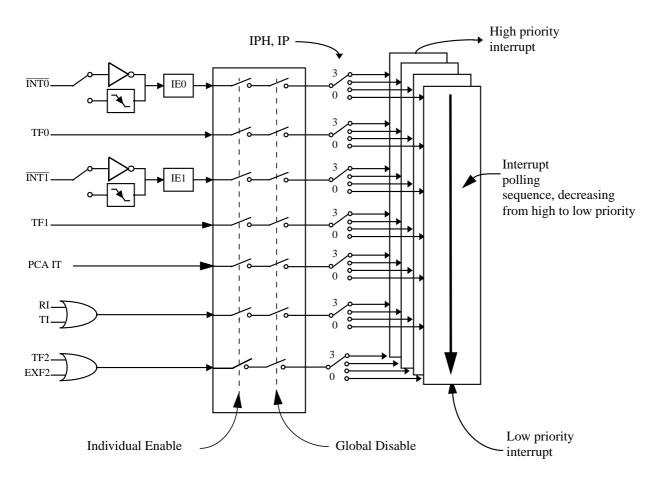

### 6.7. Interrupt System

The TS80C51Rx2 has a total of 7 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), three timer interrupts (timers 0, 1 and 2), the serial port interrupt and the PCA global interrupt. These interrupts are shown in Figure 16.

WARNING: Note that in the first version of RC devices, the PCA interrupt is in the lowest priority. Thus the order in INTO, TF0, INT1, TF1, RI or TI, TF2 or EXF2, PCA.

#### Figure 16. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 19.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 20.) and in the Interrupt Priority High register (See Table 21.). shows the bit values and priority levels associated with each combination.

The PCA interrupt vector is located at address 0033H. All other vector addresses are the same as standard C52 devices.

#### Table 21. IPH Register

#### IPH - Interrupt Priority High Register (B7h)

| 7             | 6               | 5                                                                  | 4                                                               | 3                                                             | 2            | 1    | 0    |  |  |

|---------------|-----------------|--------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|--------------|------|------|--|--|

| -             | РРСН            | РТ2Н                                                               | PSH                                                             | PT1H                                                          | PX1H         | РТОН | РХОН |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                    | Description                                                     |                                                               |              |      |      |  |  |

| 7             | -               | <b>Reserved</b><br>The value read f                                | from this bit is ind                                            | eterminate. Do not s                                          | et this bit. |      |      |  |  |

| 6             | РРСН            | PCA interrupt prio                                                 |                                                                 | <u>ority Level</u><br>Lowest<br>Highest                       |              |      |      |  |  |

| 5             | РТ2Н            | <b>Timer 2 overflow in</b><br><u>PT2H</u><br>0<br>0<br>1<br>1<br>1 | tterrupt Priority<br><u>PT2</u><br>0<br>1<br>0<br>1<br>1        | <b>High bit</b><br><u>Priority Level</u><br>Lowest<br>Highest |              |      |      |  |  |

| 4             | PSH             | Serial port Priority<br>PSH<br>0<br>1<br>1<br>1                    | High bit<br><u>PS</u><br>0<br>1<br>0<br>1                       | <u>Priority Level</u><br>Lowest<br>Highest                    |              |      |      |  |  |

| 3             | PT1H            | <b>Timer 1 overflow in</b><br><u>PT1H</u><br>0<br>0<br>1<br>1<br>1 | <b>tterrupt Priority</b><br><u>PT1</u><br>0<br>1<br>0<br>1<br>1 | High bit<br><u>Priority Level</u><br>Lowest<br>Highest        |              |      |      |  |  |

| 2             | PX1H            | External interrupt<br><u>PX1H</u><br>0<br>1<br>1<br>1              | 1 Priority High b<br><u>PX1</u><br>0<br>1<br>0<br>1             | it <u>Priority Level</u><br>Lowest<br>Highest                 |              |      |      |  |  |

| 1             | РТОН            | Timer 0 overflow in <u>PT0H</u> 0           1           1          | tterrupt Priority<br><u>PTO</u><br>0<br>1<br>0<br>1<br>1        | <b>High bit</b><br><u>Priority Level</u><br>Lowest<br>Highest |              |      |      |  |  |

| 0             | РХОН            | External interrupt<br><u>PX0H</u><br>0<br>1<br>1<br>1              | 0 Priority High b<br><u>PX0</u><br>0<br>1<br>0<br>1             | <b>it</b><br><u>Priority Level</u><br>Lowest<br>Highest       |              |      |      |  |  |

Reset Value = X000 0000b Not bit addressable

| Table 22. | The state of | ports during | idle and | power-down mode |

|-----------|--------------|--------------|----------|-----------------|

|-----------|--------------|--------------|----------|-----------------|

| Mode       | Program<br>Memory | ALE | PSEN | PORT0      | PORT1     | PORT2     | PORT3     |

|------------|-------------------|-----|------|------------|-----------|-----------|-----------|

| Idle       | Internal          | 1   | 1    | Port Data* | Port Data | Port Data | Port Data |

| Idle       | External          | 1   | 1    | Floating   | Port Data | Address   | Port Data |

| Power Down | Internal          | 0   | 0    | Port Data* | Port Data | Port Data | Port Data |

| Power Down | External          | 0   | 0    | Floating   | Port Data | Port Data | Port Data |

\* Port 0 can force a "zero" level. A "one" will leave port floating.

### 8. TS87C51RB2/RC2/RD2 EPROM

### 8.1. EPROM Structure

The TS87C51RB2/RC2/RD2 EPROM is divided in two different arrays:

| •  | the code array:                                         |

|----|---------------------------------------------------------|

| •  | the encryption array:                                   |

| In | addition a third non programmable array is implemented: |

| •  | the signature array:                                    |

### 8.2. EPROM Lock System

The program Lock system, when programmed, protects the on-chip program against software piracy.

### 8.2.1. Encryption Array

Within the EPROM array are 64 bytes of encryption array that are initially unprogrammed (all FF's). Every time a byte is addressed during program verify, 6 address lines are used to select a byte of the encryption array. This byte is then exclusive-NOR'ed (XNOR) with the code byte, creating an encrypted verify byte. The algorithm, with the encryption array in the unprogrammed state, will return the code in its original, unmodified form.

When using the encryption array, one important factor needs to be considered. If a byte has the value FFh, verifying the byte will produce the encryption byte value. If a large block (>64 bytes) of code is left unprogrammed, a verification routine will display the content of the encryption array. For this reason all the unused code bytes should be programmed with random values. This will ensure program protection.

### 8.2.2. Program Lock Bits

The three lock bits, when programmed according to Table 29.8.2.3., will provide different level of protection for the on-chip code and data.

| Program Lock Bits |     |     | Protection description |                                                                                                                                                                                                                       |  |  |  |

|-------------------|-----|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Security level    | LB1 | LB2 | LB3                    |                                                                                                                                                                                                                       |  |  |  |

| 1                 | U   | U   | U                      | No program lock features enabled. Code verify will still be encrypted by the encryption array if programmed. MOVC instruction executed from external program memory returns non encrypted data.                       |  |  |  |

| 2                 | Р   | U   | U                      | MOVC instruction executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on reset, and further programming of the EPROM is disabled. |  |  |  |

| 3                 | U   | Р   | U                      | Same as 2, also verify is disabled.                                                                                                                                                                                   |  |  |  |

| 4                 | U   | U   | Р                      | Same as 3, also external execution is disabled.                                                                                                                                                                       |  |  |  |

| Table 29. | Program | Lock | bits |

|-----------|---------|------|------|

|-----------|---------|------|------|

U: unprogrammed,

P: programmed

WARNING: Security level 2 and 3 should only be programmed after EPROM and Core verification.

### 8.2.3. Signature bytes

The TS87C51RB2/RC2/RD2 contains 4 factory programmed signatures bytes. To read these bytes, perform the process described in section 8.3.

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -M | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10 | 8  | 15 | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30 | 22 | 35 | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20 | 15 | 25 | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40 | 25 | 45 | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7  | 5  | 15 | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40 | 30 | 45 | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10 | 10 | 10 | ns    |

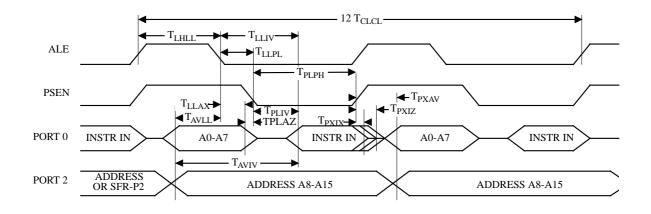

Table 38. AC Parameters for a Variable Clock: derating formula

### 10.5.3. External Program Memory Read Cycle

Figure 25. External Program Memory Read Cycle

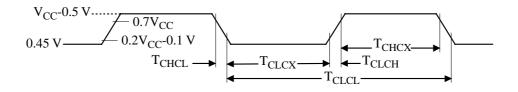

### **10.5.11. External Clock Drive Characteristics (XTAL1)**

| Table | 46. | AC | Parameters |

|-------|-----|----|------------|

|-------|-----|----|------------|

| Symbol                               | Parameter               | Min | Max | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

### 10.5.12. External Clock Drive Waveforms

#### Figure 30. External Clock Drive Waveforms

#### 10.5.13. AC Testing Input/Output Waveforms

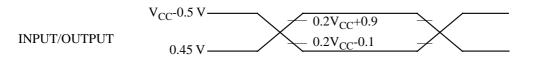

Figure 31. AC Testing Input/Output Waveforms

AC inputs during testing are driven at  $V_{CC}$  - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at  $V_{IH}$  min for a logic "1" and  $V_{IL}$  max for a logic "0".

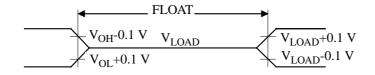

#### **10.5.14. Float Waveforms**

Figure 32. Float Waveforms

|      | TS80C51RA2/RD2 ROMless | TS83C51RB2/RC2/RD2zzz<br>ROM | TS87C51RB2/RC2/RD2 OTP |

|------|------------------------|------------------------------|------------------------|

| -MCA | X                      | Х                            | X                      |

| -MCB | X                      | Х                            | X                      |

| -MCE | X                      | Х                            | X                      |

| -MCL | RD2 only               | RD2 only                     | RD2 only               |

| -MCM | RD2 only               | RD2 only                     | RD2 only               |

| -VCA | Х                      | Х                            | Х                      |

| -VCB | X                      | Х                            | X                      |

| -VCE | Х                      | X                            | X                      |

| -VCL | RD2 only               | RD2 only                     | RD2 only               |

| -VCM | RD2 only               | RD2 only                     | RD2 only               |

| -LCA | Х                      | Х                            | X                      |

| -LCB | X                      | Х                            | X                      |

| -LCE | Х                      | Х                            | X                      |

| -LCL | RD2 only               | RD2 only                     | RD2 only               |

| -LCM | RD2 only               | RD2 only                     | RD2 only               |

| -MIA | Х                      | Х                            | X                      |

| -MIB | X                      | Х                            | X                      |

| -MIE | Х                      | X                            | X                      |

| -MIL | RD2 only               | RD2 only                     | RD2 only               |

| -MIM | RD2 only               | RD2 only                     | RD2 only               |

| -VIA | Х                      | Х                            | X                      |

| -VIB | X                      | Х                            | X                      |

| -VIE | X                      | X                            | X                      |

| -VIL | RD2 only               | RD2 only                     | RD2 only               |

| -VIM | RD2 only               | RD2 only                     | RD2 only               |

| -LIA | Х                      | Х                            | X                      |

| -LIB | X                      | Х                            | X                      |

| -LIE | X                      | Х                            | X                      |

| -LIL | RD2 only               | RD2 only                     | RD2 only               |

| -LIM | RD2 only               | RD2 only                     | RD2 only               |

| -EA  | Х                      |                              | X                      |

| -EB  | X                      |                              | X                      |

| -EE  | X                      |                              | X                      |

| -EL  | RD2 only               |                              | RD2 only               |

| -EM  | RD2 only               |                              | RD2 only               |

| -EJ  |                        |                              | RC2 and RD2 only       |

| -EK  |                        |                              | RC2 and RD2 only       |

| -EN  |                        |                              | RD2 only               |

### Table 48. Possible Ordering Entries

• -Ex for samples

- Tape and Reel available for B, E, L and M packages

- Dry pack mandatory for E and M packages