Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                 |

|----------------------------|--------------------------|

| Core Processor             | 80C51                    |

| Core Size                  | 8-Bit                    |

| Speed                      | 40/30MHz                 |

| Connectivity               | UART/USART               |

| Peripherals                | POR, PWM, WDT            |

| Number of I/O              | 32                       |

| Program Memory Size        | 64KB (64K x 8)           |

| Program Memory Type        | OTP                      |

| EEPROM Size                | -                        |

| RAM Size                   | 1K x 8                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V              |

| Data Converters            | -                        |

| Oscillator Type            | Internal                 |

| Operating Temperature      | 0°C ~ 70°C (TA)          |

| Mounting Type              | Through Hole             |

| Package / Case             | 40-DIP (0.600", 15.24mm) |

| Supplier Device Package    | 40-PDIL                  |

| Purchase URL               |                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4. SFR Mapping

The Special Function Registers (SFRs) of the TS80C51Rx2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3, P4, P5

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- HDW Watchdog Timer Reset: WDTRST, WDTPRG

- PCA registers: CL, CH, CCAPiL, CCAPiH, CCON, CMOD, CCAPMi

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

#### Table 1. All SFRs with their address and their reset value

|     | Bit<br>addressable                 |                    | Non Bit addressable |                     |                      |                      |                      |                                     |     |  |  |

|-----|------------------------------------|--------------------|---------------------|---------------------|----------------------|----------------------|----------------------|-------------------------------------|-----|--|--|

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |  |

| F8h |                                    | CH<br>0000 0000    | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAPL2H<br>XXXX XXXX | CCAPL3H<br>XXXX XXXX | CCAPL4H<br>XXXX XXXX |                                     | FFh |  |  |

| F0h | B<br>0000 0000                     |                    |                     |                     |                      |                      |                      |                                     | F7h |  |  |

| E8h | P5 bit<br>addressable<br>1111 1111 | CL<br>0000 0000    | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                                     | EFh |  |  |

| E0h | ACC<br>0000 0000                   |                    |                     |                     |                      |                      |                      |                                     | E7h |  |  |

| D8h | CCON<br>00X0 0000                  | CMOD<br>00XX X000  | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                                     | DFh |  |  |

| D0h | PSW<br>0000 0000                   |                    |                     |                     |                      |                      |                      |                                     | D7h |  |  |

| C8h | T2CON<br>0000 0000                 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                                     | CFh |  |  |

| C0h | P4 bit<br>addressable<br>1111 1111 |                    |                     |                     |                      |                      |                      | P5 byte<br>addressable<br>1111 1111 | C7h |  |  |

| B8h | IP<br>X000 000                     | SADEN<br>0000 0000 |                     |                     |                      |                      |                      |                                     | BFh |  |  |

| B0h | P3<br>1111 1111                    |                    |                     |                     |                      |                      |                      | IPH<br>X000 0000                    | B7h |  |  |

| A8h | IE<br>0000 0000                    | SADDR<br>0000 0000 |                     |                     |                      |                      |                      |                                     | AFh |  |  |

| A0h | P2<br>1111 1111                    |                    | AUXR1<br>XXXX0XX0   |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000                 | A7h |  |  |

| 98h | SCON<br>0000 0000                  | SBUF<br>XXXX XXXX  |                     |                     |                      |                      |                      |                                     | 9Fh |  |  |

| 90h | P1<br>1111 1111                    |                    |                     |                     |                      |                      |                      |                                     | 97h |  |  |

| 88h | TCON<br>0000 0000                  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XXXXXX00     | CKCON<br>XXXX XXX0                  | 8Fh |  |  |

| 80h | P0<br>1111 1111                    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000                   | 87h |  |  |

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |  |

|     | macaminad                          |                    |                     |                     |                      |                      |                      |                                     |     |  |  |

reserved

## **5.1. Pin Description for 64/68 pin Packages**

Port 4 and Port 5 are 8-bit bidirectional I/O ports with internal pull-ups. Pins that have 1 written to them are pulled high by the internal pull ups and can be used as inputs.

As inputs, pins that are externally pulled low will source current because of the internal pull-ups.

Refer to the previous pin description for other pins.

|      | PLCC68 | SQUARE VQFP64<br>1.4 |

|------|--------|----------------------|

| VSS  | 51     | 9/40                 |

| VCC  | 17     | 8                    |

| P0.0 | 15     | 6                    |

| P0.1 | 14     | 5                    |

| P0.2 | 12     | 3                    |

| P0.3 | 11     | 2                    |

| P0.4 | 9      | 64                   |

| P0.5 | 6      | 61                   |

| P0.6 | 5      | 60                   |

| P0.7 | 3      | 59                   |

| P1.0 | 19     | 10                   |

| P1.1 | 21     | 12                   |

| P1.2 | 22     | 13                   |

| P1.3 | 23     | 14                   |

| P1.4 | 25     | 16                   |

| P1.5 | 27     | 18                   |

| P1.6 | 28     | 19                   |

| P1.7 | 29     | 20                   |

| P2.0 | 54     | 43                   |

| P2.1 | 55     | 44                   |

| P2.2 | 56     | 45                   |

| P2.3 | 58     | 47                   |

| P2.4 | 59     | 48                   |

| P2.5 | 61     | 50                   |

| P2.6 | 64     | 53                   |

| P2.7 | 65     | 54                   |

| P3.0 | 34     | 25                   |

| P3.1 | 39     | 28                   |

# 6. TS80C51Rx2 Enhanced Features

In comparison to the original 80C52, the TS80C51Rx2 implements some new features, which are:

- The X2 option.

- The Dual Data Pointer.

- The extended RAM.

- The Programmable Counter Array (PCA).

- The Watchdog.

- The 4 level interrupt priority system.

- The power-off flag.

- The ONCE mode.

- The ALE disabling.

- Some enhanced features are also located in the UART and the timer 2.

### 6.1. X2 Feature

The TS80C51Rx2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

### 6.1.1. Description

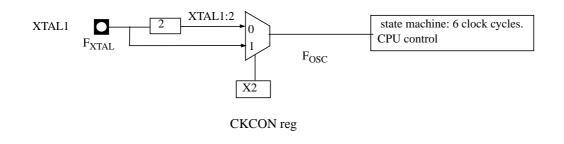

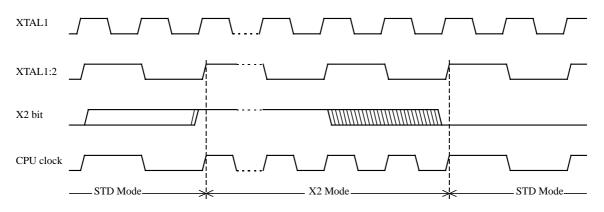

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 1. shows the clock generation block diagram. X2 bit is validated on XTAL1÷2 rising edge to avoid glitches when switching from X2 to STD mode. Figure 2. shows the mode switching waveforms.

Figure 1. Clock Generation Diagram

The X2 bit in the CKCON register (See Table 3.) allows to switch from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature (X2 mode).

### CAUTION

In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals using clock frequency as time reference (UART, timers, PCA...) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. UART with 4800 baud rate will have 9600 baud rate.

### Table 3. CKCON Register

### CKCON - Clock Control Register (8Fh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|---|---|---|---|---|---|---|----|

| - | - | - | - | - | - | - | X2 |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                     |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 6          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 5          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 4          | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 3          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 2          | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 1          | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 0          | X2              | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |

Reset Value = XXXX XXX0b Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel-wm.com)

### 6.2. Dual Data Pointer Register Ddptr

The additional data pointer can be used to speed up code execution and reduce code size in a number of ways.

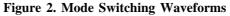

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1/bit0 (See Table 4.) that allows the program code to switch between them (Refer to Figure 3).

Figure 3. Use of Dual Pointer

Table 4. AUXR1: Auxiliary Register 1

| AUXR1<br>Address 0A2H |             | - | - | - | - | GF3 | - | - | DPS |

|-----------------------|-------------|---|---|---|---|-----|---|---|-----|

|                       | Reset value | Х | Х | Х | Х | 0   | Х | Х | 0   |

| Symbol | Function        | Function                                               |  |  |  |  |  |  |

|--------|-----------------|--------------------------------------------------------|--|--|--|--|--|--|

| -      | Not implement   | Not implemented, reserved for future use. <sup>a</sup> |  |  |  |  |  |  |

| DPS    | Data Pointer S  | ata Pointer Selection.                                 |  |  |  |  |  |  |

|        | DPS             | Operating Mode                                         |  |  |  |  |  |  |

|        | 0               | DPTR0 Selected                                         |  |  |  |  |  |  |

|        | 1               | DPTR1 Selected                                         |  |  |  |  |  |  |

| GF3    | This bit is a g | This bit is a general purpose user flag <sup>b</sup> . |  |  |  |  |  |  |

a. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new feature. In that case, the reset value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

b. GF3 will not be available on first version of the RC devices.

### Application

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for example, block operations (copy, compare, search ...) are well served by using one data pointer as a 'source' pointer and the other one as a "destination" pointer.

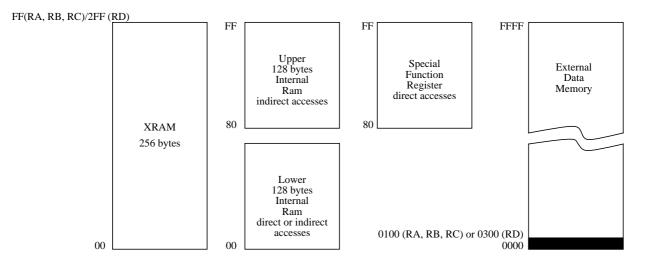

Figure 4. Internal and External Data Memory Address

| Ad | AUXR<br>Idress 08EH                                      |                       | -                                                                                               | EX                          |           |             |         |            |      |   |  |  |

|----|----------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|-----------------------------|-----------|-------------|---------|------------|------|---|--|--|

|    | Reset                                                    | value                 | Х                                                                                               | Х                           | Х         | X           | Х       | Х          | 0    | 0 |  |  |

|    | Symbol                                                   |                       | Function                                                                                        |                             |           |             |         |            |      |   |  |  |

|    | - Not implemented, reserved for future use. <sup>a</sup> |                       |                                                                                                 |                             |           |             |         |            |      |   |  |  |

|    | AO                                                       | AO Disable/Enable ALE |                                                                                                 |                             |           |             |         |            |      |   |  |  |

|    |                                                          | AO                    | Operating Mode                                                                                  |                             |           |             |         |            |      |   |  |  |

|    |                                                          | 0                     | 0 ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 if X2 mode is used) |                             |           |             |         |            |      |   |  |  |

|    |                                                          | 1                     | ALI                                                                                             | E is active                 | only duri | ng a MOV    | X or MO | VC instruc | tion |   |  |  |

|    | EXTRAM                                                   | Internal/E:           | xternal R.                                                                                      | AM (00H-                    | FFH) acce | ess using N | AOVX @  | Ri/@DP     | TR   |   |  |  |

|    |                                                          | EXTRA                 | RAM Operating Mode                                                                              |                             |           |             |         |            |      |   |  |  |

|    |                                                          | 0                     | Internal XRAM access using MOVX @ Ri/ @ DPTR                                                    |                             |           |             |         |            |      |   |  |  |

|    |                                                          | 1                     | Exte                                                                                            | External data memory access |           |             |         |            |      |   |  |  |

Table 5. Auxiliary Register AUXR

a. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

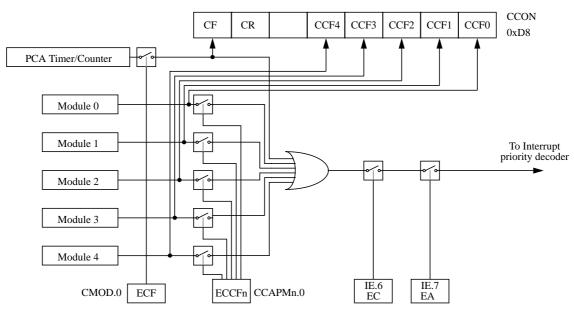

Figure 8. PCA Interrupt System

PCA Modules: each one of the five compare/capture modules has six possible functions. It can perform:

- 16-bit Capture, positive-edge triggered,

- 16-bit Capture, negative-edge triggered,

- 16-bit Capture, both positive and negative-edge triggered,

- 16-bit Software Timer,

- 16-bit High Speed Output,

- 8-bit Pulse Width Modulator.

In addition, module 4 can be used as a Watchdog Timer.

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (See Table 10). The registers contain the bits that control the mode that each module will operate in.

- The ECCF bit (CCAPMn.0 where n=0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module.

- PWM (CCAPMn.1) enables the pulse width modulation mode.

- The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register.

- The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

- The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition.

- The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function.

Table 11 shows the CCAPMn settings for the various PCA functions.

### 6.5.2. 16-bit Software Timer / Compare Mode

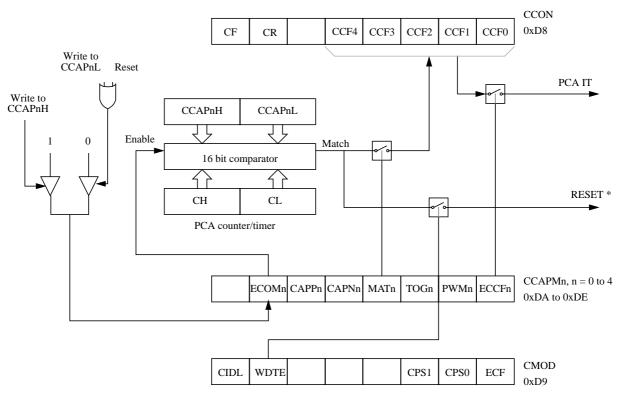

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (See Figure 10).

\* Only for Module 4

### Figure 10. PCA Compare Mode and PCA Watchdog Timer

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen. Writing to CCAPnH will set the ECOM bit.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

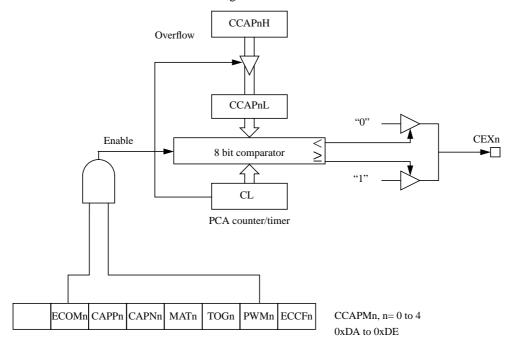

## 6.5.4. Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 12 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

Figure 12. PCA PWM Mode

## 6.5.5. PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 10 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. periodically change the compare value so it will never match the PCA timer,

- 2. periodically change the PCA timer value so it will never match the compare values, or

- 3. disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

### Table 17. PCON Register

#### PCON - Power Control Register (87h)

| 7          | 6               | 5                     | 4                                                                                            |          | 3                  | 2                    | 1                   | 0   |  |  |  |

|------------|-----------------|-----------------------|----------------------------------------------------------------------------------------------|----------|--------------------|----------------------|---------------------|-----|--|--|--|

| SMOD1      | SMOD            | ) -                   | POI                                                                                          | F        | GF1                | GF0                  | PD                  | IDL |  |  |  |

| Bit Number | Bit<br>Mnemonic |                       | Description                                                                                  |          |                    |                      |                     |     |  |  |  |

| 7          | SMOD1           |                       | erial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                   |          |                    |                      |                     |     |  |  |  |

| 6          | SMOD0           |                       | <b>de bit 0</b><br>ect SM0 bit in S0<br>lect FE bit in SC0                                   |          |                    |                      |                     |     |  |  |  |

| 5          | -               | Reserved<br>The value | ead from this bit                                                                            | is inde  | terminate. Do not  | set this bit.        |                     |     |  |  |  |

| 4          | POF             |                       | cognize next reset                                                                           |          | rom 0 to its nomin | al voltage. Can also | o be set by softwar | re. |  |  |  |

| 3          | GF1             |                       | se Flag<br>user for general j<br>for general purp                                            |          |                    |                      |                     |     |  |  |  |

| 2          | GF0             |                       | se Flag<br>user for general j<br>for general purp                                            |          |                    |                      |                     |     |  |  |  |

| 1          | PD              | Cleared by            | wer-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode. |          |                    |                      |                     |     |  |  |  |

| 0          | IDL             |                       | rdware when into                                                                             | errupt ( | or reset occurs.   |                      |                     |     |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

### Table 18. Priority Level Bit Values

| IPH.x | IP.x | Interrupt Level Priority |

|-------|------|--------------------------|

| 0     | 0    | 0 (Lowest)               |

| 0     | 1    | 1                        |

| 1     | 0    | 2                        |

| 1     | 1    | 3 (Highest)              |

A low-priority interrupt can be interrupted by a high priority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence.

### Table 19. IE Register

#### IE - Interrupt Enable Register (A8h)

|   | 7  | 6  | 5   | 4  | 3   | 2   | 1   | 0   |

|---|----|----|-----|----|-----|-----|-----|-----|

| E | ĊA | EC | ET2 | ES | ET1 | EX1 | ЕТО | EX0 |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                 |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | EA              | Enable All interrupt bit<br>Clear to disable all interrupts.<br>Set to enable all interrupts.<br>If EA=1, each interrupt source is individually enabled or disabled by setting or clearing its own interrupt<br>enable bit. |

| 6          | EC              | PCA interrupt enable bit<br>Clear to disable . Set to enable.                                                                                                                                                               |

| 5          | ET2             | Timer 2 overflow interrupt Enable bit<br>Clear to disable timer 2 overflow interrupt.<br>Set to enable timer 2 overflow interrupt.                                                                                          |

| 4          | ES              | Serial port Enable bit<br>Clear to disable serial port interrupt.<br>Set to enable serial port interrupt.                                                                                                                   |

| 3          | ET1             | Timer 1 overflow interrupt Enable bit         Clear to disable timer 1 overflow interrupt.         Set to enable timer 1 overflow interrupt.                                                                                |

| 2          | EX1             | External interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                                                                                                            |

| 1          | ET0             | Timer 0 overflow interrupt Enable bit         Clear to disable timer 0 overflow interrupt.         Set to enable timer 0 overflow interrupt.                                                                                |

| 0          | EX0             | External interrupt 0 Enable bit<br>Clear to disable external interrupt 0.<br>Set to enable external interrupt 0.                                                                                                            |

Reset Value = 0000 0000b Bit addressable

#### Table 21. IPH Register

#### IPH - Interrupt Priority High Register (B7h)

| 7             | 6               | 5                                                                  | 4                                                                                | 3                                                             | 2            | 1    | 0    |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------|--------------|------|------|--|--|--|

| - PPCH        |                 | РТ2Н                                                               | PSH                                                                              | PT1H                                                          | PX1H         | РТОН | РХОН |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                        |                                                                                  |                                                               |              |      |      |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value read f                                | from this bit is ind                                                             | eterminate. Do not s                                          | et this bit. |      |      |  |  |  |

| 6             | РРСН            | PCA interrupt prio<br><u>PPCH</u><br>0<br>1<br>1                   |                                                                                  | <u>ority Level</u><br>Lowest<br>Highest                       |              |      |      |  |  |  |

| 5             | РТ2Н            | <b>Timer 2 overflow in</b><br><u>PT2H</u><br>0<br>0<br>1<br>1<br>1 | tterrupt Priority<br><u>PT2</u> 0<br>1<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1   | <b>High bit</b><br><u>Priority Level</u><br>Lowest<br>Highest |              |      |      |  |  |  |

| 4             | PSH             | Serial port Priority<br><u>PSH</u><br>0<br>1<br>1<br>1             | High bit<br><u>PS</u><br>0<br>1<br>0<br>1                                        | <u>Priority Level</u><br>Lowest<br>Highest                    |              |      |      |  |  |  |

| 3             | PT1H            | <b>Timer 1 overflow in</b><br><u>PT1H</u><br>0<br>0<br>1<br>1<br>1 | terrupt Priority<br><u>PT1</u><br>0<br>1<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | High bit<br><u>Priority Level</u><br>Lowest<br>Highest        |              |      |      |  |  |  |

| 2             | PX1H            | External interrupt<br><u>PX1H</u><br>0<br>0<br>1<br>1<br>1         | 1 Priority High b<br><u>PX1</u><br>0<br>1<br>0<br>1<br>1                         | it <u>Priority Level</u><br>Lowest<br>Highest                 |              |      |      |  |  |  |

| 1             | РТОН            | Timer 0 overflow in <u>PT0H</u> 0           1           1          | tterrupt Priority<br><u>PTO</u><br>0<br>1<br>0<br>1<br>1                         | <b>High bit</b><br><u>Priority Level</u><br>Lowest<br>Highest |              |      |      |  |  |  |

| 0             | РХОН            | External interrupt                                                 | 0 Priority High b<br><u>PX0</u><br>0<br>1<br>0<br>1                              | <b>it</b><br><u>Priority Level</u><br>Lowest<br>Highest       |              |      |      |  |  |  |

Reset Value = X000 0000b Not bit addressable

# 6.11. ONCE<sup>TM</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS80C51Rx2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C51Rx2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and  $\overline{\text{PSEN}}$  is high.

- Hold ALE low as RST is deactivated.

While the TS80C51Rx2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

#### Table 25. External Pin Status during ONCE Mode

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

## **8.3. EPROM Programming**

### 8.3.1. Set-up modes

In order to program and verify the EPROM or to read the signature bytes, the TS87C51RB2/RC2/RD2 is placed in specific set-up modes (See Figure 18.).

Control and program signals must be held at the levels indicated in Table 30.

### **8.3.2.** Definition of terms

Address Lines: P1.0-P1.7, P2.0-P2.5, P3.4, P3.5 respectively for A0-A15 (P2.5 (A13) for RB, P3.4 (A14) for RC, P3.5 (A15) for RD)

Data Lines: P0.0-P0.7 for D0-D7

**Control Signals:** RST, <u>PSEN</u>, P2.6, P2.7, P3.3, P3.6, P3.7.

Program Signals: ALE/PROG, EA/VPP.

| Mode                                      | RST | PSEN | ALE/<br>PROG | <b>EA</b> /VPP | P2.6 | P2.7 | P3.3 | P3.6 | P3.7 |

|-------------------------------------------|-----|------|--------------|----------------|------|------|------|------|------|

| Program Code data                         | 1   | 0    | Г            | 12.75V         | 0    | 1    | 1    | 1    | 1    |

| Verify Code data                          | 1   | 0    | 1            | 1              | 0    |      | 0    | 1    | 1    |

| Program Encryption Array<br>Address 0-3Fh | 1   | 0    | Г            | 12.75V         | 0    | 1    | 1    | 0    | 1    |

| Read Signature Bytes                      | 1   | 0    | 1            | 1              | 0    |      | 0    | 0    | 0    |

| Program Lock bit 1                        | 1   | 0    | Г            | 12.75V         | 1    | 1    | 1    | 1    | 1    |

| Program Lock bit 2                        | 1   | 0    | Г            | 12.75V         | 1    | 1    | 1    | 0    | 0    |

| Program Lock bit 3                        | 1   | 0    | Г            | 12.75V         | 1    | 0    | 1    | 1    | 0    |

Table 30. EPROM Set-Up Modes

## **10.5.2. External Program Memory Characteristics**

| Table | 36. | Symbol | Description |

|-------|-----|--------|-------------|

|-------|-----|--------|-------------|

| Symbol            | Parameter                         |

|-------------------|-----------------------------------|

| Т                 | Oscillator clock period           |

| T <sub>LHLL</sub> | ALE pulse width                   |

| T <sub>AVLL</sub> | Address Valid to ALE              |

| T <sub>LLAX</sub> | Address Hold After ALE            |

| T <sub>LLIV</sub> | ALE to Valid Instruction In       |

| T <sub>LLPL</sub> | ALE to PSEN                       |

| T <sub>PLPH</sub> | PSEN Pulse Width                  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In      |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN |

| T <sub>PXIZ</sub> | Input Instruction FloatAfter PSEN |

| T <sub>PXAV</sub> | PSEN to Address Valid             |

| T <sub>AVIV</sub> | Address to Valid Instruction In   |

| T <sub>PLAZ</sub> | PSEN Low to Address Float         |

### Table 37. AC Parameters for Fix Clock

| Speed             |     | M<br>MHz | X2 1<br>30 1 | V<br>node<br>MHz<br>z equiv. | standar | V<br>rd mode<br>MHz | X2 r<br>20 M | L<br>node<br>MHz<br>z equiv. | standar | L<br><sup>.</sup> d mode<br>⁄IHz | Units |

|-------------------|-----|----------|--------------|------------------------------|---------|---------------------|--------------|------------------------------|---------|----------------------------------|-------|

| Symbol            | Min | Max      | Min          | Max                          | Min     | Max                 | Min          | Max                          | Min     | Max                              |       |

| Т                 | 25  |          | 33           |                              | 25      |                     | 50           |                              | 33      |                                  | ns    |

| T <sub>LHLL</sub> | 40  |          | 25           |                              | 42      |                     | 35           |                              | 52      |                                  | ns    |

| T <sub>AVLL</sub> | 10  |          | 4            |                              | 12      |                     | 5            |                              | 13      |                                  | ns    |

| T <sub>LLAX</sub> | 10  |          | 4            |                              | 12      |                     | 5            |                              | 13      |                                  | ns    |

| T <sub>LLIV</sub> |     | 70       |              | 45                           |         | 78                  |              | 65                           |         | 98                               | ns    |

| T <sub>LLPL</sub> | 15  |          | 9            |                              | 17      |                     | 10           |                              | 18      |                                  | ns    |

| T <sub>PLPH</sub> | 55  |          | 35           |                              | 60      |                     | 50           |                              | 75      |                                  | ns    |

| T <sub>PLIV</sub> |     | 35       |              | 25                           |         | 50                  |              | 30                           |         | 55                               | ns    |

| T <sub>PXIX</sub> | 0   |          | 0            |                              | 0       |                     | 0            |                              | 0       |                                  | ns    |

| T <sub>PXIZ</sub> |     | 18       |              | 12                           |         | 20                  |              | 10                           |         | 18                               | ns    |

| T <sub>AVIV</sub> |     | 85       |              | 53                           |         | 95                  |              | 80                           |         | 122                              | ns    |

| T <sub>PLAZ</sub> |     | 10       |              | 10                           |         | 10                  |              | 10                           |         | 10                               | ns    |

## **10.5.4. External Data Memory Characteristics**

| Parameter                                     |

|-----------------------------------------------|

| RD Pulse Width                                |

| WR Pulse Width                                |

| RD to Valid Data In                           |

| Data Hold After RD                            |

| Data Float After RD                           |

| ALE to Valid Data In                          |

| Address to Valid Data In                      |

| ALE to $\overline{WR}$ or $\overline{RD}$     |

| Address to $\overline{WR}$ or $\overline{RD}$ |

| Data Valid to $\overline{WR}$ Transition      |

| Data set-up to WR High                        |

| Data Hold After $\overline{WR}$               |

| RD Low to Address Float                       |

| RD or WR High to ALE high                     |

|                                               |

### Table 39. Symbol Description

| Speed             |     | -M<br>40 MHz |     | -V<br>X2 mode<br>30 MHz<br>60 MHz equiv. |     | -V<br>standard mode<br>40 MHz |     | -L<br>X2 mode<br>20 MHz<br>40 MHz equiv. |     | -L<br>standard mode<br>30 MHz |    |

|-------------------|-----|--------------|-----|------------------------------------------|-----|-------------------------------|-----|------------------------------------------|-----|-------------------------------|----|

| Symbol            | Min | Max          | Min | Max                                      | Min | Max                           | Min | Max                                      | Min | Max                           |    |

| T <sub>RLRH</sub> | 130 |              | 85  |                                          | 135 |                               | 125 |                                          | 175 |                               | ns |

| T <sub>WLWH</sub> | 130 |              | 85  |                                          | 135 |                               | 125 |                                          | 175 |                               | ns |

| T <sub>RLDV</sub> |     | 100          |     | 60                                       |     | 102                           |     | 95                                       |     | 137                           | ns |

| T <sub>RHDX</sub> | 0   |              | 0   |                                          | 0   |                               | 0   |                                          | 0   |                               | ns |

| T <sub>RHDZ</sub> |     | 30           |     | 18                                       |     | 35                            |     | 25                                       |     | 42                            | ns |

| T <sub>LLDV</sub> |     | 160          |     | 98                                       |     | 165                           |     | 155                                      |     | 222                           | ns |

| T <sub>AVDV</sub> |     | 165          |     | 100                                      |     | 175                           |     | 160                                      |     | 235                           | ns |

| T <sub>LLWL</sub> | 50  | 100          | 30  | 70                                       | 55  | 95                            | 45  | 105                                      | 70  | 130                           | ns |

| T <sub>AVWL</sub> | 75  |              | 47  |                                          | 80  |                               | 70  |                                          | 103 |                               | ns |

| T <sub>QVWX</sub> | 10  |              | 7   |                                          | 15  |                               | 5   |                                          | 13  |                               | ns |

| T <sub>QVWH</sub> | 160 |              | 107 |                                          | 165 |                               | 155 |                                          | 213 |                               | ns |

| T <sub>WHQX</sub> | 15  |              | 9   |                                          | 17  |                               | 10  |                                          | 18  |                               | ns |

| T <sub>RLAZ</sub> |     | 0            |     | 0                                        |     | 0                             |     | 0                                        |     | 0                             | ns |

| T <sub>WHLH</sub> | 10  | 40           | 7   | 27                                       | 15  | 35                            | 5   | 45                                       | 13  | 53                            | ns |

Table 40. AC Parameters for a Fix Clock

## **10.5.11. External Clock Drive Characteristics (XTAL1)**

| Table | 46. | AC | Parameters |

|-------|-----|----|------------|

|-------|-----|----|------------|

| Symbol                               | Parameter               | Min | Max | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

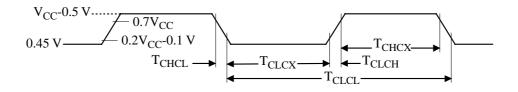

### 10.5.12. External Clock Drive Waveforms

### Figure 30. External Clock Drive Waveforms

### 10.5.13. AC Testing Input/Output Waveforms

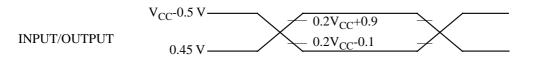

Figure 31. AC Testing Input/Output Waveforms

AC inputs during testing are driven at  $V_{CC}$  - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at  $V_{IH}$  min for a logic "1" and  $V_{IL}$  max for a logic "0".

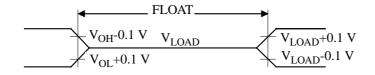

### **10.5.14. Float Waveforms**

Figure 32. Float Waveforms

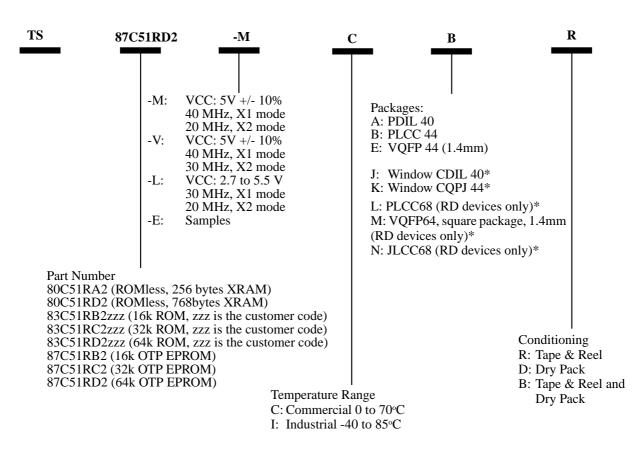

# 11. Ordering Information

(\*) Check with Atmel Wireless & Microcontrollers Sales Office for availability. Ceramic packages (J, K, N) are available for proto typing, not for volume production. Ceramic packages are available for OTP only.

| Code                                   | -M | -V        | -L        | Unit |

|----------------------------------------|----|-----------|-----------|------|

| Standard Mode, oscillator frequency    | 40 | 40        | 30        | MHz  |

| Standard Mode, internal frequency      | 40 | 40        | 30        |      |

| X2 Mode, oscillator frequency          | 20 | 30        | 20        | MHz  |

| X2 Mode, internal equivalent frequency | 40 | <b>60</b> | <b>40</b> |      |