# E·XFL

### NXP USA Inc. - DSPB56720AG Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Not For New Designs                                                 |

|-------------------------|---------------------------------------------------------------------|

| Туре                    | Audio Processor                                                     |

| Interface               | Host Interface, I <sup>2</sup> C, SAI, SPI                          |

| Clock Rate              | 200MHz                                                              |

| Non-Volatile Memory     | External                                                            |

| On-Chip RAM             | 744kB                                                               |

| Voltage - I/O           | 3.30V                                                               |

| Voltage - Core          | 1.00V                                                               |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                     |

| Mounting Type           | Surface Mount                                                       |

| Package / Case          | 144-LQFP                                                            |

| Supplier Device Package | 144-LQFP (20x20)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/dspb56720ag |

|                         |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Electrical Characteristics

### 2.1 Maximum Ratings

Table 2 shows the maximum ratings.

This device contains circuitry protecting against damage due to high static voltage or electrical fields. However, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability of operation is enhanced if unused inputs are pulled to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ). The suggested value for a pull-up or pull-down resistor is 4.7 k $\Omega$ .

### NOTE

In the calculation of timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification will never occur in the same device that has a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

| Rating <sup>1</sup>                                                                    | Symbol                                                                    | Value <sup>1, 2</sup> | Unit |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------|------|

| Supply Voltage                                                                         | V <sub>CORE_VDD</sub> ,<br>V <sub>PLLD_VDD</sub>                          | -0.3 to + 1.26        | V    |

|                                                                                        | V <sub>PLLP_VDD,</sub><br>V <sub>IO_VDD,</sub><br>V <sub>PLLA_VDD</sub> , | -0.3 to + 4.0         | V    |

| Maximum CORE_VDD power supply ramp time <sup>3</sup>                                   | Tr                                                                        | 10                    | ms   |

| Input Voltage per pin excluding VDD and GND                                            | V <sub>IN</sub>                                                           | GND -0.3 to 5.5 V     | V    |

| Current drain per pin excluding V <sub>DD</sub> and GND (Except for pads listed below) | I                                                                         | 12                    | mA   |

| LSYNC_OUT                                                                              | I <sub>lsync_out</sub>                                                    | 16                    | mA   |

| LCLK                                                                                   | I <sub>Iclk</sub>                                                         | 16                    | mA   |

| LALE                                                                                   | I <sub>ale</sub>                                                          | 16                    | mA   |

| TDO                                                                                    | I <sub>JTAG</sub>                                                         | 24                    | mA   |

| Operating temperature range                                                            | TJ                                                                        | -40 to +100           | °C   |

### **Table 2. Maximum Ratings**

### 2.4 **Power Consumption Considerations**

Power dissipation is a key issue in portable DSP applications. Some of the factors which affect current consumption are described in this section. Most of the current consumed by CMOS devices is alternating current (ac), which is charging and discharging the capacitances of the pins and internal nodes.

Current consumption is described by the following formula:

$$\mathbf{I} = \mathbf{C} \times \mathbf{V} \times \mathbf{f}$$

Eqn. 1

where

V=voltage swing f=frequency of node/pin toggle

C=node/pin capacitance

**Example 1. Power Consumption Example**

For a GPIO address pin loaded with 50 pF capacitance, operating at 3.3 V, and with a 150 MHz clock, toggling at its maximum possible rate (75 MHz), the current consumption is

$$I = 50 \times 10^{-12} \times 3.3 \times 75 \times 10^{6} = 12.375 \text{ mA}$$

Eqn. 2

The maximum internal current ( $I_{CCI}$ max) value reflects the typical possible switching of the internal buses on best-case operation conditions, which is not necessarily a real application case. The typical internal current ( $I_{CCItyp}$ ) value reflects the average switching of the internal buses on typical operating conditions.

For applications that require very low current consumption, do the following:

- Minimize the number of pins that are switching.

- Minimize the capacitive load on the pins.

One way to evaluate power consumption is to use a current per MIPS measurement methodology to minimize specific board effects (for example, to compensate for measured board current not caused by the DSP). Use the test algorithm, specific test current measurements, and the following equation to derive the current per MIPS value.

$$I/MIPS = I/MHz = (I_{tvpF2} - I_{tvpF1})/(F2 - F1)$$

Eqn. 3

where :

I<sub>typF2</sub>=current at F2 I<sub>typF1</sub>=current at F1 F2=high frequency (any specified operating frequency) F1=low frequency (any specified operating frequency lower than F2)

### NOTE

F1 should be significantly less than F2. For example, F2 could be 66 MHz and F1 could be 33 MHz. The degree of difference between F1 and F2 determines the amount of precision with which the current rating can be determined for an application.

### 2.5 DC Electrical Characteristics

Table 4 shows the DC electrical characteristics.

|--|

|                                                    | Characteristics                                                                                  | Symbol            | Min         | Тур        | Max       | Unit       |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------|-------------|------------|-----------|------------|

| Commercial                                         | Supply voltages:<br>• Core (Core_VDD)<br>• PLL (PLLD_VDD, PLLD1_VDD)                             | V <sub>DD</sub>   | 0.9         | 1          | 1.1       | V          |

|                                                    | Supply voltages:<br>• I/O (IO_VDD)<br>• PLL (PLLP_VDD, PLLP1_VDD)<br>• PLL (PLLA_VDD, PLLA1_VDD) | V <sub>DDIO</sub> | 3.14        | 3.3        | 3.46      | V          |

| Automotive                                         | Supply voltages:<br>• Core (Core_VDD)<br>• PLL (PLLD_VDD, PLLD1_VDD)                             | V <sub>DD</sub>   | 0.95        | 1          | 1.05      | V          |

|                                                    | Supply voltages:<br>• I/O (IO_VDD)<br>• PLL (PLLP_VDD, PLLP1_VDD)<br>• PLL (PLLA_VDD, PLLA1_VDD) | V <sub>DDIO</sub> | 3.14        | 3.3        | 3.46      | V          |

| Note: To avo                                       | bid a high current condition and possible system damage, all 3.                                  | 3 V supplies m    | ust rise be | fore the 1 | .0 V supp | lies rise. |

| Input low vo                                       | tage                                                                                             | V <sub>IL</sub>   | -0.3        | _          | 0.8       | V          |

| Input leakag                                       | e current                                                                                        | I <sub>IN</sub>   | —           | —          | ± 84      | μA         |

| Clock pin In                                       | out Capacitance (EXTAL)                                                                          | C <sub>IN</sub>   | —           | 18         | —         | pF         |

| High impeda                                        | ance (off-state) input current (@ 3.3 V or 0 V)                                                  | I <sub>TSI</sub>  | -10         | —          | 10        | μA         |

| Output high<br>I <sub>OH</sub> = -12 n<br>LSYNC_O  |                                                                                                  | V <sub>OH</sub>   | 2.4         | _          | -         | V          |

| Output low v<br>I <sub>OL</sub> = 12 m/<br>LSYNC_O | •                                                                                                | V <sub>OL</sub>   | _           | _          | 0.4       | V          |

| Internal pull-                                     | up resistor                                                                                      | R <sub>PU</sub>   | 64          | 92         | 142       | kΩ         |

| Internal pull-                                     | down resistor                                                                                    | R <sub>PD</sub>   | 57          | 90         | 157       | kΩ         |

| Commercial                                         | Internal supply current <sup>1</sup> (core only) at internal clock of 200 MHz                    |                   |             |            |           |            |

|                                                    | In Normal mode                                                                                   | I <sub>CCI</sub>  | —           | 224        | 445       | mA         |

|                                                    | In Wait mode                                                                                     | Iccw              | -           | 121        | 353       | mA         |

|                                                    | <ul> <li>In Stop mode<sup>2</sup></li> </ul>                                                     | I <sub>CCS</sub>  | —           | 90         | 327       | mA         |

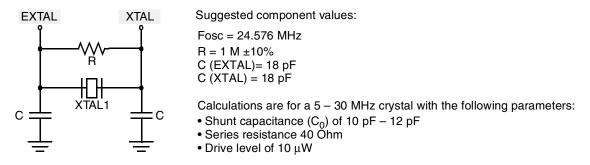

### Figure 9. Using the On-Chip Oscillator

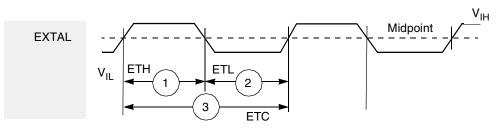

If the DSP56720/DSP56721 system clock is an externally supplied square wave voltage source, it is connected to EXTAL (Figure 10). When the external square wave source is connected to EXTAL, the XTAL pin is not used.

Note: The midpoint is 0.5  $(V_{IH} + V_{IL})$ .

### Figure 10. External Clock Timing

Table 6 lists the clock operation.

| No. | Characteristics                                                                                         | Symbol | Min          | Мах         | Units |

|-----|---------------------------------------------------------------------------------------------------------|--------|--------------|-------------|-------|

| 1   | EXTAL input high <sup>1</sup><br>(40% to 60% duty cycle)<br>• Crystal oscillator<br>• Square wave input | Eth    | 16.67<br>2.5 | 100<br>inf  | ns    |

| 2   | EXTAL input low <sup>1</sup><br>(40% to 60% duty cycle)<br>• Crystal oscillator<br>• Square wave input  | Etl    | 16.67<br>2.5 | 100<br>inf  | ns    |

| 3   | EXTAL cycle time <ul> <li>With PLL disabled</li> <li>With PLL enabled</li> </ul>                        | Etc    | 5<br>33.3    | inf<br>500  | ns    |

| 4   | Instruction cycle time <ul> <li>With PLL disabled</li> <li>With PLL enabled</li> </ul>                  | Тс     | 5.00<br>5.00 | inf<br>5120 | ns    |

### Table 6. Clock Operation

#### Notes:

1. Measured at 50% of the input transition.

2. The indicated duty cycle is for the specified maximum frequency for which a part is rated. The minimum clock high or low time required for correct operation, however, remains the same at lower operating frequencies; therefore, when a lower clock frequency is used, the signal symmetry may vary from the specified duty cycle as long as the minimum high time and low time requirements are met.

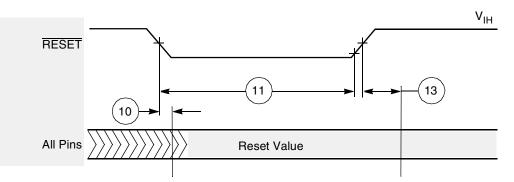

### 2.9 Reset, Stop, Mode Select, and Interrupt Timing

Table 7 shows the reset, stop, mode select, and interrupt timing.

| No. | Characteristics                                                                                                                                                                     | Expression                                                | Min      | Max  | Unit     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------|------|----------|

| 10  | Delay from RESET assertion to all pins at reset value <sup>3</sup>                                                                                                                  | _                                                         | _        | 11   | ns       |

| 11  | <ul> <li>Required RESET duration<sup>4</sup></li> <li>Power on, external clock generator, PLL disabled</li> <li>Power on, external clock generator, PLL enabled</li> </ul>          | $2 \times T_{C}$<br>$2 \times T_{C}$                      | 10<br>10 |      | ns<br>ns |

| 13  | Syn reset deassert delay time<br>• Minimum                                                                                                                                          | $2 \times T_{C}$                                          | 10       |      | ns       |

|     | Maximum (PLL enabled)                                                                                                                                                               | $(2 \text{ x T}_{\text{C}}) + \text{T}_{\text{LOCK}}$     | 200      | —    | us       |

| 14  | Mode select setup time                                                                                                                                                              | —                                                         | 10.0     | _    | ns       |

| 15  | Mode select hold time                                                                                                                                                               | —                                                         | 12       | _    | ns       |

| 16  | Minimum edge-triggered interrupt request assertion width                                                                                                                            | —                                                         | 7        | _    | ns       |

| 17  | Minimum edge-triggered interrupt request deassertion width                                                                                                                          | —                                                         | 4        | _    | ns       |

| 18  | Delay from interrupt trigger to interrupt code execution                                                                                                                            | $10 \times T_{C+4}$                                       | 54       |      | ns       |

| 19  | Duration of level sensitive IRQA assertion to ensure interrupt service (when exiting Stop) <sup>1, 2, 3</sup> • PLL is active during Stop and Stop delay is enabled (OMR Bit 6 = 0) | (128 Kbytes × T <sub>C)</sub>                             | 655      |      | μs       |

|     | • PLL is active during Stop and Stop delay is not enabled (OMR Bit 6 = 1)                                                                                                           | 25 × T <sub>C</sub>                                       | 125      | —    | ns       |

|     | <ul> <li>PLL is not active during Stop and Stop delay is enabled (OMR Bit 6 = 0)</li> </ul>                                                                                         | (128 Kbytes $\times$ T <sub>C</sub> ) + T <sub>LOCK</sub> | 855      | —    | μs       |

|     | <ul> <li>PLL is not active during Stop and Stop delay is not enabled (OMR Bit 6 = 1)</li> </ul>                                                                                     | $(25 \times T_{C}) + T_{LOCK}$                            | 200      | —    | μs       |

| 20  | <ul> <li>Delay from IRQA, IRQB, IRQC, IRQD, NMI assertion to<br/>general-purpose transfer output valid caused by first interrupt<br/>instruction execution<sup>1</sup></li> </ul>   | 10 × T <sub>C</sub> + 3.8                                 | _        | 53.8 | ns       |

| 21  | Interrupt Requests Rate <sup>1</sup> <ul> <li>ESAI, ESAI_1, ESAI_2, ESAI_3, SHI, SHI_1, Timer, Timer_1</li> </ul>                                                                   | $12 \times T_{C}$                                         | _        | 60.0 | ns       |

|     | • DMA                                                                                                                                                                               | $8 \times T_{C}$                                          | —        | 40.0 | ns       |

|     | • IRQ, NMI (edge trigger)                                                                                                                                                           | $8 \times T_{C}$                                          | —        | 40.0 | ns       |

|     | • IRQ (level trigger)                                                                                                                                                               | $12 \times T_{C}$                                         | —        | 60.0 | ns       |

| No. | Characteristics                                                                               | Expression       | Min | Max  | Unit |

|-----|-----------------------------------------------------------------------------------------------|------------------|-----|------|------|

| 22  | DMA Requests Rate <ul> <li>Data read from ESAI, ESAI_1, ESAI_2, ESAI_3, SHI, SHI_1</li> </ul> | $6 \times T_{C}$ |     | 30.0 | ns   |

|     | Data write to ESAI, ESAI_1, ESAI_2, ESAI_3, SHI, SHI_1                                        | $7 \times T_{C}$ | —   | 35.0 | ns   |

|     | Timer, Timer_1                                                                                | $2 \times T_{C}$ | —   | 10.0 | ns   |

|     | • IRQ, NMI (edge trigger)                                                                     | $3 \times T_{C}$ | —   | 15.0 | ns   |

Table 7. Reset, Stop, Mode Select, and Interrupt Timing Parameters

#### Notes:

1. When using fast interrupts and when IRQA, IRQB, IRQC, and IRQD are defined as level-sensitive, timings 19 through 21 apply to prevent multiple interrupt service. To avoid these timing restrictions, the Edge-triggered mode is recommended when using fast interrupts. Long interrupts are recommended when using Level-sensitive mode.

2. For PLL disable, if using an external clock (PCTL Bit 13 = 1), no stabilization delay is required and recovery time will be defined by the OMR Bit 6 settings.

For PLL enable, (if bit 12 of the PCTL register is 0), the PLL is shut down during Stop. Recovering from Stop requires the PLL to get locked. The PLL lock procedure duration, PLL Lock Cycles (PLC), may be in the range of 200  $\mu$ s.

- 3. Periodically sampled and not 100% tested.

- 4. RESET duration is measured during the time in which RESET is asserted, V<sub>DD</sub> is valid, and the EXTAL input is active and valid. When V<sub>DD</sub> is valid, but the other "required RESET duration" conditions (as specified above) have not been yet met, the device circuitry will be in an uninitialized state that can result in significant power consumption and heat-up. Designs should minimize this state to the shortest possible duration.

Figure 11 shows the reset timing diagram.

Figure 11. Reset Timing Diagram

| No. | Characteristics <sup>1,3,4</sup>                                                  | Mode   | Filter Mode | Expression                                                                                                        | Min   | Max  | Unit |

|-----|-----------------------------------------------------------------------------------|--------|-------------|-------------------------------------------------------------------------------------------------------------------|-------|------|------|

| 33  | SCK edge to data out valid                                                        | Master | Bypassed    | $3.0 \times T_{C} + 30$                                                                                           |       | 45   | ns   |

|     | (data out delay time)                                                             | /Slave | Very Narrow | $3.0 	imes T_{C} + 95$                                                                                            | —     | 110  | ns   |

|     |                                                                                   |        | Narrow      | 3.0 × T <sub>C</sub> + 120                                                                                        | —     | 135  | ns   |

|     |                                                                                   |        | Wide        | $3.0 \times T_{C} + 210$                                                                                          | —     | 225  | ns   |

| 34  | SCK edge to data out not valid                                                    | Master | Bypassed    | $2.0 \times T_{C}$                                                                                                | 10    | _    | ns   |

|     | (data out hold time)                                                              | /Slave | Very Narrow | $2.0 	imes T_{C} + 5$                                                                                             | 15    | _    | ns   |

|     |                                                                                   |        | Narrow      | $2.0 	imes T_{C} + 45$                                                                                            | 55    | _    | ns   |

|     |                                                                                   |        | Wide        | $2.0 	imes T_{C} + 95$                                                                                            | 105   |      | ns   |

| 35  | SS assertion to data out valid<br>(CPHA = 0)                                      | Slave  | —           | —                                                                                                                 | _     | 14.0 | ns   |

| 36  | First SCK sampling edge to HREQ output                                            | Slave  | Bypassed    | $3.0 	imes T_{C} + 30$                                                                                            | 45    | _    | ns   |

|     | deassertion                                                                       |        | Very Narrow | $3.0 	imes T_{C} + 40$                                                                                            | 55    | _    | ns   |

|     |                                                                                   |        | Narrow      | $3.0 	imes T_{C} + 80$                                                                                            | 95    | _    | ns   |

|     |                                                                                   |        | Wide        | 3.0 × T <sub>C</sub> + 130                                                                                        | 145   | _    | ns   |

| 37  | Last SCK sampling edge to HREQ output                                             | Slave  | Bypassed    | $4.0 	imes T_{C} + 30$                                                                                            | 50.0  |      | ns   |

| 37  | not deasserted (CPHA = 1)                                                         |        | Very Narrow | $4.0 	imes T_{C} + 40$                                                                                            | 60.0  | _    | ns   |

|     |                                                                                   |        | Narrow      | $4.0 	imes T_{C} + 80$                                                                                            | 100.0 | _    | ns   |

|     |                                                                                   |        | Wide        | $4.0 \times T_{C} + 130$                                                                                          | 150.0 | _    | ns   |

| 38  | $\overline{SS}$ deassertion to $\overline{HREQ}$ output not deasserted (CPHA = 0) | Slave  | —           | $3.0 \times T_{C} + 30$                                                                                           | 45.0  | _    | ns   |

| 39  | $\overline{SS}$ deassertion pulse width (CPHA = 0)                                | Slave  | _           | $2.0 \times T_{C}$                                                                                                | 10.0  | _    | ns   |

| 40  | HREQ in assertion to first SCK edge                                               | Master | Bypassed    | $\begin{array}{c} 0.5 \times \mathrm{T}_{\mathrm{SPICC}} + 3.0 \times \\ \mathrm{T}_{\mathrm{C}} + 5 \end{array}$ | 49.5  | _    | ns   |

|     |                                                                                   |        | Very Narrow | $\begin{array}{c} 0.5 \times \mathrm{T}_{\mathrm{SPICC}} + 3.0 \times \\ \mathrm{T}_{\mathrm{C}} + 5 \end{array}$ | 49.5  | _    | ns   |

|     |                                                                                   |        | Narrow      | $\begin{array}{c} 0.5 \times \mathrm{T_{SPICC}} + 3.0 \times \\ \mathrm{T_{C}} + 5 \end{array}$                   | 111.5 | —    | ns   |

|     |                                                                                   |        | Wide        | $\begin{array}{c} 0.5 \times \mathrm{T}_{\mathrm{SPICC}} + 3.0 \times \\ \mathrm{T}_{\mathrm{C}} + 5 \end{array}$ | 206.5 |      | ns   |

### Table 8. Serial Host Interface SPI Protocol Timing Parameters (Continued)

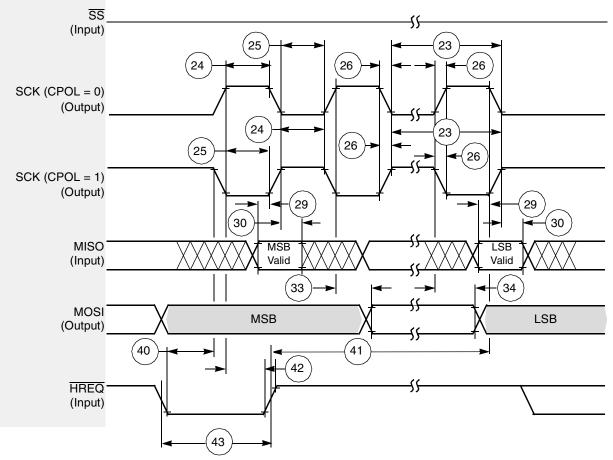

Figure 16. SPI Master Timing Diagram (CPHA = 1)

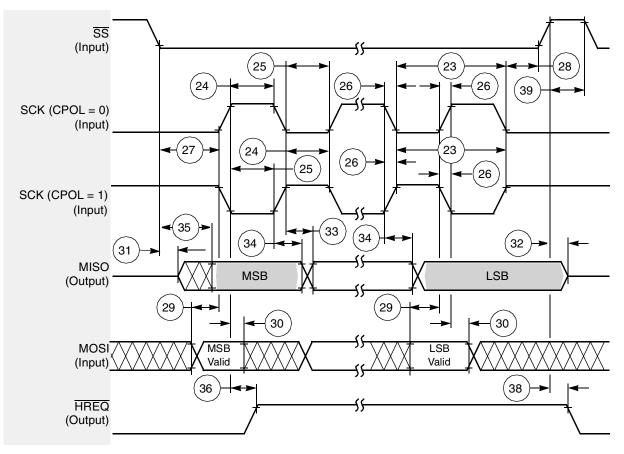

Figure 17. SPI Slave Timing Diagram (CPHA = 0)

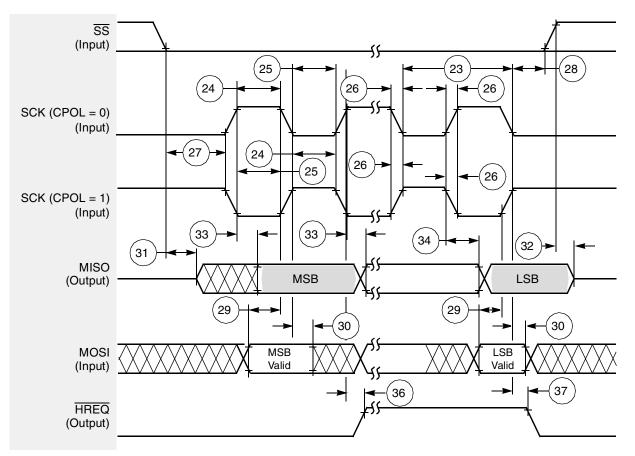

Figure 18. SPI Slave Timing Diagram (CPHA = 1)

# 2.11 Serial Host Interface (SHI) I<sup>2</sup>C Protocol Timing

Table 9 lists the SHI I<sup>2</sup>C protocol timing parameters and Figure 19 shows the timing diagram.

Table 9. SHI I<sup>2</sup>C Protocol Timing Parameters

| Standard I <sup>2</sup> C |                                                                                                                                           |                     |                |                      |           |                      |                      |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|----------------------|-----------|----------------------|----------------------|--|

| No.                       | Characteristics <sup>1,2,3,4,5</sup>                                                                                                      | Symbol/             | Standard       |                      | Fast-Mode |                      | Unit                 |  |

|                           |                                                                                                                                           | Expression          | Min            | Мах                  | Min       | Max                  | Unit                 |  |

|                           | Tolerable Spike Width on SCL or SDA<br>Filters Bypassed<br>Very Narrow Filters enabled<br>Narrow Filters enabled<br>Wide Filters enabled. | -                   | <br> <br> <br> | 0<br>10<br>50<br>100 |           | 0<br>10<br>50<br>100 | ns<br>ns<br>ns<br>ns |  |

| 44                        | SCL clock frequency                                                                                                                       | F <sub>SCL</sub>    | _              | 100                  | —         | 400                  | kHz                  |  |

| 44                        | SCL clock cycle                                                                                                                           | T <sub>SCL</sub>    | 10             | —                    | 2.5       | —                    | μs                   |  |

| 45                        | Bus free time                                                                                                                             | T <sub>BUF</sub>    | 4.7            | —                    | 1.3       | —                    | μs                   |  |

| 46                        | Start condition set-up time                                                                                                               | T <sub>SUSTA</sub>  | 4.7            | —                    | 0.6       | —                    | μs                   |  |

| 47                        | Start condition hold time                                                                                                                 | T <sub>HD;STA</sub> | 4.0            | —                    | 0.6       | —                    | μs                   |  |

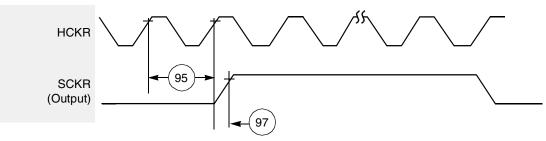

Figure 23. ESAI HCKR Timing

### 2.14 Timer Timing

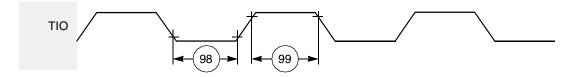

Table 11 lists the timer timing parameters and Figure 24 shows the timing diagram.

| Table 11. Timer Timing Parameters | . Timer Timing Parameters |

|-----------------------------------|---------------------------|

|-----------------------------------|---------------------------|

| No. | Characteristics | Expression             |      |     | Unit |

|-----|-----------------|------------------------|------|-----|------|

| 10. | Characteristics | Expression             | Min  | Мах | onn  |

| 98  | TIO Low         | $2 \times T_{C} + 2.0$ | 12.0 |     | ns   |

| 99  | TIO High        | $2 \times T_{C} + 2.0$ | 12.0 | _   | ns   |

Notes:

1. V<sub>CORE VDD</sub> = 1.00 V  $\pm$  0.10 V; T<sub>J</sub> = -40°C to 100°C, C<sub>L</sub> = 50 pF

2. TIMER\_1 specs match those of TIMER

Figure 24. TIO Timer Event Input Restrictions Diagram

### 2.15 GPIO Timing

Table 12 lists the general purpose input and output (GPIO) timing and Figure 25 shows the timing diagram.

Table 12. GPIO Timing Parameters

| No. | Characteristics <sup>1</sup>                                      | Expression Min |    |   | Unit |

|-----|-------------------------------------------------------------------|----------------|----|---|------|

| 100 | Fsys edge to GPIO out valid (GPIO out delay time) <sup>2</sup>    | — — 7 ns       |    |   | ns   |

| 101 | Fsys edge to GPIO out not valid (GPIO out hold time) <sup>2</sup> | — — 7 ns       |    |   | ns   |

| 102 | Fsys In valid to EXTAL edge (GPIO in set-up time) <sup>2</sup>    | —              | 2  |   | ns   |

| 103 | Fsys edge to GPIO in not valid (GPIO in hold time) <sup>2</sup>   | — 0 —          |    | _ | ns   |

| 104 | Minimum GPIO pulse high width                                     | 2 × TC         | 10 | _ | ns   |

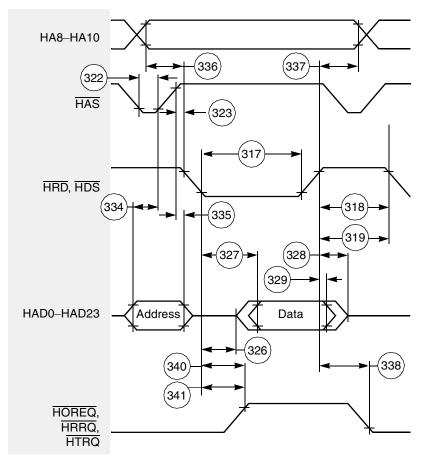

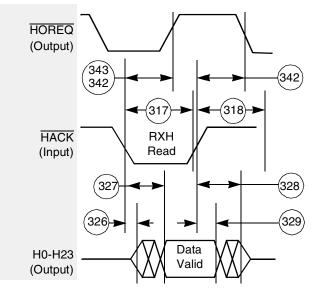

Figure 32. HDI24 Read Timing Diagram, Multiplexed Bus

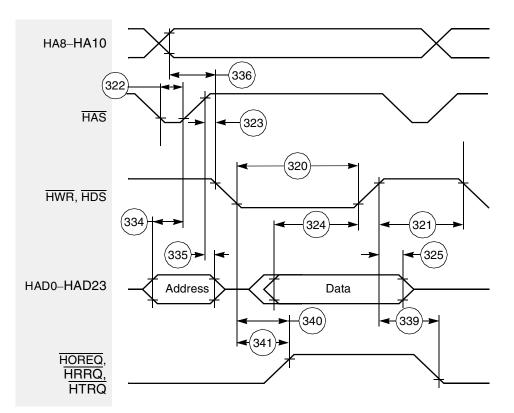

Figure 33. HDI24 Write Timing Diagram, Multiplexed Bus

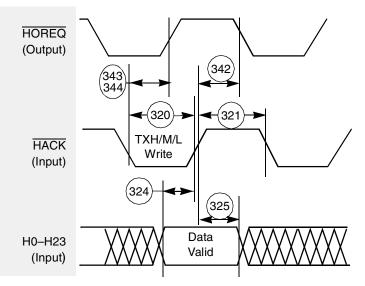

Figure 34. HDI24 Host DMA Write Timing Diagram

Figure 35. HDI24 Host DMA Read Timing Diagram

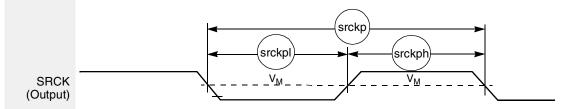

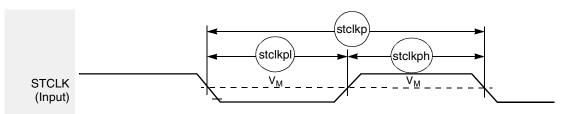

### 2.19 S/PDIF Timing

Table 16 lists the Sony/Philips Digital Interconnect Format (S/PDIF) timing parameters and Figure 36 and Figure 37 show the timing diagrams.

| Table 16. | S/PDIF | Timina | Parameters  |

|-----------|--------|--------|-------------|

|           |        | g      | i ulumeters |

| Characteristics                                                                                                                    | Symbol  | All Free  | quency              | Unit |  |

|------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|---------------------|------|--|

| Characteristics                                                                                                                    | Symbol  | Min       | Мах                 |      |  |

| SPDIFIN1, SPDIFIN2, SPDIFIN3, SPDIFIN4 Skew:<br>asynchronous inputs, no specs apply                                                | _       | _         | 0.7                 | ns   |  |

| <ul> <li>SPDIFOUT1,SPDIFOUT2 output (Load = 50 pf)</li> <li>Skew</li> <li>Transition Risng</li> <li>Transition Falling</li> </ul>  | <br>    | <br><br>_ | 1.5<br>24.2<br>31.3 | ns   |  |

| <ul> <li>SPDIFOUT1, SPDIFOUT2 output (Load = 30 pf)</li> <li>Skew</li> <li>Transition Risng</li> <li>Transition Falling</li> </ul> | <br>    |           | 1.5<br>13.6<br>18.0 | ns   |  |

| SRCK period                                                                                                                        | srckp   | 40.0      | _                   | ns   |  |

| SRCK high period                                                                                                                   | srckph  | 16.0      | _                   | ns   |  |

| SRCK low period                                                                                                                    | srckpl  | 16.0      | _                   | ns   |  |

| STCLK period                                                                                                                       | stclkp  | 40.0      | _                   | ns   |  |

| STCLK high period                                                                                                                  | stclkph | 16.0      | —                   | ns   |  |

| STCLK low period                                                                                                                   | stclkpl | 16.0      |                     | ns   |  |

Figure 36. S/PDIF SRCK Timing Diagram

Figure 37. S/PIDF STCLK Timing Diagram

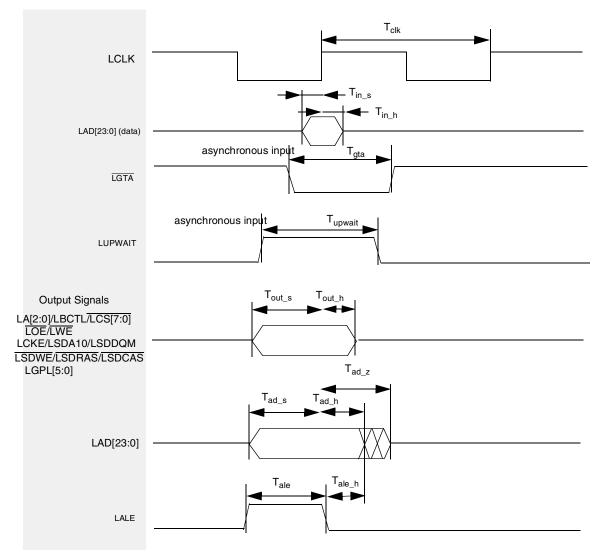

### 2.20 EMC Timing (DSP56720 Only)

The DSP56721 device does not have an EMC module. For EMC timing parameters in DSP56720 devices, see Table 17, through Table 19; for timing diagrams, see Figure 38 through Figure 40.

| Parameter                                                            | Symbol                | Min | Мах | Unit |

|----------------------------------------------------------------------|-----------------------|-----|-----|------|

| LCLK cycle time                                                      | T <sub>clk</sub>      | 10  | —   | ns   |

| LCLK skew to LSYNC_OUT                                               | T <sub>clk_skew</sub> | —   | 160 | ps   |

| Input setup to LSYNC_IN (except LGTA/LUPWAIT)                        | T <sub>in_s</sub>     | 3   | —   | ns   |

| Input hold from LSYNC_IN (except LGTA/LUPWAIT)                       | T <sub>in_h</sub>     | 2   | —   | ns   |

| LGTA valid time                                                      | T <sub>gta</sub>      | 12  | —   | ns   |

| LUPWAIT valid time                                                   | T <sub>upwait</sub>   | 12  | —   | ns   |

| LALE negedge to LAD(address phase) invaild (address latch hold time) | T <sub>ale_h</sub>    | 3   | —   | ns   |

| LALE valid time                                                      | T <sub>ale</sub>      | 3.8 | —   | ns   |

| Output setup from LSYNC_IN (except LAD[23:0] and LALE)               | T <sub>out_s</sub>    | 4   | —   | ns   |

| Output hold from LSYNC_IN (except LAD[23:0] and LALE)                | T <sub>out_h</sub>    | 2   | —   | ns   |

| LAD[23:0] output setup from LSYNC_IN                                 | T <sub>ad_s</sub>     | 3.5 | —   | ns   |

| LAD[23:0] output hold from LSYNC_IN                                  | T <sub>ad_h</sub>     | 1.5 | —   | ns   |

| LSYNC_IN to output high impedance for LAD[23:0]                      | T <sub>ad_z</sub>     |     | 4.3 | ns   |

Table 17. EMC Timing Parameters (EMC PLL Enabled; LCRR[CLKDIV] = 2)

Chapter 22, "External Memory Controller (EMC)," in the *Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual* explains in detail the interfacing and features of EMC. The applicable sections are as follows:

- Section 22.4.4.3, "UPM Signal Timing"

- Section 22.4.4.7, "Memory System Interface Example Using UPM"

| Parameter                                   | Symbol            | Min | Max  | Unit |

|---------------------------------------------|-------------------|-----|------|------|

| LAD[23:0] output setup from LCLK            | T <sub>ad_s</sub> | 12  | —    | ns   |

| LAD[23:0] output hold from LCLK             | T <sub>ad_h</sub> | 17  | —    | ns   |

| LCLK to output high impedance for LAD[23:0] | T <sub>ad_z</sub> |     | 17.1 | ns   |

### Table 19. EMC Timing Parameters (EMC PLL Bypassed; LRCC[CLKDIV] = 8) (Continued)

Notes:

1. A negative hold time means that the signal could be invalid before the LCLK rising edge.

Figure 40. EMC Signals (EMC PLL Bypassed; LRCC[CLKDIV] = 8)

# **3** Functional Description and Application Information

See the Symphony™ DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual (DSP56720RM) for detailed functional and applications information.

# 4 Ordering Information

Table 20 provides ordering information for both the DSP56720 and DSP56721.

| -<br>-              |                |               |                                      |  |

|---------------------|----------------|---------------|--------------------------------------|--|

| Device              | Device Marking | Ambient Temp. | LQFP Package                         |  |

| DSP56720 Commercial | DSPA56720AG    | 0°C–70°C      | $20 \text{ mm} \times 20 \text{ mm}$ |  |

|                     | DSPB56720AG    | 0°C–70°C      | $20 \text{ mm} \times 20 \text{ mm}$ |  |

|                     | DSPC56720AG    | 0°C–70°C      | $20 \text{ mm} \times 20 \text{ mm}$ |  |

| DSP56720 Automotive | DSPA56720CAG   | -40°C-85°C    | $20 \text{ mm} \times 20 \text{ mm}$ |  |

|                     | DSPB56720CAG   | -40°C-85°C    | $20 \text{ mm} \times 20 \text{ mm}$ |  |

|                     | DSPC56720CAG   | -40°C-85°C    | 20 mm × 20 mm                        |  |

| DSP56721 Commercial | DSPA56721AG    | 0°C–70°C      | $20 \text{ mm} \times 20 \text{ mm}$ |  |

|                     | DSPB56721AG    | 0°C–70°C      | 20 mm × 20 mm                        |  |

|                     | DSPC56721AG    | 0°C–70°C      | 20 mm × 20 mm                        |  |

|                     | DSPA56721AF    | 0°C–70°C      | 14 mm × 14 mm                        |  |

|                     | DSPB56721AF    | 0°C–70°C      | 14 mm × 14 mm                        |  |

|                     | DSPC56721AF    | 0°C–70°C      | 14 mm × 14 mm                        |  |

| DSP56721 Automotive | DSPA56721CAG   | -40°C-85°C    | $20 \text{ mm} \times 20 \text{ mm}$ |  |

|                     | DSPB56721CAG   | -40°C-85°C    | 20 mm × 20 mm                        |  |

|                     | DSPC56721CAG   | -40°C-85°C    | 20 mm × 20 mm                        |  |

|                     | DSPA56721CAF   | -40°C-85°C    | 14 mm × 14 mm                        |  |

|                     | DSPB56721CAF   | -40°C-85°C    | 14 mm × 14 mm                        |  |

|                     | DSPC56721CAF   | -40°C-85°C    | 14 mm × 14 mm                        |  |

### Table 20. Ordering Information

# 5 Package Information

For the outline drawings of available device packages, see Table 21 and sections 5.1–5.2.

Table 21. Package Outline Drawings

| Device   | Package              | See                                              |

|----------|----------------------|--------------------------------------------------|

| DSP56720 | 144-pin plastic LQFP | Figure 43 on page 51 and<br>Figure 44 on page 52 |

| DSP56721 | 80-pin plastic LQFP  | Figure 43 on page 51 and<br>Figure 42 on page 50 |

|          | 144-pin plastic LQFP | Figure 43 on page 51 and<br>Figure 44 on page 52 |

### Figure 44. 144-Pin Package Outline Drawing (2 of 2)

### NOTES

- <sup>1</sup> All dimensinos are in millimeters

- <sup>2</sup> Interpret dimensions and tolerances per ASME Y14.5M-1994.

- <sup>3</sup> Datums B, C and D to be determined at datum plane H.

- <sup>4</sup> The top ppackage body size may be smaller than the bottom package size by a maximum of 0.1 mm.

- <sup>5</sup> These dimensions do not include mold protrusions. The maximum allowable protrusion is 0.25 mm per side. These dimensions are maximum body size dimensions including mold mismatch.

- <sup>6</sup> This dimension does not include dambar protrusion. Protrusions shall not cause the lead width to exceed 0.35 mm minimum space between protrusion and an adjacent lead shall be 0.07 mm.

<sup>7</sup> These dimensions are determined at the seating plane, datum A.

# 6 **Product Documentation**

This Data Sheet is labeled as a particular type: Product Preview, Advance Information, or Technical Data. Definitions of these types are available at: http://www.freescale.com. Documentation is available from a local Freescale Semiconductor, Inc. distributor, semiconductor sales office, Literature Distribution Center, or through the Freescale DSP home page on the Internet (the source for the latest information).

The following documents are required for a complete description of the device and are necessary to design properly with the parts:

*DSP56300 Family Manual* (document number DSP56300FM). Detailed description of the 56300-family architecture and the 24-bit core processor and instruction set.

Symphony™ DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual (document number DSP56720RM). Detailed description of memory, peripherals, and interfaces.

DSP56720 Product Brief (DSP56720PB). Brief description of the DSP56720 device.

DSP56721 Product Brief (DSP56721PB). Brief description of the DSP56721 device.

# 7 Revision History

Table 22 summarizes revisions to this document.

#### Table 22. Revision History

| Revision | Date    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5        | 02/2009 | <ul> <li>Updated values and added Commercial and Automotive columns in Table 4, "DC Electrical Characteristics."</li> <li>Updated values in the following tables: Table 7, Table 9, Table 10, Table 11, Table 12, Table 13, Table 15, Table 17, Table 18, and Table 19.</li> <li>In Table 10, "Enhanced Serial Audio Interface Timing Parameters," changed value for 87 to "13".</li> <li>Added Section 2.4, "Power Consumption Considerations."</li> <li>In Section 2.20, "EMC Timing (DSP56720 Only)," added text regarding the EMC chapter and applicable sections.</li> <li>Added automotive information to Table 20, "Ordering Information."</li> </ul> |

| 4        | 04/2008 | <ul> <li>Added formula for thermal characteristics on page 10.</li> <li>Added values for pull-up and pull-down resistors on page 12.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3        | 03/2008 | <ul> <li>Updated order information on page 1 to include additional parts with temperature<br/>specification.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2        | 02/2008 | Timing updates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1        | 12/2007 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support: http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: DSP56720EC Rev. 5 02/2009 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc., 2009. All rights reserved.