# E·XFL

#### NXP USA Inc. - DSPB56720CAG Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Not For New Designs                                                  |

|-------------------------|----------------------------------------------------------------------|

| Туре                    | Audio Processor                                                      |

| Interface               | Host Interface, I <sup>2</sup> C, SAI, SPI                           |

| Clock Rate              | 200MHz                                                               |

| Non-Volatile Memory     | External                                                             |

| On-Chip RAM             | 744kB                                                                |

| Voltage - I/O           | 3.30V                                                                |

| Voltage - Core          | 1.00V                                                                |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                    |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 144-LQFP                                                             |

| Supplier Device Package | 144-LQFP (20x20)                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/dspb56720cag |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Pin Assignments

DSP56720 devices are available in one package type; DSP56721 devices are available in two package types. For the pin assignments of a specific device in a specific package, refer to Section 1.1, "Pinout for DSP56720 144-Pin Plastic LQFP Package," through Section 1.3, "Pinout for DSP56721 144-Pin Plastic LQFP Package."

| Device   | Package              | See                |

|----------|----------------------|--------------------|

| DSP56720 | 144-pin plastic LQFP | Figure 3 on page 5 |

| DSP56721 | 80-pin plastic LQFP  | Figure 4 on page 6 |

|          | 144-pin plastic LQFP | Figure 5 on page 7 |

Table 1. Pin Assignments by Package

For more detailed information about signals, refer to the *Symphony™ DSP56720/DSP56721 Multi-Core Audio Processors Reference Manuall* (DSP56720RM).

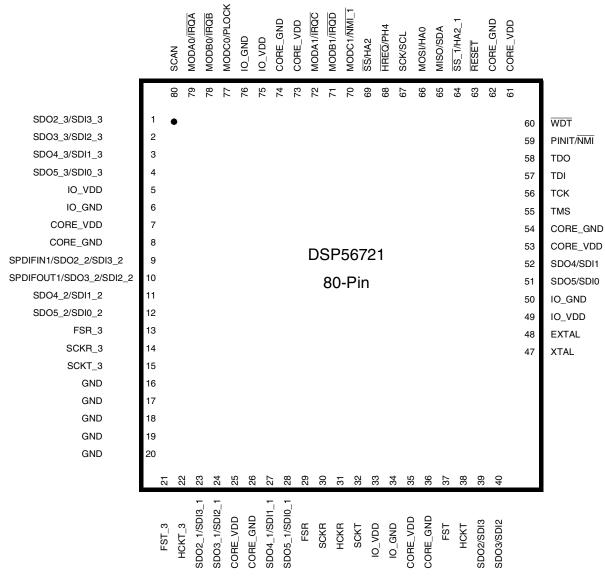

### 1.2 Pinout for DSP56721 80-Pin Plastic LQFP Package

Figure 4 shows the pinout of the DSP56721 80-pin plastic LQFP package.

Figure 4. DSP56721 80-Pin Package

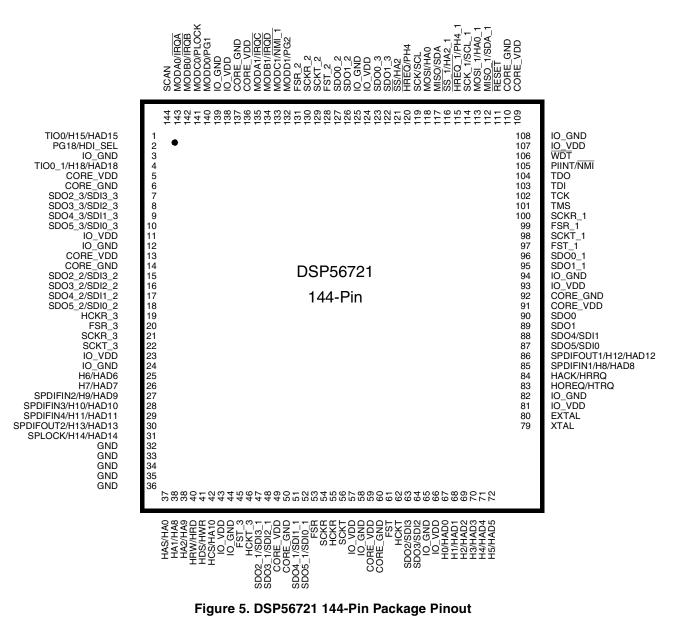

## 1.3 Pinout for DSP56721 144-Pin Plastic LQFP Package

Figure 5 shows the pinout of the DSP56721 144-pin plastic LQFP package.

### 1.4 Pin Multiplexing

Many pins are multiplexed. For more about pin multiplexing, refer to the Symphony™ DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual (DSP56720RM).

|              | Characteristics | Symbol           | Min | Тур | Max | Unit |  |  |  |

|--------------|-----------------|------------------|-----|-----|-----|------|--|--|--|

| Automotive   | In Normal Mode  | I <sub>CCI</sub> |     | 242 | 496 | mA   |  |  |  |

|              | In Wait Mode    | ICCW             | —   | 125 | 409 | mA   |  |  |  |

|              | In Stop mode    | I <sub>CCS</sub> | —   | 107 | 376 | mA   |  |  |  |

| Input capaci | tance           | C <sub>IN</sub>  | _   | _   | 10  | pF   |  |  |  |

#### Table 4. DC Electrical Characteristics (Continued)

#### Notes:

1. The Current Consumption section provides a formula to compute the estimated current requirements in Normal mode. In order to obtain these results, all inputs must be terminated (i.e., not allowed to float). Measurements are based on synthetic intensive DSP benchmarks. The power consumption numbers in this specification are 90% of the measured results of this benchmark. This reflects typical DSP applications. Typical internal supply current is measured with  $V_{CORE_VDD} = 1.0 V$ ,  $V_{DD_IO} = 3.3 V$  at  $T_J = 25^{\circ}$  C. Maximum internal supply current is measured with  $V_{CORE_VDD} = 1.10 V$ ,  $V_{IO_VDD} = 3.4 V$  at  $T_J = 100^{\circ}$ C.

2. In order to obtain these results, all inputs, which are not disconnected at Stop mode, must be terminated (i.e., not allowed to float).

### 2.6 AC Electrical Characteristics

The timing waveforms shown in the AC electrical characteristics section are tested with a  $V_{IL}$  maximum of 0.8 V and a  $V_{IH}$  minimum of 2.0 V for all pins. AC timing specifications, which are referenced to a device input signal, are measured in production with respect to the 50% point of the respective input signal's transition. DSP56720/DSP56721 output levels are measured with the production test machine  $V_{OL}$  and  $V_{OH}$  reference levels set at 0.4 V and 2.4 V, respectively.

### 2.7 Internal Clocks

Internal clock characteristics are listed in Table 5.

| No. | Characteristics                                                                                       | Symbol | Min           | Тур | Max        | Unit | Condition                   |

|-----|-------------------------------------------------------------------------------------------------------|--------|---------------|-----|------------|------|-----------------------------|

| 1   | Comparison Frequency                                                                                  | Fref   | 2             | —   | 8          | MHz  | Fref = Fin/NR               |

| 2   | Input Clock Frequency                                                                                 | Fin    | Max = 200 MHz |     |            |      | —                           |

| 3   | PLL VCO Frequency                                                                                     | Fvco   | 200           | —   | 400        | MHz  | $Fvco = (Fin \times NF)/NR$ |

| 4   | Output Clock Frequency <sup>[1]</sup> <ul> <li>with PLL enabled</li> <li>with PLL disabled</li> </ul> | Fout   | 25<br>—       | _   | 200<br>200 | MHz  | Fout= Fvco/NO<br>Fout = Fin |

| 5   | Duty Cycle                                                                                            | —      | 40            | 50  | 60         | %    | Fvco=<br>200 MHz–400 MHz    |

Table 5. Internal Clocks

#### Notes:

Fin = External frequency, NF = Multiplication Factor, NR = Predivision Factor, NO = Output Divider

## 2.8 External Clock Operation

The DSP56720/DSP56721 system clock is derived from the on-chip oscillator or is externally supplied. To use the on-chip oscillator, connect a crystal and associated resistor/capacitor components to EXTAL and XTAL; see the example in Figure 9.

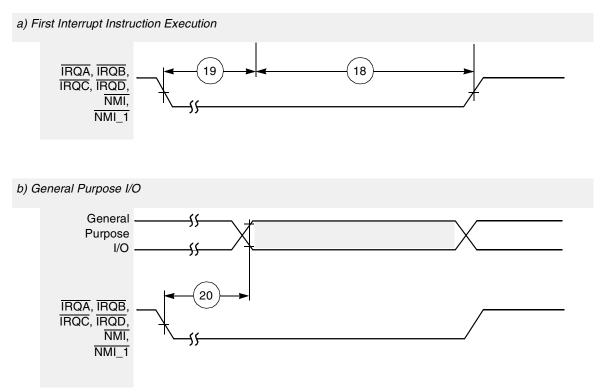

Figure 13 shows the negative edge-triggered external interrupt timing diagram.

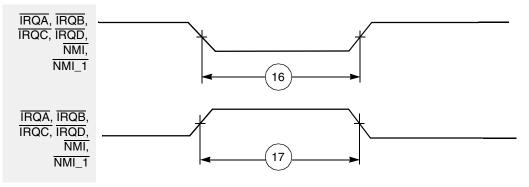

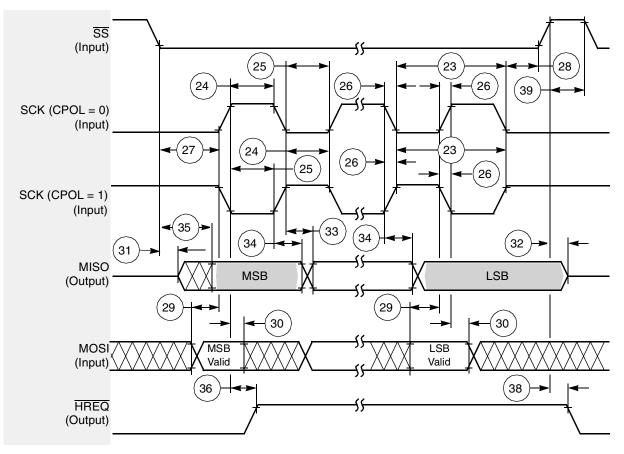

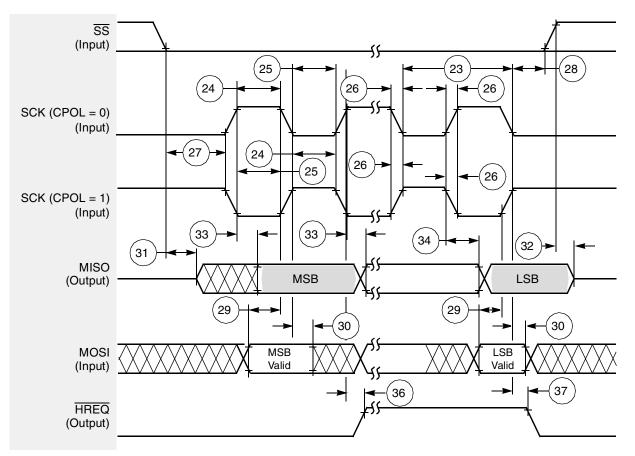

Figure 16. SPI Master Timing Diagram (CPHA = 1)

Figure 17. SPI Slave Timing Diagram (CPHA = 0)

Figure 18. SPI Slave Timing Diagram (CPHA = 1)

## 2.11 Serial Host Interface (SHI) I<sup>2</sup>C Protocol Timing

Table 9 lists the SHI I<sup>2</sup>C protocol timing parameters and Figure 19 shows the timing diagram.

Table 9. SHI I<sup>2</sup>C Protocol Timing Parameters

| Standard I <sup>2</sup> C |                                                                                                                                           |                     |                |                      |     |                      |                      |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|----------------------|-----|----------------------|----------------------|--|--|

| No.                       | Characteristics <sup>1,2,3,4,5</sup>                                                                                                      | Symbol/             | Star           | Standard             |     | Mode                 | Unit                 |  |  |

|                           |                                                                                                                                           | Expression          | Min            | Мах                  | Min | Max                  |                      |  |  |

|                           | Tolerable Spike Width on SCL or SDA<br>Filters Bypassed<br>Very Narrow Filters enabled<br>Narrow Filters enabled<br>Wide Filters enabled. | -                   | <br> <br> <br> | 0<br>10<br>50<br>100 |     | 0<br>10<br>50<br>100 | ns<br>ns<br>ns<br>ns |  |  |

| 44                        | SCL clock frequency                                                                                                                       | F <sub>SCL</sub>    | _              | 100                  | —   | 400                  | kHz                  |  |  |

| 44                        | SCL clock cycle                                                                                                                           | T <sub>SCL</sub>    | 10             | —                    | 2.5 | —                    | μs                   |  |  |

| 45                        | Bus free time                                                                                                                             | T <sub>BUF</sub>    | 4.7            | —                    | 1.3 | —                    | μs                   |  |  |

| 46                        | Start condition set-up time                                                                                                               | T <sub>SUSTA</sub>  | 4.7            | —                    | 0.6 | —                    | μs                   |  |  |

| 47                        | Start condition hold time                                                                                                                 | T <sub>HD;STA</sub> | 4.0            | —                    | 0.6 | —                    | μs                   |  |  |

|     | Standard I <sup>2</sup> C                                                                                                       |                     |                              |      |                          |      |                      |  |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------|------|--------------------------|------|----------------------|--|--|--|--|

| No. | Characteristics <sup>1,2,3,4,5</sup>                                                                                            | Symbol/             | Standard                     |      | Fast-                    | Mode | Unit                 |  |  |  |  |

|     |                                                                                                                                 | Expression          | Min                          | Мах  | Min                      | Мах  | Onit                 |  |  |  |  |

| 60  | HREQin assertion to first SCL edge• Filters bypassed• Very Narrow filters enabled• Narrow filters enabled• Wide filters enabled | T <sub>AS;RQI</sub> | 4327<br>4317<br>4282<br>4227 | <br> | 927<br>917<br>877<br>827 |      | ns<br>ns<br>ns<br>ns |  |  |  |  |

| 61  | First SCL edge to HREQ is not asserted (HREQ in hold time.)                                                                     | t <sub>HO;RQI</sub> | 0.0                          | _    | 0.0                      | _    | ns                   |  |  |  |  |

#### Table 9. SHI I<sup>2</sup>C Protocol Timing Parameters (Continued)

Notes:

1.  $V_{CORE\_VDD}$  = 1.00± 0.10 V;  $T_{J}$  = -40°C to 100°C;  $C_{L}$  = 50 pF.

2. Pull-up resistor:  $R_{P}(min) = 1.5k\Omega$ .

3. Capacitive load:  $C_{b}(max) = 50 \text{ pF}.$

4. All times assume noise free inputs.

5. All times assume internal clock frequency of 200 MHz.

6. SHI\_1 specs match those of SHI.

7. Master Mode

## 2.12 Programming the SHI I<sup>2</sup>C Serial Clock

The programmed serial clock cycle,  $T_{I^2CCP}$ , is specified by the value of the HDM[7:0] and HRS bits of the HCKR (SHI clock control register).

The expression for  $T_{I^2CCP}$  is

$$T_{1^2CCP} = [T_C \times 2 \times (HDM[7:0] + 1) \times (7 \times (1 - HRS) + 1)]$$

Eqn. 4

where

- HRS is the pre scaler rate select bit. When HRS is cleared, the fixed

divide-by-eight pre scaler is operational. When HRS is set, the pre scaler is bypassed.

HDM[7:0] are the divider modulus select bits. A divide ratio from 1 to 256 (HDM[7:0] = \$00 to \$FF) may be selected.

In I<sup>2</sup>C mode, the user may select a value for the programmed serial clock cycle from

$$6 \times T_{C}$$

(if HDM[7:0] = \$02 and HRS = 1) Eqn. 5

to

$$4096 \times T_{C}$$

(if HDM[7:0] = \$FF and HRS = 0) Eqn. 6

The programmed serial clock cycle ( $T_{I^2CCP}$ ) should be chosen in order to achieve the desired SCL serial clock cycle ( $T_{SCL}$ ), as shown in Equation 4.

$$T_{I^{2}CCP} + 3 \times T_{C} + 45ns + T_{R}$$

(Nominal, SCL Serial Clock Cycle (TSCL) generated as master) Eqn. 7

| No. | Characteristics <sup>1, 3, 4</sup>                                       | Symbol | Expression <sup>5</sup> | Min         | Max          | Condition <sup>2</sup> | Unit |

|-----|--------------------------------------------------------------------------|--------|-------------------------|-------------|--------------|------------------------|------|

| 71  | Data in setup time before SCKR (SCK in synchronous mode) falling edge    | _      |                         | 5<br>19.0   | _            | x ck<br>i ck           | ns   |

| 72  | Data in hold time after SCKR falling edge                                | _      | _                       | 3.5<br>9.0  | —            | x ck<br>i ck           | ns   |

| 73  | FSR input (bl, wr) high before SCKR falling edge <sup>6</sup>            | _      |                         | 2.0<br>12.0 | _            | x ck<br>i ck a         | ns   |

| 74  | FSR input (wl) high before SCKR falling edge                             |        |                         | 2.0<br>12.0 |              | x ck<br>i ck a         | ns   |

| 75  | FSR input hold time after SCKR falling edge                              | _      | _                       | 2.5<br>8.5  | —            | x ck<br>i ck a         | ns   |

| 76  | Flags input setup before SCKR falling edge                               | _      | _                       | 0.0<br>19.0 | —            | x ck<br>i ck s         | ns   |

| 77  | Flags input hold time after SCKR falling edge                            |        |                         | 6.0<br>0.0  |              | x ck<br>i ck s         | ns   |

| 78  | SCKT rising edge to FST out (bl) high                                    | _      | _                       |             | 14<br>8.0    | x ck<br>i ck           | ns   |

| 79  | SCKT rising edge to FST out (bl) low                                     |        | _                       |             | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 80  | SCKT rising edge to FST out (wr) high <sup>6</sup>                       | _      |                         |             | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 81  | SCKT rising edge to FST out (wr) low <sup>6</sup>                        |        |                         |             | 22.0<br>12.0 | x ck<br>i ck           | ns   |

| 82  | SCKT rising edge to FST out (wl) high                                    |        | _                       |             | 14<br>9.0    | x ck<br>i ck           | ns   |

| 83  | SCKT rising edge to FST out (wl) low                                     | _      |                         |             | 14<br>10.0   | x ck<br>i ck           | ns   |

| 84  | SCKT rising edge to data out enable from high impedance                  | _      | _                       |             | 22.0<br>17.0 | x ck<br>i ck           | ns   |

| 85  | SCKT rising edge to transmitter #0 drive enable assertion                | _      | _                       |             | 17.0<br>11.0 | x ck<br>i ck           | ns   |

| 86  | SCKT rising edge to data out valid                                       | _      |                         |             | 13<br>13.0   | x ck<br>i ck           | ns   |

| 87  | SCKT rising edge to data out high impedance <sup>7</sup>                 | _      | _                       |             | 13<br>16.0   | x ck<br>i ck           | ns   |

| 88  | SCKT rising edge to transmitter #0 drive enable deassertion <sup>7</sup> | _      | _                       |             | 14.0<br>9.0  | x ck<br>i ck           | ns   |

| 89  | FST input (bl, wr) setup time before SCKT falling edge <sup>6</sup>      |        | _                       | 2.0<br>18.0 | —            | x ck<br>i ck           | ns   |

| 90  | FST input (wl) setup time before SCKT falling edge                       |        | _                       | 2.0<br>18.0 | —            | x ck<br>i ck           | ns   |

| 91  | FST input hold time after SCKT falling edge                              |        | —                       | 4.0<br>5.0  |              | x ck<br>i ck           | ns   |

#### Table 10. Enhanced Serial Audio Interface Timing Parameters (Continued)

| No. | Characteristics <sup>1, 3, 4</sup>                      | Symbol | Expression <sup>5</sup> | Min | Max         | Condition <sup>2</sup> | Unit |

|-----|---------------------------------------------------------|--------|-------------------------|-----|-------------|------------------------|------|

| 92  | FST input (wl) to data out enable from high impedance   | —      | —                       | _   | 21.0        | —                      | ns   |

| 93  | FST input (wl) to transmitter #0 drive enable assertion | —      | —                       | _   | 14.0        | _                      | ns   |

| 94  | Flag output valid after SCKT rising edge                | —      | —                       |     | 14.0<br>9.0 | x ck<br>i ck           | ns   |

| 95  | HCKR/HCKT clock cycle                                   | —      | $2 \times T_{C}$        | 10  | —           | _                      | ns   |

| 96  | HCKT input rising edge to SCKT output                   | —      | —                       |     | 18.0        | —                      | ns   |

| 97  | HCKR input rising edge to SCKR output                   | —      | —                       | _   | 18.0        | —                      | ns   |

#### Table 10. Enhanced Serial Audio Interface Timing Parameters (Continued)

Notes:

1.  $V_{CORE \ VDD}$  = 1.00 ± 0.10 V;  $T_{J}$  = -40°C to 100°C;  $C_{L}$  = 50 pF.

- 2. i ck = internal clock

- x ck = external clock

i ck a = internal clock, asynchronous mode

(Asynchronous implies that SCKT and SCKR are two different clocks.)

i ck s = internal clock, synchronous mode

(Synchronous implies that SCKT and SCKR are the same clock.)

- 3. bl = bit length wl = word length

- wr = word length relative

- 4. SCKT(SCKT pin) = transmit clock SCKR(SCKR pin) = receive clock FST(FST pin) = transmit frame sync FSR(FSR pin) = receive frame sync HCKT(HCKT pin) = transmit high frequency clock HCKR(HCKR pin) = receive high frequency clock

- 5. For the internal clock, the external clock cycle is defined by Tc and the ESAI control register.

- 6. The word-relative frame sync signal waveform relative to the clock operates in the same manner as the bit-length frame sync signal waveform, but spreads from one serial clock before first bit clock (same as bit length frame sync signal), until the one before last bit clock of the first word in frame.

- 7. Periodically sampled and not 100% tested.

- 8. ESAI\_1, ESAI\_2, ESAI\_3 specs match those of ESAI.

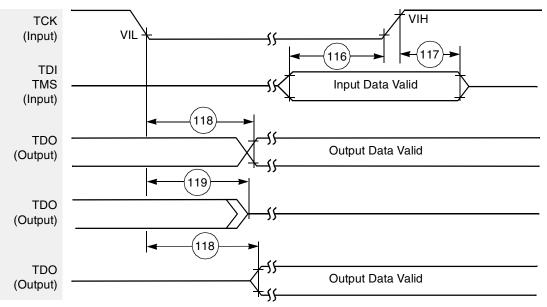

Figure 28. Test Access Port Timing Diagram

## 2.17 Watchdog Timer Timing

Table 14 lists the watchdog timer timing.

Table 14. Watchdog Timer Timing Parameters

| No. | Characteristics                                                         | Expression       | Min  | Мах | Unit |

|-----|-------------------------------------------------------------------------|------------------|------|-----|------|

| 120 | Delay from time-out to fall of WDT, WDT_1                               | $2 \times T_{C}$ | 10.0 | _   | ns   |

| 121 | Delay from timer clear to rise of $\overline{WDT}$ , $\overline{WDT_1}$ | $2 \times Tc$    | 10.0 | _   | ns   |

## 2.18 Host Data Interface (HDI24) Timing

The HDI24 module is only on the DSP56721 device; the DSP56720 device does not have a HDI24 module. Also, only 16 bits of the HDI24 interface are pinned out on the DSP56721 device. Table 15 lists HDI24 timing and Figure 29 through Figure 35 show the timing diagrams.

| No. | Characteristics <sup>2</sup>                                                                                                                                                                                                                  | Expression            | 200  | Unit |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|----|

|     |                                                                                                                                                                                                                                               | Expression            | Min  | Мах  |    |

| 317 | Read data strobe assertion width <sup>3</sup><br>HACK read assertion width                                                                                                                                                                    | T <sub>C</sub> + 9.9  | 14.9 | _    | ns |

| 318 | Read data strobe deassertion width <sup>3</sup><br>HACK read deassertion width                                                                                                                                                                | —                     | 9.9  | —    | ns |

| 319 | Read data strobe deassertion width <sup>3</sup> after "Last Data Register" reads <sup>4,5</sup> ,<br>or between two consecutive CVR, ICR, or ISR reads <sup>6</sup><br>HACK deassertion width after "Last Data Register" reads <sup>4,5</sup> | 2×T <sub>C</sub> +6.6 | 16.6 |      | ns |

| No. | Characteristics <sup>2</sup>                                                                                                                                                        | Expression                | 200 MHz |       | Unit |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------|-------|------|

|     |                                                                                                                                                                                     |                           | Min     | Max   |      |

| 339 | Delay from write data strobe deassertion to host request assertion for "Last Data Register" write <sup>4, 7, 9</sup>                                                                | 2 × T <sub>C</sub>        | 10.0    | _     | ns   |

| 340 | Delay from data strobe assertion to<br>host request deassertion for "Last Data Register" read or write (HROD = $0$ ) <sup>4</sup> , 8, 9                                            | _                         | _       | 19.1  | ns   |

| 341 | Delay from data strobe assertion to<br>host request deassertion for "Last Data Register" read or write (HROD =<br>1, open drain Host Request) <sup>4, 8, 9, 10</sup>                | _                         | _       | 300.0 | ns   |

| 342 | Delay from DMA HACK deassertion to HOREQ assertion                                                                                                                                  |                           |         |       | ns   |

|     | <ul> <li>For "Last Data Register" read<sup>4</sup></li> </ul>                                                                                                                       | 2×T <sub>C</sub> +19.1    | 29.1    |       |      |

|     | <ul> <li>For "Last Data Register" write<sup>4</sup></li> </ul>                                                                                                                      | 1 × T <sub>C</sub> + 19.1 | 24.1    | _     |      |

|     | For other cases                                                                                                                                                                     | —                         | 0.0     |       |      |

| 343 | Delay from DMA $\overline{HACK}$ assertion to HOREQ deassertion<br>• HROD = 0 <sup>4</sup>                                                                                          | —                         | —       | 20.2  | ns   |

| 344 | <ul> <li>Delay from DMA HACK assertion to HOREQ deassertion for "Last Data Register" read or write</li> <li>HROD = 1, open drain Host Request<sup>4</sup>, <sup>10</sup></li> </ul> | _                         | —       | 300.0 | ns   |

#### Table 15. HDI24 Timing Parameters (Continued)

#### Notes:

1. In the timing diagrams that follow, the controls pins are drawn as active low. The pin polarity is programmable.

2.  $V_{CC} = 1.0 \text{ V} \pm 10\%$ ;  $T_J = -40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ ;  $C_L = 50 \text{ pF}$ .

3. The read data strobe is HRD in the dual data strobe mode and HDS in the single data strobe mode.

4. The "last data register" is the register at address \$7, which is the last location to be read or written in data transfers.

5. This timing is applicable only if a read from the "last data register" is followed by a read from the RXL, RXM, or RXH registers without first polling RXDF or HREQ bits, or waiting for the assertion of the HOREQ signal.

- 6. This timing is applicable only if two consecutive reads from one of these registers are executed.

- 7. The write data strobe is HWR in the dual data strobe mode and HDS in the single data strobe mode.

- 8. The data strobe is host read (HRD) or host write (HWR) in the dual data strobe mode and host data strobe (HDS) in the single data strobe mode.

9. The host request is HOREQ in the single host request mode and HRRQ and HTRQ in the double host request mode.

10. In this calculation, the host request signal is pulled up by a 4.7 kW resistor in the open-drain mode.

11. HDI24\_1 specs match those of HDI24.

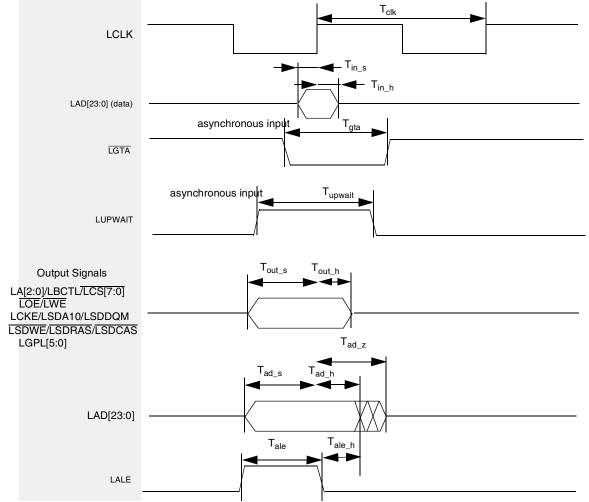

Figure 39. EMC Signals (EMC PLL Bypassed; LRCC[CLKDIV] = 4)

| Table 19. EMC Timing Parameters (EMC PL | L Bypassed; LRCC[CLKDIV] = 8) |

|-----------------------------------------|-------------------------------|

|-----------------------------------------|-------------------------------|

| Parameter                                                             | Symbol              | Min | Мах | Unit |

|-----------------------------------------------------------------------|---------------------|-----|-----|------|

| LCLK cycle time                                                       | T <sub>clk</sub>    | 40  | _   | ns   |

| Input setup to LCLK (except LGTA/LUPWAIT)                             | T <sub>in_s</sub>   | 8   | _   | ns   |

| Input hold from LCLK (except LGTA/LUPWAIT) <sup>1</sup>               | T <sub>in_h</sub>   | -1  | _   | ns   |

| LGTA valid time                                                       | T <sub>gta</sub>    | 42  | _   | ns   |

| LUPWAIT valid time                                                    | T <sub>upwait</sub> | 42  | _   | ns   |

| LALE negedge to LAD (address phase) invalid (address latch hold time) | T <sub>ale_h</sub>  | 5   | —   | ns   |

| LALE valid time                                                       | T <sub>ale</sub>    | 34  | —   | ns   |

| Output setup from LCLK (except LAD[23:0] and LALE)                    | T <sub>out_s</sub>  | 19  | —   | ns   |

| Output hold from LCLK (except LAD[23:0] and LALE)                     | T <sub>out_h</sub>  | 18  | —   | ns   |

## 5.1 80-Pin Package Outline Drawing

Figure 41 and Figure 42 show the 80-pin package outline drawings.

Figure 41. 80-Pin Package Outline Drawing (1 of 2)

#### Figure 42. 80-Pin Package Outline Drawing (2 of 2)

#### NOTES

- <sup>1</sup> Dimensioning and tolerancing per asme Y14.5M-1994.

- <sup>2</sup> Controlling dimension: millimeter

- <sup>3</sup> Datum plane H is located at the bottom of lead and is coincident with the lead where the lead exits the plastic body at the bottom of the parting line.

- <sup>4</sup> Datum E, F and D to be determined at datum plane H.

- <sup>5</sup> Dimensions to be determined at seating plane C.

- <sup>6</sup> Dimensions do not include mold protrusion. Allowable protrusion is 0.25 mm per side. Dimensions include mold mismatch and are determined at datum plane H.

- <sup>7</sup> Dimension does not include dambar protrusion. Dambar protrusion shall not cause the lead width to exceed 0.46 mm. Minimnum space between protrusion and adjacent lead or protrusion 0.07 mm.

## 5.2 144-Pin Package Outline Drawing

Figure 43 and Figure 44 show the 144-pin package drawings.

Figure 43. 144-Pin Package Outline Drawing (1 of 2)

#### Figure 44. 144-Pin Package Outline Drawing (2 of 2)

#### NOTES

- <sup>1</sup> All dimensinos are in millimeters

- <sup>2</sup> Interpret dimensions and tolerances per ASME Y14.5M-1994.

- <sup>3</sup> Datums B, C and D to be determined at datum plane H.

- <sup>4</sup> The top ppackage body size may be smaller than the bottom package size by a maximum of 0.1 mm.

- <sup>5</sup> These dimensions do not include mold protrusions. The maximum allowable protrusion is 0.25 mm per side. These dimensions are maximum body size dimensions including mold mismatch.

- <sup>6</sup> This dimension does not include dambar protrusion. Protrusions shall not cause the lead width to exceed 0.35 mm minimum space between protrusion and an adjacent lead shall be 0.07 mm.

<sup>7</sup> These dimensions are determined at the seating plane, datum A.

## 6 **Product Documentation**

This Data Sheet is labeled as a particular type: Product Preview, Advance Information, or Technical Data. Definitions of these types are available at: http://www.freescale.com. Documentation is available from a local Freescale Semiconductor, Inc. distributor, semiconductor sales office, Literature Distribution Center, or through the Freescale DSP home page on the Internet (the source for the latest information).

The following documents are required for a complete description of the device and are necessary to design properly with the parts:

*DSP56300 Family Manual* (document number DSP56300FM). Detailed description of the 56300-family architecture and the 24-bit core processor and instruction set.

Symphony™ DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual (document number DSP56720RM). Detailed description of memory, peripherals, and interfaces.

DSP56720 Product Brief (DSP56720PB). Brief description of the DSP56720 device.

DSP56721 Product Brief (DSP56721PB). Brief description of the DSP56721 device.

## 7 Revision History

Table 22 summarizes revisions to this document.

#### Table 22. Revision History

| Revision | Date    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5        | 02/2009 | <ul> <li>Updated values and added Commercial and Automotive columns in Table 4, "DC Electrical Characteristics."</li> <li>Updated values in the following tables: Table 7, Table 9, Table 10, Table 11, Table 12, Table 13, Table 15, Table 17, Table 18, and Table 19.</li> <li>In Table 10, "Enhanced Serial Audio Interface Timing Parameters," changed value for 87 to "13".</li> <li>Added Section 2.4, "Power Consumption Considerations."</li> <li>In Section 2.20, "EMC Timing (DSP56720 Only)," added text regarding the EMC chapter and applicable sections.</li> <li>Added automotive information to Table 20, "Ordering Information."</li> </ul> |

| 4        | 04/2008 | <ul> <li>Added formula for thermal characteristics on page 10.</li> <li>Added values for pull-up and pull-down resistors on page 12.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3        | 03/2008 | <ul> <li>Updated order information on page 1 to include additional parts with temperature<br/>specification.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2        | 02/2008 | Timing updates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1        | 12/2007 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support: http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: DSP56720EC Rev. 5 02/2009 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc., 2009. All rights reserved.