Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

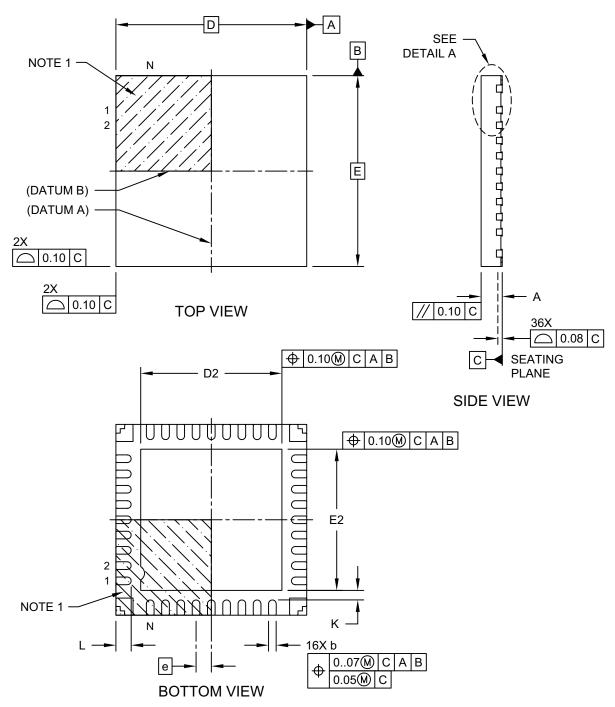

| Package / Case             | 28-UQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-UQFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck128mp202t-i-2n |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33CK256MP508 Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33CK256MP508 devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

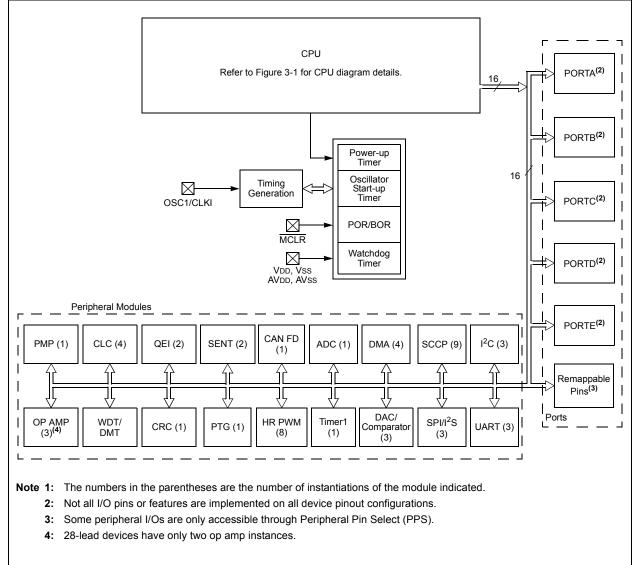

Figure 1-1 shows a general block diagram of the core and peripheral modules of the dsPIC33CK256MP508 family. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

# FIGURE 1-1: dsPIC33CK256MP508 FAMILY BLOCK DIAGRAM<sup>(1)</sup>

## 2.2.1 BULK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a bulk capacitor for integrated circuits, including DSCs, to supply a local power source. The value of the bulk capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the bulk capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

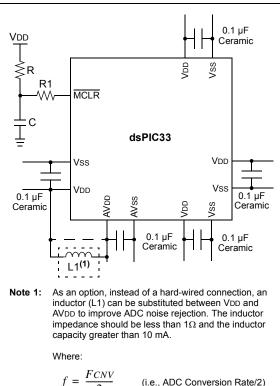

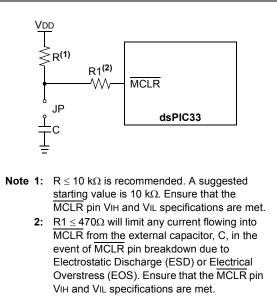

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- · Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

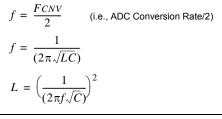

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components, as shown in Figure 2-2, within one-quarter inch (6 mm) from the MCLR pin.

| <b>TABLE 7-4</b> : | INTERRUPT PRIORITY REGISTERS |

|--------------------|------------------------------|

|--------------------|------------------------------|

| Register | Address | Bit 15 | Bit14      | Bit 13     | Bit 12     | Bit 11 | Bit 10     | Bit 9      | Bit 8      | Bit 7 | Bit 6      | Bit 5      | Bit 4      | Bit 3 | Bit 2      | Bit 1      | Bit 0      |

|----------|---------|--------|------------|------------|------------|--------|------------|------------|------------|-------|------------|------------|------------|-------|------------|------------|------------|

| IPC0     | 840h    | _      | CNBIP2     | CNBIP1     | CNBIP0     |        | CNAIP2     | CNAIP1     | CNAIP0     | _     | T1IP2      | T1IP1      | T1IP0      | _     | INT0IP2    | INT0IP1    | INT0IP0    |

| IPC1     | 842h    | _      | CCT1IP2    | CCT1IP1    | CCT1IP0    | _      | CCP1IP2    | CCP1IP1    | CCP1IP0    |       |            | _          | _          | _     | DMA0IP2    | DMA0IP1    | DMA0IP0    |

| IPC2     | 844h    | _      | U1RXIP2    | U1RXIP1    | U1RXIP0    | _      | SPI1TXIP2  | SPI1TXIP1  | SPI1TXIP0  | _     | SPI1RXIP2  | SPI1RXIP1  | SPI1RXIP0  | _     | DMA1IP2    | DMA1IP1    | DMA1IP0    |

| IPC3     | 846h    | _      | INT1IP2    | INT1IP1    | INT1IP0    | _      | NVMIP2     | NVMIP1     | NVMIP0     | _     | ECCSBEIP2  | ECCSBEIP1  | ECCSBEIP0  | _     | U1TXIP2    | U1TXIP1    | U1TXIP0    |

| IPC4     | 848h    | _      | CNCIP2     | CNCIP1     | CNCIP0     | _      | DMA2IP2    | DMA2IP1    | DMA2IP0    | _     | MI2C1IP2   | MI2C1IP1   | MI2C1IP0   | _     | SI2C1IP2   | SI2C1IP1   | SI2C1IP0   |

| IPC5     | 84Ah    | _      | CCP2IP2    | CCP2IP1    | CCP2IP0    | _      | _          | _          | _          | _     | DMA3IP2    | DMA3IP1    | DMA3IP20   | _     | INT2IP2    | INT2IP1    | INT2IP0    |

| IPC6     | 84Ch    | _      | U2RXIP2    | U2RXIP1    | U2RXIP0    | _      | INT3IP2    | INT3IP1    | INT3IP0    | _     | C1IP2      | C1IP1      | C1IP0      | _     | CCT2IP2    | CCT2IP1    | CCT2IP0    |

| IPC7     | 84Eh    | _      | C1RXIP2    | C1RXIP1    | C1RXIP0    | _      | SPI2TXIP2  | SPI2TXIP1  | SPI2TXIP0  | _     | SPI2RXIP2  | SPI2RXIP1  | SPI2RXIP0  | _     | U2TXIP2    | U2TXIP1    | U2TXIP0    |

| IPC8     | 850h    | _      | CCP3IP2    | CCP3IP1    | CCP3IP0    | _      | -          | _          | _          | _     | _          | _          | _          | _     | _          | _          | _          |

| IPC9     | 852h    | _      | _          | _          | _          | _      | MI2C2IP2   | MI2C2IP1   | MI2C2IP0   | _     | SI2C2IP2   | SI2C2IP1   | SI2C2IP0   | _     | CCT3IP2    | CCT3IP1    | CCT3IP0    |

| IPC10    | 854h    | _      | CCP5IP2    | CCP5IP1    | CCP5IP0    | _      | _          | _          | _          | _     | CCT4IP2    | CCT4IP1    | CCT4IP0    | _     | CCP4IP2    | CCP4IP1    | CCP4IP0    |

| IPC11    | 856h    | _      | CCT6IP2    | CCT6IP1    | CCT6IP0    | _      | CCP6IP2    | CCP6IP1    | CCP6IP0    | _     | DMTIP2     | DMTIP1     | DMTIP0     | _     | CCT5IP2    | CCT5IP1    | CCT5IP0    |

| IPC12    | 858h    | _      | CRCIP2     | CRCIP1     | CRCIP0     | _      | U2EIP2     | U2EIP1     | U2EIP0     | _     | U1EIP2     | U1EIP1     | U1EIP0     | _     | QEI1IP2    | QEI1IP1    | QEI1IP0    |

| IPC13    | 85Ah    | _      | _          | _          | _          | _      | QEI2IP2    | QEI2IP1    | QEI2IP0    | _     | _          | _          | _          | _     | C1TXIP2    | C1TXIP1    | C1TXIP0    |

| IPC14    | 85Ch    | _      | SPI3RXIP2  | SPI3RXIP1  | SPI3RXIP0  | _      | U3TXIP2    | U3TXIP1    | U3TXIP1    | _     | U3RXIP2    | U3RXIP1    | U3RXIP0    | _     | U3EIP2     | U3EIP1     | U3EIP0     |

| IPC15    | 85Eh    | _      | PTGSTEPIP2 | PTGSTEPIP1 | PTGSTEPIP0 | _      | JTAGIP2    | JTAGIP1    | JTAGIP0    | _     | ICDIP2     | ICDIP1     | ICDIP0     | _     | SPI3TXIP2  | SPI3TXIP1  | SPI3TXIP0  |

| IPC16    | 860h    | _      | PWM1IP2    | PWM1IP1    | PWM1IP0    | _      | _          | _          | _          | _     | I2C2BCIP2  | I2C2BCIP1  | I2C2BCIP0  | _     | I2C1BCIP2  | I2C1BCIP1  | I2C1BCIP0  |

| IPC17    | 862h    | _      | PWM5IP2    | PWM5IP1    | PWM5IP0    | _      | PWM4IP2    | PWM4IP1    | PWM4IP0    | _     | PWM3IP2    | PWM3IP1    | PWM3IP0    | _     | PWM2IP2    | PWM2IP1    | PWM2IP0    |

| IPC18    | 864h    | _      | CNDIP2     | CNDIP1     | CNDIP0     | _      | PWM8IP2    | PWM8IP1    | PWM8IP0    | _     | PWM7IP2    | PWM7IP1    | PWM7IP0    | _     | PWM6IP2    | PWM6IP1    | PWM6IP0    |

| IPC19    | 866h    | _      | CMP3IP2    | CMP3IP1    | CMP3IP0    | _      | CMP2IP2    | CMP2IP1    | CMP2IP0    | _     | CMP1IP2    | CMP1IP1    | CMP1IP0    | _     | CNEIP2     | CNEIP1     | CNEIP0     |

| IPC20    | 868h    | _      | PTG1IP2    | PTG1IP1    | PTG1IP0    | _      | PTG0IP2    | PTG0IP1    | PTG0IP0    | _     | PTGWDTIP2  | PTGWDTIP1  | PTGWDTIP0  | —     | —          | —          | _          |

| IPC21    | 86Ah    | _      | SENT1EIP2  | SENT1EIP1  | SENT1EIP0  | _      | SENT1IP2   | SENT1IP1   | SENT1IP0   | _     | PTG3IP2    | PTG3IP1    | PTG3IP0    | —     | PTG2IP2    | PTG2IP1    | PTG2IP0    |

| IPC22    | 86Ch    | _      | ADCAN0IP2  | ADCAN0IP1  | ADCAN0IP0  | _      | ADCIP2     | ADCIP1     | ADCIP0     | _     | SENT2EIP2  | SENT2EIP1  | SENT2EIP0  | _     | SENT2IP2   | SENT2IP1   | SENT2IP0   |

| IPC23    | 86Eh    | _      | ADCAN4IP2  | ADCAN4IP1  | ADCAN4IP0  |        | ADCAN3IP2  | ADCAN3IP1  | ADCAN3IP0  |       | ADCAN2IP2  | ADCAN2IP1  | ADCAN2IP0  | _     | ADCAN1IP2  | ADCAN1IP1  | ADCAN1IP0  |

| IPC24    | 870h    | _      | ADCAN8IP2  | ADCAN8IP1  | ADCAN8IP0  |        | ADCAN7IP2  | ADCAN7IP1  | ADCAN7IP0  |       | ADCAN6IP2  | ADCAN6IP1  | ADCAN6IP0  | _     | ADCAN5IP2  | ADCAN5IP1  | ADCAN5IP0  |

| IPC25    | 872h    | —      | ADCAN12IP2 | ADCAN12IP1 | ADCAN12IP0 |        | ADCAN11IP2 | ADCAN11IP1 | ADCAN11IP0 |       | ADCAN10IP2 | ADCAN10IP1 | ADCAN10IP0 | _     | ADCAN9IP2  | ADCAN9IP1  | ADCAN9IP0  |

| IPC26    | 874h    | -      | ADCAN16IP2 | ADCAN16IP2 | ADCAN16IP2 |        | ADCAN15IP2 | ADCAN15IP1 | ADCAN15IP0 |       | ADCAN14IP2 | ADCAN14IP1 | ADCAN14IP0 | _     | ADCAN13IP2 | ADCAN13IP1 | ADCAN13IPC |

| IPC27    | 876h    | -      | ADCAN20IP2 | ADCAN20IP1 | ADCAN20IP0 |        | ADCAN19IP2 | ADCAN19IP1 | ADCAN19IP0 |       | ADCAN18IP2 | ADCAN18IP1 | ADCAN18IP0 | _     | ADCAN17IP2 | ADCAN17IP1 | ADCAN17IPC |

| IPC28    | 878h    | -      | ADFLTIP2   | ADFLTIP1   | ADFLTIP0   |        | ADCAN23IP2 | ADCAN23IP1 | ADCAN22IP0 |       | ADCAN22IP2 | ADCAN22IP1 | ADCAN22IP0 | _     | ADCAN21IP2 | ADCAN21IP1 | ADCAN21IPC |

| IPC29    | 87Ah    | -      | ADCMP3IP2  | ADCMP3IP1  | ADCMP3IP0  |        | ADCMP2IP2  | ADCMP2IP1  | ADCMP2IP0  |       | ADCMP1IP2  | ADCMP1IP1  | ADCMP1IP0  | _     | ADCMP0IP2  | ADCMP0IP1  | ADCMP0IP0  |

| IPC30    | 87Ch    | -      | ADFLTR3IP2 | ADFLTR3IP1 | ADFLTR3IP0 |        | ADFLTR2IP2 | ADFLTR2IP1 | ADFLTR2IP0 |       | ADFLTR1IP2 | ADFLTR1IP1 | ADFLTR1IP0 | _     | ADFLTR0IP2 | ADFLTR0IP1 | ADFLTR0IP0 |

| IPC31    | 87Eh    | _      | SPI2GIP0   | SPI2GIP1   | SPI2GIP0   | _      | SPI1GIP2   | SPI1GIP1   | SPI1GIP0   | _     | CLC2PIP2   | CLC2PIP1   | CLC2PIP0   | _     | CLC1PIP2   | CLC1PIP1   | CLC1PIP0   |

| IPC32    | 880h    | _      | _          | _          | _          | _      | _          | —          | —          | _     | —          | —          | _          | _     | SPI3GIP2   | SPI3GIP1   | SPI3GIP0   |

| IPC33    | 882h    | _      | _          | _          | _          | _      | _          | —          | _          | _     | —          | _          | _          | _     | —          | —          | —          |

| IPC34    | 884h    | _      | _          | _          | _          | _      | _          | _          | —          | _     | _          | —          | _          | _     | —          | —          | _          |

## 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 7.3.1 KEY RESOURCES

- "Interrupts" (DS70000600) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 7.4 Interrupt Control and Status Registers

The dsPIC33CK256MP508 family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.0.1 INTCON1 through INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior, contains the Global Interrupt Enable bit (GIE) and the Alternate Interrupt Vector Table Enable bit (AIVTEN).

INTCON3 contains the status flags for the Auxiliary PLL and DO stack overflow status trap sources.

The INTCON4 register contains the Software Generated Hard Trap Status bit (SGHT).

## 7.4.0.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.4.0.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

## 7.4.0.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of seven priority levels.

## 7.4.0.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<7:0>) and Interrupt Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP<2:0> bits in the first position of IPC0 (IPC0<2:0>).

#### 7.4.0.6 Status/Control Registers

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to "dsPIC33E Enhanced CPU" (DS70005158) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

## **REGISTER 7-7:** INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0             | U-0                                                                                  | R-0                                                   | U-0             | R-0              | R-0               | R-0                | R-0             |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|------------------|-------------------|--------------------|-----------------|--|--|--|--|

| _               | —                                                                                    | VHOLD                                                 | —               | ILR3             | ILR2              | ILR1               | ILR0            |  |  |  |  |

| bit 15          |                                                                                      |                                                       |                 |                  |                   |                    | bit 8           |  |  |  |  |

|                 |                                                                                      |                                                       |                 |                  |                   |                    |                 |  |  |  |  |

| R-0             | R-0                                                                                  | R-0                                                   | R-0             | R-0              | R-0               | R-0                | R-0             |  |  |  |  |

| VECNUM7         | VECNUM6                                                                              | VECNUM5                                               | VECNUM4         | VECNUM3          | VECNUM2           | VECNUM1            | VECNUM0         |  |  |  |  |

| bit 7           |                                                                                      |                                                       |                 |                  |                   |                    | bit (           |  |  |  |  |

| Legend:         |                                                                                      |                                                       |                 |                  |                   |                    |                 |  |  |  |  |

| R = Readable    | bit                                                                                  | W = Writable                                          | bit             | U = Unimpler     | mented bit, read  | l as '0'           |                 |  |  |  |  |

| -n = Value at F | POR                                                                                  | '1' = Bit is set                                      |                 | '0' = Bit is cle | ared              | x = Bit is unkr    | nown            |  |  |  |  |

|                 |                                                                                      |                                                       |                 |                  |                   |                    |                 |  |  |  |  |

| bit 15-14       | •                                                                                    | ted: Read as '                                        |                 |                  |                   |                    |                 |  |  |  |  |

| bit 13          | VHOLD: Vect                                                                          | tor Number Ca                                         | oture Enable b  | oit              |                   |                    |                 |  |  |  |  |

|                 |                                                                                      |                                                       | l current value | of vector numb   | per encoding tree | e (i.e., highest p | riority pending |  |  |  |  |

|                 | interrupt)                                                                           |                                                       | nto VECNII IM<  | 7·0> at Interru  | pt Acknowledge    | and retained u     | Intil nevt IACk |  |  |  |  |

| bit 12          |                                                                                      | ted: Read as '                                        |                 |                  | ipt Acknowledge   |                    |                 |  |  |  |  |

| bit 11-8        | -                                                                                    | ew CPU Interru                                        |                 | ol bite          |                   |                    |                 |  |  |  |  |

| bit 11-0        |                                                                                      | Interrupt Priorit                                     | •               |                  |                   |                    |                 |  |  |  |  |

|                 |                                                                                      | interrupt i nom                                       |                 |                  |                   |                    |                 |  |  |  |  |

|                 | 0001 = CPU Interrupt Priority Level is 1<br>0000 = CPU Interrupt Priority Level is 0 |                                                       |                 |                  |                   |                    |                 |  |  |  |  |

|                 |                                                                                      | •                                                     | 5               |                  |                   |                    |                 |  |  |  |  |

| bit 7-0         |                                                                                      | 0>: Vector Nun                                        |                 | g Interrupt bits | 6                 |                    |                 |  |  |  |  |

|                 | 11111111 = 255, Reserved; do not use                                                 |                                                       |                 |                  |                   |                    |                 |  |  |  |  |

|                 | <br>00001001 = 9, IC1 – Input Capture 1                                              |                                                       |                 |                  |                   |                    |                 |  |  |  |  |

|                 | 00001000 = 8, INTO – External Interrupt 0                                            |                                                       |                 |                  |                   |                    |                 |  |  |  |  |

|                 | 00000111 = 7, Reserved; do not use<br>00000110 = 6, Generic soft error trap          |                                                       |                 |                  |                   |                    |                 |  |  |  |  |

|                 |                                                                                      | <ol> <li>Generic soft</li> <li>Reserved; d</li> </ol> |                 |                  |                   |                    |                 |  |  |  |  |

|                 |                                                                                      | 4, Math error tr                                      |                 |                  |                   |                    |                 |  |  |  |  |

|                 | 00000011 =                                                                           | 3, Stack error t                                      | rap             |                  |                   |                    |                 |  |  |  |  |

|                 |                                                                                      | 2, Generic har                                        |                 |                  |                   |                    |                 |  |  |  |  |

|                 |                                                                                      | 1, Address erro<br>0, Oscillator fai                  |                 |                  |                   |                    |                 |  |  |  |  |

|                 | - 00000000 -                                                                         | o, Oscillator Idi                                     | iuap            |                  |                   |                    |                 |  |  |  |  |

## 8.4 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the dsPIC33CK256MP508 family devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State. Five control registers are associated with the Change Notification (CN) functionality of each I/O port. To enable the Change Notification feature for the port, the ON bit (CNCONx<15>) must be set.

The CNEN0x and CNEN1x registers contain the CN interrupt enable control bits for each of the input pins. The setting of these bits enables a CN interrupt for the corresponding pins. Also, these bits, in combination with the CNSTYLE bit (CNCONx<11>), define a type of transition when the interrupt is generated. Possible CN event options are listed in Table 8-3.

#### TABLE 8-3: CHANGE NOTIFICATION EVENT OPTIONS

| CNSTYLE Bit<br>(CNCONx<11>) | CNEN1x<br>Bit      | CNEN0x<br>Bit | Change Notification Event<br>Description                                              |

|-----------------------------|--------------------|---------------|---------------------------------------------------------------------------------------|

| 0                           | Does not<br>matter | 0             | Disabled                                                                              |

| 0                           | Does not<br>matter | 1             | Detects a mismatch between<br>the last read state and the<br>current state of the pin |

| 1                           | 0                  | 0             | Disabled                                                                              |

| 1                           | 0                  | 1             | Detects a positive transition<br>only (from '0' to '1')                               |

| 1                           | 1                  | 0             | Detects a negative transition<br>only (from '1' to '0')                               |

| 1                           | 1                  | 1             | Detects both positive and<br>negative transitions                                     |

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. In addition to the CNSTATx register, the CNFx register is implemented for each port. This register contains flags for Change Notification events. These flags are set if the valid transition edge, selected in the CNEN0x and CNEN1x registers, is detected. CNFx stores the occurrence of the event. CNFx bits must be cleared in software to get the next Change Notification interrupt. The CN interrupt is generated only for the I/Os configured as inputs (corresponding TRISx bits must be set).

| Note: | Pull-ups and pull-downs on Input Change  |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | Notification pins should always be       |  |  |  |  |  |  |  |  |  |

|       | disabled when the port pin is configured |  |  |  |  |  |  |  |  |  |

|       | as a digital output.                     |  |  |  |  |  |  |  |  |  |

## 8.5 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 8.5.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions.

## 8.5.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. One example includes I<sup>2</sup>C modules. A similar requirement excludes all modules with analog inputs, such as the A/D Converter (ADC)

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

# TABLE 8-12: PORTE REGISTER SUMMARY

| Register | Bit 15 | Bit 14      | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------|-------------|--------|--------|---------|--------|-------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| ANSLE    | _      | —           | —      | —      | —       | _      | —     | _        | _     | —     | —     | _     | —     | _     | _     | _     |

| TRISE    |        | TRISE<15:0> |        |        |         |        |       |          |       |       |       |       |       |       |       |       |

| PORTE    |        | RE<15:0>    |        |        |         |        |       |          |       |       |       |       |       |       |       |       |

| LATE     |        | LATE<15:0>  |        |        |         |        |       |          |       |       |       |       |       |       |       |       |

| ODCE     |        | ODCE<15:0>  |        |        |         |        |       |          |       |       |       |       |       |       |       |       |

| CNPUE    |        | CNPUE<15:0> |        |        |         |        |       |          |       |       |       |       |       |       |       |       |

| CNPDE    |        |             |        |        |         |        | (     | CNPDE<1  | 5:0>  |       |       |       |       |       |       |       |

| CNCONE   | ON     | —           | —      | —      | CNSTYLE | _      | _     | _        | _     | —     | _     | _     | _     | _     | _     | _     |

| CNEN0E   |        |             |        |        |         |        | C     | NEN0E<1  | 5:0>  |       |       |       |       |       |       |       |

| CNSTATE  |        |             |        |        |         |        | С     | NSTATE<1 | 5:0>  |       |       |       |       |       |       |       |

| CNEN1E   |        |             |        |        |         |        | C     | NEN1E<1  | 5:0>  |       |       |       |       |       |       |       |

| CNFE     |        |             |        |        |         |        |       | CNFE<15  | 0>    |       |       |       |       |       |       |       |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI15R7 | PCI15R6 | PCI15R5 | PCI15R4 | PCI15R3 | PCI15R2 | PCI15R1 | PCI15R0 |

| bit 15  |         |         |         |         |         | •       | bit 8   |

|         |         |         |         |         |         |         |         |

| R/W-0   |

| PCI14R7 | PCI14R6 | PCI14R5 | PCI14R4 | PCI14R3 | PCI14R2 | PCI14R1 | PCI14R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

## REGISTER 8-47: RPINR43: PERIPHERAL PIN SELECT INPUT REGISTER 43

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-8 | PCI15R<7:0>: Assign PWM Input 15 (PCI15) to the Corresponding RPn Pin bits |

|----------|----------------------------------------------------------------------------|

|          | See Table 8-4.                                                             |

| bit 7-0  | PCI14R<7:0>: Assign PWM Input 14 (PCI14) to the Corresponding RPn Pin bits |

|          | See Table 8-4.                                                             |

## REGISTER 8-48: RPINR44: PERIPHERAL PIN SELECT INPUT REGISTER 44

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SENT1R7 | SENT1R6 | SENT1R5 | SENT1R4 | SENT1R3 | SENT1R2 | SENT1R1 | SENT1R0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PCI16R7 | PCI16R6 | PCI16R5 | PCI16R4 | PCI16R3 | PCI16R2 | PCI16R1 | PCI16R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 SENT1R<7:0>: Assign SENT1 Input (SENT1) to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0 **PCI16<7:0>:** Assign PWM Input 16 (PCI16) to the Corresponding RPn Pin bits See Table 8-4.

**—**

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

|        | _   | RP181R5 <sup>(1)</sup> | RP181R4 <sup>(1)</sup> | RP181R3 <sup>(1)</sup> | RP181R2 <sup>(1)</sup> | RP181R1 <sup>(1)</sup> | RP181R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _     | —   | RP180R5 <sup>(1)</sup> | RP180R4 <sup>(1)</sup> | RP180R3 <sup>(1)</sup> | RP180R2 <sup>(1)</sup> | RP180R1 <sup>(1)</sup> | RP180R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                                                                      |                      |                    |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-14 Unimplemented: Read as '0'

| bit 13-8 | <b>RP181R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP181 Output Pin bits |

|----------|-------------------------------------------------------------------------------------------|

|          | (see Table 8-7 for peripheral function numbers)                                           |

| bit 7-6  | Unimplemented: Read as '0'                                                                |

bit 5-0 **RP180R<5:0>:** Peripheral Output Function is Assigned to RP180 Output Pin bits (see Table 8-7 for peripheral function numbers)

Note 1: These are virtual output ports.

### REGISTER 9-7: APLLFBD1: APLL FEEDBACK DIVIDER REGISTER

| U-0    | U-0 | U-0 | U-0 | r-0 | r-0 | r-0 | r-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| R/W-1          | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-1 | R/W-1 | R/W-0 |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|

| APLLFBDIV<7:0> |       |       |       |       |       |       |       |  |

| bit 7          |       |       |       |       |       |       | bit 0 |  |

| Legend:           | r = Reserved bit |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-12 Unimplemented: Read as '0'

bit 11-8 Reserved: Maintain as '0'

- bit 7-0 APLLFBDIV<7:0>: APLL Feedback Divider bits

- 11111111 = Reserved

- ... 11001000 **= 200** maximum<sup>(1)</sup>

... 10010110 = **150 (default)**

... 00010000 = 16 minimum<sup>(1)</sup>

- ... 00000010 = Reserved 00000001 = Reserved 00000000 = Reserved

- **Note 1:** The allowed range is 16-200 (decimal). The rest of the values are reserved and should be avoided. The power-on default feedback divider is 150 (decimal) with an 8 MHz FRC input clock; the VCO frequency is 1.2 GHz.

| R/W-0        | U-0                                                                                                                                                                     | R/W-0                                                                                                                                                        | R/W-0             | R/W-0             | U-0            | R/W-0, HC         | R-0, HSC       |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|----------------|-------------------|----------------|--|--|--|--|

| ROEN         |                                                                                                                                                                         | ROSIDL                                                                                                                                                       | ROOUT             | ROSLP             | _              | ROSWEN            | ROACTIV        |  |  |  |  |

| bit 15       |                                                                                                                                                                         |                                                                                                                                                              |                   | -                 |                |                   | bit 8          |  |  |  |  |

|              |                                                                                                                                                                         |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

| U-0          | U-0                                                                                                                                                                     | U-0                                                                                                                                                          | U-0               | R/W-0             | R/W-0          | R/W-0             | R/W-0          |  |  |  |  |

|              | _                                                                                                                                                                       |                                                                                                                                                              |                   | ROSEL3            | ROSEL2         | ROSEL1            | ROSEL0         |  |  |  |  |

| bit 7        |                                                                                                                                                                         |                                                                                                                                                              |                   |                   |                |                   | bit (          |  |  |  |  |

|              |                                                                                                                                                                         |                                                                                                                                                              | <u> </u>          |                   | 0 11 11 10     |                   |                |  |  |  |  |

| Legend:      | 1.1.1                                                                                                                                                                   | HC = Hardwar                                                                                                                                                 |                   | HSC = Hardw       |                |                   |                |  |  |  |  |

| R = Readab   |                                                                                                                                                                         | W = Writable I                                                                                                                                               | DIT               | U = Unimpler      |                |                   |                |  |  |  |  |

| -n = Value a | at POR                                                                                                                                                                  | '1' = Bit is set                                                                                                                                             |                   | '0' = Bit is clea | ared           | x = Bit is unkr   | nown           |  |  |  |  |

| bit 15       | ROEN: Re                                                                                                                                                                | eference Clock Er                                                                                                                                            | able bit          |                   |                |                   |                |  |  |  |  |

|              |                                                                                                                                                                         | ence Oscillator is                                                                                                                                           |                   | REFCLKO pin       |                |                   |                |  |  |  |  |

|              |                                                                                                                                                                         | ence Oscillator is                                                                                                                                           |                   | ·· • -··• p···    |                |                   |                |  |  |  |  |

| bit 14       | Unimplem                                                                                                                                                                | nented: Read as                                                                                                                                              | '0'               |                   |                |                   |                |  |  |  |  |

| bit 13       | ROSIDL: F                                                                                                                                                               | Reference Clock                                                                                                                                              | Stop in Idle bit  |                   |                |                   |                |  |  |  |  |

|              | 1 = Refere                                                                                                                                                              | ence Oscillator co                                                                                                                                           | ntinues to run ir | n Idle mode       |                |                   |                |  |  |  |  |

|              | 0 = Refere                                                                                                                                                              | ence Oscillator is                                                                                                                                           | disabled in Idle  | mode              |                |                   |                |  |  |  |  |

| bit 12       | ROOUT: R                                                                                                                                                                | Reference Clock (                                                                                                                                            | Dutput Enable b   | bit               |                |                   |                |  |  |  |  |

|              |                                                                                                                                                                         | <ul> <li>1 = Reference clock external output is enabled and available on the REFCLKO pin</li> <li>0 = Reference clock external output is disabled</li> </ul> |                   |                   |                |                   |                |  |  |  |  |

|              |                                                                                                                                                                         |                                                                                                                                                              | •                 |                   |                |                   |                |  |  |  |  |

| bit 11       |                                                                                                                                                                         | Reference Clock S                                                                                                                                            | • •               |                   |                |                   |                |  |  |  |  |

|              |                                                                                                                                                                         | ence Oscillator co<br>ence Oscillator is                                                                                                                     |                   | •                 |                |                   |                |  |  |  |  |

| bit 10       |                                                                                                                                                                         | nented: Read as                                                                                                                                              |                   | p modes           |                |                   |                |  |  |  |  |

| bit 9        | -                                                                                                                                                                       | Reference Clock                                                                                                                                              |                   | a hit             |                |                   |                |  |  |  |  |

|              |                                                                                                                                                                         |                                                                                                                                                              | •                 |                   | NVx) is reque  | sted or is in pro | ogress (set in |  |  |  |  |

|              | <ul> <li>1 = Clock divider change (requested by changes to RODIVx) is requested or is in progress (set in<br/>software, cleared by hardware upon completion)</li> </ul> |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              | 0 = Clock divider change has completed or is not pending                                                                                                                |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

| bit 8        |                                                                                                                                                                         | Reference Clock                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              |                                                                                                                                                                         | ence clock is activ<br>ence clock is stop                                                                                                                    |                   |                   | ation may be s | afely changed     |                |  |  |  |  |

| bit 7-4      |                                                                                                                                                                         | nented: Read as                                                                                                                                              |                   |                   | ation may be 3 | alory changed     |                |  |  |  |  |

| bit 3-0      | -                                                                                                                                                                       | :0>: Reference C                                                                                                                                             |                   | lect bits         |                |                   |                |  |  |  |  |

|              | 1111 = Re                                                                                                                                                               |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              |                                                                                                                                                                         |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              | 1000 = Reserved                                                                                                                                                         |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              | 0111 = REFI pin                                                                                                                                                         |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              | 0110 = Fv<br>0101 = BF                                                                                                                                                  |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              | 0101 - BF<br>0100 = LP                                                                                                                                                  |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              | 0011 = FR                                                                                                                                                               |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              | 0011 11                                                                                                                                                                 |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

|              | 0010 <b>= Pr</b> i                                                                                                                                                      | imary Oscillator                                                                                                                                             |                   |                   |                |                   |                |  |  |  |  |

|              | 0010 = Pri<br>0001 = Pe                                                                                                                                                 |                                                                                                                                                              |                   |                   |                |                   |                |  |  |  |  |

## REGISTER 9-10: REFOCONL: REFERENCE CLOCK CONTROL LOW REGISTER

NOTES:

## **REGISTER 12-10: PWMEVTy: PWM EVENT OUTPUT CONTROL REGISTER y**<sup>(5)</sup> **(CONTINUED)**

bit 2-0 EVTyPGS<2:0>: PWM Event Source Selection bits<sup>(2)</sup> 111 = PWM Generator 8 110 = PWM Generator 7 ... 000 = PWM Generator 1

- **Note 1:** The event signal is stretched using peripheral\_clk because different PWM Generators may be operating from different clock sources.

- 2: No event will be produced if the selected PWM Generator is not present.

- 3: This is the PWM Generator output signal prior to output mode logic and any output override logic.

- **4:** This signal should be the PGx\_clk domain signal prior to any synchronization into the system clock domain.

- 5: 'y' denotes a common instance (A-F).

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| —            | _   | —   | —   | _   | —   | —   | —   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

|              |     |     |     |     |     |     |     |  |

| R/W-0       | R/W-1   | R/W-1   | U-0 | U-0 | U-0 | U-0 | U-0 |

|-------------|---------|---------|-----|-----|-----|-----|-----|

| FORM        | SHRRES1 | SHRRES0 | —   | —   | —   | —   | —   |

| bit 7 bit 0 |         |         |     |     |     |     |     |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                             |

|----------|--------------------------------------------------------|

| bit 7    | FORM: Fractional Data Output Format bit                |

|          | 1 = Fractional                                         |

|          | 0 = Integer                                            |

| bit 6-5  | SHRRES<1:0>: Shared ADC Core Resolution Selection bits |

|          | 11 = 12-bit resolution                                 |

|          | 10 = 10-bit resolution                                 |

|          | 01 = 8-bit resolution                                  |

|          | 00 = 6-bit resolution                                  |

| bit 4-0  | Unimplemented: Read as '0'                             |

| R/W-0               | U-0                                                                                                                                                       | U-0                                                                           | U-0            | R/W-0              | R/W-0               | R/W-0          | U-0   |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------|--------------------|---------------------|----------------|-------|--|

| SLOPEN              | —                                                                                                                                                         | —                                                                             | —              | HME <sup>(1)</sup> | TWME <sup>(2)</sup> | PSE            | —     |  |

| bit 15              |                                                                                                                                                           |                                                                               |                |                    |                     |                | bit 8 |  |

|                     |                                                                                                                                                           |                                                                               |                |                    |                     |                |       |  |

| U-0                 | U-0                                                                                                                                                       | U-0                                                                           | U-0            | U-0                | U-0                 | U-0            | U-0   |  |

| —                   |                                                                                                                                                           | —                                                                             | —              | —                  | —                   | —              | —     |  |

| bit 7               |                                                                                                                                                           |                                                                               |                |                    |                     |                | bit 0 |  |

|                     |                                                                                                                                                           |                                                                               |                |                    |                     |                |       |  |

| Legend:             |                                                                                                                                                           |                                                                               |                |                    |                     |                |       |  |

| R = Readab          | le bit                                                                                                                                                    | W = Writable bit                                                              |                | U = Unimpler       | mented bit, read    | as '0'         |       |  |

| -n = Value a        | t POR                                                                                                                                                     | '1' = Bit is set                                                              |                | '0' = Bit is cle   | eared               |                |       |  |

| bit 15<br>bit 14-12 | 1 = Enables<br>0 = Disables                                                                                                                               | ope Function Ena<br>slope function<br>slope function; sl<br>nted: Read as '0' |                | ator is disabled   | to reduce powe      | er consumption |       |  |

| bit 11              | HME: Hysteretic Mode Enable bit <sup>(1)</sup><br>1 = Enables Hysteretic mode for DACx<br>0 = Disables Hysteretic mode for DACx                           |                                                                               |                |                    |                     |                |       |  |

| bit 10              | 1 = Enables                                                                                                                                               | ngle Wave Mode I<br>Triangle Wave m<br>Triangle Wave m                        | ode for DACx   |                    |                     |                |       |  |

| bit 9               | <ul> <li>PSE: Positive Slope Mode Enable bit</li> <li>1 = Slope mode is positive (increasing)</li> <li>0 = Slope mode is negative (decreasing)</li> </ul> |                                                                               |                |                    |                     |                |       |  |

| bit 8-0             | Unimplemer                                                                                                                                                | nted: Read as '0'                                                             |                |                    |                     |                |       |  |

| Note 1: ⊢           | IME mode reau                                                                                                                                             | ires the user to d                                                            | isable the slo | pe function (SL    | OPEN = 0).          |                |       |  |

## REGISTER 14-8: SLPxCONH: DACx SLOPE CONTROL HIGH REGISTER

- **Note 1:** HME mode requires the user to disable the slope function (SLOPEN = 0).

- 2: TWME mode requires the user to enable the slope function (SLOPEN = 1).

## REGISTER 15-13: INTXxHLDL: INTERVAL x TIMER HOLD REGISTER LOW

|                                                                      |       | '1' = Bit is set | it.   | '0' = Bit is cleared |       | x = Bit is unkr | nown  |

|----------------------------------------------------------------------|-------|------------------|-------|----------------------|-------|-----------------|-------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                      |       |                 |       |

| Legend:                                                              |       |                  |       |                      |       |                 |       |

|                                                                      |       |                  |       |                      |       |                 |       |

| bit 7                                                                |       |                  |       |                      |       |                 | bit 0 |

|                                                                      |       |                  | INTH  | LD<7:0>              |       |                 |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0 | R/W-0           | R/W-0 |

| bit 15                                                               |       |                  |       |                      |       |                 | bit 8 |

| L:1 4 F                                                              |       |                  |       | D 13.02              |       |                 | L:1 0 |

|                                                                      |       |                  | INTHI | _D<15:8>             |       |                 |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0 | R/W-0           | R/W-0 |

bit 15-0 INTHLD<15:0>: Low Word Used to Form 32-Bit Interval Timer Hold Register (INTxHLD) bits

## REGISTER 15-14: INTXxHLDH: INTERVAL x TIMER HOLD REGISTER HIGH

| R/W-0                              | R/W-0 | R/W-0            | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|------------------|-------|----------------------------------------|-------|-------|-------|

|                                    |       |                  | INTHL | .D<31:24>                              |       |       |       |

| bit 15                             |       |                  |       |                                        |       |       | bit 8 |

|                                    |       |                  |       |                                        |       |       |       |

| R/W-0                              | R/W-0 | R/W-0            | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |                  | INTHL | .D<23:16>                              |       |       |       |

| bit 7                              |       |                  |       |                                        |       |       | bit 0 |

|                                    |       |                  |       |                                        |       |       |       |

| Legend:                            |       |                  |       |                                        |       |       |       |

| R = Readable bit W = Writable bit  |       |                  | it    | U = Unimplemented bit, read as '0'     |       |       |       |

| -n = Value at POR '1' = Bit is set |       | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknow |       |       | nown  |

|                                    |       |                  |       |                                        |       |       |       |

bit 15-0 INTHLD<31:16>: High Word Used to Form 32-Bit Interval Timer Hold Register (INTxHLD) bits

## TABLE 31-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field                                                                                                                             | Description                                                                                                                                                                                                                                                          |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Wm*Wm       Multiplicand and Multiplier Working register pair for Square instructions ∈         {W4 * W4,W5 * W5,W6 * W6,W7 * W7} |                                                                                                                                                                                                                                                                      |  |  |

| Wm*Wn                                                                                                                             | Multiplicand and Multiplier Working register pair for DSP instructions $\in$ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                       |  |  |

| Wn                                                                                                                                | One of 16 Working registers ∈ {W0W15}                                                                                                                                                                                                                                |  |  |