Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 39                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 19x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-TQFP                                                                           |

| Supplier Device Package    | 48-TQFP (7x7)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck128mp205t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.6 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to a certain frequency (see Section 9.0 "Oscillator with High-Frequency PLL") to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

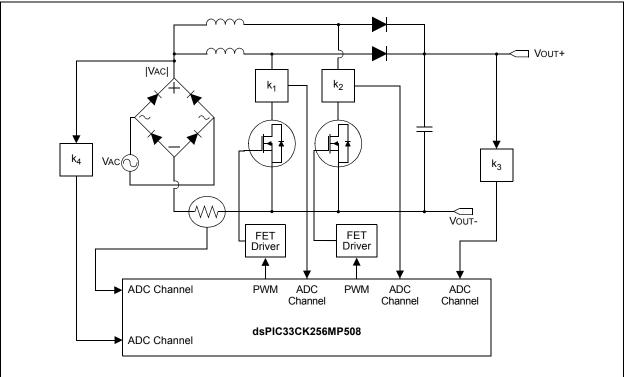

## FIGURE 2-4: INTERLEAVED PFC

#### 2.8 Targeted Applications

- Power Factor Correction (PFC):

- Interleaved PFC

- Critical Conduction PFC

- Bridgeless PFC

- DC/DC Converters:

- Buck, Boost, Forward, Flyback, Push-Pull

- Half/Full-Bridge

- Phase-Shift Full-Bridge

- Resonant Converters

- · DC/AC:

- Half/Full-Bridge Inverter

- Resonant Inverter

- Motor Control

- BLDC

- PMSM

- SR

- ACIM

Examples of typical application connections are shown in Figure 2-4 through Figure 2-6.

| Register        | Address | All Resets                              | Register         | Address | All Resets                              | Register  | Address | All Resets                              |

|-----------------|---------|-----------------------------------------|------------------|---------|-----------------------------------------|-----------|---------|-----------------------------------------|

| PTG             |         |                                         | CCP1CON3H        | 95A     | 00000-00                                | CCP3PRL   | 9AC     | 1111111111111111111                     |

| PTGCST          | 900     | 00-00000x00                             | CCP1STATL        | 95C     | 000xx0000                               | CCP3PRH   | 9AE     | 111111111111111111                      |

| PTGCON          | 902     | 000000000000-000                        | CCP1STATH        | 95E     | 00000                                   | CCP3RAL   | 9B0     | 000000000000000000000000000000000000000 |

| PTGBTE          | 904     | *****                                   | CCP1TMRL         | 960     | 000000000000000000                      | CCP3RBL   | 9B4     | 000000000000000000000000000000000000000 |

| PTGBTEH         | 906     | 000000000000000000                      | CCP1TMRH         | 962     | 000000000000000000                      | CCP3BUFL  | 9B8     | 000000000000000000000000000000000000000 |

| PTGHOLD         | 908     | 000000000000000000                      | CCP1PRL          | 964     | 111111111111111111                      | CCP3BUFH  | 9BA     | 000000000000000000000000000000000000000 |

| <b>PTGT0LIM</b> | 90C     | 000000000000000000                      | CCP1PRH          | 966     | 111111111111111111                      | CCP4CON1L | 9BC     | 0000000000000000000000000000000000000   |

| PTGT1LIM        | 910     | 000000000000000000                      | CCP1RAL          | 968     | 000000000000000000                      | CCP4CON1H | 9BE     | 00000000000000                          |

| PTGSDLIM        | 914     | 000000000000000000000000000000000000000 | CCP1RBL          | 96C     | 000000000000000000                      | CCP4CON2L | 9C0     | 00-000000000                            |

| <b>PTGC0LIM</b> | 918     | 000000000000000000000000000000000000000 | CCP1BUFL         | 970     | 000000000000000000                      | CCP4CON2H | 9C2     | 100-00000                               |

| PTGC1LIM        | 91C     | 000000000000000000                      | CCP1BUFH         | 972     | 000000000000000000                      | CCP4CON3H | 9C6     | 00000-00                                |

| PTGADJ          | 920     | 000000000000000000                      | CCP2CON1L        | 974     | 000000000000000                         | CCP4STATL | 9C8     | 000xx0000                               |

| PTGL0           | 924     | 000000000000000000000000000000000000000 | CCP2CON1H        | 976     | 00000000000000                          | CCP4STATH | 9CA     | 00000                                   |

| PTGQPTR         | 928     | 00000                                   | CCP2CON2L        | 978     | 00-000000000                            | CCP4TMRL  | 9CC     | 000000000000000000000000000000000000000 |

| PTGQUE0         | 930     | ****                                    | CCP2CON2H        | 97A     | 0100-00000                              | CCP4TMRH  | 9CE     | 000000000000000000000000000000000000000 |

| PTGQUE1         | 932     | *****                                   | CCP2CON3H        | 97E     | 00000-00                                | CCP4PRL   | 9D0     | 111111111111111111                      |

| PTGQUE2         | 934     | ****                                    | CCP2STATL        | 980     | 000xx0000                               | CCP4PRH   | 9D2     | 1111111111111111111                     |

| PTGQUE3         | 936     | *****                                   | CCP2STATH        | 982     | 00000                                   | CCP4RAL   | 9D4     | 000000000000000000000000000000000000000 |

| PTGQUE4         | 938     | *****                                   | CCP2TMRL         | 984     | 000000000000000000                      | CCP4RBL   | 9D8     | 000000000000000000000000000000000000000 |

| PTGQUE5         | 93A     | *****                                   | CCP2TMRH         | 986     | 000000000000000000                      | CCP4BUFL  | 9DC     | 000000000000000000000000000000000000000 |

| PTGQUE6         | 93C     | *****                                   | CCP2PRL          | 988     | 111111111111111111                      | CCP4BUFH  | 9DE     | 000000000000000000000000000000000000000 |

| PTGQUE7         | 93E     | *****                                   | CCP2PRH          | 98A     | 111111111111111111                      | CCP5CON1L | 9E0     | 0000000000000000000000000000000000000   |

| PTGQUE8         | 940     | *****                                   | CCP2RAL          | 98C     | 000000000000000000                      | CCP5CON1H | 9E2     | 00000000000000                          |

| PTGQUE9         | 942     | *****                                   | CCP2RBL          | 990     | 000000000000000000                      | CCP5CON2L | 9E4     | 00-000000000                            |

| PTGQUE10        | 944     | *****                                   | CCP2BUFL         | 994     | 000000000000000000                      | CCP5CON2H | 9E6     | 100-00000                               |

| PTGQUE11        | 946     | *****                                   | CCP2BUFH         | 996     | 000000000000000000                      | CCP5CON3H | 9EA     | 00000-00                                |

| PTGQUE12        | 948     | *****                                   | CCP3CON1L        | 998     | 000000000000000                         | CCP5STATL | 9EC     | 000xx0000                               |

| PTGQUE13        | 94A     | *****                                   | CCP3CON1H        | 99A     | 00000000000000                          | CCP5STATH | 9EE     | 00000                                   |

| PTGQUE14        | 94C     | *****                                   | CCP3CON2L        | 99C     | 00-000000000                            | CCP5TMRL  | 9F0     | 000000000000000000000000000000000000000 |

| PTGQUE15        | 94E     | *****                                   | CCP3CON2H        | 99E     | 100-00000                               | CCP5TMRH  | 9F2     | 000000000000000000000000000000000000000 |

| CCP             | •       |                                         | CCP3CON3H        | 9A2     | 00000-00                                | CCP5PRL   | 9F4     | 111111111111111111                      |

| CCP1CON1L       | 950     | 000000000000000                         | CCP3STATL        | 9A4     | 000xx0000                               | CCP5PRH   | 9F6     | 111111111111111111                      |

| CCP1CON1H       | 952     | 00000000000000                          | <b>CCP3STATH</b> | 9A6     | 00000                                   | CCP5RAL   | 9F8     | 000000000000000000000000000000000000000 |

| CCP1CON2L       | 954     | 00-000000000                            | CCP3TMRL         | 9A8     | 000000000000000000                      | CCP5RBL   | 9FC     | 000000000000000000000000000000000000000 |

| CCP1CON2H       | 956     | 100-00000                               | <b>CCP3TMRH</b>  | 9AA     | 000000000000000000000000000000000000000 |           | •       |                                         |

#### TABLE 4-10: SFR BLOCK 900h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address values are in hexadecimal. Reset values are in binary.

# TABLE 8-1: PIN AND ANSELx AVAILABILITY

| Device              | Rx15 | Rx14 | Rx13 | Rx12 | Rx11 | Rx10 | Rx9 | Rx8 | Rx7 | Rx6 | Rx5 | Rx4 | Rx3 | Rx2 | Rx1 | Rx0 |

|---------------------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                     |      |      |      |      |      | POR  | ΓΑ  |     |     |     |     |     |     |     |     |     |

| dsPIC33XXXMP508/208 |      |      |      |      |      | _    |     |     | _   |     | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | _    | _    |      | _    | _    | _    | _   | _   | _   | _   | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP504/204 | _    | _    | _    | _    | _    | _    | _   | _   | _   | _   | _   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP503/203 | _    | _    |      |      |      | —    | _   | _   | —   | _   |     | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP502/202 | _    | _    |      |      |      | —    | _   | _   | —   | _   |     | Х   | Х   | Х   | Х   | Х   |

| ANSELA              |      |      |      | _    |      | —    | —   | —   | —   | _   |     | Х   | Х   | Х   | Х   | Х   |

|                     |      |      |      |      |      | POR  | ГВ  |     |     |     |     |     |     |     |     | -   |

| dsPIC33XXXMP508/208 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP504/204 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP503/203 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP502/202 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| ANSELB              | _    | _    | _    |      |      | _    | Х   | Х   | Х   | _   |     | Х   | Х   | Х   | Х   | Х   |

|                     |      |      |      |      |      | POR  | ГС  |     |     |     |     |     |     |     |     |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP504/204 |      |      | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP503/203 | —    | —    | —    | —    | _    | —    | —   | —   | —   | —   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP502/202 | —    | —    | —    | —    | _    | —    | —   | —   | —   | —   | _   | —   | —   | —   |     | —   |

| ANSELC              |      |      |      | —    | _    | —    | —   | _   | Х   | Х   | —   | —   | Х   | Х   | Х   | Х   |

|                     |      |      |      |      |      | POR  | TD  |     |     |     |     |     |     |     |     |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP504/204 | —    | —    | Х    | —    | —    | Х    | —   | Х   | —   | —   | —   | —   | —   | —   | Х   | —   |

| dsPIC33XXXMP503/203 | —    | —    | —    | —    | —    | —    | —   | —   | —   | —   | —   | —   | —   | —   | —   | —   |

| dsPIC33XXXMP502/202 | —    | —    | —    | —    | —    | —    | —   | —   | —   | —   | —   | —   | —   | —   | —   | —   |

| ANSELD              |      | —    | Х    |      | Х    | Х    | —   | —   | —   | —   | —   | —   |     | —   | —   | —   |

|                     |      |      |      |      | -    | POR  | ΓE  |     |     |     |     |     |     |     |     |     |

| dsPIC33XXXMP508/208 | Х    | Х    | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| dsPIC33XXXMP506/206 | —    | —    | —    | —    | —    | —    | —   | —   | —   | —   |     | —   | —   | —   | —   | —   |

| dsPIC33XXXMP504/204 | —    | —    | —    | —    | _    | —    | —   | —   | —   | —   | _   | —   | —   | —   | —   | —   |

| dsPIC33XXXMP503/203 | —    | —    | —    | —    | —    | —    | —   | —   | —   | —   | —   | —   | —   | —   | —   | —   |

| dsPIC33XXXMP502/202 | _    | _    |      | —    | _    | —    | —   | —   | —   | _   |     | —   | —   | —   | —   | —   |

| ANSELE              | _    | _    | _    | —    | _    | _    | _   | _   | _   | —   | _   | Х   | Х   | Х   | Х   | Х   |

#### TABLE 8-2: 5V INPUT TOLERANT PORTS

| PORTA | —    | —    | —    | —    | —    | —    | —   | —   | —   | —   | —   | RA4 | RA3 | RA2 | RA1 | RA0 |

|-------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| PORTB | RB15 | RB14 | RB13 | RB12 | RB11 | RB10 | RB9 | RB8 | RB7 | RB6 | RB5 | RB4 | RB3 | RB2 | RB1 | RB0 |

| PORTC | RC15 | RC14 | RC13 | RC12 | RC11 | RC10 | RC9 | RC8 | RC7 | RC6 | RC5 | RC4 | RC3 | RC2 | RC1 | RC0 |

| PORTD | RD15 | RD14 | RD13 | RD12 | RD11 | RD10 | RD9 | RD8 | RD7 | RD6 | RD5 | RD4 | RD3 | RD2 | RD1 | RD0 |

| PORTE | RE15 | RE14 | RE13 | RE12 | RE11 | RE10 | RE9 | RE8 | RE7 | RE6 | RE5 | RE4 | RE3 | RE2 | RE1 | RE0 |

**Legend:** Shaded pins are up to 5.5 VDC input tolerant.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP45R5 | RP45R4 | RP45R3 | RP45R2 | RP45R1 | RP45R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP44R5 | RP44R4 | RP44R3 | RP44R2 | RP44R1 | RP44R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

#### REGISTER 8-60: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP45R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP45 Output Pin bits (see Table 8-7 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                              |

| bit 5-0   | <b>RP44R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP44 Output Pin bits (see Table 8-7 for peripheral function numbers) |

#### REGISTER 8-61: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP47R5 | RP47R4 | RP47R3 | RP47R2 | RP47R1 | RP47R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP46R5 | RP46R4 | RP46R3 | RP46R2 | RP46R1 | RP46R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP47R<5:0>:** Peripheral Output Function is Assigned to RP47 Output Pin bits (see Table 8-7 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP46R<5:0>:** Peripheral Output Function is Assigned to RP46 Output Pin bits (see Table 8-7 for peripheral function numbers)

Equation 9-1 provides the relationship between the PLL Input Frequency (FPLLI) and VCO Output Frequency (FVCO).

### EQUATION 9-1: Fvco CALCULATION

$FVCO = FPLLI \times \left(\frac{M}{N1}\right) = FPLLI \times \left(\frac{PLLFBDIV < 7:0>}{PLLPRE < 3:0>}\right)$

Equation 9-2 provides the relationship between the PLL Input Frequency (FPLLI) and PLL Output Frequency (FPLLO).

#### EQUATION 9-2: FPLLO CALCULATION

$FPLLO = FPLLI \times \left(\frac{M}{N1 \times N2 \times N3}\right) = FPLLI \times \left(\frac{PLLFBDIV < 7:0>}{PLLPRE < 3:0> \times POST1DIV < 2:0> \times POST2DIV < 2:0>}\right)$

Where:

$$\begin{split} M &= PLLFBDIV < 7:0 > \\ N1 &= PLLPRE < 3:0 > \\ N2 &= POST1DIV < 2:0 > \\ N3 &= POST2DIV < 2:0 > \end{split}$$

**Note:** The PLL Phase Detector Input Divider Select (PLLPREx) bits and the PLL Feedback Divider (PLLFBDIVx) bits should not be changed when operating in PLL mode. Therefore, the user must start in either a non-PLL mode or clock switch to a non-PLL mode (e.g., internal FRC Oscillator) to make any necessary changes and then clock switch to the desired PLL mode.

It is not permitted to directly clock switch from one PLL clock source to a different PLL clock source. The user would need to transition between PLL clock sources with a clock switch to a non-PLL clock source.

#### EXAMPLE 9-1: CODE EXAMPLE FOR USING PRIMARY PLL WITH 8 MHz INTERNAL FRC

```

//code example for 50 MIPS system clock using 8MHz FRC

// Select FRC on POR

#pragma config FNOSC = FRC

// Oscillator Source Selection (Internal Fast RC (FRC))

#pragma config IESO = OFF

// Enable Clock Switching

#pragma config FCKSM = CSECMD

int

main()

// Configure PLL prescaler, both PLL postscalers, and PLL feedback divider

CLKDIVbits.PLLPRE = 1;

// N1=1

PLLFBDbits.PLLFBDIV = 125;

// M = 125

PLLDIVbits.POST1DIV = 5;

// N2=5

PLLDIVbits.POST2DIV = 1;

// N3=1

// Initiate Clock Switch to FRC with PLL (NOSC=0b001)

__builtin_write_OSCCONH(0x01);

_builtin_write_OSCCONL(OSCCON | 0x01);

// Wait for Clock switch to occur

while (OSCCONbits.OSWEN!= 0);

```

## 9.5 Oscillator Configuration

The oscillator system has both Configuration registers and SFRs to configure, control and monitor the system. The FOSCSEL and FOSC Configuration registers (Register 30-4 and Register 30-5, respectively) are used for initial setup. Table 9-1 lists the configuration settings that select the device's oscillator source and operating mode at a Power-on Reset (POR).

| TABLE 9-1: | CONFIGURATION BIT VALUES FOR CLOCK SELECTION |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

| Oscillator<br>Source | Oscillator Mode                                  | FNOSC<2:0><br>Value | POSCMD<1:0><br>Value | Notes |

|----------------------|--------------------------------------------------|---------------------|----------------------|-------|

| S0                   | Fast RC Oscillator (FRC)                         | 000                 | xx                   | 1     |

| S1                   | Fast RC Oscillator with PLL (FRCPLL)             | 001                 | xx                   | 1     |

| S2                   | Primary Oscillator (EC)                          | 010                 | 00                   | 1     |

| S2                   | Primary Oscillator (XT)                          | 010                 | 01                   |       |

| S2                   | Primary Oscillator (HS)                          | 010                 | 10                   |       |

| S3                   | Primary Oscillator with PLL (ECPLL)              | 011                 | 00                   | 1     |

| S3                   | Primary Oscillator with PLL (XTPLL)              | 011                 | 01                   |       |

| S3                   | Primary Oscillator with PLL (HSPLL)              | 011                 | 10                   |       |

| S4                   | Reserved                                         | 100                 | xx                   |       |

| S5                   | Low-Power RC Oscillator (LPRC)                   | 101                 | xx                   | 1     |

| S6                   | Backup FRC (BFRC)                                | 110                 | xx                   | 1     |

| S7                   | Fast RC Oscillator with ÷ N Divider<br>(FRCDIVN) | 111                 | XX                   | 1, 2  |

Note 1: The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

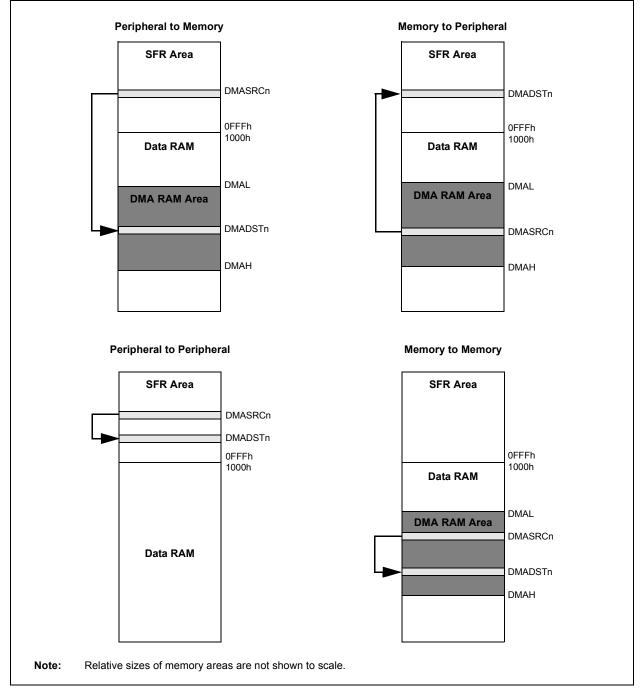

## FIGURE 10-2: TYPES OF DMA DATA TRANSFERS

## REGISTER 11-1: C1CONH: CAN CONTROL REGISTER HIGH (CONTINUED)

| bit 4 | TXQEN: Enable Transmit Queue bit <sup>(1)</sup>                                                        |

|-------|--------------------------------------------------------------------------------------------------------|

|       | 1 = Enables Transmit Message Queue (TXQ) and reserves space in RAM                                     |

|       | 0 = Does not reserve space in RAM for TXQ                                                              |

| bit 3 | STEF: Store in Transmit Event FIFO bit <sup>(1)</sup>                                                  |

|       | 1 = Saves transmitted messages in TEF                                                                  |

|       | 0 = Does not save transmitted messages in TEF                                                          |

| bit 2 | SERRLOM: Transition to Listen Only Mode on System Error bit <sup>(1)</sup>                             |

|       | 1 = Transitions to Listen Only mode                                                                    |

|       | 0 = Transitions to Restricted Operation mode                                                           |

| bit 1 | ESIGM: Transmit ESI in Gateway Mode bit <sup>(1)</sup>                                                 |

|       | 1 = ESI is transmitted as recessive when ESI of the message is high or CAN controller is error passive |

|       | 0 = ESI reflects error status of CAN controller                                                        |

| bit 0 | RTXAT: Restrict Retransmission Attempts bit <sup>(1)</sup>                                             |

|       | 1 = Restricted retransmission attempts, uses TXAT<1:0> bits (C1TXQCONH<6:5>)                           |

|       | 0 = Unlimited number of retransmission attempts, TXAT<1:0> bits will be ignored                        |

|       |                                                                                                        |

**Note 1:** These bits can only be modified in Configuration mode (OPMOD<2:0> = 100).

### REGISTER 12-20: PGxyPCIH: PWM GENERATOR xy PCI REGISTER HIGH (x = PWM GENERATOR #; y = F, CL, FF OR S)

|            | (X                                                                                                                                                                                           | - FWW GEN                                           | ERAIOR #, y                  | – F, CL, FF (    | UK 3)             |                    |                |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------|------------------|-------------------|--------------------|----------------|--|--|--|

| R/W-0      | R/W-0                                                                                                                                                                                        | R/W-0                                               | R/W-0                        | U-0              | R/W-0             | R/W-0              | R/W-0          |  |  |  |

| BPEN       | BPSEL2 <sup>(1)</sup>                                                                                                                                                                        | BPSEL1 <sup>(1)</sup>                               | BPSEL0 <sup>(1)</sup>        |                  | ACP2              | ACP1               | ACP0           |  |  |  |

| bit 15     |                                                                                                                                                                                              |                                                     |                              |                  |                   |                    | bit 8          |  |  |  |

|            |                                                                                                                                                                                              |                                                     |                              |                  |                   |                    |                |  |  |  |

| R/W-0      | R/W-0                                                                                                                                                                                        | R/W-0                                               | R/W-0                        | R/W-0            | R/W-0             | R/W-0              | R/W-0          |  |  |  |

| SWPCI      | SWPCIM1                                                                                                                                                                                      | SWPCIM0                                             | LATMOD                       | TQPS             | TQSS2             | TQSS1              | TQSS0          |  |  |  |

| bit 7      |                                                                                                                                                                                              |                                                     |                              |                  |                   |                    | bit C          |  |  |  |

| Legend:    |                                                                                                                                                                                              |                                                     |                              |                  |                   |                    |                |  |  |  |

| R = Reada  | ıble bit                                                                                                                                                                                     | W = Writable                                        | bit                          | U = Unimpler     | nented bit, read  | as '0'             |                |  |  |  |

| -n = Value |                                                                                                                                                                                              | '1' = Bit is se                                     |                              | '0' = Bit is cle |                   | x = Bit is unkn    | own            |  |  |  |

|            |                                                                                                                                                                                              |                                                     |                              |                  |                   |                    |                |  |  |  |

| bit 15     | BPEN: PCI                                                                                                                                                                                    | Bypass Enable                                       | e bit                        |                  |                   |                    |                |  |  |  |

|            |                                                                                                                                                                                              |                                                     |                              |                  |                   | erator will be cor | ntrolled by PC |  |  |  |

|            |                                                                                                                                                                                              |                                                     | Senerator select             | ed by the BPS    | EL<2:0> bits      |                    |                |  |  |  |

| bit 14-12  |                                                                                                                                                                                              | ction is not byp                                    | Source Selecti               | on hito(1)       |                   |                    |                |  |  |  |

| DIL 14-12  |                                                                                                                                                                                              |                                                     |                              |                  | Llogic when BPI   | <b>EN =</b> 1      |                |  |  |  |

|            | 111 = PCI control is sourced from PWM Generator 8 PCI logic when BPEN = 1<br>110 = PCI control is sourced from PWM Generator 7 PCI logic when BPEN = 1                                       |                                                     |                              |                  |                   |                    |                |  |  |  |

|            | 101 = PCI control is sourced from PWM Generator 6 PCI logic when BPEN = 1                                                                                                                    |                                                     |                              |                  |                   |                    |                |  |  |  |

|            | 100 = PCI control is sourced from PWM Generator 5 PCI logic when BPEN = 1                                                                                                                    |                                                     |                              |                  |                   |                    |                |  |  |  |

|            | 011 = PCI control is sourced from PWM Generator 4 PCI logic when BPEN = 1                                                                                                                    |                                                     |                              |                  |                   |                    |                |  |  |  |

|            | 010 = PCI control is sourced from PWM Generator 3 PCI logic when BPEN = 1<br>001 = PCI control is sourced from PWM Generator 2 PCI logic when BPEN = 1                                       |                                                     |                              |                  |                   |                    |                |  |  |  |

|            |                                                                                                                                                                                              |                                                     |                              |                  | I logic when BPI  |                    |                |  |  |  |

| bit 11     | Unimpleme                                                                                                                                                                                    | nted: Read as                                       | ·'O'                         |                  |                   |                    |                |  |  |  |

| bit 10-8   | ACP<2:0>:                                                                                                                                                                                    | PCI Acceptance                                      | e Criteria Seleo             | ction bits       |                   |                    |                |  |  |  |

|            | 111 = Rese                                                                                                                                                                                   |                                                     |                              |                  |                   |                    |                |  |  |  |

|            | 110 = Rese                                                                                                                                                                                   |                                                     |                              |                  |                   |                    |                |  |  |  |

|            |                                                                                                                                                                                              | 101 = Latched any edge<br>100 = Latched rising edge |                              |                  |                   |                    |                |  |  |  |

|            | 011 = Latch                                                                                                                                                                                  | •••                                                 |                              |                  |                   |                    |                |  |  |  |

|            | 010 = Any e                                                                                                                                                                                  |                                                     |                              |                  |                   |                    |                |  |  |  |

|            |                                                                                                                                                                                              | 001 = Rising edge                                   |                              |                  |                   |                    |                |  |  |  |

| bit 7      | 000 = Level                                                                                                                                                                                  | tware PCI Con                                       | tral bit                     |                  |                   |                    |                |  |  |  |

|            |                                                                                                                                                                                              |                                                     |                              | v the SMPCIM     | <1:0> control bit | te                 |                |  |  |  |

|            | <ul> <li>1 = Drives a '1' to PCI logic assigned to by the SWPCIM&lt;1:0&gt; control bits</li> <li>0 = Drives a '0' to PCI logic assigned to by the SWPCIM&lt;1:0&gt; control bits</li> </ul> |                                                     |                              |                  |                   |                    |                |  |  |  |

| bit 6-5    |                                                                                                                                                                                              | -                                                   | PCI Control Mo               | -                |                   |                    |                |  |  |  |

|            | 11 = Reserv                                                                                                                                                                                  | /ed                                                 |                              |                  |                   |                    |                |  |  |  |

|            |                                                                                                                                                                                              |                                                     | d to termination             |                  |                   |                    |                |  |  |  |

|            |                                                                                                                                                                                              |                                                     | d to acceptance              |                  |                   |                    |                |  |  |  |

| hit 1      |                                                                                                                                                                                              | -                                                   | d to PCI accept<br>lodo bit  | ance logic       |                   |                    |                |  |  |  |

| bit 4      |                                                                                                                                                                                              | PCI SR Latch M                                      | iode bit<br>iinant in Latche | d Accentance r   | nodes             |                    |                |  |  |  |

|            |                                                                                                                                                                                              |                                                     | ant in Latched A             |                  |                   |                    |                |  |  |  |

|            |                                                                                                                                                                                              |                                                     |                              |                  | -                 |                    |                |  |  |  |

| NIGTO 11   | Solooto '0' if o                                                                                                                                                                             |                                                     | Concrator in not             | t propont        |                   |                    |                |  |  |  |

Note 1: Selects '0' if selected PWM Generator is not present.

NOTES:

# 13.0 HIGH-SPEED, 12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (DS70005213) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33CK256MP508 devices have a high-speed, 12-bit Analog-to-Digital Converter (ADC) that features a low conversion latency, high resolution and oversampling capabilities to improve performance in AC/DC, DC/DC power converters. The devices implement the ADC with three SAR cores, two dedicated and one shared.

# 13.1 ADC Features Overview

The High-Speed, 12-Bit Multiple SARs Analog-to-Digital Converter (ADC) includes the following features:

- Three ADC Cores: Two Dedicated Cores and One Shared (common) Core

- User-Configurable Resolution of up to 12 Bits for each Core

- Up to 3.5 Msps Conversion Rate per Channel at 12-Bit Resolution

- Low-Latency Conversion

- Up to 24 Analog Input Channels, with a Separate 16-Bit Conversion Result Register for each Input

- Conversion Result can be Formatted as Unsigned or Signed Data, on a per Channel Basis, for All Channels

- Simultaneous Sampling of up to 3 Analog Inputs

- Channel Scan Capability

- Multiple Conversion Trigger Options for each Core, including:

- PWM triggers from CPU cores

- MCCP/SCCP modules triggers

- CLC modules triggers

- External pin trigger event (ADTRG31)

- Software trigger

- Four Integrated Digital Comparators with Dedicated Interrupts:

- Multiple comparison options

- Assignable to specific analog inputs

- Four Oversampling Filters with Dedicated Interrupts:

- Provide increased resolution

- Assignable to a specific analog input

The module consists of three independent SAR ADC cores. Simplified block diagrams of the Multiple SARs 12-Bit ADC are shown in Figure 13-1 and Figure 13-2.

The analog inputs (channels) are connected through multiplexers and switches to the Sample-and-Hold (S&H) circuit of each ADC core. The core uses the channel information (the output format, the Measurement mode and the input number) to process the analog sample. When conversion is complete, the result is stored in the result buffer for the specific analog input, and passed to the digital filter and digital comparator if they were configured to use data from this particular channel.

The ADC module can sample up to three inputs at a time (two inputs from the dedicated SAR cores and one from the shared SAR core). If multiple ADC inputs request conversion on the shared core, the module will convert them in a sequential manner, starting with the lowest order input.

The ADC provides each analog input the ability to specify its own trigger source. This capability allows the ADC to sample and convert analog inputs that are associated with PWM generators operating on independent time bases.

#### REGISTER 15-4: QEIxSTAT: QEIx STATUS REGISTER (CONTINUED)

- bit 2 **HOMIEN:** Home Input Event Interrupt Enable bit

- 1 = Interrupt is enabled0 = Interrupt is disabled

- bit 1 **IDXIRQ:** Status Flag for Index Event Status bit

- 1 = Index event has occurred

- 0 = No Index event has occurred

- bit 0 IDXIEN: Index Input Event Interrupt Enable bit

- 1 = Interrupt is enabled

- 0 = Interrupt is disabled

- Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

## REGISTER 19-12: PMRADDR: PARALLEL MASTER PORT READ ADDRESS REGISTER<sup>(2)</sup>

| R/W-0<br>RCS2 <sup>(1)</sup> | R/W-0                  |                             | <b>B A A A A</b>            | <b>B</b> 4 4 4 6                   | <b>B</b> 8 8 4 6 |                 | <b>B</b> 8 4 4 6   |  |

|------------------------------|------------------------|-----------------------------|-----------------------------|------------------------------------|------------------|-----------------|--------------------|--|

| RCS2(")                      | (1)                    | R/W-0                       | R/W-0                       | R/W-0                              | R/W-0            | R/W-0           | R/W-0              |  |

| (4)                          | RCS1 <sup>(1)</sup>    | -                           |                             | RADD                               | R<13:8>          |                 |                    |  |

| RADDR15 <sup>(1)</sup>       | RADDR14 <sup>(1)</sup> |                             |                             | 10.00                              |                  |                 |                    |  |

| bit 15                       |                        |                             |                             |                                    |                  |                 | bit 8              |  |

|                              |                        |                             |                             |                                    |                  | DAMA            | DAMO               |  |

| R/W-0                        | R/W-0                  | R/W-0                       | R/W-0                       | R/W-0                              | R/W-0            | R/W-0           | R/W-0              |  |

|                              |                        |                             | RADD                        | R<7:0>                             |                  |                 |                    |  |

| bit 7                        |                        |                             |                             |                                    |                  |                 | bit 0              |  |

|                              |                        |                             |                             |                                    |                  |                 |                    |  |

| Legend:                      |                        |                             |                             |                                    |                  |                 |                    |  |

| R = Readable                 | bit                    | W = Writable bit            |                             | U = Unimplemented bit, read as '0' |                  |                 |                    |  |

| -n = Value at F              | POR                    | '1' = Bit is set            |                             | '0' = Bit is cleared x             |                  | x = Bit is unkr | x = Bit is unknown |  |

|                              |                        |                             |                             |                                    |                  |                 |                    |  |

| bit 15                       | RCS2: Chip S           | Select 2 bit <sup>(1)</sup> |                             |                                    |                  |                 |                    |  |

|                              | 1 = Chip Sele          |                             |                             |                                    |                  |                 |                    |  |

|                              | 0 = Chip Sele          | ect 2 is inactive           | (RADDR15 f                  | unction is selec                   | cted)            |                 |                    |  |

| bit 15                       | RADDR15: Ta            | arget Read Add              | dress bit 15 <sup>(1)</sup> |                                    |                  |                 |                    |  |

| bit 14                       | RCS1: Chip S           | Select 1 bit <sup>(1)</sup> |                             |                                    |                  |                 |                    |  |

|                              | 1 = Chip Sele          | ect 1 is active             |                             |                                    |                  |                 |                    |  |

|                              | 0 = Chip Sele          | ect 1 is inactive           | (RADDR14 f                  | unction is seled                   | cted)            |                 |                    |  |

| bit 14                       | RADDR14: Ta            | arget Read Add              | dress bit 14 <sup>(1)</sup> |                                    |                  |                 |                    |  |

|                              |                        | >: Target Read              | Addroce bite                |                                    |                  |                 |                    |  |

2: This register is only used when the DUALBUF bit (PMCONH<1>) is set to '1'.

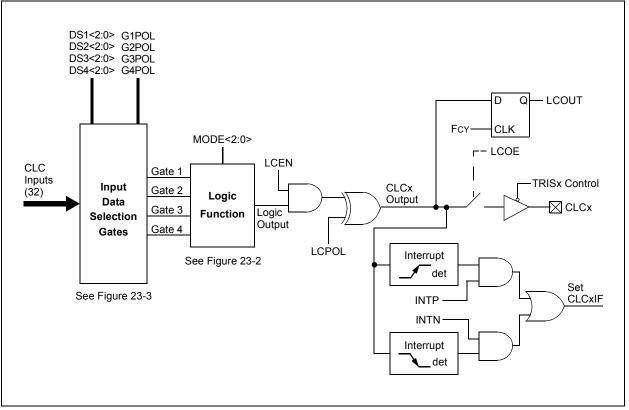

# 23.0 CONFIGURABLE LOGIC CELL (CLC)

Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. For more information, refer to "Configurable Logic Cell (CLC)" (DS70005298) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM. The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins. This provides greater flexibility and potential in embedded designs, since the CLC module can operate outside the limitations of software execution, and supports a vast amount of output designs.

There are four input gates to the selected logic function. These four input gates select from a pool of up to 32 signals that are selected using four data source selection multiplexers. Figure 23-1 shows an overview of the module.

Figure 23-3 shows the details of the data source multiplexers and Figure 23-2 shows the logic input gate connections.

## FIGURE 23-1: CLCx MODULE

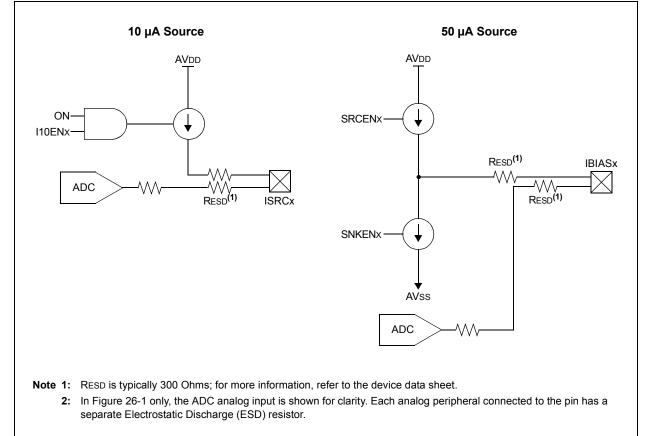

# 26.0 CURRENT BIAS GENERATOR (CBG)

- Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Current Bias Generator (CBG)" (DS70005253) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Current Bias Generator (CBG) consists of two classes of current sources: 10  $\mu$ A and 50  $\mu$ A sources. The major features of each current source are:

- 10 µA Current Sources:

- Current sourcing only

- Up to four independent sources

- 50 µA Current Sources:

- Selectable current sourcing or sinking

- Selectable current mirroring for sourcing and sinking

A simplified block diagram of the CBG module is shown in Figure 26-1.

## REGISTER 30-1: FSEC CONFIGURATION REGISTER

| U-1           | U-1                                                    | U-1                                                                     | U-1             | U-1               | U-1              | U-1             | U-1        |  |  |  |  |

|---------------|--------------------------------------------------------|-------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|------------|--|--|--|--|

| 0-1           | 0-1                                                    | 0-1                                                                     | 0-1             | 0-1               | 0-1              | 0-1             | 0-1        |  |  |  |  |

| <br>bit 23    |                                                        | _                                                                       |                 | _                 |                  | _               | <br>bit 16 |  |  |  |  |

| 511 25        |                                                        |                                                                         |                 |                   |                  |                 | DIL TO     |  |  |  |  |

| R/PO-1        | U-1                                                    | U-1                                                                     | U-1             | R/PO-1            | R/PO-1           | R/PO-1          | R/PO-1     |  |  |  |  |

| AIVTDIS       | _                                                      |                                                                         | —               | CSS2              | CSS1             | CSS0            | CWRP       |  |  |  |  |

| bit 15        |                                                        |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

|               |                                                        |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

| R/PO-1        | R/PO-1                                                 | R/PO-1                                                                  | U-1             | R/PO-1            | R/PO-1           | R/PO-1          | R/PO-1     |  |  |  |  |

| GSS1          | GSS0                                                   | GWRP                                                                    | —               | BSEN              | BSS1             | BSS0            | BWRP       |  |  |  |  |

| bit 7         |                                                        |                                                                         |                 |                   |                  |                 | bit 0      |  |  |  |  |

| Legend:       |                                                        | PO = Program                                                            | n Onco hit      |                   |                  |                 |            |  |  |  |  |

| R = Readabl   | la hit                                                 | W = Writable                                                            |                 | II – Unimplon     | nonted hit read  | d oo 'O'        |            |  |  |  |  |

|               |                                                        |                                                                         |                 | •                 | nented bit, read |                 |            |  |  |  |  |

| -n = Value at | IPOR                                                   | '1' = Bit is set                                                        |                 | '0' = Bit is clea | areo             | x = Bit is unkr | lown       |  |  |  |  |

| bit 23-16     | Unimplemer                                             | nted: Read as ':                                                        | ı,              |                   |                  |                 |            |  |  |  |  |

| bit 15        | -                                                      |                                                                         |                 | Disable bit       |                  |                 |            |  |  |  |  |

|               |                                                        | AIVTDIS: Alternate Interrupt Vector Table Disable bit 1 = Disables AIVT |                 |                   |                  |                 |            |  |  |  |  |

|               | 0 = Enables AIVT                                       |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

| bit 14-12     | Unimplemented: Read as '1'                             |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

| bit 11-9      |                                                        | Configuration Se                                                        | -               |                   | n Level bits     |                 |            |  |  |  |  |

|               | 111 = No protection (other than CWRP write protection) |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

|               | 110 = Standard security<br>10x = Enhanced security     |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

|               | 0xx = High s                                           | •                                                                       |                 |                   |                  |                 |            |  |  |  |  |

| bit 8         | CWRP: Conf                                             | iguration Segm                                                          | ent Write-Prot  | ect bit           |                  |                 |            |  |  |  |  |

|               |                                                        | ation Segment ation Segment                                             |                 |                   |                  |                 |            |  |  |  |  |

| bit 7-6       | •                                                      | General Segmer                                                          | •               |                   | el bits          |                 |            |  |  |  |  |

|               |                                                        | ection (other that                                                      |                 |                   |                  |                 |            |  |  |  |  |

|               | 10 = Standard security                                 |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

|               | 0x = High security                                     |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

| bit 5         | GWRP: General Segment Write-Protect bit                |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

|               |                                                        | gram memory i<br>gram memory i                                          |                 |                   |                  |                 |            |  |  |  |  |

| bit 4         |                                                        | ted: Read as ':                                                         |                 |                   |                  |                 |            |  |  |  |  |

| bit 3         | BSEN: Boot                                             | Segment Contr                                                           | ol bit          |                   |                  |                 |            |  |  |  |  |

|               | 1 = No Boot                                            | Segment                                                                 |                 |                   |                  |                 |            |  |  |  |  |

|               |                                                        | gment size is de                                                        | -               |                   |                  |                 |            |  |  |  |  |

| bit 2-1       |                                                        | Boot Segment C                                                          |                 |                   | its              |                 |            |  |  |  |  |

|               | 11 = No prot<br>10 = Standar                           | ection (other tha                                                       | an BWRP write   | e protection)     |                  |                 |            |  |  |  |  |

|               | 0x = High se                                           | •                                                                       |                 |                   |                  |                 |            |  |  |  |  |

| bit 0         | -                                                      | Segment Write                                                           | -Protect bit    |                   |                  |                 |            |  |  |  |  |

|               | 1 = User pro                                           | gram memory i                                                           | s not write-pro |                   |                  |                 |            |  |  |  |  |

|               | 0 = User pro                                           | gram memory i                                                           | s write-protect | ed                |                  |                 |            |  |  |  |  |

|               |                                                        |                                                                         |                 |                   |                  |                 |            |  |  |  |  |

| Legend: |        | PO = Prograr | n Once bit  |         |        |        |        |  |

|---------|--------|--------------|-------------|---------|--------|--------|--------|--|

| bit 7   |        |              |             |         |        |        | bit 0  |  |

|         |        |              | BSLI        | vl<7:0> |        |        |        |  |

| R/PO-1  | R/PO-1 | R/PO-1       | R/PO-1      | R/PO-1  | R/PO-1 | R/PO-1 | R/PO-1 |  |

| bit 15  |        |              |             |         |        |        | bit 8  |  |

|         | —      | —            | BSLIM<12:8> |         |        |        |        |  |

| U-1     | U-1    | U-1          | R/PO-1      | R/PO-1  | R/PO-1 | R/PO-1 | R/PO-1 |  |

| bit 23  |        |              |             |         |        |        | bit 16 |  |

| _       | _      | _            | _           | _       | —      | —      | _      |  |

| U-1     | U-1    | U-1          | U-1         | U-1     | U-1    | U-1    | U-1    |  |

### **REGISTER 30-2: FBSLIM CONFIGURATION REGISTER**

| Legend:           | PO = Program Once bit |                             |                    |

|-------------------|-----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared        | x = Bit is unknown |

bit 23-13 Unimplemented: Read as '1'

bit 12-0 BSLIM<12:0>: Boot Segment Code Flash Page Address Limit bits

Contains the page address of the first active General Segment page. The value to be programmed is the inverted page address, such that programming additional '0's can only increase the Boot Segment size.

### **REGISTER 30-3: FSIGN CONFIGURATION REGISTER**

| U-1                                  | U-1                                 | U-1          | U-1 | U-1                                     | U-1 | U-1 | U-1    |  |

|--------------------------------------|-------------------------------------|--------------|-----|-----------------------------------------|-----|-----|--------|--|

| _                                    | —                                   | —            | —   | —                                       | —   | —   | —      |  |

| bit 23                               |                                     |              |     |                                         |     |     | bit 16 |  |

|                                      |                                     |              |     |                                         |     |     |        |  |

| r-0                                  | U-1                                 | U-1          | U-1 | U-1                                     | U-1 | U-1 | U-1    |  |

| —                                    | —                                   | —            |     | —                                       | —   | —   | —      |  |

| bit 15                               |                                     |              |     |                                         |     |     | bit 8  |  |

|                                      |                                     |              |     |                                         |     |     |        |  |

| U-1                                  | U-1                                 | U-1          | U-1 | U-1                                     | U-1 | U-1 | U-1    |  |

|                                      | —                                   | —            |     | —                                       | —   | —   | —      |  |

| bit 7                                |                                     |              |     |                                         |     |     | bit 0  |  |

|                                      |                                     |              |     |                                         |     |     |        |  |

| Legend:                              |                                     | r = Reserved | bit | PO = Program Once bit                   |     |     |        |  |

| R = Readabl                          | e bit                               | W = Writable | bit | U = Unimplemented bit, read as '0'      |     |     |        |  |

| -n = Value at POR '1' = Bit is set   |                                     |              |     | '0' = Bit is cleared x = Bit is unknown |     |     | nown   |  |

|                                      |                                     |              |     |                                         |     |     |        |  |

| bit 23-16 Unimplemented: Read as '1' |                                     |              |     |                                         |     |     |        |  |

| bit 15                               | it 15 Reserved: Maintain as '0'     |              |     |                                         |     |     |        |  |

| bit 14-0                             | bit 14-0 Unimplemented: Read as '1' |              |     |                                         |     |     |        |  |

|                                      |                                     |              |     |                                         |     |     |        |  |

| Base<br>Instr<br># Assembly<br>Mnemonic |        | Assembly Syntax |                | Description                                         | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |

|-----------------------------------------|--------|-----------------|----------------|-----------------------------------------------------|---------------|-------------------------------|--------------------------|

| 69                                      | NEG    | NEG Acc         |                | Negate Accumulator                                  | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                                         |        | NEG             | f              | $f = \overline{f} + 1$                              | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | NEG             | f,WREG         | WREG = $f + 1$                                      | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | NEG             | Ws,Wd          | Wd = Ws + 1                                         | 1             | 1                             | C,DC,N,OV,Z              |

| 70                                      | NOP    | NOP             |                | No Operation                                        | 1             | 1                             | None                     |

|                                         |        | NOPR            |                | No Operation                                        | 1             | 1                             | None                     |

| 71                                      | NORM   | NORM            | Acc, Wd        | Normalize Accumulator                               | 1             | 1                             | N,OV,Z                   |

| 72                                      | POP    | POP             | f              | Pop f from Top-of-Stack (TOS)                       | 1             | 1                             | None                     |

|                                         |        | POP             | Wdo            | Pop from Top-of-Stack (TOS) to Wdo                  | 1             | 1                             | None                     |

|                                         |        | POP.D           | Wnd            | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1)   | 1             | 2                             | None                     |

|                                         |        | POP.S           |                | Pop Shadow Registers                                | 1             | 1                             | All                      |

| 73                                      | PUSH   | PUSH            | f              | Push f to Top-of-Stack (TOS)                        | 1             | 1                             | None                     |

|                                         |        | PUSH            | Wso            | Push Wso to Top-of-Stack (TOS)                      | 1             | 1                             | None                     |

|                                         |        | PUSH.D          | Wns            | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)       | 1             | 2                             | None                     |

|                                         |        | PUSH.S          |                | Push Shadow Registers                               | 1             | 1                             | None                     |

| 74                                      | PWRSAV | PWRSAV          | #lit1          | Go into Sleep or Idle mode                          | 1             | 1                             | WDTO,Sleep               |

| 75                                      | RCALL  | RCALL           | Expr           | Relative Call                                       | 1             | 4                             | SFA                      |

|                                         |        | RCALL           | Wn             | Computed Call                                       | 1             | 4                             | SFA                      |

| 76                                      | REPEAT | REPEAT          | #lit15         | Repeat Next Instruction lit15 + 1 times             | 1             | 1                             | None                     |