Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------|

| roduct Status             | Active                                                                            |

| Core Processor            | dsPIC                                                                             |

| Core Size                 | 16-Bit                                                                            |

| peed                      | 100MHz                                                                            |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| eripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| lumber of I/O             | 21                                                                                |

| rogram Memory Size        | 128KB (128K x 8)                                                                  |

| rogram Memory Type        | FLASH                                                                             |

| EPROM Size                | -                                                                                 |

| AM Size                   | 16K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Oata Converters           | A/D 12x12b; D/A 3x12b                                                             |

| Oscillator Type           | Internal                                                                          |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Nounting Type             | Surface Mount                                                                     |

| ackage / Case             | 28-UQFN Exposed Pad                                                               |

| upplier Device Package    | 28-UQFN (6x6)                                                                     |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck128mp502t-i-2n |

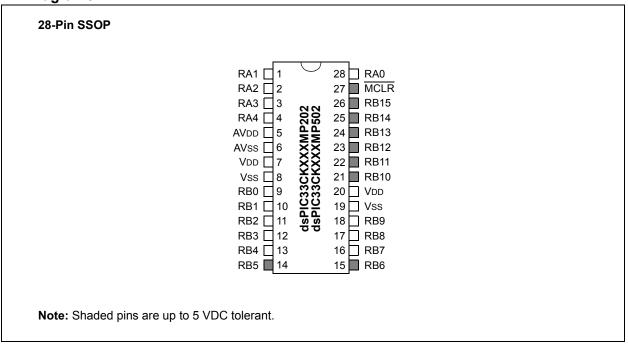

TABLE 3: 28-PIN SSOP

| Pin# | Function                                                              | Pin# | Function                         |

|------|-----------------------------------------------------------------------|------|----------------------------------|

| 1    | OA1IN-/ANA1/RA1                                                       | 15   | PGC3/RP38/SCL2/RB6               |

| 2    | OA1IN+/AN9/RA2                                                        | 16   | TDO/AN2/CMP3A/RP39/SDA3/RB7      |

| 3    | DACOUT1/AN3/CMP1C/RA3                                                 | 17   | PGD1/AN10/ <b>RP40</b> /SCL1/RB8 |

| 4    | AN4/CMP3B/IBIAS3/RA4                                                  | 18   | PGC1/AN11/ <b>RP41</b> /SDA1/RB9 |

| 5    | AVDD                                                                  | 19   | Vss                              |

| 6    | AVss                                                                  | 20   | VDD                              |

| 7    | VDD                                                                   | 21   | TMS/ <b>RP42</b> /PWM3H/RB10     |

| 8    | Vss                                                                   | 22   | TCK/RP43/PWM3L/RB11              |

| 9    | OSCI/CLKI/AN5/RP32/RB0                                                | 23   | TDI/ <b>RP44</b> /PWM2H/RB12     |

| 10   | OSCO/CLKO/AN6/RP33/RB1                                                | 24   | RP45/PWM2L/RB13                  |

| 11   | OA2OUT/AN1/AN7/ANA0/CMP1D/CMP2D/CMP3D/ <b>RP34</b> /<br>SCL3/INT0/RB2 | 25   | RP46/PWM1H/RB14                  |

| 12   | PGD2/OA2IN-/AN8/ <b>RP35</b> /RB3                                     | 26   | RP47/PWM1L/RB15                  |

| 13   | PGC2/OA2IN+/ <b>RP36</b> /RB4                                         | 27   | MCLR                             |

| 14   | PGD3/ <b>RP37</b> /SDA2/RB5                                           | 28   | OA1OUT/AN0/CMP1A/IBIAS0/RA0      |

Note: RPn represents remappable peripheral functions.

### 3.4.2 CPU RESOURCES

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 3.4.2.1 Key Resources

- "dsPIC33E Enhanced CPU" (DS70005158) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

### 3.4.4 ARITHMETIC LOGIC UNIT (ALU)

The dsPIC33CK256MP508 family ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70000157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

### 3.4.4.1 Multiplier

Using the high-speed, 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- · 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

### 3.4.4.2 Divider

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- · 32-bit signed/16-bit signed divide

- · 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute. There are additional instructions: DIV2 and DIVF2. Divide instructions will complete in 6 cycles.

#### 3.4.5 DSP ENGINE

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are, ADD, SUB, NEG, MIN and MAX.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed, unsigned or mixed-sign DSP multiply (USx)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

| Instruction | Algebraic<br>Operation  | ACC<br>Write-Back |  |  |  |  |  |  |

|-------------|-------------------------|-------------------|--|--|--|--|--|--|

| CLR         | A = 0                   | Yes               |  |  |  |  |  |  |

| ED          | $A = (x - y)^2$         | No                |  |  |  |  |  |  |

| EDAC        | $A = A + (x - y)^2$     | No                |  |  |  |  |  |  |

| MAC         | $A = A + (x \bullet y)$ | Yes               |  |  |  |  |  |  |

| MAC         | $A = A + x^2$           | No                |  |  |  |  |  |  |

| MOVSAC      | No change in A          | Yes               |  |  |  |  |  |  |

| MPY         | $A = x \cdot y$         | No                |  |  |  |  |  |  |

| MPY         | $A = x^2$               | No                |  |  |  |  |  |  |

| MPY.N       | $A = -x \bullet y$      | No                |  |  |  |  |  |  |

| MSC         | $A = A - x \bullet y$   | Yes               |  |  |  |  |  |  |

TABLE 7-1: INTERRUPT VECTOR DETAILS

| _                                     | Vector                           | IRQ   |                   | In       | Interrupt Bit Location |              |  |  |

|---------------------------------------|----------------------------------|-------|-------------------|----------|------------------------|--------------|--|--|

| Interrupt Source                      | Interrupt Source # # IVT Address |       | IVT Address       | Flag     | Enable                 | Priority     |  |  |

| INT0 – External Interrupt 0           | 8                                | 0     | 0x000014          | IFS0<0>  | IEC0<0>                | IPC0<2:0>    |  |  |

| T1 – Timer1                           | 9                                | 1     | 0x000016          | IFS0<1>  | IEC0<1>                | IPC0<6:4>    |  |  |

| CNA – Change Notice Interrupt A       | 10                               | 2     | 0x000018          | IFS0<2>  | IEC0<2>                | IPC0<10:8>   |  |  |

| CNB – Change Notice Interrupt B       | 11                               | 3     | 0x00001A          | IFS0<3>  | IEC0<3>                | IPC0<14:12>  |  |  |

| DMA0 – DMA Channel 0                  | 12                               | 4     | 0x00001C          | IFS0<4>  | IEC0<4>                | IPC1<2:0>    |  |  |

| Reserved                              | 13                               | 5     | 0x00001E          | _        | _                      | _            |  |  |

| CCP1 – Input Capture/Output Compare 1 | 14                               | 6     | 0x000020          | IFS0<6>  | IEC0<6>                | IPC1<10:8>   |  |  |

| CCT1 – CCP1 Timer                     | 15                               | 7     | 0x000022          | IFS0<7>  | IEC0<7>                | IPC1<14:12>  |  |  |

| DMA1 – DMA Channel 1                  | 16                               | 8     | 0x000024          | IFS0<8>  | IEC0<8>                | IPC2<2:0>    |  |  |

| SPI1RX – SPI1 Receiver                | 17                               | 9     | 0x000026          | IFS0<9>  | IEC0<9>                | IPC2<6:4>    |  |  |

| SPI1TX – SPI1 Transmitter             | 18                               | 10    | 0x000028          | IFS0<10> | IEC0<10>               | IPC2<10:8>   |  |  |

| U1RX – UART1 Receiver                 | 19                               | 11    | 0x00002A          | IFS0<11> | IEC0<11>               | IPC2<14:12>  |  |  |

| U1TX – UART1 Transmitter              | 20                               | 12    | 0x00002C          | IFS0<12> | IEC0<12>               | IPC3<2:0>    |  |  |

| ECCSBE – ECC Single Bit Error         | 21                               | 13    | 0x00002E          | IFS0<13> | IEC0<13>               | IPC3<6:4>    |  |  |

| NVM – NVM Write Complete              | 22                               | 14    | 0x000030          | IFS0<14> | IEC0<14>               | IPC3<10:8>   |  |  |

| INT1 – External Interrupt 1           | 23                               | 15    | 0x000032          | IFS0<15> | IEC0<15>               | IPC3<14:12>  |  |  |

| SI2C1 – I2C1 Slave Event              | 24                               | 16    | 0x000034          | IFS1<0>  | IEC1<0>                | IPC4<2:0>    |  |  |

| MI2C1 – I2C1 Master Event             | 25                               | 17    | 0x000036          | IFS1<1>  | IEC1<1>                | IPC4<6:4>    |  |  |

| DMA2 – DMA Channel 2                  | 26                               | 18    | 0x000038          | IFS1<2>  | IEC1<2>                | IPC4<10:8>   |  |  |

| CNC – Change Notice Interrupt C       | 27                               | 19    | 0x00003A          | IFS1<3>  | IEC1<3>                | IPC4<14:12>  |  |  |

| INT2 – External Interrupt 2           | 28                               | 20    | 0x00003C          | IFS1<4>  | IEC1<4>                | IPC5<2:0>    |  |  |

| DMA3 – DMA Channel 3                  | 29                               | 21    | 0x00003E          | IFS1<5>  | IEC1<5>                | IPC5<6:4>    |  |  |

| Reserved                              | 30                               | 22    | 0x000040          | _        | 1                      | _            |  |  |

| CCP2 – Input Capture/Output Compare 2 | 31                               | 23    | 0x000042          | IFS1<7>  | IEC1<7>                | IPC5<14:12>  |  |  |

| CCT2 – CCP2 Timer                     | 32                               | 24    | 0x000044          | IFS1<8>  | IEC1<8>                | IPC6<2:0>    |  |  |

| CAN1 – CAN1 Combined Error            | 33                               | 25    | 0x000046          | IFS1<9>  | IEC1<9>                | IPC6<6:4>    |  |  |

| INT3 – External Interrupt 3           | 34                               | 26    | 0x000048          | IFS1<10> | IEC1<10>               | IPC6<10:8>   |  |  |

| U2RX – UART2 Receiver                 | 35                               | 27    | 0x00004A          | IFS1<11> | IEC1<11>               | IPC6<14:12>  |  |  |

| U2TX – UART2 Transmitter              | 36                               | 28    | 0x00004C          | IFS1<12> | IEC1<12>               | IPC7<2:0>    |  |  |

| SPI2RX – SPI2 Receiver                | 37                               | 29    | 0x00004E          | IFS1<13> | IEC1<13>               | IPC7<6:4>    |  |  |

| SPI2TX – SPI2 Transmitter             | 38                               | 30    | 0x000050          | IFS1<14> | IEC1<14>               | IPC7<10:8>   |  |  |

| C1RX – CAN1 RX Data Ready             | 39                               | 31    | 0x000052          | IFS1<15> | IEC1<15>               | IPC7<14:12>  |  |  |

| Reserved                              | 40-42                            | 32-34 | 0x000054-0x000058 | _        | -                      | _            |  |  |

| CCP3 – Input Capture/Output Compare 3 | 43                               | 35    | 0x00005A          | IFS2<3>  | IEC2<3>                | IPC8<14:12>  |  |  |

| CCT3 – CCP3 Timer                     | 44                               | 36    | 0x00005C          | IFS2<4>  | IEC2<4>                | IPC9<2:0>    |  |  |

| SI2C2 - I2C2 Slave Event              | 45                               | 37    | 0x00005E          | IFS2<5>  | IEC2<5>                | IPC9<6:4>    |  |  |

| MI2C2 – I2C2 Master Event             | 46                               | 38    | 0x000060          | IFS2<6>  | IEC2<6>                | IPC9<10:8>   |  |  |

| Reserved                              | 47                               | 39    | 0x000062          | _        | _                      | _            |  |  |

| CCP4 – Input Capture/Output Compare 4 | 48                               | 40    | 0x000064          | IFS2<8>  | IEC2<8>                | IPC10<2:0>   |  |  |

| CCT4 – CCP4 Timer                     | 49                               | 41    | 0x000066          | IFS2<9>  | IEC2<9>                | IPC10<6:4>   |  |  |

| Reserved                              | 50                               | 42    | 0x000068          | _        | _                      | _            |  |  |

| CCP5 – Input Capture/Output Compare 5 | 51                               | 43    | 0x00006A          | IFS2<11> | IEC2<11>               | IPC10<14:12> |  |  |

| CCT5 – CCP5 Timer                     | 52                               | 44    | 0x00006C          | IFS2<12> | IEC2<12>               | IPC11<2:0>   |  |  |

| DMT – Deadman Timer                   | 53                               | 45    | 0x00006E          | IFS2<13> | IEC2<13>               | IPC11<6:4>   |  |  |

| CCP6 - Input Capture/Output Compare 6 | 54                               | 46    | 0x000070          | IFS2<14> | IEC2<14>               | IPC11<10:8>  |  |  |

| CCT6 – CCP6 Timer                     | 55                               | 47    | 0x000072          | IFS2<15> | IEC2<15>               | IPC11<14:12> |  |  |

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|---------|---------|-------|-------|-------|

| NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE | OVBTE | COVTE |

| bit 15 |        |        |         |         |       |       | bit 8 |

| R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|----------|---------|---------|---------|---------|--------|---------|-------|

| SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL | _     |

| bit 7    |         |         |         |         |        |         | bit 0 |

| Legend |  |

|--------|--|

|--------|--|

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **NSTDIS:** Interrupt Nesting Disable bit

1 = Interrupt nesting is disabled0 = Interrupt nesting is enabled

bit 14 **OVAERR:** Accumulator A Overflow Trap Flag bit

1 = Trap was caused by an overflow of Accumulator A

0 = Trap was not caused by an overflow of Accumulator A

bit 13 OVBERR: Accumulator B Overflow Trap Flag bit

1 = Trap was caused by an overflow of Accumulator B

0 = Trap was not caused by an overflow of Accumulator B

bit 12 COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit

1 = Trap was caused by a catastrophic overflow of Accumulator A

0 = Trap was not caused by a catastrophic overflow of Accumulator A

bit 11 COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit

1 = Trap was caused by a catastrophic overflow of Accumulator B

0 = Trap was not caused by a catastrophic overflow of Accumulator B

bit 10 **OVATE:** Accumulator A Overflow Trap Enable bit

1 = Trap overflow of Accumulator A

0 = Trap is disabled

bit 9 **OVBTE:** Accumulator B Overflow Trap Enable bit

1 = Trap overflow of Accumulator B

0 = Trap is disabled

bit 8 **COVTE**: Catastrophic Overflow Trap Enable bit

1 = Trap catastrophic overflow of Accumulator A or B is enabled

0 = Trap is disabled

bit 7 SFTACERR: Shift Accumulator Error Status bit

1 = Math error trap was caused by an invalid accumulator shift

0 = Math error trap was not caused by an invalid accumulator shift

bit 6 **DIV0ERR:** Divide-by-Zero Error Status bit

1 = Math error trap was caused by a divide-by-zero

0 = Math error trap was not caused by a divide-by-zero

bit 5 DMACERR: DMA Controller Trap Status bit

1 = DMAC error trap has occurred

0 = DMAC error trap has not occurred

bit 4 MATHERR: Math Error Status bit

1 = Math error trap has occurred

0 = Math error trap has not occurred

### REGISTER 9-5: PLLDIV: PLL OUTPUT DIVIDER REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   | R/W-0   |

|--------|-----|-----|-----|-----|-----|---------|---------|

| _      | _   | _   | _   | _   | _   | VCODIV1 | VCODIV0 |

| bit 15 |     |     |     |     |     |         | bit 8   |

| U-0   | R/W-1                      | R/W-0                      | R/W-0                      | U-0 | R/W-0                      | R/W-0                      | R/W-1                      |

|-------|----------------------------|----------------------------|----------------------------|-----|----------------------------|----------------------------|----------------------------|

| _     | POST1DIV2 <sup>(1,2)</sup> | POST1DIV1 <sup>(1,2)</sup> | POST1DIV0 <sup>(1,2)</sup> | _   | POST2DIV2 <sup>(1,2)</sup> | POST2DIV1 <sup>(1,2)</sup> | POST2DIV0 <sup>(1,2)</sup> |

| bit 7 |                            |                            |                            |     |                            |                            | bit 0                      |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-8 VCODIV<1:0>: PLL VCO Output Divider Select bits

11 **=** Fvco

10 = Fvco/2

01 = Fvco/3

00 = Fvco/4

bit 7 **Unimplemented:** Read as '0'

bit 6-4 **POST1DIV<2:0>:** PLL Output Divider #1 Ratio bits<sup>(1,2)</sup>

POST1DIV<2:0> can have a valid value, from 1 to 7 (POST1DIVx value should be greater than or equal to the POST2DIVx value). The POST1DIVx divider is designed to operate at higher clock rates than the POST2DIVx divider.

bit 3 Unimplemented: Read as '0'

bit 2-0 POST2DIV<2:0>: PLL Output Divider #2 Ratio bits<sup>(1,2)</sup>

POST2DIV<2:0> can have a valid value, from 1 to 7 (POST2DIVx value should be less than or equal to the POST1DIVx value). The POST1DIVx divider is designed to operate at higher clock rates than the POST2DIVx divider.

- Note 1: The POST1DIVx and POST2DIVx divider values must not be changed while the PLL is operating.

- 2: The default values for POST1DIVx and POST2DIVx are 4 and 1, respectively, yielding a 150 MHz system source clock.

### REGISTER 11-37: C1TEFSTA: CAN TRANSMIT EVENT FIFO STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | S/HC-0  | R-0                   | R-0                   | R-0                    |

|-------|-----|-----|-----|---------|-----------------------|-----------------------|------------------------|

| _     | _   | _   | _   | TEFOVIF | TEFFIF <sup>(1)</sup> | TEFHIF <sup>(1)</sup> | TEFNEIF <sup>(1)</sup> |

| bit 7 |     |     |     |         |                       |                       | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | S = Settable bit Can Set by '1'    |                    |

|-------------------|-----------------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

bit 3 **TEFOVIF:** Transmit Event FIFO Overflow Interrupt Flag bit

1 = Overflow event has occurred0 = No overflow event has occurred

bit 2 **TEFFIF:** Transmit Event FIFO Full Interrupt Flag bit<sup>(1)</sup>

1 = FIFO is full 0 = FIFO is not full

bit 1 **TEFHIF:** Transmit Event FIFO Half Full Interrupt Flag bit<sup>(1)</sup>

1 = FIFO is ≥ half full 0 = FIFO is < half full

bit 0 **TEFNEIF:** Transmit Event FIFO Not Empty Interrupt Flag bit<sup>(1)</sup>

1 = FIFO is not empty 0 = FIFO is empty

Note 1: These bits are read-only and reflect the status of the FIFO.

### REGISTER 12-13: PGxCONH: PWM GENERATOR x CONTROL REGISTER HIGH (CONTINUED)

- bit 6

TRGMOD: PWM Generator Trigger Mode Selection bit

1 = PWM Generator operates in Retriggerable mode

0 = PWM Generator operates in Single Trigger mode

bit 5-4

Unimplemented: Read as '0'

bit 3-0

SOCS<3:0>: Start-of-Cycle Selection bits(1,2,3)

1111 = TRIG bit or PCI Sync function only (no hardware trigger source is selected)

1110-0101 = Reserved

0100 = Trigger output selected by PG4 or PG8 PGTRGSEL<2:0> bits (PGxEVTL<2:0>)

0011 = Trigger output selected by PG3 or PG7 PGTRGSEL<2:0> bits (PGxEVTL<2:0>)

0010 = Trigger output selected by PG2 or PG6 PGTRGSEL<2:0> bits (PGxEVTL<2:0>)

0001 = Trigger output selected by PG1 or PG5 PGTRGSEL<2:0> bits (PGxEVTL<2:0>)

0000 = Local EOC PWM Generator is self-triggered

- **Note 1:** The PCI selected Sync signal is always available to be OR'd with the selected SOC signal per the SOCS<3:0> bits if the PCI Sync function is enabled.

- 2: The source selected by the SOCS<3:0> bits MUST operate from the same clock source as the local PWM Generator. If not, the source must be routed through the PCI Sync logic so the trigger signal may be synchronized to the PWM Generator clock domain.

- **3:** PWM Generators are grouped into groups of four: PG1-PG4 and PG5-PG8, if available. Any generator within a group of four may be used to trigger another generator within the same group.

#### REGISTER 12-30: PGxDTL: PWM GENERATOR x DEAD-TIME REGISTER LOW

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|----------------------|-------|-------|

| _      | _   |       |       | DTL<1 | 13:8> <sup>(1)</sup> |       |       |

| bit 15 |     |       |       |       |                      |       | bit 8 |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|-------|-------|-------|-------|-------|-------|-------|

| DTL<7:0> |       |       |       |       |       |       |       |

| bit 7    |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTL<13:0>: PWMxL Dead-Time Delay bits<sup>(1)</sup>

**Note 1:** DTL<13:11> bits are not available when HREN (PGxCONL<7>) = 0.

### REGISTER 12-31: PGxDTH: PWM GENERATOR x DEAD-TIME REGISTER HIGH

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|----------------------|-------|-------|

| _      | _   |       |       | DTH<1 | 13:8> <sup>(1)</sup> |       |       |

| bit 15 |     |       |       |       |                      |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | DTH   | l<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-0 **DTH<13:0>:** PWMxH Dead-Time Delay bits<sup>(1)</sup>

**Note 1:** DTH<13:11> bits are not available when HREN (PGxCONL<7>) = 0.

### REGISTER 16-13: UxTXCHK: UARTx TRANSMIT CHECKSUM REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | TXCHK<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 |            |       |       |       |       |       | bit 0 |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **TXCHK<7:0>:** Transmit Checksum bits (calculated from TX words)

LIN Modes:

C0EN = 1: Sum of all transmitted data + addition carries, including PID. C0EN = 0: Sum of all transmitted data + addition carries, excluding PID.

LIN Slave:

Cleared when Break is detected.

LIN Master/Slave:

Cleared when Break is detected.

Other Modes:

C0EN = 1: Sum of every byte transmitted + addition carries.

C0EN = 0: Value remains unchanged.

#### REGISTER 16-16: UXSCINT: UARTX SMART CARD INTERRUPT REGISTER

| U-0    | U-0 | R/W-0, HS | R/W-0, HS | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS |

|--------|-----|-----------|-----------|-----|-----------|-----------|-----------|

| _      | _   | RXRPTIF   | TXRPTIF   | _   | BTCIF     | WTCIF     | GTCIF     |

| bit 15 |     |           |           |     |           |           | bit 8     |

| U-0   | U-0 | R/W-0   | R/W-0   | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|---------|---------|-----|-------|-------|-------|

| _     | _   | RXRPTIE | TXRPTIE | _   | BTCIE | WTCIE | GTCIE |

| bit 7 |     |         |         |     |       |       | bit 0 |

Legend:HS = Hardware Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 RXRPTIF: Receive Repeat Interrupt Flag bit

1 = Parity error has persisted after the same character has been received five times (four retransmits)

0 = Flag is cleared

bit 12 **TXRPTIF:** Transmit Repeat Interrupt Flag bit

1 = Line error has been detected after the last retransmit per TXRPT<1:0>

0 = Flag is cleared

bit 11 **Unimplemented:** Read as '0'

bit 9

bit 10 **BTCIF:** Block Time Counter Interrupt Flag bit

1 = Block Time Counter has reached 00 = Block Time Counter has not reached 0

WTCIF: Waiting Time Counter Interrupt Flag bit

1 = Waiting Time Counter has reached 00 = Waiting Time Counter has not reached 0

bit 8 GTCIF: Guard Time Counter Interrupt Flag bit

1 = Guard Time Counter has reached 0

0 = Guard Time Counter has not reached 0

bit 7-6 Unimplemented: Read as '0'

bit 5 RXRPTIE: Receive Repeat Interrupt Enable bit

1 = An interrupt is invoked when a parity error has persisted after the same character has been

received five times (four retransmits)

0 = Interrupt is disabled

bit 4 **TXRPTIE:** Transmit Repeat Interrupt Enable bit

1 = An interrupt is invoked when a line error is detected after the last retransmit per TXRPT<1:0> has

been completed

0 = Interrupt is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2 BTCIE: Block Time Counter Interrupt Enable bit

1 = Block Time Counter interrupt is enabled

0 = Block Time Counter interrupt is disabled

bit 1 WTCIE: Waiting Time Counter Interrupt Enable bit

1 = Waiting Time Counter interrupt is enabled

0 = Waiting Time Counter Interrupt is disabled

bit 0 GTCIE: Guard Time Counter interrupt enable bit

1 = Guard Time Counter interrupt is enabled

0 = Guard Time Counter interrupt is disabled

**NOTES:**

### REGISTER 20-3: SENTxDATL: SENTx RECEIVE DATA REGISTER LOW(1)

| R/W-0  | R/W-0                 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----------------------|-------|-------|-------|-------|-------|-------|

|        | DATA4<3:0> DATA5<3:0> |       |       |       |       |       |       |

| bit 15 |                       |       |       |       |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-------|-------|-------|----------|-------|-------|-------|--|

|       | DATA6 | <3:0> |       | CRC<3:0> |       |       |       |  |

| bit 7 |       |       |       |          |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 DATA4<3:0>: Data Nibble 4 Data bits

bit 11-8 DATA5<3:0>: Data Nibble 5 Data bits

bit 7-4 DATA6<3:0>: Data Nibble 6 Data bits

bit 3-0 CRC<3:0>: CRC Nibble Data bits

**Note 1:** Register bits are read-only in Receive mode (RCVEN = 1). In Transmit mode, the CRC<3:0> bits are read-only when automatic CRC calculation is enabled (RCVEN = 0, CRCEN = 1).

### REGISTER 20-4: SENTxDATH: SENTx RECEIVE DATA REGISTER HIGH<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-------|-------|-------|------------|-------|-------|-------|--|

|        | STAT< | <3:0> |       | DATA1<3:0> |       |       |       |  |

| bit 15 |       |       |       |            |       |       | bit 8 |  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-------|-------|-------|------------|-------|-------|-------|--|

|       | DATA2 | <3:0> |       | DATA3<3:0> |       |       |       |  |

| bit 7 |       |       |       |            |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 STAT<3:0>: Status Nibble Data bits

bit 11-8 DATA1<3:0>: Data Nibble 1 Data bits

bit 7-4 DATA2<3:0>: Data Nibble 2 Data bits

bit 3-0 DATA3<3:0>: Data Nibble 3 Data bits

**Note 1:** Register bits are read-only in Receive mode (RCVEN = 1). In Transmit mode, the CRC<3:0> bits are read-only when automatic CRC calculation is enabled (RCVEN = 0, CRCEN = 1).

### REGISTER 24-11: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | PTGADJ<15:8> |       |       |       |       |       |       |  |  |  |

| bit 15 |              |       |       |       |       |       | bit 8 |  |  |  |

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-------------|-------|-------|-------|-------|-------|-------|--|--|

|       | PTGADJ<7:0> |       |       |       |       |       |       |  |  |

| bit 7 |             |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits

This register holds the user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 register using the PTGADD command.

Note 1: These bits are read-only when the module is executing Step commands.

### REGISTER 24-12: PTGL0: PTG LITERAL 0 REGISTER<sup>(1,2)</sup>

| R/W-0  | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | PTGL0<15:8> |       |       |       |       |       |       |  |  |  |

| bit 15 |             |       |       |       |       |       | bit 8 |  |  |  |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PTGL0<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7      |       |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 15-0 PTGL0<15:0>: PTG Literal 0 Register bits

This register holds the 6-bit value to be written to the CNVCHSEL<5:0> bits (ADCON3L<5:0>) with the PTGCTRL Step command.

- **Note 1:** These bits are read-only when the module is executing Step commands.

- 2: The PTG strobe output is typically connected to the ADC Channel Select register. This allows the PTG to directly control ADC channel switching. See the specific device data sheet for connections of the PTG output.

### TABLE 33-5: OPERATING CURRENT (IDD)(2)

Operating Conditions: 3.0V to 3.6V (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$  for Extended

| -40°C ≤ TA ≤ +125°C for Extended |                     |       |       |        |       |                                                             |  |  |  |

|----------------------------------|---------------------|-------|-------|--------|-------|-------------------------------------------------------------|--|--|--|

| Parameter No.                    | Typ. <sup>(1)</sup> | Max.  | Units |        |       | Conditions                                                  |  |  |  |

| DC20                             | 7.76                | 10.7  | mA    | -40°C  |       |                                                             |  |  |  |

|                                  | 7.49                | 10    | mA    | +25°C  | 3.3V  | 10 MIPS (N1 = 1, N2 = 5, N3 = 2,<br>M = 50, Fvco = 400 MHz, |  |  |  |

|                                  | 7.82                | 12.2  | mA    | +85°C  | 3.34  | FPLLO = 40 MHz)                                             |  |  |  |

|                                  | 10.32               | 20.45 | mA    | +125°C |       | ,                                                           |  |  |  |

| DC21                             | 10.36               | 13.1  | mA    | -40°C  |       |                                                             |  |  |  |

|                                  | 10.09               | 12.45 | mA    | +25°C  | 3.3V  | 20 MIPS (N1 = 1, N2 = 5, N3 = 1,                            |  |  |  |

|                                  | 10.42               | 14.5  | mA    | +85°C  | 3.30  | M = 50, Fvco = 400 MHz,<br>FPLLO = 80 MHz)                  |  |  |  |

|                                  | 12.89               | 23.45 | mA    | +125°C |       |                                                             |  |  |  |

| DC22                             | 14.54               | 17.45 | mA    | -40°C  |       |                                                             |  |  |  |

|                                  | 14.26               | 16.7  | mA    | +25°C  | 3.3V  | 40 MIPS (N1 = 1, N2 = 3, N3 = 1,<br>M = 60, Fvco = 480 MHz, |  |  |  |

|                                  | 14.58               | 18.9  | mA    | +85°C  |       | FPLLO = 160 MHz)                                            |  |  |  |

|                                  | 17.06               | 27.4  | mA    | +125°C |       | <u>,                                      </u>              |  |  |  |

| DC23                             | 22.2                | 25.4  | mA    | -40°C  |       |                                                             |  |  |  |

|                                  | 21.91               | 24.9  | mA    | +25°C  | 3.3V  | 70 MIPS (N1 = 1, N2 = 2, N3 = 1,                            |  |  |  |

|                                  | 22.21               | 27    | mA    | +85°C  | 3.30  | M = 70, Fvco = 560 MHz,<br>Fpllo = 280 MHz)                 |  |  |  |

|                                  | 24.65               | 35.1  | mA    | +125°C |       | 200 1011 127                                                |  |  |  |

| DC24                             | 27.36               | 30.7  | mA    | -40°C  |       |                                                             |  |  |  |

|                                  | 26.96               | 30.5  | mA    | +25°C  | 2 2)/ | 90 MIPS (N1 = 1, N2 = 2, N3 = 1,                            |  |  |  |

|                                  | 26.68               | 31.7  | mA    | +85°C  | 3.3V  | M = 90, Fvco = 720 MHz,<br>Fpllo = 360 MHz)                 |  |  |  |

|                                  | 29.01               | 39.9  | mA    | +125°C |       | 11228 300 1111 127                                          |  |  |  |

| DC25                             | 27.14               | 30.9  | mA    | -40°C  |       |                                                             |  |  |  |

|                                  | 26.54               | 30.1  | mA    | +25°C  | 2 2)/ | 100 MIPS (N1 = 1, N2 = 1,                                   |  |  |  |

|                                  | 26.79               | 31.7  | mA    | +85°C  | 3.3V  | N3 = 1, M = 50, Fvco = 400 MHz,<br>FPLLO = 400 MHz)         |  |  |  |

|                                  | 29.23               | 40    | mA    | +125°C |       |                                                             |  |  |  |

Note 1: Data in the "Typ." column are for design guidance only and are not tested.

- 2: Base Run current (IDD) is measured as follows:

- · Oscillator is switched to EC+PLL mode in software

- OSC1 pin is driven with external 8 MHz square wave with levels from 0.3V to VDD 0.3V

- OSC2 is configured as an I/O in the Configuration Words (OSCIOFCN (FOSC<2>) = 0)

- FSCM is disabled (FCKSM<1:0> (FOSC<7:6>) = 01)

- Watchdog Timer is disabled (FWDT<15> = 0 and WDTCONL<15> = 0)

- · All I/O pins (except OSC1) are configured as outputs and driving low

- No peripheral modules are operating or being clocked (defined PMDx bits are all '1's)

- JTAG is disabled (JTAGEN (FICD<5>) = 0)

- NOP instructions are executed in while(1) loop

### TABLE 33-16: I/O PIN INPUT INJECTION CURRENT SPECIFICATIONS

Operating Conditions: 3.0V to 3.6V (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for Industrial

$-40^{\circ}C \le TA \le +125^{\circ}C$  for Extended

| Param<br>No. | Symbol | Characteristic                                                                 | Min. | Max.                | Units | Conditions                                                                                                                  |

|--------------|--------|--------------------------------------------------------------------------------|------|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| DI60a        | licl   | Input Low Injection Current                                                    | 0    | -5 <sup>(1,4)</sup> | mA    | All pins                                                                                                                    |

| DI60b        | lich   | Input High Injection Current                                                   | 0    | +5(2,3,4)           | mA    | All pins, excepting all 5V tolerant pins and SOSCI                                                                          |

| DI60c        | ∑lict  | Total Input Injection Current (sum of all I/O and control pins) <sup>(5)</sup> | -20  | +20                 | mA    | Absolute instantaneous sum of all $\pm$ input injection currents from all I/O pins (   IICL   +   IICH   ) $\leq \sum$ IICT |

Note 1: VIL Source < (VSS - 0.3).

- 2: VIH Source > (VDD + 0.3) for non-5V tolerant pins only.

- **3:** 5V tolerant pins do not have an internal high-side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- 4: Injection currents can affect the ADC results.

- 5: Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted in the sum.

### TABLE 33-17: I/O PIN OUTPUT SPECIFICATIONS

Operating Conditions: 3.0V to 3.6V (unless otherwise stated)

Operating temperature  $-40^{\circ}C \le TA \le +85^{\circ}C$  for Industrial

-40°C ≤ TA ≤ +125°C for Extended

|        |        | 40 0 3 IA 3 1 IZO 0 II                                      | OI EXICII | aca  |      |       |                          |

|--------|--------|-------------------------------------------------------------|-----------|------|------|-------|--------------------------|

| Param. | Symbol | Characteristic                                              | Min.      | Тур. | Max. | Units | Conditions               |

| DO10   | Vol    | Output Low Voltage<br>4x Sink Driver Pins                   | _         | _    | 0.42 | V     | VDD = 3.6V, IOL < 9 mA   |

|        |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(1)</sup>    | _         | _    | 0.4  | V     | VDD = 3.6V, IOL < 11 mA  |

| DO20   | Vон    | Output High Voltage<br>4x Source Driver Pins                | 2.4       | _    | _    | V     | VDD = 3.6V, IOH > -8 mA  |

|        |        | Output High Voltage<br>8x Source Driver Pins <sup>(1)</sup> | 2.4       | _    | _    | V     | VDD = 3.6V, IOH > -12 mA |

Note 1: 8x sink/source pins are RB1, RC8, RC9 and RD8.

### TABLE 33-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Operating Conditions: 3.0V to 3.6V (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$  for Extended

| Param<br>No. | Symbol  | Characte                      | eristic <sup>(3)</sup>    | Min.            | Max. | Units | Conditions                                  |

|--------------|---------|-------------------------------|---------------------------|-----------------|------|-------|---------------------------------------------|

| IS10         | TLO:SCL | Clock Low Time                | 100 kHz mode              | 4.7             | _    | μs    |                                             |

|              |         |                               | 400 kHz mode              | 1.3             | _    | μs    |                                             |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 0.5             | _    | μs    |                                             |

| IS11         | THI:SCL | Clock High Time               | 100 kHz mode              | 4.0             | _    | μs    | Device must operate at a minimum of 1.5 MHz |

|              |         |                               | 400 kHz mode              | 0.6             | _    | μs    | Device must operate at a minimum of 10 MHz  |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 0.26            | _    | μs    |                                             |

| IS20         | TF:SCL  | SDAx and SCLx                 | 100 kHz mode              | _               | 300  | ns    | CB is specified to be from                  |

|              |         | Fall Time                     | 400 kHz mode              | 20 x (VDD/5.5V) | 300  | ns    | 10 to 400 pF                                |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 20 x (VDD/5.5V) | 120  | ns    |                                             |

| IS21         | TR:SCL  | SDAx and SCLx                 | 100 kHz mode              | _               | 1000 | ns    | CB is specified to be from                  |

|              |         | Rise Time                     | 400 kHz mode              | 20 + 0.1 CB     | 300  | ns    | 10 to 400 pF                                |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | _               | 120  | ns    |                                             |

| IS25         | TSU:DAT | Data Input                    | 100 kHz mode              | 250             |      | ns    |                                             |

|              |         | Setup Time                    | 400 kHz mode              | 100             |      | ns    |                                             |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 50              | _    | ns    |                                             |

| IS26 THD:DA  | THD:DAT | Data Input                    | 100 kHz mode              | 0               |      | μs    |                                             |

|              |         | Hold Time                     | 400 kHz mode              | 0               | 0.9  | μs    |                                             |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 0               | 0.3  | μs    |                                             |

| IS30         | Tsu:sta | Start Condition<br>Setup Time | 100 kHz mode              | 4.7             | _    | μs    | Only relevant for Repeated                  |

|              |         |                               | 400 kHz mode              | 0.6             | _    | μs    | Start condition                             |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 0.26            | _    | μs    |                                             |

| IS31         | THD:STA | Start Condition               | 100 kHz mode              | 4.0             | _    | μs    | After this period, the first                |

|              |         | Hold Time                     | 400 kHz mode              | 0.6             | _    | μs    | clock pulse is generated                    |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 0.26            | _    | μs    |                                             |

| IS33         | Tsu:sto | Stop Condition                | 100 kHz mode              | 4.0             | _    | μs    |                                             |

|              |         | Setup Time                    | 400 kHz mode              | 0.6             | _    | μs    |                                             |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 0.26            |      | μs    |                                             |

| IS34         | THD:STO | Stop Condition                | 100 kHz mode              | >0              | _    | μs    |                                             |

|              |         | Hold Time                     | 400 kHz mode              | >0              | _    | μs    |                                             |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | >0              |      | μs    |                                             |

| IS40         | TAA:SCL | Output Valid from             | 100 kHz mode              | 0               | 3450 | ns    |                                             |

|              |         | Clock                         | 400 kHz mode              | 0               | 900  | ns    |                                             |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 0               | 450  | ns    |                                             |

| IS45         | TBF:SDA | Bus Free Time                 | 100 kHz mode              | 4.7             |      | μs    | Time the bus must be free                   |

|              |         |                               | 400 kHz mode              | 1.3             | _    | μs    | before a new transmission                   |

|              |         |                               | 1 MHz mode <sup>(1)</sup> | 0.5             | _    | μs    | can start                                   |

| IS50         | Св      | Bus Capacitive Lo             | ading                     | _               | 400  | pF    |                                             |

| IS51         | TPGD    | Pulse Gobbler Del             | ay                        | 65              | 390  | ns    | (Note 2)                                    |

Note 1: Maximum Pin Capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**<sup>2:</sup>** Typical value for this parameter is 130 ns.

<sup>3:</sup> These parameters are characterized but not tested in manufacturing.

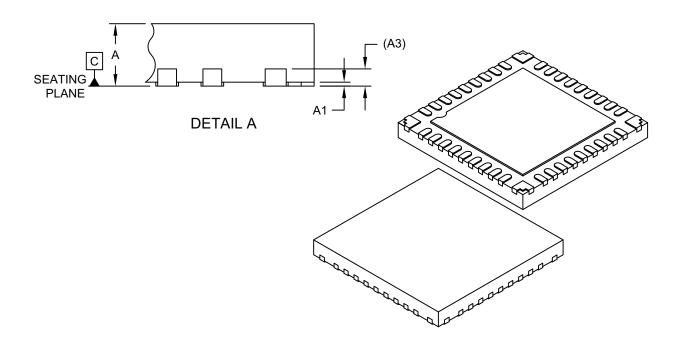

# 36-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M5) - 5x5 mm Body [UQFN] With Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | MILLIMETERS |          |      |  |

|-------------------------|--------|-------------|----------|------|--|

| Dimension               | Limits | MIN         | NOM      | MAX  |  |

| Number of Terminals     | N      |             | 36       |      |  |

| Pitch                   | е      |             | 0.40 BSC |      |  |

| Overall Height          | Α      | 0.50        | 0.55     | 0.60 |  |

| Standoff                | A1     | 0.00        | 0.02     | 0.05 |  |

| Terminal Thickness      | A3     | 0.152 REF   |          |      |  |

| Overall Length          | D      | 5.00 BSC    |          |      |  |

| Exposed Pad Length      | D2     | 3.60        | 3.70     | 3.80 |  |

| Overall Width           | E      | 5.00 BSC    |          |      |  |

| Exposed Pad Width       | E2     | 3.60        | 3.70     | 3.80 |  |

| Terminal Width          | b      | 0.15        | 0.20     | 0.25 |  |

| Terminal Length         | L      | 0.30        | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | K      |             | 0.25 REF |      |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-436A-M5 Sheet 2 of 2

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging D Ε 0.25 C NOTE 1 0.25 C **TOP VIEW** 0.10 C SEATING PLANE C (A3) ○ 0.08 C ◆ 0.10M C A B D2 ⊕ 0.10M C A B (DATUM B) E2 NOTE 1 e/2 (DATUM A) Κ 0.10M C A B 0.05(M) C **BOTTOM VIEW**

Microchip Technology Drawing C04-154A Sheet 1 of 2

| G                                               |      | Interrupt Controller                               |      |

|-------------------------------------------------|------|----------------------------------------------------|------|

| Getting Started Guidelines                      | 23   | Alternate Interrupt Vector Table (AIVT)            |      |

| Connection Requirements                         |      | Control and Status Registers                       | 105  |

| Decoupling Capacitors                           |      | INTCON1                                            |      |

| External Oscillator Pins                        |      | INTCON2                                            | 105  |

| ICSP Pins                                       |      | INTCON3                                            | 105  |

| Master Clear (MCLR) Pin                         |      | INTCON4                                            | 105  |

| Oscillator Value Conditions on Start-up         |      | INTTREG                                            | 105  |

| Targeted Applications                           |      | Interrupt Vector Details                           | 98   |

| Unused I/Os                                     |      | Interrupt Vector Table (IVT)                       | 95   |

| Unused I/Os                                     | 20   | Reset Sequence                                     |      |

| Н                                               |      | Resources                                          |      |

| High-Resolution PWM (HSPWM) with                |      | Interrupt Vector Table                             |      |

| • , , ,                                         | 257  | Interrupts Coincident with Power Save Instructions |      |

| Fine Edge Placement                             | 237  | _                                                  |      |

| High-Speed Analog Comparator with               | 240  | J                                                  |      |

| Slope Compensation DAC                          | 319  | JTAG Boundary Scan Interface                       | 505  |

| High-Speed, 12-Bit Analog-to-Digital            | 20.4 | JTAG Interface                                     |      |

| Converter (ADC)                                 |      |                                                    |      |

| Control Registers                               |      | L                                                  |      |

| Features Overview                               |      | Low-Power Sleep Modes (table)                      | 494  |

| Resources                                       | 293  |                                                    |      |

| HSPWM                                           |      | M                                                  |      |

| Architecture                                    | 258  | Memory Organization                                | 39   |

| Control Registers                               | 259  | Resources                                          |      |

| 1                                               |      | Microchip Internet Web Site                        |      |

| I                                               |      | Modulo Addressing                                  |      |

| I/O Ports                                       |      | Applicability                                      |      |

| Configuring Analog/Digital Port Pins            | 118  | Operation Example                                  |      |

| Control Registers                               | 118  | Start and End Address                              |      |

| Helpful Tips                                    | 136  | W Address Register Selection                       |      |

| Parallel I/O (PIO)                              | 115  |                                                    |      |

| Resources                                       |      | MPLAB REAL ICE In-Circuit Emulator System          | 543  |

| Write/Read Timing                               |      | MPLAB X Integrated Development                     | - 44 |

| l <sup>2</sup> C                                |      | Environment Software                               |      |

| Clock Rates                                     | 393  | MPLINK Object Linker/MPLIB Object Librarian        | 542  |

| Communicating as Master in Single               |      | 0                                                  |      |

| Master Environment                              | 391  |                                                    | 404  |

| Control Registers                               |      | Operational Amplifier                              |      |

| Reserved Addresses                              |      | Control Registers                                  | 482  |

| Setting Baud Rate as Bus Master                 |      | Oscillator                                         |      |

| Slave Address Masking                           |      | Configuration                                      |      |

| ICSP Write Inhibit                              |      | Control Registers                                  |      |

| Activation                                      |      | CPU Clocking                                       |      |

|                                                 |      | Internal Fast RC (FRC)                             |      |

| In-Circuit Debugger MPLAB ICD 3                 |      | Low-Power RC (LPRC)                                |      |

|                                                 |      | Primary (POSC)                                     | 186  |

| PICkit 3 Programmer                             |      | Oscillator with High-Frequency PLL                 | 179  |

| In-Circuit Emulation                            |      | D.                                                 |      |

| In-Circuit Serial Programming (ICSP)            |      | Р                                                  |      |

| Input Change Notification (ICN)                 |      | Packaging                                          | 581  |

| Instruction Addressing Modes                    |      | Details                                            | 583  |

| File Register Instructions                      |      | Marking                                            | 581  |

| Fundamental Modes Supported                     | 69   | Parallel Master Port (PMP)                         |      |

| MAC Instructions                                | 70   | Peripheral Module Disable (PMD)                    |      |

| MCU Instructions                                | 69   | Peripheral Pin Select (PPS)                        |      |

| Move and Accumulator Instructions               | 70   | Available Peripherals                              |      |

| Other Instructions                              | 70   | Available Pins                                     |      |

| Instruction Set Summary                         | 531  | Control                                            |      |

| Overview                                        |      |                                                    |      |

| Symbols Used in Opcode Descriptions             |      | Control Registers                                  |      |

| Instruction-Based Power-Saving Modes            |      | Input Mapping                                      |      |

| Idle                                            |      | Output Mapping                                     |      |

| Sleep                                           |      | Output Selection for Remappable Pins               |      |

| Inter-Integrated Circuit. See I <sup>2</sup> C. |      | Remappable Output Pin Registers                    |      |

| Internet Address                                | 615  | Remappable Pin Inputs                              |      |

| monot / daroo                                   |      | Selectable Input Sources                           | 129  |