#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck128mp502t-i-ss |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33CK256MP508 Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33CK256MP508 devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

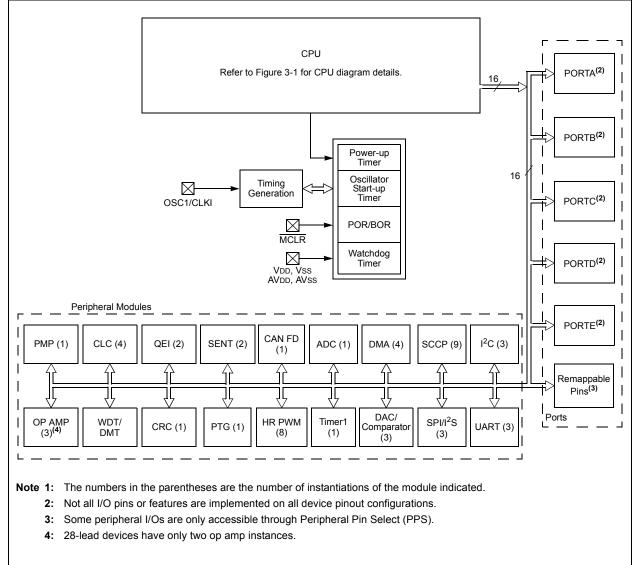

Figure 1-1 shows a general block diagram of the core and peripheral modules of the dsPIC33CK256MP508 family. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

# FIGURE 1-1: dsPIC33CK256MP508 FAMILY BLOCK DIAGRAM<sup>(1)</sup>

|                | 1       |                                         | •             |          |                |           |         |                                         |

|----------------|---------|-----------------------------------------|---------------|----------|----------------|-----------|---------|-----------------------------------------|

| Register       | Address | All Resets                              | Register      | Address  | All Resets     | Register  | Address | All Resets                              |

| UART3          |         |                                         | I2C3TRN       | F70      | 111111111      | WDTCONH   | FB6     | 000000000000000000000000000000000000000 |

| U3MODE         | F00     | 000-0000000000                          | I2C3RCV       | F74      | 00000000       | REFO      |         |                                         |

| U3MODEH        | F02     | 0000000000000                           | Reset and Osc | cillator |                | REFOCONL  | FB8     | 000-000000                              |

| <b>U</b> 3STA  | F04     | 00000001000000                          | RCON          | F80      | xxx01x0xxxxx   | REFOCONH  | FBA     | 000000000000000000000000000000000000000 |

| <b>U3STAH</b>  | F06     | 0000-00000101110                        | OSCCON        | F84      | 0000-yyy0-0-00 | REFOTRIML | FBC     | 00000000                                |

| U3BRG          | F08     | 000000000000000000000000000000000000000 | CLKDIV        | F86      | 00110000000001 | Processor |         |                                         |

| U3BRGH         | F0A     | 0000                                    | PLLFBD        | F88      | 000010010110   | PCTRAPL   | FC0     | *****                                   |

| <b>U3RXREG</b> | F0C     | xxxxxxxx                                | PLLDIV        | F8A      | 00-001-001     | PCTRAPH   | FC2     | xxxxxxx                                 |

| <b>U3TXREG</b> | F10     | xxxxxxxx                                | OSCTUN        | F8C      | 000000         | FEXL      | FC4     | *****                                   |

| U3P1           | F14     | 000000000                               | ACLKCON1      | F8E      | 000-000001     | FEXH      | FC6     | xxxxxxxx                                |

| U3P2           | F16     | 000000000                               | APLLFBD1      | F90      | 000010010110   | FEX2L     | FC8     | *****                                   |

| U3P3           | F18     | 000000000000000000                      | APLLDIV1      | F92      | 00-001-001     | FEX2H     | FCA     | xxxxxxxx                                |

| U3P3H          | F1A     | 00000000                                | CANCLKCON     | F9A      | 00000-000000   | VISI      | FCC     | *****                                   |

| <b>U3TXCHK</b> | F1C     | 00000000                                | DCOTUN        | F9C      | 000000000000   | DPCL      | FCE     | *****                                   |

| <b>U3RXCHK</b> | F1E     | 00000000                                | DCOCON        | F9E      | 0-xxxx         | DPCH      | FD0     | xxxxxxxx                                |

| U3SCCON        | F20     | 00000-                                  | PMD           |          |                | APPO      | FD2     | *****                                   |

| <b>U3SCINT</b> | F22     | 00-00000-000                            | PMD1          | FA4      | 000-0000-00    | APPI      | FD4     | *****                                   |

| <b>U3INT</b>   | F24     | 0                                       | PMD2          | FA6      | 000000000      | APPS      | FD6     | xxxxx                                   |

| I2C3           |         |                                         | PMD3          | FA8      | 00-0-000-      | STROUTL   | FD8     | *****                                   |

| I2C3CONL       | F5C     | 01000000000000                          | PMD4          | FAA      | 0              | STROUTH   | FDA     | *****                                   |

| I2C3CONH       | F5E     | 0000000                                 | PMD6          | FAE      | 0000           | STROVCNT  | FDC     | *****                                   |

| I2C3 STAT      | F60     | 00000000000000                          | PMD7          | FB0      | 0000           | JDATAL    | FFA     | 000000000000000000000000000000000000000 |

| I2C3ADD        | F64     | 0000000000                              | PMD8          | FB2      | 000000000-     | JDATAH    | FFC     | 000000000000000000000000000000000000000 |

| I2C3MSK        | F68     | 0000000000                              | WDT           | •        |                |           |         | •                                       |

| I2C3BRG        | F6C     | 000000000000000000000000000000000000000 | WDTCONL       | FB4      | 00000000000000 |           |         |                                         |

# TABLE 4-16: SFR BLOCK F00h

Legend: x = unknown or indeterminate value; "-" =unimplemented bits; y = value set by Configuration bits. Address values are in hexadecimal. Reset values are in binary.

# 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

| Internuet Course                     | Vector | IRQ |             | In       | Interrupt Bit Location |              |  |  |

|--------------------------------------|--------|-----|-------------|----------|------------------------|--------------|--|--|

| Interrupt Source                     | #      | #   | IVT Address | Flag     | Enable                 | Priority     |  |  |

| QEI1 – QEI Position Counter Compare  | 56     | 48  | 0x000074    | IFS3<0>  | IEC3<0>                | IPC12<2:0>   |  |  |

| U1E – UART1 Error                    | 57     | 49  | 0x000076    | IFS3<1>  | IEC3<1>                | IPC12<6:4>   |  |  |

| U2E – UART2 Error                    | 58     | 50  | 0x000078    | IFS3<2>  | IEC3<2>                | IPC12<10:8>  |  |  |

| CRC – CRC Generator                  | 59     | 51  | 0x00007A    | IFS3<3>  | IEC3<3>                | IPC12<14:12> |  |  |

| C1TX – CAN1 TX Data Request          | 60     | 52  | 0x00007C    | IFS3<4>  | IEC3<4>                | IPC13<2:0>   |  |  |

| Reserved                             | 61     | 53  | 0x00007E    | _        | —                      | _            |  |  |

| QEI2 – QEI Position Counter Compare  | 62     | 54  | 0x000080    | IFS3<6>  | IEC3<6>                | IPC13<10:8>  |  |  |

| Reserved                             | 63     | 55  | 0x000082    | _        | _                      | —            |  |  |

| U3E – UART3 Error                    | 64     | 56  | 0x000084    | IFS3<8>  | IEC3<8>                | IPC14<2:0>   |  |  |

| U3RX – UART3 Receiver                | 65     | 57  | 0x000086    | IFS3<9>  | IEC3<9>                | IPC14<6:4>   |  |  |

| U3TX – UART3 Transmitter             | 66     | 58  | 0x000088    | IFS3<10> | IEC3<10>               | IPC14<10:8>  |  |  |

| SPI3RX – SPI3 Receiver               | 67     | 59  | 0x00008A    | IFS3<11> | IEC3<11>               | IPC14<14:12> |  |  |

| SPI3TX – SPI3 Transmitter            | 68     | 60  | 0x00008C    | IFS3<12> | IEC3<12>               | IPC15<2:0>   |  |  |

| ICD – In-Circuit Debugger            | 69     | 61  | 0x00008E    | IFS3<13> | IEC3<13>               | IPC15<6:4>   |  |  |

| JTAG – JTAG Programming              | 70     | 62  | 0x000090    | IFS3<14> | IEC3<14>               | IPC15<10:8>  |  |  |

| PTGSTEP – PTG Step                   | 71     | 63  | 0x000092    | IFS3<15> | IEC3<15>               | IPC15<14:12> |  |  |

| I2C1BC – I2C1 Bus Collision          | 72     | 64  | 0x000094    | IFS4<0>  | IEC4<0>                | IPC16<2:0>   |  |  |

| I2C2BC – I2C2 Bus Collision          | 73     | 65  | 0x000096    | IFS4<1>  | IEC4<1>                | IPC16<6:4>   |  |  |

| Reserved                             | 74     | 66  | 0x000098    | _        | _                      | _            |  |  |

| PWM1 – PWM Generator 1               | 75     | 67  | 0x00009A    | IFS4<3>  | IEC4<3>                | IPC16<14:12> |  |  |

| PWM2 – PWM Generator 2               | 76     | 68  | 0x00009C    | IFS4<4>  | IEC4<4>                | IPC17<2:0>   |  |  |

| PWM3 – PWM Generator 3               | 77     | 69  | 0x00009E    | IFS4<5>  | IEC4<5>                | IPC17<6:4>   |  |  |

| PWM4 – PWM Generator 4               | 78     | 70  | 0x0000A0    | IFS4<6>  | IEC4<6>                | IPC17<10:8>  |  |  |

| PWM5 – PWM Generator 5               | 79     | 71  | 0x0000A2    | IFS4<7>  | IEC4<7>                | IPC17<14:12> |  |  |

| PWM6 – PWM Generator 6               | 80     | 72  | 0x0000A4    | IFS4<8>  | IEC4<8>                | IPC18<2:0>   |  |  |

| PWM7 – PWM Generator 7               | 81     | 73  | 0x0000A6    | IFS4<9>  | IEC4<9>                | IPC18<6:4>   |  |  |

| PWM8 – PWM Generator 8               | 82     | 74  | 0x0000A8    | IFS4<10> | IEC4<10>               | IPC18<10:8>  |  |  |

| CND – Change Notice D                | 83     | 75  | 0x0000AA    | IFS4<11> | IEC4<11>               | IPC18<14:12> |  |  |

| CNE – Change Notice E                | 84     | 76  | 0x0000AC    | IFS4<12> | IEC4<12>               | IPC19<2:0>   |  |  |

| CMP1 – Comparator 1                  | 85     | 77  | 0x0000AE    | IFS4<13> | IEC4<13>               | IPC19<6:4>   |  |  |

| CMP2 – Comparator 2                  | 86     | 78  | 0x0000B0    | IFS4<14> | IEC4<14>               | IPC19<10:8>  |  |  |

| CMP3 – Comparator 3                  | 87     | 79  | 0x0000B2    | IFS4<15> | IEC4<15>               | IPC19<14:12> |  |  |

| Reserved                             | 88     | 80  | 0x0000B4    | _        | _                      | _            |  |  |

| PTGWDT – PTG Watchdog Timer Time-out | 89     | 81  | 0x0000B6    | IFS5<1>  | IEC5<1>                | IPC20<6:4>   |  |  |

| PTG0 – PTG Trigger 0                 | 90     | 82  | 0x0000B8    | IFS5<2>  | IEC5<2>                | IPC20<10:8>  |  |  |

| PTG1 – PTG Trigger 1                 | 91     | 83  | 0x0000BA    | IFS5<3>  | IEC5<3>                | IPC20<14:12> |  |  |

| PTG2 – PTG Trigger 2                 | 92     | 84  | 0x0000BC    | IFS5<4>  | IEC5<4>                | IPC21<2:0>   |  |  |

| PTG3 – PTG Trigger 3                 | 93     | 85  | 0x0000BE    | IFS5<5>  | IEC5<6>                | IPC21<6:4>   |  |  |

| SENT1 – SENT1 TX/RX                  | 94     | 86  | 0x0000C0    | IFS5<6>  | IEC5<6>                | IPC21<10:8>  |  |  |

| SENT1E – SENT1 Error                 | 95     | 87  | 0x0000C2    | IFS5<7>  | IEC5<7>                | IPC21<14:12> |  |  |

| SENT2 – SENT2 TX/RX                  | 96     | 88  | 0x0000C4    | IFS5<8>  | IEC5<8>                | IPC22<2:0>   |  |  |

| SENT2E – SENT2 Error                 | 97     | 89  | 0x0000C6    | IFS5<9>  | IEC5<9>                | IPC22<6:4>   |  |  |

| ADC – ADC Global Interrupt           | 98     | 90  | 0x0000C8    | IFS5<10> | IEC5<10>               | IPC22<10:8>  |  |  |

# dsPIC33CK256MP508 FAMILY

Equation 9-3 provides the relationship between the APLL Input Frequency (AFPLLI) and the AVCO Output Frequency (AFvCO).

#### EQUATION 9-3: AFvco CALCULATION

$$AFVCO = AFPLLI \times \left(\frac{M}{N1}\right) = AFPLLI \times \left(\frac{APLLFBDIV < 7:0>}{APLLPRE < 3:0>}\right)$$

Equation 9-4 provides the relationship between the APLL Input Frequency (AFPLLI) and APLL Output Frequency (AFPLLO).

#### EQUATION 9-4: AFPLLO CALCULATION

$AFPLLO = AFPLLI \times \left(\frac{M}{N1 \times N2 \times N3}\right) = AFPLLI \times \left(\frac{APLLFBDIV<7:0>}{APLLPRE<3:0> \times APOST1DIV<2:0> \times APOST2DIV<2:0>}\right)$

Where:

M = APLLFBDIV<7:0> N1 = APLLPRE<3:0> N2 = APOST1DIV<2:0> N3 = APOST2DIV<2:0>

# EXAMPLE 9-2: CODE EXAMPLE FOR USING AUXILIARY PLL WITH THE INTERNAL FRC OSCILLATOR

```

//code example for AFVCO = 1 GHz and AFPLLO = 500 MHz using 8 MHz internal FRC

// Configure the source clock for the APLL

ACLKCONIbits.FRCSEL = 1; // Select internal FRC as the clock source

// Configure the APLL prescaler, APLL feedback divider, and both APLL postscalers.

ACLKCONIbits.APLLPRE = 1; // N1 = 1

APLLFBDIbits.APLLFBDIV = 125; // M = 125

APLLDIVIbits.APOST1DIV = 2; // N2 = 2

APLLDIVIbits.APOST2DIV = 1; // N3 = 1

// Enable APLL

ACLKCONIbits.APLLEN = 1;

```

Note: Even with the APLLEN bit set, another peripheral must generate a clock request before the APLL will start.

#### 10.1.6 CHANNEL PRIORITY

Each DMA channel functions independently of the others, but also competes with the others for access to the data and DMA buses. When access collisions occur, the DMA Controller arbitrates between the channels using a user-selectable priority scheme. Two schemes are available:

- Round Robin: When two or more channels collide, the lower numbered channel receives priority on the first collision. On subsequent collisions, the higher numbered channels each receive priority based on their channel number.

- Fixed: When two or more channels collide, the lowest numbered channel always receives priority, regardless of past history; however, any channel being actively processed is not available for an immediate retrigger. If a higher priority channel is continually requesting service, it will be scheduled for service after the next lower priority channel with a pending request.

# 10.2 Typical Setup

To set up a DMA channel for a basic data transfer:

- Enable the DMA Controller (DMAEN = 1) and select an appropriate channel priority scheme by setting or clearing PRSSEL.

- 2. Program DMAH and DMAL with appropriate upper and lower address boundaries for data RAM operations.

- Select the DMA channel to be used and disable its operation (CHEN = 0).

- Program the appropriate source and destination addresses for the transaction into the channel's DMASRCn and DMADSTn registers. For PIA mode addressing, use the base address value.

- Program the DMACNTn register for the number of triggers per transfer (One-Shot or Continuous modes) or the number of words (bytes) to be transferred (Repeated modes).

- 6. Set or clear the SIZE bit to select the data size.

- 7. Program the TRMODE<1:0> bits to select the Data Transfer mode.

- 8. Program the SAMODE<1:0> and DAMODE<1:0> bits to select the addressing mode.

- 9. Enable the DMA channel by setting CHEN.

- 10. Enable the trigger source interrupt.

## 10.3 Peripheral Module Disable

The channels of the DMA Controller can be individually powered down using the Peripheral Module Disable (PMD) registers.

# 10.4 Registers

The DMA Controller uses a number of registers to control its operation. The number of registers depends on the number of channels implemented for a particular device.

There are always four module-level registers (one control and three buffer/address):

- DMACON: DMA Engine Control Register (Register 10-1)

- DMAH and DMAL: DMA High and Low Address Limit Registers

- DMABUF: DMA Transfer Data Buffer

Each of the DMA channels implements five registers (two control and three buffer/address):

- DMACHn: DMA Channel n Control Register (Register 10-2)

- DMAINTn: DMA Channel n Interrupt Register (Register 10-3)

- DMASRCn: DMA Data Source Address Pointer for Channel n Register

- DMADSTn: DMA Data Destination Source for Channel n Register

- DMACNTn: DMA Transaction Counter for Channel n Register

For dsPIC33CK256MP508 devices, there are a total of 34 registers.

| U-0          | U-0           | U-0                                       | U-0 | U-0              | U-0              | U-0            | U-0      |

|--------------|---------------|-------------------------------------------|-----|------------------|------------------|----------------|----------|

| _            |               |                                           |     | <u> </u>         |                  | <u> </u>       | <u> </u> |

| bit 15       |               |                                           |     |                  |                  |                | bit 8    |

|              |               |                                           |     |                  |                  |                |          |

| U-0          | U-0           | U-0                                       | U-0 | U-0              | R/W-0            | R/W-0          | R/W-0    |

| —            | _             | —                                         |     | —                | TSRES            | TSEOF          | TBCEN    |

| bit 7        |               |                                           |     |                  |                  |                | bit 0    |

|              |               |                                           |     |                  |                  |                |          |

| Legend:      |               |                                           |     |                  |                  |                |          |

| R = Readab   | ole bit       | W = Writable b                            | it  | U = Unimple      | mented bit, read | d as '0'       |          |

| -n = Value a | nt POR        | '1' = Bit is set                          |     | '0' = Bit is cle | eared            | x = Bit is unk | nown     |

|              |               |                                           |     |                  |                  |                |          |

| bit 15-3     | Unimplemen    | ted: Read as '0                           | 1   |                  |                  |                |          |

| bit 2        |               | estamp Reset bit                          |     | • •              |                  |                |          |

|              |               | e point of the bit                        | 0   |                  |                  |                |          |

|              |               | e point of Start-o                        |     |                  |                  |                |          |

| bit 1        |               | estamp End-of-F                           | . , |                  |                  |                |          |

|              |               | np when frame is                          |     |                  | ):               |                |          |

|              |               | error until last, b<br>error until the en |     | EOF              |                  |                |          |

|              |               | np at "beginning"                         |     |                  |                  |                |          |

|              |               | cal Frame: At sa                          |     | SOF              |                  |                |          |

|              |               | ame: see TSRES                            | · · | 001              |                  |                |          |

| bit 0        |               | e Base Counter                            |     |                  |                  |                |          |

|              | 1 = Enables   |                                           |     |                  |                  |                |          |

|              | 0 = Stops and |                                           |     |                  |                  |                |          |

|              |               |                                           |     |                  |                  |                |          |

#### REGISTER 11-11: C1TSCONH: CAN TIMESTAMP CONTROL REGISTER HIGH

#### REGISTER 11-12: C1TSCONL: CAN TIMESTAMP CONTROL REGISTER LOW

| U-0                                | U-0   | U-0                                     | U-0   | U-0                                | U-0   | R/W-0 | R/W-0   |  |  |

|------------------------------------|-------|-----------------------------------------|-------|------------------------------------|-------|-------|---------|--|--|

| _                                  |       |                                         |       | _                                  |       | TBCPF | RE<9:8> |  |  |

| bit 15                             | ·     |                                         |       | ·                                  |       |       | bit 8   |  |  |

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0   |  |  |

|                                    |       |                                         | TBCPR | E<7:0>                             |       |       |         |  |  |

| bit 7                              |       |                                         |       |                                    |       |       | bit 0   |  |  |

| Legend:                            |       |                                         |       |                                    |       |       |         |  |  |

| R = Readable                       | bit   | W = Writable bit                        |       | U = Unimplemented bit, read as '0' |       |       |         |  |  |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |                                    |       |       |         |  |  |

bit 15-10 Unimplemented: Read as '0' bit 9-0 TBCPRE<9:0>: CAN Time Base Counter Prescaler bits 1023 = TBC increments every 1024 clocks .... 0 = TBC increments every 1 clock

#### REGISTER 11-27: C1FIFOBAH: CAN MESSAGE MEMORY BASE ADDRESS REGISTER HIGH

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|-----------------|-------|------------------|--------|------------------|-----------------|----------------|-------|

|                 |       |                  | FIFOBA | \<31:24>         |                 |                |       |

| bit 15          |       |                  |        |                  |                 |                | bit 8 |

|                 |       |                  |        |                  |                 |                |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|                 |       |                  | FIFOBA | \<23:16>         |                 |                |       |

| bit 7           |       |                  |        |                  |                 |                | bit 0 |

|                 |       |                  |        |                  |                 |                |       |

| Legend:         |       |                  |        |                  |                 |                |       |

| R = Readable    | bit   | W = Writable bit |        | U = Unimpler     | nented bit, rea | ad as 'O'      |       |

| -n = Value at P | POR   | '1' = Bit is set |        | '0' = Bit is cle | ared            | x = Bit is unk | nown  |

bit 15-0 FIFOBA<31:16>: Message Memory Base Address bits

Defines the base address for the transmit event FIFO followed by the message objects.

#### REGISTER 11-28: C1FIFOBAL: CAN MESSAGE MEMORY BASE ADDRESS REGISTER LOW

| R/W-0                              | R/W-0   | R/W-0       | R/W-0                                             | R/W-0                                                                                              | R/W-0                                                                                                                            | R/W-0                                                                                                                                                                                      |

|------------------------------------|---------|-------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |         | FIFOB.      | A<15:8>                                           |                                                                                                    |                                                                                                                                  |                                                                                                                                                                                            |

|                                    |         |             |                                                   |                                                                                                    |                                                                                                                                  | bit 8                                                                                                                                                                                      |

| R/M/-0                             | R/\\\_0 | R/W/-0      | R/M-0                                             | R/M-0                                                                                              | R-0                                                                                                                              | R-0                                                                                                                                                                                        |

| 1000-0                             | 10,00-0 |             |                                                   | 10.00-0                                                                                            | 11-0                                                                                                                             | 11-0                                                                                                                                                                                       |

|                                    |         |             |                                                   |                                                                                                    |                                                                                                                                  | bit 0                                                                                                                                                                                      |

|                                    |         |             |                                                   |                                                                                                    |                                                                                                                                  |                                                                                                                                                                                            |

|                                    |         |             |                                                   |                                                                                                    |                                                                                                                                  |                                                                                                                                                                                            |

| R = Readable bit W = Writable bit  |         |             | U = Unimplemented bit, read as '0'                |                                                                                                    |                                                                                                                                  |                                                                                                                                                                                            |

| -n = Value at POR '1' = Bit is set |         |             | '0' = Bit is cleared x = Bit is unknown           |                                                                                                    |                                                                                                                                  | nown                                                                                                                                                                                       |

|                                    | R/W-0   | R/W-0 R/W-0 | R/W-0     R/W-0       R/W-0     R/W-0       FIFOE | FIFOBA<15:8>           R/W-0         R/W-0         R/W-0           FIFOBA<7:0>         FIFOBA<7:0> | FIFOBA<15:8>           R/W-0         R/W-0         R/W-0         R/W-0           FIFOBA<7:0>         U = Unimplemented bit, real | FIFOBA<15:8>           R/W-0         R/W-0         R/W-0         R/W-0         R-0           FIFOBA<7:0>           bit         W = Writable bit         U = Unimplemented bit, read as '0' |

bit 15-0 **FIFOBA<15:0>:** Message Memory Base Address bits Defines the base address for the transmit event FIFO followed by the message objects.

# REGISTER 12-9: LOGCONY: COMBINATORIAL PWM LOGIC CONTROL REGISTER $y^{(2)}$

| R/W-0<br>MS2y0 <sup>(1)</sup><br>bit 8<br>R/W-0<br>1LFyD0 <sup>(3)</sup><br>bit 0 |

|-----------------------------------------------------------------------------------|

| bit 8<br>R/W-0<br>ILFyD0 <sup>(3)</sup>                                           |

| R/W-0<br>1LFyD0 <sup>(3)</sup>                                                    |

| 1LFyD0 <sup>(3)</sup>                                                             |

| 1LFyD0 <sup>(3)</sup>                                                             |

|                                                                                   |

| bit C                                                                             |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

|                                                                                   |

- **Note 1:** Logic function input will be connected to '0' if the PWM channel is not present.

- **2:** 'y' denotes a common instance (A-F).

- **3:** Instances of y = A, C, E of LOGCONy assign logic function output to the PWMxL pin. Instances of y = B, D, F of LOGCONy assign logic function to the PWMxH pin.

| U-0          | U-0   | U-0              | U-0   | U-0          | U-0              | R/W-0    | R/W-0  |

|--------------|-------|------------------|-------|--------------|------------------|----------|--------|

| —            |       | —                | _     | —            | —                | TMCE     | 3<9:8> |

| bit 15       |       |                  |       |              |                  |          | bit 8  |

|              |       |                  |       |              |                  |          |        |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

|              |       |                  | TMCI  | B<7:0>       |                  |          |        |

| bit 7        |       |                  |       |              |                  |          | bit 0  |

|              |       |                  |       |              |                  |          |        |

| Legend:      |       |                  |       |              |                  |          |        |

| R = Readable | e bit | W = Writable bit |       | U = Unimpler | nented bit, read | d as '0' |        |

bit 15-10 **Unimplemented:** Read as '0'

-n = Value at POR

bit 9-0 **TMCB<9:0>:** DACx Leading-Edge Blanking bits These register bits specify the blanking period for the comparator, following changes to the DAC output during Change-of-State (COS), for the input signal selected by the HCFSEL<3:0> bits in Register 14-9.

'0' = Bit is cleared

#### REGISTER 14-5: DACxCONL: DACx CONTROL LOW REGISTER

'1' = Bit is set

| R/W-0  | R/W-0                  | R/W-0                  | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  |

|--------|------------------------|------------------------|-----|-----|-------|--------|--------|

| DACEN  | IRQM1 <sup>(1,2)</sup> | IRQM0 <sup>(1,2)</sup> | —   | —   | CBE   | DACOEN | FLTREN |

| bit 15 |                        |                        |     |     |       |        | bit 8  |

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   |

|---------|--------|--------|--------|--------|--------|---------|---------|

| CMPSTAT | CMPPOL | INSEL2 | INSEL1 | INSEL0 | HYSPOL | HYSSEL1 | HYSSEL0 |

| bit 7   |        |        |        |        |        |         | bit 0   |

| Legend:           |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 15 DACEN: Individual DACx Module Enable bit

- 1 = Enables DACx module

- 0 = Disables DACx module to reduce power consumption; any pending Slope mode and/or underflow conditions are cleared

- bit 14-13 IRQM<1:0>: Interrupt Mode select bits<sup>(1,2)</sup>

- 11 = Generates an interrupt on either a rising or falling edge detect

- 10 = Generates an interrupt on a falling edge detect

- 01 = Generates an interrupt on a rising edge detect

- 00 = Interrupts are disabled

- bit 12-11 Unimplemented: Read as '0'

#### **Note 1:** Changing these bits during operation may generate a spurious interrupt.

2: The edge selection is a post-polarity selection via the CMPPOL bit.

#### REGISTER 14-6: DACxDATH: DACx DATA HIGH REGISTER

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|-------|-------|----------|-------|-------|-------|

|                                                                      |       |       | DACD  | AT<15:8> |       |       |       |

| bit 15                                                               |       |       |       |          |       |       | bit 8 |

|                                                                      |       |       |       |          |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |       |       | DACE  | )AT<7:0> |       |       |       |

| bit 7                                                                |       |       |       |          |       |       | bit 0 |

|                                                                      |       |       |       |          |       |       |       |

| Legend:                                                              |       |       |       |          |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |          |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared              |       |       |       |          |       |       |       |

#### bit 15-0 DACDAT<15:0>: DACx Data bits

This register specifies the high DACx data value. Valid values are from 0x0205 to 0x3890.

#### REGISTER 14-7: DACxDATL: DACx DATA LOW REGISTER

| R/W-0         | R/W-0                                                   | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |

|---------------|---------------------------------------------------------|------------------|-------|--------------|------------------|----------|-------|--|--|

|               |                                                         |                  | DACLO | )W<15:8>     |                  |          |       |  |  |

| bit 15        |                                                         |                  |       |              |                  |          | bit 8 |  |  |

|               |                                                         |                  |       |              |                  |          |       |  |  |

| R/W-0         | R/W-0                                                   | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |

|               |                                                         |                  | DACL  | OW<7:0>      |                  |          |       |  |  |

| bit 7         |                                                         |                  |       |              |                  |          | bit 0 |  |  |

|               |                                                         |                  |       |              |                  |          |       |  |  |

| Legend:       |                                                         |                  |       |              |                  |          |       |  |  |

| R = Readable  | e bit                                                   | W = Writable bit |       | U = Unimplen | nented bit, read | d as '0' |       |  |  |

| -n = Value at | -n = Value at POR '1' = Bit is set '0' = Bit is cleared |                  |       |              |                  |          |       |  |  |

#### bit 15-0 DACLOW<15:0>: DACx Low Data bits

In Hysteretic mode, Slope Generator mode and Triangle mode, this register specifies the low data value and/or limit for the DACx module. Valid values are from 0x0205 to 0x3890.

# 15.1 QEI Control and Status Registers

#### REGISTER 15-1: QEIxCON: QEIx CONTROL REGISTER

| R/W-0      | U-0                                                                                              | R/W-0                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                      | R/W-0                                                                                                     | R/W-0                                                                      | R/W-0                                               | R/W-0                                     |  |

|------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------|--|

| QEIEN      | I —                                                                                              | QEISIDL                                                                                                                                                                                                                                                    | PIMOD2 <sup>(1,5)</sup>                                                                                                                                    | PIMOD1 <sup>(1,5)</sup>                                                                                   | PIMOD0 <sup>(1,5)</sup>                                                    | IMV1 <sup>(2)</sup>                                 | IMV0 <sup>(2)</sup>                       |  |

| bit 15     |                                                                                                  |                                                                                                                                                                                                                                                            |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     | bit 8                                     |  |

|            |                                                                                                  |                                                                                                                                                                                                                                                            |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |

| U-0        | R/W-0                                                                                            | R/W-0                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                      | R/W-0                                                                                                     | R/W-0                                                                      | R/W-0                                               | R/W-0                                     |  |

|            | INTDIV2 <sup>(3)</sup>                                                                           | INTDIV1 <sup>(3)</sup>                                                                                                                                                                                                                                     | INTDIV0 <sup>(3)</sup>                                                                                                                                     | CNTPOL                                                                                                    | GATEN                                                                      | CCM1                                                | CCM0                                      |  |

| bit 7      |                                                                                                  |                                                                                                                                                                                                                                                            |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     | bit 0                                     |  |

|            |                                                                                                  |                                                                                                                                                                                                                                                            |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |

| Legend:    |                                                                                                  |                                                                                                                                                                                                                                                            |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |

| R = Read   |                                                                                                  | W = Writable                                                                                                                                                                                                                                               |                                                                                                                                                            | •                                                                                                         | nented bit, read                                                           |                                                     |                                           |  |

| -n = Value | e at POR                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                           |                                                                                                                                                            | '0' = Bit is clea                                                                                         | ared                                                                       | x = Bit is unkr                                     | nown                                      |  |

|            |                                                                                                  |                                                                                                                                                                                                                                                            |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |

| bit 15     |                                                                                                  |                                                                                                                                                                                                                                                            | r Interface Mod                                                                                                                                            | ule Enable bit                                                                                            |                                                                            |                                                     |                                           |  |

|            |                                                                                                  | ounters are ena<br>ounters are dis                                                                                                                                                                                                                         | abled, but SFR                                                                                                                                             | s can be read (                                                                                           | or written                                                                 |                                                     |                                           |  |

| bit 14     |                                                                                                  | ted: Read as '                                                                                                                                                                                                                                             | ,                                                                                                                                                          |                                                                                                           |                                                                            |                                                     |                                           |  |

| bit 13     | •                                                                                                | I Stop in Idle M                                                                                                                                                                                                                                           |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |

|            |                                                                                                  | -                                                                                                                                                                                                                                                          | eration when de                                                                                                                                            | evice enters Id                                                                                           | le mode                                                                    |                                                     |                                           |  |

|            |                                                                                                  |                                                                                                                                                                                                                                                            | ation in Idle mod                                                                                                                                          |                                                                                                           |                                                                            |                                                     |                                           |  |

| bit 12-10  | PIMOD<2:0>:                                                                                      | Position Cour                                                                                                                                                                                                                                              | nter Initialization                                                                                                                                        | n Mode Select                                                                                             | bits <sup>(1,5)</sup>                                                      |                                                     |                                           |  |

|            | 110 = Modulo<br>101 = Resets<br>100 = Second<br>011 = First In<br>010 = Next In<br>001 = Every I | Count mode<br>the position co<br>d Index event a<br>dex event afte<br>adex input even<br>Index input even                                                                                                                                                  | for position cou<br>for position cou<br>ounter when the<br>fter Home even<br>r Home event in<br>the initializes the<br>part resets the p<br>son affect the | nter<br>e position coun<br>t initializes pos<br>nitializes positio<br>position counter<br>osition counter | iter equals the<br>ition counter wi<br>on counter with<br>er with contents | QEIxGEC regis<br>th contents of C<br>contents of QE | ster<br>QEIxIC register<br>EIxIC register |  |

| bit 9-8    | IMV<1:0>: Inc                                                                                    | dex Match Valu                                                                                                                                                                                                                                             | ie bits <sup>(2)</sup>                                                                                                                                     |                                                                                                           |                                                                            |                                                     |                                           |  |

|            | 10 = Index ma<br>01 = Index ma<br>00 = Index ma                                                  | <ul> <li>11 = Index match occurs when QEBx = 1 and QEAx = 1</li> <li>10 = Index match occurs when QEBx = 1 and QEAx = 0</li> <li>01 = Index match occurs when QEBx = 0 and QEAx = 1</li> <li>00 = Index match occurs when QEBx = 0 and QEAx = 0</li> </ul> |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |

| bit 7      | Unimplemen                                                                                       | ted: Read as '                                                                                                                                                                                                                                             | 0'                                                                                                                                                         |                                                                                                           |                                                                            |                                                     |                                           |  |

| Note 1:    | When CCMx = 10 ignored.                                                                          | ) or CCMx = 1                                                                                                                                                                                                                                              | 1, all of the QE                                                                                                                                           | counters oper                                                                                             | ate as timers a                                                            | nd the PIMOD                                        | <2:0> bits are                            |  |

| 2:         | When CCMx = 00<br>POSxCNTL regist                                                                |                                                                                                                                                                                                                                                            | nd QEBx values                                                                                                                                             | s match the Ind                                                                                           | lex Match Value                                                            | e (IMV), the PC                                     | SxCNTH and                                |  |

| 3:         | The selected cloc                                                                                | k rate should b                                                                                                                                                                                                                                            | e at least twice                                                                                                                                           | the expected                                                                                              | maximum quad                                                               | drature count ra                                    | ate.                                      |  |

| -          |                                                                                                  |                                                                                                                                                                                                                                                            |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |

- **4:** Not all devices support this mode.

- **5:** The QCAPEN and HCAPEN bits must be cleared during PIMODx Modes 2 through 7 to ensure proper functionality. Not all devices support HCAPEN.

#### REGISTER 16-4: UxSTAH: UARTx STATUS REGISTER HIGH (CONTINUED)

- bit 2 XON: UART in XON Mode bit Only valid when FLO<1:0> control bits are set to XON/XOFF mode. 1 = UART has received XON 0 = UART has not received XON or XOFF was received

- bit 1 URXBE: UART RX Buffer Empty Status bit

- 1 = Receive buffer is empty; writing '1' when URXEN = 0 will reset the RX FIFO Pointers and counters

0 = Receive buffer is not empty

- bit 0 URXBF: UART RX Buffer Full Status bit

- 1 = Receive buffer is full

- 0 = Receive buffer is not full

- Note 1: The receive watermark interrupt is not set if PERIF or FERIF is set and the corresponding IE bit is set.

| U-0                                | U-0           | U-0                       | U-0                                     | U-0              | U-0              | U-0             | R/W-0          |

|------------------------------------|---------------|---------------------------|-----------------------------------------|------------------|------------------|-----------------|----------------|

|                                    |               |                           |                                         | _                | _                |                 | P1<8>          |

| bit 15                             |               |                           |                                         |                  |                  |                 | bit 8          |

|                                    |               |                           |                                         |                  |                  |                 |                |

| R/W-0                              | R/W-0         | R/W-0                     | R/W-0                                   | R/W-0            | R/W-0            | R/W-0           | R/W-0          |

|                                    |               |                           | P1<                                     | 7:0>             |                  |                 |                |

| bit 7                              |               |                           |                                         |                  |                  |                 | bit 0          |

|                                    |               |                           |                                         |                  |                  |                 |                |

| Legend:                            |               |                           |                                         |                  |                  |                 |                |

| R = Readab                         | le bit        | W = Writable              | bit                                     | U = Unimpler     | nented bit, read | d as '0'        |                |

| -n = Value at POR '1' = Bit is set |               |                           | '0' = Bit is cleared x = Bit is unknown |                  |                  |                 |                |

|                                    |               |                           |                                         |                  |                  |                 |                |

| bit 15-9                           | Unimplemen    | ted: Read as '0           | 3                                       |                  |                  |                 |                |

| bit 8-0                            | P1<8:0>: Par  | ameter 1 bits             |                                         |                  |                  |                 |                |

|                                    | DMX TX:       |                           |                                         |                  |                  |                 |                |

|                                    |               | tes to Transmit           | <ul> <li>– 1 (not includ</li> </ul>     | ling Start code) |                  |                 |                |

|                                    | LIN Master T  |                           |                                         |                  |                  |                 |                |

|                                    |               | nit (bits<5:0>).          |                                         |                  |                  |                 |                |

|                                    |               | s TX with Addre           |                                         |                  | 0 (1.1) - 7 0. ) |                 |                |

|                                    |               | ansmit. A '1' is a        | iutomatically in                        | iserted into bit | 9 (Dits<7:0>).   |                 |                |

|                                    | Smart Card N  |                           | o countor io on                         | aratad an tha h  | it clock where   | noriad in alway | a aqual ta ana |

|                                    | ETU (bits<8:0 | Counter bits. Thi<br>)>). | s counter is op                         |                  |                  | periou is alway | s equal to one |

|                                    | Other Modes   |                           |                                         |                  |                  |                 |                |

|                                    | Not used.     |                           |                                         |                  |                  |                 |                |

|                                    |               |                           |                                         |                  |                  |                 |                |

#### REGISTER 16-9: UxP1: UARTx TIMING PARAMETER 1 REGISTER

# REGISTER 16-17: UXINT: UARTX INTERRUPT REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0, HS | R/W-0, HS | U-0 | U-0 | U-0 | R/W-0 | U-0 | U-0   |

|-----------|-----------|-----|-----|-----|-------|-----|-------|

| WUIF      | ABDIF     | —   | —   | —   | ABDIE | —   | —     |

| bit 7     |           |     |     |     |       |     | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                  |

|----------|-----------------------------------------------------------------------------------------------------------------------------|

| bit 7    | WUIF: Wake-up Interrupt Flag bit                                                                                            |

|          | 1 = Sets when WAKE = 1 and RX makes a '1'-to-'0' transition; triggers event interrupt (must be cleared<br>by software)      |

|          | 0 = WAKE is not enabled or WAKE is enabled, but no wake-up event has occurred                                               |

| bit 6    | ABDIF: Auto-Baud Completed Interrupt Flag bit                                                                               |

|          | 1 = Sets when ABD sequence makes the final '1'-to-'0' transition; triggers event interrupt (must be<br>cleared by software) |

|          | 0 = ABAUD is not enabled or ABAUD is enabled but auto-baud has not completed                                                |