Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$= \cdot \times =$

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 39                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

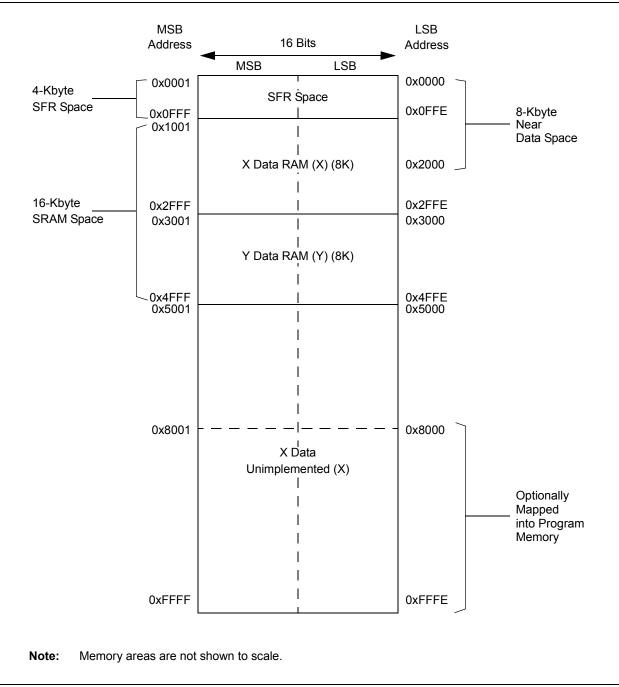

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

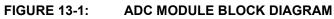

| Data Converters            | A/D 19x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

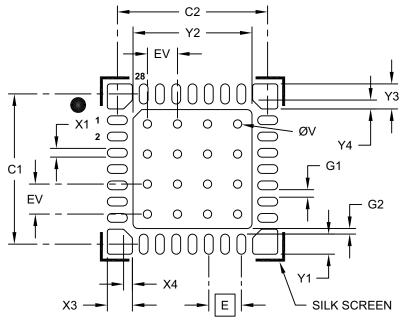

| Mounting Type              | Surface Mount                                                                     |

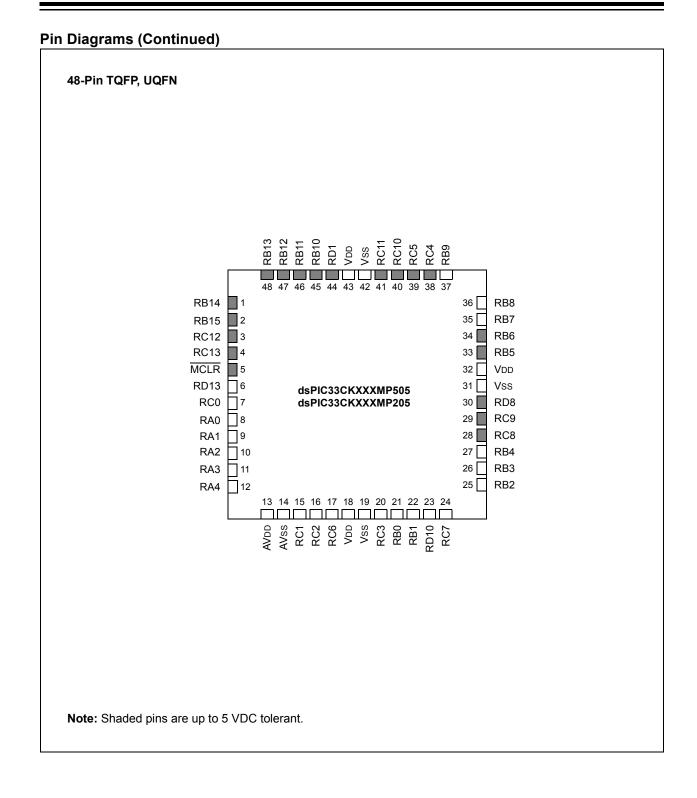

| Package / Case             | 48-TQFP                                                                           |

| Supplier Device Package    | 48-TQFP (7x7)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck128mp505t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33CK256MP508 FAMILY

### FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33CK128MPX0X DEVICES

## REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0      | U-0 | U-0 | U-0   | U-0    | U-0 | U-0 | U-0   |

|----------|-----|-----|-------|--------|-----|-----|-------|

| —        | —   | —   | —     | —      | —   | —   | —     |

| bit 15   |     |     |       |        |     |     | bit 8 |

| W-0      | W-0 | W-0 | W-0   | W-0    | W-0 | W-0 | W-0   |

|          |     |     | NVMKE | Y<7:0> |     |     |       |

| bit 7    |     |     |       |        |     |     | bit 0 |

|          |     |     |       |        |     |     |       |

| l egend: |     |     |       |        |     |     |       |

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** NVM Key Register bits (write-only)

#### REGISTER 5-5: NVMSRCADR: NVM SOURCE DATA ADDRESS REGISTER

| R/W-0                              | R/W-0 | R/W-0            | R/W-0        | R/W-0             | R/W-0    | R/W-0          | R/W-0 |

|------------------------------------|-------|------------------|--------------|-------------------|----------|----------------|-------|

|                                    |       |                  | NVMSRC       | ADR<15:8>         |          |                |       |

| bit 15                             |       |                  |              |                   |          |                | bit 8 |

|                                    |       |                  |              |                   |          |                |       |

| R/W-0                              | R/W-0 | R/W-0            | R/W-0        | R/W-0             | R/W-0    | R/W-0          | R/W-0 |

|                                    |       |                  | NVMSRC       | ADR<7:0>          |          |                |       |

| bit 7                              |       |                  |              |                   |          |                | bit 0 |

|                                    |       |                  |              |                   |          |                |       |

| Legend:                            |       |                  |              |                   |          |                |       |

| R = Readable bit W = Writable bit  |       |                  | U = Unimplem | ented bit, rea    | d as '0' |                |       |

| -n = Value at POR '1' = Bit is set |       | '1' = Bit is set |              | '0' = Bit is clea | ared     | x = Bit is unk | nown  |

### bit 15-0 **NVMSRCADR<15:0>:** NVM Source Data Address bits The RAM address of the data to be programmed into Flash when the NVMOP<3:0> bits are set to row programming.

## REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0                                | U-0 | U-0      | U-0                                     | U-0 | U-0 | U-0    | U-0   |

|------------------------------------|-----|----------|-----------------------------------------|-----|-----|--------|-------|

|                                    | 00  | <u> </u> | 50                                      |     | 50  |        | 50    |

|                                    |     | —        |                                         |     | —   | —      |       |

| bit 15                             |     |          |                                         |     |     |        | bit   |

|                                    |     |          |                                         |     |     |        |       |

| U-0                                | U-0 | U-0      | U-0                                     | U-0 | U-0 | R/W-0  | R/W-0 |

| _                                  | _   | —        | _                                       | —   | —   | ECCDBE | SGHT  |

| bit 7                              |     |          |                                         |     |     |        | bit   |

|                                    |     |          |                                         |     |     |        |       |

| Legend:                            |     |          |                                         |     |     |        |       |

| R = Readable bit W = Writable bit  |     | bit      | U = Unimplemented bit, read as '0'      |     |     |        |       |

| -n = Value at POR '1' = Bit is set |     |          | '0' = Bit is cleared x = Bit is unknown |     |     | iown   |       |

bit 15-2 Unimplemented: Read as '0'

1 = ECC double-bit error trap has occurred

0 = ECC double-bit error trap has not occurred

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

### REGISTER 8-6: CNPUX: CHANGE NOTIFICATION PULL-UP ENABLE FOR PORTX REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|------------------------------------|-------|-------|-------|------------------------------------|-------|-----------------|-------|

|                                    |       |       | CNPL  | Jx<15:8>                           |       |                 |       |

| bit 15                             |       |       |       |                                    |       |                 | bit 8 |

|                                    |       |       |       |                                    |       |                 |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                                    |       |       | CNP   | Jx<7:0>                            |       |                 |       |

| bit 7                              |       |       |       |                                    |       |                 | bit 0 |

|                                    |       |       |       |                                    |       |                 |       |

| Legend:                            |       |       |       |                                    |       |                 |       |

| R = Readable bit W = Writable bit  |       |       | oit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |

bit 15-0 CNPUx<15:0>: Change Notification Pull-up Enable for PORTx bits

1 = The pull-up for PORTx[n] is enabled – takes precedence over the pull-down selection

0 = The pull-up for PORTx[n] is disabled

### REGISTER 8-7: CNPDx: CHANGE NOTIFICATION PULL-DOWN ENABLE FOR PORTx REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| CNPDx<15:8> |       |       |       |       |       |       |       |

| bit 15      |       |       |       |       |       |       | bit 8 |

|             |       |       |       |       |       |       |       |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------|-------|-------|-------|-------|-------|-------|-------|

| CNPDx<7:0> |       |       |       |       |       |       |       |

| bit 7      |       |       |       |       |       | bit 0 |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 CNPDx<15:0>: Change Notification Pull-Down Enable for PORTx bits

1 = The pull-down for PORTx[n] is enabled (if the pull-up for PORTx[n] is not enabled)

0 = The pull-down for PORTx[n] is disabled

## 8.4 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the dsPIC33CK256MP508 family devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State. Five control registers are associated with the Change Notification (CN) functionality of each I/O port. To enable the Change Notification feature for the port, the ON bit (CNCONx<15>) must be set.

The CNEN0x and CNEN1x registers contain the CN interrupt enable control bits for each of the input pins. The setting of these bits enables a CN interrupt for the corresponding pins. Also, these bits, in combination with the CNSTYLE bit (CNCONx<11>), define a type of transition when the interrupt is generated. Possible CN event options are listed in Table 8-3.

#### TABLE 8-3: CHANGE NOTIFICATION EVENT OPTIONS

| CNSTYLE Bit<br>(CNCONx<11>) | CNEN1x<br>Bit      | CNEN0x<br>Bit | Change Notification Event<br>Description                                              |

|-----------------------------|--------------------|---------------|---------------------------------------------------------------------------------------|

| 0                           | Does not<br>matter | 0             | Disabled                                                                              |

| 0                           | Does not<br>matter | 1             | Detects a mismatch between<br>the last read state and the<br>current state of the pin |

| 1                           | 0                  | 0             | Disabled                                                                              |

| 1                           | 0                  | 1             | Detects a positive transition<br>only (from '0' to '1')                               |

| 1                           | 1                  | 0             | Detects a negative transition<br>only (from '1' to '0')                               |

| 1                           | 1                  | 1             | Detects both positive and<br>negative transitions                                     |

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. In addition to the CNSTATx register, the CNFx register is implemented for each port. This register contains flags for Change Notification events. These flags are set if the valid transition edge, selected in the CNEN0x and CNEN1x registers, is detected. CNFx stores the occurrence of the event. CNFx bits must be cleared in software to get the next Change Notification interrupt. The CN interrupt is generated only for the I/Os configured as inputs (corresponding TRISx bits must be set).

| Note: | Pull-ups and pull-downs on Input Change  |

|-------|------------------------------------------|

|       | Notification pins should always be       |

|       | disabled when the port pin is configured |

|       | as a digital output.                     |

## 8.5 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 8.5.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions.

## 8.5.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. One example includes I<sup>2</sup>C modules. A similar requirement excludes all modules with analog inputs, such as the A/D Converter (ADC)

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

# TABLE 8-8: PORTA REGISTER SUMMARY

| Register | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4        | Bit 3 | Bit 2      | Bit 1 | Bit 0 |

|----------|--------|--------|--------|--------|---------|--------|-------|-------|-------|-------|-------|--------------|-------|------------|-------|-------|

| ANSELA   | _      | —      | —      | —      | —       | —      | —     | —     | —     | —     | —     | ANSELA<4:0>  |       |            |       |       |

| TRISA    | _      | _      | _      | _      | —       | —      | —     | _     | —     | —     | —     |              |       | TRISA<4:0> |       |       |

| PORTA    | _      | _      | _      | _      | —       | —      | —     | _     | _     | —     | —     |              |       | RA<4:0>    |       |       |

| LATA     | _      | —      | —      | —      | —       | _      | _     | _     | _     | _     | _     |              |       | LATA<4:0>  |       |       |

| ODCA     | _      | —      | —      | —      | —       | _      | _     | _     | _     | _     | _     |              |       | ODCA<4:0>  |       |       |

| CNPUA    | _      | _      | _      | _      | —       | —      | —     | _     | _     | —     | —     |              | (     | CNPUA<4:0  | >     |       |

| CNPDA    | _      | —      | —      | —      | —       | _      | _     | _     | _     | _     | _     |              | (     | CNPDA<4:0  | >     |       |

| CNCONA   | ON     | —      | —      | —      | CNSTYLE | _      | _     | _     | _     | _     | _     | _            | _     | —          | _     | —     |

| CNEN0A   |        | _      | _      | _      | _       | _      | —     | —     | —     |       |       |              | C     | NEN0A<4:0  | >     |       |

| CNSTATA  | _      | —      | —      | —      | —       | —      | —     | —     | —     | _     | _     | CNSTATA<4:0> |       |            |       |       |

| CNEN1A   |        | —      | _      | _      | _       | —      | —     | _     | —     |       |       | CNEN1A<4:0>  |       |            |       |       |

| CNFA     |        | _      | _      | _      | _       | _      | _     | _     | _     |       |       |              |       | CNFA<4:0>  |       |       |

# TABLE 8-9: PORTB REGISTER SUMMARY

| Register | Bit 15      | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------------|--------|--------|--------|---------|--------|-------|-----------|-------|-------|-------|-------------|-------|-------|-------|-------|

| ANSELB   |             | —      | —      | _      | -       | —      | A     | NSELB<9:  | 7>    | —     | —     | ANSELB<4:0> |       |       |       |       |

| TRISB    | TRISB<15:0> |        |        |        |         |        |       |           |       |       |       |             |       |       |       |       |

| PORTB    |             |        |        |        |         |        | F     | RS<15:0>  |       |       |       |             |       |       |       |       |

| LATB     |             |        |        |        |         |        | LA    | ATB<15:0> |       |       |       |             |       |       |       |       |

| ODCB     |             |        |        |        |         |        | O     | DCB<15:0> | >     |       |       |             |       |       |       |       |

| CNPUB    |             |        |        |        |         |        | CN    | PUB<15:0  | >     |       |       |             |       |       |       |       |

| CNPDB    |             |        |        |        |         |        | CN    | PDB<15:0  | >     |       |       |             |       |       |       |       |

| CNCONB   | ON          | —      | —      | -      | CNSTYLE | _      | —     | _         | _     | _     | —     | _           | _     | _     | _     | _     |

| CNEN0B   |             |        |        |        |         |        | CN    | EN0<15:0  | >     |       |       |             |       |       |       |       |

| CNSTATB  |             |        |        |        |         |        | CNS   | TATB<15:  | 0>    |       |       |             |       |       |       |       |

| CNEN1B   |             |        |        |        |         |        | CNE   | EN1B<15:0 | )>    |       |       |             |       |       |       |       |

| CNFB     | CNFB<15:0>  |        |        |        |         |        |       |           |       |       |       |             |       |       |       |       |

## 12.3 Control Registers

There are two categories of Special Function Registers (SFRs) used to control the operation of the PWM module:

- Common, shared by all PWM Generators

- PWM Generator-specific

An 'x' in the register name denotes an instance of a PWM Generator.

A 'y' in the register name denotes an instance of the common function.

## REGISTER 12-1: PCLKCON: PWM CLOCK CONTROL REGISTER

| R/W-0         | R/W-0                          | U-0                                  | U-0            | U-0                        | U-0           | U-0                              | R/W-0                            |

|---------------|--------------------------------|--------------------------------------|----------------|----------------------------|---------------|----------------------------------|----------------------------------|

| HRRDY         | HRERR                          | —                                    | _              | _                          | _             | —                                | LOCK <sup>(1)</sup>              |

| bit 15        |                                |                                      |                |                            |               |                                  | bit 8                            |

|               |                                | <b>DAALO</b>                         | <b>DAA/O</b>   |                            |               |                                  | DAVA                             |

| U-0           | U-0                            | R/W-0                                | R/W-0          | U-0                        | U-0           | R/W-0<br>MCLKSEL1 <sup>(2)</sup> | R/W-0<br>MCLKSEL0 <sup>(2)</sup> |

|               | _                              | DIVSEL1                              | DIVSEL0        | —                          | —             | MCLKSEL                          |                                  |

| bit 7         |                                |                                      |                |                            |               |                                  | bit 0                            |

| Legend:       |                                |                                      |                |                            |               |                                  |                                  |

| R = Readabl   | le bit                         | W = Writable                         | bit            | U = Unimplei               | mented bit, I | read as '0'                      |                                  |

| -n = Value at | t POR                          | '1' = Bit is set                     |                | '0' = Bit is cle           | ared          | x = Bit is unkno                 | wn                               |

|               |                                |                                      |                |                            |               |                                  |                                  |

| bit 15        | HRRDY: Higl                    | h-Resolution Re                      | eady bit       |                            |               |                                  |                                  |

|               | 0                              | resolution circ                      |                |                            |               |                                  |                                  |

|               | •                              | n-resolution circ                    |                | ady                        |               |                                  |                                  |

| bit 14        | •                              | h-Resolution E                       |                |                            |               |                                  |                                  |

|               |                                | has occurred; has occurred;          |                |                            |               | en HRRDY = 1                     |                                  |

| bit 13-9      |                                | nted: Read as '                      |                |                            |               |                                  |                                  |

| bit 8         | LOCK: Lock                     | bit <sup>(1)</sup>                   |                |                            |               |                                  |                                  |

|               | •                              | otected register<br>otected register |                |                            |               |                                  |                                  |

| bit 7-6       | Unimplemer                     | nted: Read as '                      | 0'             |                            |               |                                  |                                  |

| bit 5-4       | DIVSEL<1:0                     | >: PWM Clock                         | Divider Select | ion bits                   |               |                                  |                                  |

|               | 11 = Divide r                  |                                      |                |                            |               |                                  |                                  |

|               | 10 = Divide r                  |                                      |                |                            |               |                                  |                                  |

|               | 01 = Divide r<br>00 = Divide r |                                      |                |                            |               |                                  |                                  |

| bit 3-2       |                                | nted: Read as '                      | 0'             |                            |               |                                  |                                  |

| bit 1-0       | MCLKSEL<1                      | I:0>: PWM Mas                        | ster Clock Sel | ection bits <sup>(2)</sup> |               |                                  |                                  |

|               |                                | – Auxiliary PLL                      |                |                            |               |                                  |                                  |

|               |                                | Primary PLL p                        |                | tput                       |               |                                  |                                  |

|               | 01 = AFVCO/2<br>00 = Fosc      | 2 – Auxiliary V(                     | 5012           |                            |               |                                  |                                  |

|               |                                |                                      |                |                            |               |                                  |                                  |

| Note 1: A     | device-specific ι              | unlock sequenc                       | e must be per  | tormed before              | this bit can  | be cleared.                      |                                  |

2: Changing the MCLKSEL<1:0> bits while ON (PGxCONL<15>) = 1 is not recommended.

| R/W-0                                                                      | ) r-0                                                                                     | U-0                                                                                                | U-0                                                                                        | U-0                                                                                                              | R/W-0                                                                                       | R/W-0              | R/W-0            |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------|------------------|

| ON                                                                         | _                                                                                         |                                                                                                    | _                                                                                          | _                                                                                                                | TRGCNT2                                                                                     | TRGCNT1            | TRGCNT0          |

| bit 15                                                                     |                                                                                           |                                                                                                    |                                                                                            |                                                                                                                  |                                                                                             |                    | bit 8            |

|                                                                            |                                                                                           |                                                                                                    | DANO                                                                                       | DAALO                                                                                                            | DAMA                                                                                        | <b>D</b> 444 0     | DAVA             |

| R/W-0                                                                      |                                                                                           | U-0                                                                                                | R/W-0                                                                                      | R/W-0                                                                                                            | R/W-0                                                                                       | R/W-0              | R/W-0            |

| HREN                                                                       | —                                                                                         | _                                                                                                  | CLKSEL1                                                                                    | CLKSEL0                                                                                                          | MODSEL2                                                                                     | MODSEL1            | MODSEL0          |

| bit 7                                                                      |                                                                                           |                                                                                                    |                                                                                            |                                                                                                                  |                                                                                             |                    | bit 0            |

| Legend:                                                                    |                                                                                           | r = Reserved                                                                                       | bit                                                                                        |                                                                                                                  |                                                                                             |                    |                  |

| R = Reada                                                                  | able bit                                                                                  | W = Writable                                                                                       | bit                                                                                        | U = Unimplei                                                                                                     | mented bit, read                                                                            | l as '0'           |                  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                                                           |                                                                                                    |                                                                                            |                                                                                                                  |                                                                                             |                    | nown             |

| bit 15                                                                     | <b>ON:</b> Enable b                                                                       | bit<br>enerator is ena                                                                             | blod                                                                                       |                                                                                                                  |                                                                                             |                    |                  |

|                                                                            | _                                                                                         | enerator is not                                                                                    |                                                                                            |                                                                                                                  |                                                                                             |                    |                  |

| bit 14                                                                     | Reserved: M                                                                               | <b>/aintain as</b> '0'                                                                             |                                                                                            |                                                                                                                  |                                                                                             |                    |                  |

| bit 13-11                                                                  | Unimplemer                                                                                | nted: Read as                                                                                      | '0'                                                                                        |                                                                                                                  |                                                                                             |                    |                  |

| bit 10-8                                                                   | -                                                                                         | 0>: Trigger Co                                                                                     |                                                                                            |                                                                                                                  |                                                                                             |                    |                  |

| bit 7                                                                      | 100 = PWM<br>011 = PWM<br>010 = PWM<br>001 = PWM<br>000 = PWM<br>HREN: PWM                | Generator pro<br>Generator pro<br>Generator pro<br>Generator pro<br>Generator pro<br>Generator pro | duces 5 PWM<br>duces 4 PWM<br>duces 3 PWM<br>duces 2 PWM<br>duces 1 PWM<br>ligh-Resolution | cycles after tri<br>cycles after tri<br>cycles after tri<br>cycles after tri<br>cycle after trig<br>n Enable bit | ggered<br>ggered<br>ggered<br>ggered<br>gered                                               |                    |                  |

|                                                                            |                                                                                           | enerator x oper<br>enerator x oper                                                                 | •                                                                                          |                                                                                                                  | le                                                                                          |                    |                  |

| bit 6-5                                                                    | Unimplemer                                                                                | nted: Read as                                                                                      | '0'                                                                                        |                                                                                                                  |                                                                                             |                    |                  |

| bit 4-3                                                                    | CLKSEL<1:0                                                                                | 0>: Clock Sele                                                                                     | ction bits                                                                                 |                                                                                                                  |                                                                                             |                    |                  |

|                                                                            | 10 = PWM G<br>01 = PWM G                                                                  | Generator uses<br>Generator uses l                                                                 | Master clock c<br>Master clock se                                                          | livided by cloc<br>lected by the N                                                                               | uency scaling cir<br>k divider circuit <sup>(:</sup><br>//CLKSEL<1:0> (<br>wer state (defau | 1)<br>(PCLKCON<1:( | 0>) control bits |

| bit 2-0                                                                    | MODSEL<2:                                                                                 | :0>: Mode Sele                                                                                     | ection bits                                                                                |                                                                                                                  |                                                                                             |                    |                  |

|                                                                            | 110 = Dual E<br>101 = Doubl<br>100 = Cente<br>011 = Reser<br>010 = Indepe<br>001 = Variab | Edge Center-Al<br>e-Update Cent<br>er-Aligned PWN                                                  | ligned PWM m<br>er-Aligned PW<br>1 mode<br>WM mode, dua<br>1 mode                          | ode (interrupt/<br>M mode                                                                                        | register update<br>register update                                                          |                    |                  |

| Note 1:                                                                    | The PWM Genera<br>duty cycle and per                                                      |                                                                                                    | •                                                                                          |                                                                                                                  | scaling circuit cl                                                                          | ock, effectively   | scaling the      |

## REGISTER 12-12: PGxCONL: PWM GENERATOR x CONTROL REGISTER LOW

## REGISTER 12-19: PGxyPCIL: PWM GENERATOR xy PCI REGISTER LOW (x = PWM GENERATOR #; y = F, CL, FF OR S)

|              | •                            |                  |                                 | -1, 02, 11         | ,                                       |                   |                    |

|--------------|------------------------------|------------------|---------------------------------|--------------------|-----------------------------------------|-------------------|--------------------|

| R/W-0        | R/W-0                        | R/W-0            | R/W-0                           | R/W-0              | R/W-0                                   | R/W-0             | R/W-0              |

| TSYNCDIS     | TERM2                        | TERM1            | TERM0                           | AQPS               | AQSS2                                   | AQSS1             | AQSS0              |

| bit 15       |                              |                  |                                 |                    |                                         |                   | bit 8              |

|              |                              |                  |                                 |                    |                                         |                   |                    |

| R/W-0        | R/W-0                        | R/W-0            | R/W-0                           | R/W-0              | R/W-0                                   | R/W-0             | R/W-0              |

| SWTERM       | PSYNC                        | PPS              | PSS4                            | PSS3               | PSS2                                    | PSS1              | PSS0               |

| bit 7        |                              |                  |                                 |                    |                                         |                   | bit (              |

|              |                              |                  |                                 |                    |                                         |                   |                    |

| Legend:      |                              |                  |                                 |                    |                                         |                   |                    |

| R = Readat   | ole bit                      | W = Writable     | bit                             | U = Unimpler       | mented bit, read a                      | as '0'            |                    |

| -n = Value a | at POR                       | '1' = Bit is se  | t                               | '0' = Bit is cle   | ared                                    | x = Bit is unkn   | iown               |

| bit 15       |                              |                  | ynchronization                  |                    |                                         |                   |                    |

|              | 0 = Termina                  | tion of latched  | PCI occurs at                   | PWM EOC            |                                         |                   |                    |

| bit 14-12    | TERM<2:0>                    | : Termination I  | Event Selection                 | bits               |                                         |                   |                    |

|              | 00000                        | ts PCI Source    |                                 |                    |                                         |                   |                    |

|              |                              | ts PCI Source    |                                 | orator output s    | elected by the PV                       |                   | -)                 |

|              |                              | RIGC trigger e   |                                 |                    |                                         | VIVIF CI~2.02 Dia | <b>&gt;</b> )      |

|              |                              | RIGB trigger e   |                                 |                    |                                         |                   |                    |

|              |                              | RIGA trigger e   |                                 |                    |                                         |                   |                    |

|              |                              |                  |                                 |                    | sitions from active<br>the SWTERM bit I |                   |                    |

| bit 11       |                              |                  | er Polarity Sele                |                    |                                         | ocation           |                    |

| Dit 11       | 1 = Inverted<br>0 = Not inve |                  | er i olanty Sele                |                    |                                         |                   |                    |

| bit 10-8     | AQSS<2:0>                    | : Acceptance     | Qualifier Source                | e Selection bits   |                                         |                   |                    |

|              |                              | -                | nly (qualifier fo               |                    |                                         |                   |                    |

|              |                              | ts PCI Source    |                                 |                    |                                         |                   |                    |

|              |                              | ts PCI Source    |                                 | orator output of   | plaated by the DV                       | WMDC1-2.05 hite   |                    |

|              |                              | Generator is f   |                                 |                    | elected by the PV                       |                   | <b>&gt;</b> )      |

|              | 010 = LEB is                 |                  | inggoroa                        |                    |                                         |                   |                    |

|              |                              |                  |                                 | enerator signal)   |                                         |                   |                    |

|              |                              |                  |                                 | ualifier forced to | oʻ1')                                   |                   |                    |

| bit 7        |                              | CI Software T    |                                 |                    |                                         |                   |                    |

|              |                              |                  | •                               | a termination ev   | ent. This bit loca                      | tion always read  | <b>Is as '</b> 0'. |

| bit 6        |                              | -                | ion Control bit                 |                    |                                         |                   |                    |

|              |                              |                  | nized to PWM<br>chronized to PV |                    |                                         |                   |                    |

| bit 5        | PPS: PCI Pc                  | plarity Select b | it                              |                    |                                         |                   |                    |

|              | 1 = Inverted                 |                  |                                 |                    |                                         |                   |                    |

|              | 0 = Not inve                 |                  |                                 |                    |                                         |                   |                    |

# dsPIC33CK256MP508 FAMILY

## 15.1 QEI Control and Status Registers

#### REGISTER 15-1: QEIxCON: QEIx CONTROL REGISTER

| R/W-0      | U-0                                                                                              | R/W-0                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                      | R/W-0                                                                                                     | R/W-0                                                                      | R/W-0                                               | R/W-0                                     |  |  |

|------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------|--|--|

| QEIEN      | I —                                                                                              | QEISIDL                                                                                                                                                                                                                                                                 | PIMOD2 <sup>(1,5)</sup>                                                                                                                                    | PIMOD1 <sup>(1,5)</sup>                                                                                   | PIMOD0 <sup>(1,5)</sup>                                                    | IMV1 <sup>(2)</sup>                                 | IMV0 <sup>(2)</sup>                       |  |  |

| bit 15     |                                                                                                  |                                                                                                                                                                                                                                                                         |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     | bit 8                                     |  |  |

|            |                                                                                                  |                                                                                                                                                                                                                                                                         |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |  |

| U-0        | R/W-0                                                                                            | R/W-0                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                      | R/W-0                                                                                                     | R/W-0                                                                      | R/W-0                                               | R/W-0                                     |  |  |

|            | INTDIV2 <sup>(3)</sup>                                                                           | INTDIV1 <sup>(3)</sup>                                                                                                                                                                                                                                                  | INTDIV0 <sup>(3)</sup>                                                                                                                                     | CNTPOL                                                                                                    | GATEN                                                                      | CCM1                                                | CCM0                                      |  |  |

| bit 7      |                                                                                                  |                                                                                                                                                                                                                                                                         |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     | bit 0                                     |  |  |

|            |                                                                                                  |                                                                                                                                                                                                                                                                         |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |  |

| Legend:    |                                                                                                  |                                                                                                                                                                                                                                                                         |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |  |

| R = Read   |                                                                                                  | W = Writable                                                                                                                                                                                                                                                            |                                                                                                                                                            | •                                                                                                         | nented bit, read                                                           |                                                     |                                           |  |  |

| -n = Value | e at POR                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                                        |                                                                                                                                                            | '0' = Bit is clea                                                                                         | ared                                                                       | x = Bit is unkr                                     | nown                                      |  |  |

|            |                                                                                                  |                                                                                                                                                                                                                                                                         |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |  |

| bit 15     |                                                                                                  |                                                                                                                                                                                                                                                                         | r Interface Mod                                                                                                                                            | ule Enable bit                                                                                            |                                                                            |                                                     |                                           |  |  |

|            |                                                                                                  | <ul> <li>1 = Module counters are enabled</li> <li>0 = Module counters are disabled, but SFRs can be read or written</li> </ul>                                                                                                                                          |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |  |

| bit 14     |                                                                                                  | ted: Read as '                                                                                                                                                                                                                                                          | ,                                                                                                                                                          |                                                                                                           |                                                                            |                                                     |                                           |  |  |

| bit 13     | •                                                                                                | I Stop in Idle M                                                                                                                                                                                                                                                        |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |  |

|            |                                                                                                  | -                                                                                                                                                                                                                                                                       | eration when de                                                                                                                                            | evice enters Id                                                                                           | le mode                                                                    |                                                     |                                           |  |  |

|            |                                                                                                  |                                                                                                                                                                                                                                                                         | ation in Idle mod                                                                                                                                          |                                                                                                           |                                                                            |                                                     |                                           |  |  |

| bit 12-10  | PIMOD<2:0>:                                                                                      | Position Cour                                                                                                                                                                                                                                                           | nter Initialization                                                                                                                                        | n Mode Select                                                                                             | bits <sup>(1,5)</sup>                                                      |                                                     |                                           |  |  |

|            | 110 = Modulo<br>101 = Resets<br>100 = Second<br>011 = First In<br>010 = Next In<br>001 = Every I | Count mode<br>the position co<br>d Index event a<br>dex event afte<br>adex input even<br>Index input even                                                                                                                                                               | for position cou<br>for position cou<br>ounter when the<br>fter Home even<br>r Home event in<br>the initializes the<br>part resets the p<br>son affect the | nter<br>e position coun<br>t initializes pos<br>nitializes positio<br>position counter<br>osition counter | iter equals the<br>ition counter wi<br>on counter with<br>er with contents | QEIxGEC regis<br>th contents of C<br>contents of QE | ster<br>QEIxIC register<br>EIxIC register |  |  |

| bit 9-8    | IMV<1:0>: Inc                                                                                    | dex Match Valu                                                                                                                                                                                                                                                          | ie bits <sup>(2)</sup>                                                                                                                                     |                                                                                                           |                                                                            |                                                     |                                           |  |  |

|            | 10 = Index ma<br>01 = Index ma<br>00 = Index ma                                                  | IMV<1:0>: Index Match Value bits <sup>(2)</sup><br>11 = Index match occurs when QEBx = 1 and QEAx = 1<br>10 = Index match occurs when QEBx = 1 and QEAx = 0<br>01 = Index match occurs when QEBx = 0 and QEAx = 1<br>00 = Index match occurs when QEBx = 0 and QEAx = 0 |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |  |

| bit 7      | Unimplemen                                                                                       | ted: Read as '                                                                                                                                                                                                                                                          | 0'                                                                                                                                                         |                                                                                                           |                                                                            |                                                     |                                           |  |  |

| Note 1:    | When CCMx = 10 ignored.                                                                          | ) or CCMx = 1                                                                                                                                                                                                                                                           | 1, all of the QE                                                                                                                                           | counters oper                                                                                             | ate as timers a                                                            | nd the PIMOD                                        | <2:0> bits are                            |  |  |

| 2:         | When CCMx = 00<br>POSxCNTL regist                                                                |                                                                                                                                                                                                                                                                         | nd QEBx values                                                                                                                                             | s match the Ind                                                                                           | lex Match Value                                                            | e (IMV), the PC                                     | SxCNTH and                                |  |  |

| 3:         | The selected cloc                                                                                | k rate should b                                                                                                                                                                                                                                                         | e at least twice                                                                                                                                           | the expected                                                                                              | maximum quad                                                               | drature count ra                                    | ate.                                      |  |  |

| -          |                                                                                                  |                                                                                                                                                                                                                                                                         |                                                                                                                                                            |                                                                                                           |                                                                            |                                                     |                                           |  |  |

- **4:** Not all devices support this mode.

- **5:** The QCAPEN and HCAPEN bits must be cleared during PIMODx Modes 2 through 7 to ensure proper functionality. Not all devices support HCAPEN.

| IADLE 10-2. I |         |                                        |

|---------------|---------|----------------------------------------|

| Slave Address | R/W Bit | Description                            |

| 0000 000      | 0       | General Call Address <sup>(2)</sup>    |

| 0000 0000     | 1       | Start Byte                             |

| 0000 001      | х       | Cbus Address                           |

| 0000 01x      | х       | Reserved                               |

| 0000 1xx      | x       | HS Mode Master Code                    |

| 1111 0xx      | x       | 10-Bit Slave Upper Byte <sup>(3)</sup> |

| 1111 1xx      | х       | Reserved                               |

## TABLE 18-2: I2Cx RESERVED ADDRESSES<sup>(1)</sup>

**Note 1:** The address bits listed here will never cause an address match independent of address mask settings.

2: This address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

### REGISTER 19-7: PMDIN1: PARALLEL MASTER PORT DATA INPUT/OUTPUT LOW REGISTER

| R/W-0                          | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|--------------------------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                                |       |                  | DATA  | IN<15:8>         |                 |                 |       |

| bit 15                         |       |                  |       |                  |                 |                 | bit 8 |

|                                |       |                  |       |                  |                 |                 |       |

| R/W-0                          | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                                |       |                  | DATA  | AIN<7:0>         |                 |                 |       |

| bit 7                          |       |                  |       |                  |                 |                 | bit 0 |

|                                |       |                  |       |                  |                 |                 |       |