Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 29                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-UFQFN Exposed Pad                                                              |

| Supplier Device Package    | 36-UQFN (5x5)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck256mp203t-i-m5 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33CK256MP508 family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

| Note: | The actual set of peripheral features and     |

|-------|-----------------------------------------------|

|       | interrupts varies by the device. Refer to the |

|       | corresponding device tables and pinout        |

|       | diagrams for device-specific information.     |

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

| Register | Address | All Resets         | Register | Address | All Resets         | Register | Address | All Resets   |

|----------|---------|--------------------|----------|---------|--------------------|----------|---------|--------------|

| PPS      |         |                    | RPINR21  | D2E     | 111111111111111111 | RPOR4    | D88     | 000000000000 |

| RPCON    | D00     | 0                  | RPINR22  | D30     | 111111111111111111 | RPOR5    | D8A     | 000000000000 |

| RPINR0   | D04     | 11111111           | RPINR23  | D32     | 111111111          | RPOR6    | D8C     | 000000000000 |

| RPINR1   | D06     | 111111111111111111 | RPINR26  | D38     | 111111111          | RPOR7    | D8E     | 000000000000 |

| RPINR2   | D08     | 11111111           | RPINR27  | D3A     | 111111111111111111 | RPOR8    | D90     | 000000000000 |

| RPINR3   | D0A     | 111111111111111111 | RPINR29  | D3E     | 111111111111111111 | RPOR9    | D92     | 000000000000 |

| RPINR4   | D0C     | 111111111111111111 | RPINR30  | D40     | 111111111          | RPOR10   | D94     | 000000000000 |

| RPINR5   | D0E     | 111111111111111111 | RPINR32  | D44     | 11111111           | RPOR11   | D96     | 000000000000 |

| RPINR6   | D10     | 111111111111111111 | RPINR33  | D46     | 111111111          | RPOR12   | D98     | 000000000000 |

| RPINR7   | D12     | 111111111111111111 | RPINR37  | D4E     | 111111111111111111 | RPOR13   | D9A     | 000000000000 |

| RPINR8   | D14     | 111111111111111111 | RPINR38  | D50     | 111111111          | RPOR14   | D9C     | 000000000000 |

| RPINR9   | D16     | 111111111111111111 | RPINR42  | D58     | 111111111111111111 | RPOR15   | D9E     | 000000000000 |

| RPINR10  | D18     | 111111111111111111 | RPINR43  | D5A     | 111111111111111111 | RPOR16   | DA0     | 000000000000 |

| RPINR11  | D1A     | 111111111111111111 | RPINR44  | D5C     | 111111111111111111 | RPOR17   | DA2     | 000000000000 |

| RPINR12  | D1C     | 111111111111111111 | RPINR45  | D5E     | 111111111111111111 | RPOR18   | DA4     | 000000000000 |

| RPINR13  | D1E     | 111111111111111111 | RPINR46  | D60     | 111111111111111111 | RPOR19   | DA6     | 000000000000 |

| RPINR14  | D20     | 111111111111111111 | RPINR47  | D62     | 111111111111111111 | RPOR20   | DA8     | 000000000000 |

| RPINR15  | D22     | 111111111111111111 | RPINR48  | D64     | 111111111111111111 | RPOR21   | DAA     | 000000000000 |

| RPINR16  | D24     | 111111111111111111 | RPINR49  | D66     | 111111111          | RPOR22   | DAC     | 000000000000 |

| RPINR17  | D26     | 111111111111111111 | RPOR0    | D80     | 000000000000       | RPOR23   | DAE     | 000000000000 |

| RPINR18  | D28     | 111111111111111111 | RPOR1    | D82     | 000000000000       | RPOR24   | DB0     | 000000000000 |

| RPINR19  | D2A     | 111111111111111111 | RPOR2    | D84     | 000000000000       | RPOR25   | DB2     | 000000000000 |

| RPINR20  | D2C     | 111111111111111111 | RPOR3    | D86     | 000000000000       | RPOR26   | DB4     | 000000000000 |

## TABLE 4-14: SFR BLOCK D00h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address values are in hexadecimal. Reset values are in binary.

## 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0                               | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0    | U-0   |  |

|-----------------------------------|-----|------------------|-----|-----------------------------------------|-----|--------|-------|--|

|                                   | 00  | <u> </u>         | 50  |                                         | 50  |        | 50    |  |

|                                   |     | —                |     |                                         | —   | —      |       |  |

| bit 15                            |     |                  |     |                                         |     |        | bit   |  |

|                                   |     |                  |     |                                         |     |        |       |  |

| U-0                               | U-0 | U-0              | U-0 | U-0                                     | U-0 | R/W-0  | R/W-0 |  |

| _                                 | _   | —                | _   | —                                       | —   | ECCDBE | SGHT  |  |

| bit 7                             |     |                  |     |                                         |     |        | bit   |  |

|                                   |     |                  |     |                                         |     |        |       |  |

| Legend:                           |     |                  |     |                                         |     |        |       |  |

| R = Readable bit W = Writable bit |     |                  | bit | U = Unimplemented bit, read as '0'      |     |        |       |  |

| -n = Value at POR                 |     | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |        | iown  |  |

bit 15-2 Unimplemented: Read as '0'

1 = ECC double-bit error trap has occurred

0 = ECC double-bit error trap has not occurred

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

| IABLE   | TABLE 10-1: DMA CHANNEL TRIGGER SOURCES |                             |         |      |                                |         |      |                              |

|---------|-----------------------------------------|-----------------------------|---------|------|--------------------------------|---------|------|------------------------------|

| CHSEL<  | 6:0>                                    | Trigger (Interrupt)         | CHSEL<  | 6:0> | Trigger (Interrupt)            | CHSEL<  | 6:0> | Trigger (Interrupt)          |

| 0000000 | 00h                                     | INT0 – External Interrupt 0 | 0100011 | 23h  | PWM Generator 8                | 1000100 | 44h  | CLC1 Positive Edge Interrupt |

| 0000001 | 01h                                     | SCCP1 Interrupt             | 0100100 | 24h  | PWM Event C                    | 1000101 | 45h  | CLC2 Positive Edge Interrupt |

| 0000010 | 02h                                     | SPI1 Receiver               | 0100101 | 25h  | SENT1 TX/RX                    | 1000110 | 46h  | SPI1 – Fault Interrupt       |

| 0000011 | 03h                                     | SPI1 Transmitter            | 0100110 | 26h  | SENT2 TX/RX                    | 1000111 | 47h  | SPI2 – Fault Interrupt       |

| 0000100 | 04h                                     | UART1 Receiver              | 0100111 | 27h  | ADC1 Group Convert Done        | 1001000 | 48h  |                              |

| 0000101 | 05h                                     | UART1 Transmitter           | 0101000 | 28h  | ADC Done AN0                   |         |      | (Reserved, do not use)       |

| 0000110 | 06h                                     | ECC Single Bit Error        | 0101001 | 29h  | ADC Done AN1                   | 1010110 | 56h  |                              |

| 0000111 | 07h                                     | NVM Write Complete          | 0101010 | 2Ah  | ADC Done AN2                   | 1010111 | 57h  | PWM Event D                  |

| 0001000 | 08h                                     | INT1 – External Interrupt 1 | 0101011 | 2Bh  | ADC Done AN3                   | 1011000 | 58h  | PWM Event E                  |

| 0001001 | 09h                                     | SI2C1 – I2C1 Slave Event    | 0101100 | 2Ch  | ADC Done AN4                   | 1011001 | 59h  | PWM Event F                  |

| 0001010 | 0Ah                                     | MI2C1 – I2C1 Master Event   | 0101101 | 2Dh  | ADC Done AN5                   | 1011010 | 5Ah  | (Reserved, do not use)       |

| 0001011 | 0Bh                                     | INT2 – External Interrupt 2 | 0101110 | 2Eh  | ADC Done AN6                   | 1011011 | 5Bh  | (Reserved, do not use)       |

| 0001100 | 0Ch                                     | SCCP2 Interrupt             | 0101111 | 2Fh  | ADC Done AN7                   | 1011100 | 5Ch  | SCCP7 Interrupt              |

| 0001101 | 0Dh                                     | INT3 – External Interrupt 3 | 0110000 | 30h  | ADC Done AN8                   | 1011101 | 5Dh  | SCCP8 Interrupt              |

| 0001110 | 0Eh                                     | UART2 Receiver              | 0110001 | 31h  | ADC Done AN9                   | 1011110 | 5Eh  | (Reserved, do not use)       |

| 0001111 | 0Fh                                     | UART2 Transmitter           | 0110010 | 32h  | ADC Done AN10                  | 1011111 | 5Fh  | ADC FIFO Ready Interrupt     |

| 0010000 | 10h                                     | SPI2 Receiver               | 0110011 | 33h  | ADC Done AN11                  | 1100000 | 60h  | CLC3 Positive Edge Interrupt |

| 0010001 | 11h                                     | SPI2 Transmitter            | 0110100 | 34h  | ADC Done AN12                  | 1100001 | 61h  | CLC4 Positive Edge Interrupt |

| 0010010 | 12h                                     | SCCP3 Interrupt             | 0110101 | 35h  | ADC Done AN13                  | 1100010 | 62h  | SPI3 Receiver                |

| 0010011 | 13h                                     | SI2C2 – I2C2 Slave Event    | 0110110 | 36h  | ADC Done AN14                  | 1100011 | 63h  | SPI3 Transmitter             |

| 0010100 | 14h                                     | MI2C2 – I2C1 Master Event   | 0110111 | 37h  | ADC Done AN15                  | 1100100 | 64h  | SI2C3 – I2C3 Slave Event     |

| 0010101 | 15h                                     | SCCP4 Interrupt             | 0111000 | 38h  | ADC Done AN16                  | 1100101 | 65h  | MI2C3 – I2C3 Master Event    |

| 0010110 | 16h                                     | SCCP5 Interrupt             | 0111001 | 39h  | ADC Done AN17                  | 1100110 | 66h  | SPI3 Fault                   |

| 0010111 | 17h                                     | SCCP6 Interrupt             | 0111010 | 3Ah  | ADC Done AN18                  | 1100111 | 67h  | MCCP9                        |

| 0011000 | 18h                                     | CRC Generator Interrupt     | 0111011 | 3Bh  | ADC Done AN19                  | 1101000 | 68h  | UART3 Receiver               |

| 0011001 | 19h                                     | PWM Event A                 | 0111100 | 3Ch  | ADC Done AN20                  | 1101001 | 69h  | UART3 Transmitter            |

| 0011010 | 1Ah                                     | (Reserved, do not use)      | 0111101 | 3Dh  | ADC Done AN21                  | 1101010 | 6Ah  | ADC Done AN24                |

| 0011011 | 1Bh                                     | PWM Event B                 | 0111110 | 3Eh  | ADC Done AN22                  | 1101011 | 6Bh  | ADC Done AN25                |

| 0011100 | 1Ch                                     | PWM Generator 1             | 0111111 | 3Fh  | ADC Done AN23                  | 1101100 | 6Ch  | PMP Event                    |

| 0011101 | 1Dh                                     | PWM Generator 2             | 1000000 | 40h  | AD1FLTR1 – Oversample Filter 1 | 1101101 | 6Dh  | PMP Error Event              |

| 0011110 | 1Eh                                     | PWM Generator 3             | 1000001 | 41h  | AD1FLTR2 – Oversample Filter 2 | 1101110 | 6Eh  |                              |

| 0011111 | 1Fh                                     | PWM Generator 4             | 1000010 | 42h  | AD1FLTR3 – Oversample Filter 3 |         |      | (Reserved, do not use)       |

| 0100000 | 20h                                     | PWM Generator 5             | 1000011 | 43h  | AD1FLTR4 – Oversample Filter 4 | 1111111 | 7Fh  |                              |

| 0100001 | 21h                                     | PWM Generator 6             |         |      |                                |         |      |                              |

| 0100010 | 22h                                     | PWM Generator 7             |         |      |                                |         |      |                              |

| TABLE 10-1: D | MA CHANNEL | TRIGGER SOURCES |

|---------------|------------|-----------------|

|---------------|------------|-----------------|

# **REGISTER 11-9:** C1TBCH: CAN TIME BASE COUNTER REGISTER HIGH<sup>(1,2)</sup>

| R/W-0                                                                       | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------------------------------------------------|-------|-------|-------|--------|-------|-------|-------|

|                                                                             |       |       | TBC<  | 31:24> |       |       |       |

| bit 15                                                                      |       |       |       |        |       |       | bit 8 |

|                                                                             |       |       |       |        |       |       |       |

| R/W-0                                                                       | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|                                                                             |       |       | TBC<  | 23:16> |       |       |       |

| bit 7                                                                       |       |       |       |        |       |       | bit 0 |

|                                                                             |       |       |       |        |       |       |       |

| Legend:                                                                     |       |       |       |        |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'        |       |       |       |        |       |       |       |

| -n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown) |       |       |       | nown   |       |       |       |

bit 15-0 **TBC<31:16>** CAN Time Base Counter bits

This is a free-running timer that increments every TBCPREx clock when TBCEN is set.

Note 1: The Time Base Counter (TBC) will be stopped and reset when TBCEN = 0 to save power.

2: The TBC prescaler count will be reset on any write to C1TBCH/L (TBCPREx will be unaffected).

## **REGISTER 11-10:** C1TBCL: CAN TIME BASE COUNTER REGISTER LOW<sup>(1,2)</sup>

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|

| TBC<15:8> |       |       |       |       |       |       |       |  |

| bit 15    |       |       |       |       |       |       | bit 8 |  |

|           |       |       |       |       |       |       |       |  |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

| TBC<7:0>  |       |       |       |       |       |       |       |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 TBC<15:0> CAN Time Base Counter bits

This is a free-running timer that increments every TBCPREx clock when TBCEN is set.

**Note 1:** The TBC will be stopped and reset when TBCEN = 0 to save power.

2: The TBC prescaler count will be reset on any write to C1TBCH/L (TBCPREx will be unaffected).

bit 7

bit 0

| U-0          | U-0            | U-0                                                                          | U-0            | U-0              | U-0              | U-0                | U-0   |  |  |  |

|--------------|----------------|------------------------------------------------------------------------------|----------------|------------------|------------------|--------------------|-------|--|--|--|

|              | —              | —                                                                            | _              | —                | —                | —                  | _     |  |  |  |

| bit 15       |                |                                                                              |                |                  |                  |                    | bit 8 |  |  |  |

|              |                |                                                                              |                |                  |                  |                    |       |  |  |  |

| U-0          | U-0            | R-1                                                                          | R-0            | R-0              | R-0              | R-0                | R-0   |  |  |  |

| —            | —              | ТХВО                                                                         | TXBP           | RXBP             | TXWARN           | RXWARN             | EWARN |  |  |  |

| bit 7        | ·              |                                                                              |                |                  | •                |                    | bit 0 |  |  |  |

|              |                |                                                                              |                |                  |                  |                    |       |  |  |  |

| Legend:      |                |                                                                              |                |                  |                  |                    |       |  |  |  |

| R = Readab   | ole bit        | W = Writable b                                                               | it             | U = Unimpler     | mented bit, read | l as '0'           |       |  |  |  |

| -n = Value a | at POR         | '1' = Bit is set                                                             |                | '0' = Bit is cle | eared            | x = Bit is unknown |       |  |  |  |

|              |                |                                                                              |                |                  |                  |                    |       |  |  |  |

| bit 15-6     | Unimplemen     | ted: Read as '0                                                              | ,              |                  |                  |                    |       |  |  |  |

| bit 5        | TXBO: Trans    | mitter in Error St                                                           | tate Bus Off b | it (TERRCNT<     | <7:0> > 255)     |                    |       |  |  |  |

|              | In Configurati | on mode, TXBO                                                                | is set since t | he module is r   | not on the bus.  |                    |       |  |  |  |

| bit 4        | TXBP: Transi   | <b>TXBP:</b> Transmitter in Error State Bus Passive bit (TERRCNT<7:0> > 127) |                |                  |                  |                    |       |  |  |  |

| bit 3        | RXBP: Recei    | ver in Error State                                                           | e Bus Passive  | e bit (RERRCN    | NT<7:0> > 127)   |                    |       |  |  |  |

| bit 2        | TXWARN: Tra    | ansmitter in Erro                                                            | or State Warni | ng bit (128 > T  | ERRCNT<7:0>      | · > 95)            |       |  |  |  |

|              |                |                                                                              |                |                  |                  |                    |       |  |  |  |

- bit 1 **RXWARN:** Receiver in Error State Warning bit (128 > RERRCNT<7:0> > 95)

- bit 0 EWARN: Transmitter or Receiver in Error State Warning bit

#### REGISTER 11-45: C1TRECL: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER LOW

| R-0     | R-0 | R-0 | R-0    | R-0     | R-0 | R-0 | R-0   |

|---------|-----|-----|--------|---------|-----|-----|-------|

|         |     |     | TERRC  | NT<7:0> |     |     |       |

| bit 15  |     |     |        |         |     |     | bit 8 |

|         |     |     |        |         |     |     |       |

| R-0     | R-0 | R-0 | R-0    | R-0     | R-0 | R-0 | R-0   |

|         |     |     | RERRCI | NT<7:0> |     |     |       |

| bit 7   |     |     |        |         |     |     | bit 0 |

|         |     |     |        |         |     |     |       |

| Legend: |     |     |        |         |     |     |       |

| - <b>J</b>        |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

|                   |                  |                            |                    |

| bit 15-8 | TERRCNT<7:0>: Transmit Error Counter bits |

|----------|-------------------------------------------|

|          |                                           |

bit 7-0 RERRCNT<7:0>: Receive Error Counter bits

#### R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 CLIEN<sup>(2)</sup> FI TIFN<sup>(1)</sup> SIFN<sup>(4)</sup> FFIFN<sup>(3)</sup> **IEVTSEL1 IEVTSEL0** \_\_\_\_ \_ bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ADTR2EN3 ADTR2EN2 ADTR2EN1 ADTR10FS4 ADTR10FS3 ADTR10FS2 ADTR10FS1 ADTR10FS0 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown FLTIEN: PCI Fault Interrupt Enable bit<sup>(1)</sup> bit 15 1 = Fault interrupt is enabled 0 = Fault interrupt is disabled bit 14 CLIEN: PCI Current-Limit Interrupt Enable bit<sup>(2)</sup> 1 = Current-limit interrupt is enabled 0 = Current-limit interrupt is disabled bit 13 FFIEN: PCI Feed-Forward Interrupt Enable bit<sup>(3)</sup> 1 = Feed-forward interrupt is enabled 0 = Feed-forward interrupt is disabled SIEN: PCI Sync Interrupt Enable bit<sup>(4)</sup> bit 12 1 = Sync interrupt is enabled 0 = Sync interrupt is disabled bit 11-10 Unimplemented: Read as '0' bit 9-8 IEVTSEL<1:0>: Interrupt Event Selection bits 11 = Time base interrupts are disabled (Sync, Fault, current-limit and feed-forward events can be independently enabled) 10 = Interrupts CPU at ADC Trigger 1 event 01 = Interrupts CPU at TRIGA compare event 00 = Interrupts CPU at EOC bit 7 ADTR2EN3: ADC Trigger 2 Source is PGxTRIGC Compare Event Enable bit 1 = PGxTRIGC register compare event is enabled as trigger source for ADC Trigger 2 0 = PGxTRIGC register compare event is disabled as trigger source for ADC Trigger 2 bit 6 ADTR2EN2: ADC Trigger 2 Source is PGxTRIGB Compare Event Enable bit 1 = PGxTRIGB register compare event is enabled as trigger source for ADC Trigger 2 0 = PGxTRIGB register compare event is disabled as trigger source for ADC Trigger 2 bit 5 ADTR2EN1: ADC Trigger 2 Source is PGxTRIGA Compare Event Enable bit 1 = PGxTRIGA register compare event is enabled as trigger source for ADC Trigger 2 0 = PGxTRIGA register compare event is disabled as trigger source for ADC Trigger 2 bit 4-0 ADTR1OFS<4:0>: ADC Trigger 1 Offset Selection bits 11111 = Offset by 31 trigger events 00010 = Offset by 2 trigger events 00001 = Offset by 1 trigger event 00000 = No offset **Note 1:** An interrupt is only generated on the rising edge of the PCI Fault active signal. 2: An interrupt is only generated on the rising edge of the PCI current-limit active signal.

#### REGISTER 12-18: PGxEVTH: PWM GENERATOR x EVENT REGISTER HIGH

- 3: An interrupt is only generated on the rising edge of the PCI feed-forward active signal.4: An interrupt is only generated on the rising edge of the PCI Sync active signal.

- DS70005349B-page 278

## REGISTER 15-5: POSxCNTL: POSITION x COUNTER REGISTER LOW

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                     | R/W-0             | R/W-0 | R/W-0              | R/W-0 |

|-----------------|-------|------------------|-------------------------------------------|-------------------|-------|--------------------|-------|

|                 |       |                  | POSC                                      | NT<15:8>          |       |                    |       |

| bit 15          |       |                  |                                           |                   |       |                    | bit 8 |

|                 |       |                  |                                           |                   |       |                    |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                     | R/W-0             | R/W-0 | R/W-0              | R/W-0 |

|                 |       |                  | POSC                                      | CNT<7:0>          |       |                    |       |

| bit 7           |       |                  |                                           |                   |       |                    | bit 0 |

|                 |       |                  |                                           |                   |       |                    |       |

| Legend:         |       |                  |                                           |                   |       |                    |       |

| R = Readable    | bit   | W = Writable I   | le bit U = Unimplemented bit, read as '0' |                   |       |                    |       |

| -n = Value at I | POR   | '1' = Bit is set |                                           | '0' = Bit is clea | ared  | x = Bit is unknown |       |

|                 |       |                  |                                           |                   |       |                    |       |

bit 15-0 POSCNT<15:0>: Low Word Used to Form 32-Bit Position Counter Register (POSxCNT) bits

#### REGISTER 15-6: POSxCNTH: POSITION x COUNTER REGISTER HIGH

| R/W-0                             | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0           | R/W-0  |

|-----------------------------------|-------|------------------|--------|------------------------------------|-------|-----------------|--------|

|                                   |       |                  | POSC   | NT<31:24>                          |       |                 |        |

| bit 15                            |       |                  |        |                                    |       |                 | bit 8  |

|                                   |       | 5444.6           | 5444.6 | 54446                              |       | 54446           | 5444.6 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0           | R/W-0  |

|                                   |       |                  | POSCI  | NT<23:16>                          |       |                 |        |

| bit 7                             |       |                  |        |                                    |       |                 | bit 0  |

| Legend:                           |       |                  |        |                                    |       |                 |        |

| R = Readable bit W = Writable bit |       |                  | bit    | U = Unimplemented bit, read as '0' |       |                 |        |

| -n = Value at F                   | POR   | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is un |       | x = Bit is unkr | nown   |

bit 15-0 **POSCNT<31:16>:** High Word Used to Form 32-Bit Position Counter Register (POSxCNT) bits

#### REGISTER 16-5: UxBRG: UARTx BAUD RATE REGISTER

| R/W-0           | R/W-0   | R/W-0            | R/W-0 | R/W-0                              | R/W-0  | R/W-0           | R/W-0   |

|-----------------|---------|------------------|-------|------------------------------------|--------|-----------------|---------|

|                 |         |                  | BRG   | <15:8>                             |        |                 |         |

| bit 15          |         |                  |       |                                    |        |                 | bit 8   |

| R/W-0           | R/W-0   | R/W-0            | R/W-0 | R/W-0                              | R/W-0  | R/W-0           | R/W-0   |

|                 | 10,00-0 | 17.44-0          |       |                                    | 1000-0 | 10.00-0         | 10,00-0 |

|                 |         |                  | BRO   | 6<7:0>                             |        |                 |         |

| bit 7           |         |                  |       |                                    |        |                 | bit 0   |

|                 |         |                  |       |                                    |        |                 |         |

| Legend:         |         |                  |       |                                    |        |                 |         |

| R = Readable    | bit     | W = Writable I   | bit   | U = Unimplemented bit, read as '0' |        |                 |         |

| -n = Value at F | POR     | '1' = Bit is set |       | '0' = Bit is clea                  | ared   | x = Bit is unki | nown    |

bit 15 BRG<15:0>: Baud Rate Divisor bits

#### REGISTER 16-6: UxBRGH: UARTx BAUD RATE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 |

|-------|-----|-----|-----|-------|-------|--------|-------|

| —     | —   | —   | —   |       | BRG<  | 19:16> |       |

| bit 7 |     |     |     |       |       |        | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

bit 3-0 BRG<19:16>: Baud Rate Divisor bits

| ABEL 10-2. IZCA RESERVED ADDRESSES |         |                                        |  |  |  |  |  |  |

|------------------------------------|---------|----------------------------------------|--|--|--|--|--|--|

| Slave Address                      | R/W Bit | Description                            |  |  |  |  |  |  |

| 0000 000                           | 0       | General Call Address <sup>(2)</sup>    |  |  |  |  |  |  |

| 0000 0000                          | 1       | Start Byte                             |  |  |  |  |  |  |

| 0000 001                           | х       | Cbus Address                           |  |  |  |  |  |  |

| 0000 01x                           | х       | Reserved                               |  |  |  |  |  |  |

| 0000 1xx                           | x       | HS Mode Master Code                    |  |  |  |  |  |  |

| 1111 0xx                           | x       | 10-Bit Slave Upper Byte <sup>(3)</sup> |  |  |  |  |  |  |

| 1111 1xx                           | x       | Reserved                               |  |  |  |  |  |  |

## TABLE 18-2: I2Cx RESERVED ADDRESSES<sup>(1)</sup>

**Note 1:** The address bits listed here will never cause an address match independent of address mask settings.

2: This address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Command Description                                               |

|---------|------------------------|-------------|-------------------------------------------------------------------|

|         | PTGCTRL <sup>(1)</sup> | 0000        | NOP.                                                              |

|         |                        | 0001        | Reserved; do not use.                                             |

|         |                        | 0010        | Disable Step delay timer (PTGSD).                                 |

|         |                        | 0011        | Reserved; do not use.                                             |

|         |                        | 0100        | Reserved; do not use.                                             |

|         |                        | 0101        | Reserved; do not use.                                             |

|         |                        | 0110        | Enable Step delay timer (PTGSD).                                  |

|         |                        | 0111        | Reserved; do not use.                                             |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the PTGT0LIM register. |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the PTGT1LIM register. |

|         |                        | 1010        | Wait for the software trigger (level, PTGSWT = 1).                |

|         |                        | 1011        | Wait for the software trigger (positive edge, PTGSWT = 0 to 1).   |

|         |                        | 1100        | Copy the PTGC0LIM register contents to the strobe output.         |

|         |                        | 1101        | Copy the PTGC1LIM register contents to the strobe output.         |

|         |                        | 1110        | Copy the PTGL0 register contents to the strobe output.            |

|         |                        | 1111        | Generate the triggers indicated in the PTGBTE register.           |

|         | PTGADD(1)              | 0000        | Add the PTGADJ register contents to the PTGC0LIM register.        |

|         |                        | 0001        | Add the PTGADJ register contents to the PTGC1LIM register.        |

|         |                        | 0010        | Add the PTGADJ register contents to the PTGT0LIM register.        |

|         |                        | 0011        | Add the PTGADJ register contents to the PTGT1LIM register.        |

|         |                        | 0100        | Add the PTGADJ register contents to the PTGSDLIM register.        |

|         |                        | 0101        | Add the PTGADJ register contents to the PTGL0 register.           |

|         |                        | 0110        | Reserved; do not use.                                             |

|         |                        | 0111        | Reserved; do not use.                                             |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy the PTGHOLD register contents to the PTGC0LIM register.      |

|         |                        | 1001        | Copy the PTGHOLD register contents to the PTGC1LIM register.      |

|         |                        | 1010        | Copy the PTGHOLD register contents to the PTGT0LIM register.      |

|         |                        | 1011        | Copy the PTGHOLD register contents to the PTGT1LIM register.      |

|         |                        | 1100        | Copy the PTGHOLD register contents to the PTGSDLIM register.      |

|         |                        | 1101        | Copy the PTGHOLD register contents to the PTGL0 register.         |

|         |                        | 1110        | Reserved; do not use.                                             |

|         |                        | 1111        | Reserved; do not use.                                             |

## TABLE 24-2: PTG COMMAND OPTIONS

**Note 1:** All reserved commands or options will execute, but they do not have any affect (i.e., execute as a NOP instruction).

NOTES:

## REGISTER 28-9: DMTPSINTVL: DMT POST-CONFIGURE INTERVAL STATUS REGISTER LOW

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|-----------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|--|

|                 |       |                  | PSINT | <sup>-</sup> V<15:8>               |       |                 |       |  |  |

| bit 15 bit      |       |                  |       |                                    |       |                 |       |  |  |

|                 |       |                  |       |                                    |       |                 |       |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|                 |       |                  | PSIN  | TV<7:0>                            |       |                 |       |  |  |

| bit 7           |       |                  |       |                                    |       |                 | bit 0 |  |  |

|                 |       |                  |       |                                    |       |                 |       |  |  |

| Legend:         |       |                  |       |                                    |       |                 |       |  |  |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unki | nown  |  |  |

bit 15-0 **PSINTV<15:0>:** Lower DMT Window Interval Configuration Status bits This is always the value of the FDMTIVTL Configuration register.

#### REGISTER 28-10: DMTPSINTVH: DMT POST-CONFIGURE INTERVAL STATUS REGISTER HIGH

| R/W-0             | R/W-0  | R/W-0            | R/W-0 | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |

|-------------------|--------|------------------|-------|------------------------------------|--------|--------------------|-------|

|                   |        |                  | PSINT | V<31:24>                           |        |                    |       |

| bit 15            |        |                  |       |                                    |        |                    | bit 8 |

| R/W-0             | R/W-0  | R/W-0            | R/W-0 | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |

| 1000 0            | 1000 0 | 1000 0           |       | V<23:16>                           | 1000 0 | 1000 0             | 10000 |

| bit 7             |        |                  |       |                                    |        |                    | bit 0 |

| 1                 |        |                  |       |                                    |        |                    |       |

| Legend:           |        |                  |       |                                    |        |                    |       |

| R = Readable bit  |        | W = Writable bit |       | U = Unimplemented bit, read as '0' |        |                    |       |

| -n = Value at POR |        | '1' = Bit is set |       | '0' = Bit is cleared               |        | x = Bit is unknown |       |

|                   |        |                  |       |                                    |        |                    |       |

bit 15-0 **PSINTV<31:16>:** Higher DMT Window Interval Configuration Status bits This is always the value of the FDMTIVTH Configuration register.

## 29.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification on the I/O ports or peripherals that use an External Clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the regulators can be configured to go into standby when Sleep mode is entered by clearing the VREGS (RCON<8>) bit (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) bit can be set to keep the regulators active during Sleep mode. The available Low-Power Sleep modes are shown in Table 29-1. Additional regulator information is available in **Section 30.4 "On-Chip Voltage Regulators"**.

| Relative<br>Power | LPWREN       | VREGS | MODE                |  |

|-------------------|--------------|-------|---------------------|--|

| Highest           | 0            | 1     | Full power, active  |  |

| _                 | 0            | 0     | Full power, standby |  |

| _                 | 1 <b>(1)</b> | 1     | Low power, active   |  |

| Lowest            | 1 <b>(1)</b> | 0     | Low power, standby  |  |

#### TABLE 29-1: LOW-POWER SLEEP MODES

**Note 1:** Low-Power modes, when LPWREN = 1, can only be used in the industrial temperature range.

## 29.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 29.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the SIDL bit in the Timer1 Control register (T1CON<13>).

#### 29.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

## 30.7 JTAG Interface

The dsPIC33CK256MP508 family devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface will be provided in future revisions of this document.

| Note: | Refer to "Programming and Diagnostics"       |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |  |  |  |  |  |  |

|       | Reference Manual" for further information on |  |  |  |  |  |  |

|       | usage, configuration and operation of the    |  |  |  |  |  |  |

|       | JTAG interface.                              |  |  |  |  |  |  |

## 30.8 In-Circuit Serial Programming™ (ICSP™)

The dsPIC33CK256MP508 family devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33CK256MP508 Family Flash Programming Specification" (DS70005300) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGC1 and PGD1

- PGC2 and PGD2

- PGC3 and PGD3

## 30.9 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or the REAL ICE<sup>™</sup> emulator is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGCx (Emulation/Debug Clock) and PGDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGC1 and PGD1

- PGC2 and PGD2

- PGC3 and PGD3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, VSS and the PGCx/PGDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGCx and PGDx).

## 30.10 Code Protection and CodeGuard™ Security

dsPIC33CK256MP508 family devices offer multiple levels of security for protecting individual intellectual property. The program Flash protection can be broken up into three segments: Boot Segment (BS), General Segment (GS) and Configuration Segment (CS). Boot Segment has the highest security privilege and can be thought to have limited restrictions when accessing other segments. General Segment has the least security and is intended for the end user system code. Configuration Segment contains only the device user configuration data, which is located at the end of the program memory space.

The code protection features are controlled by the Configuration registers, FSEC and FBSLIM. The FSEC register controls the code-protect level for each segment and if that segment is write-protected. The size of BS and GS will depend on the BSLIM<12:0> bits setting and if the Alternate Interrupt Vector Table (AIVT) is enabled. The BSLIM<12:0> bits define the number of pages for BS with each page containing 1024 IW. The smallest BS size is one page, which will consist of the Interrupt Vector Table (IVT) and 512 IW of code protection.

If the AIVT is enabled, the last page of BS will contain the AIVT and will not contain any BS code. With AIVT enabled, the smallest BS size is now two pages (2048 IW), with one page for the IVT and BS code, and the other page for the AIVT. Write protection of the BS does not cover the AIVT. The last page of BS can always be programmed or erased by BS code. The General Segment will start at the next page and will consume the rest of program Flash, except for the Flash Configuration Words. The IVT will assume GS security only if BS is not enabled. The IVT is protected from being programmed or page erased when either security segment has enabled write protection.

# 31.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33CK256MP508 familv of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "16-Bit MCU and DSC Programmer's Reference Manual' (DS70000157), which is available from the Microchip web site (www.microchip.com).

The dsPIC33CK256MP508 family instruction set is almost identical to that of the dsPIC30F and dsPIC33F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- Control operations

Table 31-1 lists the general symbols used in describing the instructions.

The dsPIC33 instruction set summary in Table 31-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- · The accumulator write-back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

# TABLE 33-9:WATCHDOG TIMER DELTA CURRENT $(\triangle IwDT)^{(1)}$

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                |    |    |        |      |  |  |

|------------------------------------------------------|--------------------------------|----|----|--------|------|--|--|

| Parameter No.                                        | No. Typ. Max. Units Conditions |    |    |        |      |  |  |

| DC61                                                 | 0.75                           | 5  | μA | -40°C  |      |  |  |

|                                                      | 2.0                            | 12 | μA | +25°C  | 3.3V |  |  |

|                                                      | 3.88                           | 24 | μA | +85°C  | 3.3V |  |  |

|                                                      | 5.69                           | 40 | μA | +125°C |      |  |  |

**Note 1:** The  $\triangle$ IWDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

| Operating Con<br>Operating temp |      | -40°C | $\leq TA \leq +8$ |            | ial                           |                                                                                    |  |

|---------------------------------|------|-------|-------------------|------------|-------------------------------|------------------------------------------------------------------------------------|--|

| Parameter No.                   | Тур. | Max.  | Units             | Conditions |                               |                                                                                    |  |

| DC100                           | 5.96 | 6.6   | mA                | -40°C      | 3.3V (AVCO = 1000 MHz. PLLFBD |                                                                                    |  |

|                                 | 5.99 | 6.7   | mA                | +25°C      |                               | PWM Input (AFPLLO = 500 MHz)<br>(AVCO = 1000 MHz, PLLFBD = 125,<br>API I DIV1 = 2) |  |

|                                 | 5.92 | 6.9   | mA                | +85°C      |                               |                                                                                    |  |

|                                 | 5.47 | 7     | mA                | +125°C     |                               | · · ·,                                                                             |  |

| DC101                           | 4.89 | 5.4   | mA                | -40°C      |                               |                                                                                    |  |

| -                               | 4.91 | 5.5   | mA                | +25°C      | 3.3V                          | PWM Input (AFPLLO = 400 MHz),<br>(AVCO = 400 MHz, PLLFBD = 50,<br>APLLDIV1 = 1)    |  |

|                                 | 4.85 | 5.7   | mA                | +85°C      |                               |                                                                                    |  |

|                                 | 4.42 | 5.7   | mA                | +125°C     |                               |                                                                                    |  |

| DC102                           | 2.77 | 3.7   | mA                | -40°C      |                               |                                                                                    |  |

|                                 | 2.75 | 3.7   | mA                | +25°C      | 3.3V                          | PWM Input (AFPLLO = 200 MHz),<br>(AVCO = 400 MHz, PLLFBD = 50,<br>APLLDIV1 = 2)    |  |

|                                 | 2.7  | 3.7   | mA                | +85°C      |                               |                                                                                    |  |

|                                 | 2.26 | 3.7   | mA                | +125°C     |                               | ,                                                                                  |  |

| DC103                           | 1.67 | 2     | mA                | -40°C      | 3.3V                          |                                                                                    |  |

|                                 | 1.66 | 2.2   | mA                | +25°C      |                               | PWM Input (AFPLLO = 100 MHz),<br>(AVCO = 400 MHz, PLLFBD = 50,<br>APLLDIV1 = 4)    |  |

|                                 | 1.63 | 2.3   | mA                | +85°C      |                               |                                                                                    |  |

|                                 | 1.17 | 2.3   | mA                | +125°C     |                               | , ,                                                                                |  |

TABLE 33-10: PWM DELTA CURRENT<sup>(1)</sup>

**Note 1:** APLL current is not included. The APLL current will be the same if more than 1 PWM is running. Listed delta currents are for only one PWM instance. All parameters are characterized but not tested during manufacturing.

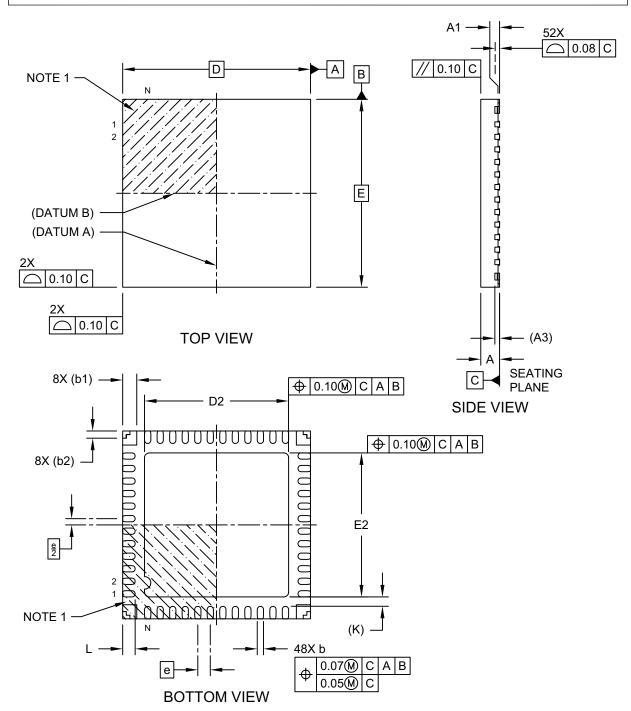

## 48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M4) - 6x6 mm Body [UQFN] With Corner Anchors and 4.6x4.6 mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-442A-M4 Sheet 1 of 2

NOTES: