Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 39                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 19x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

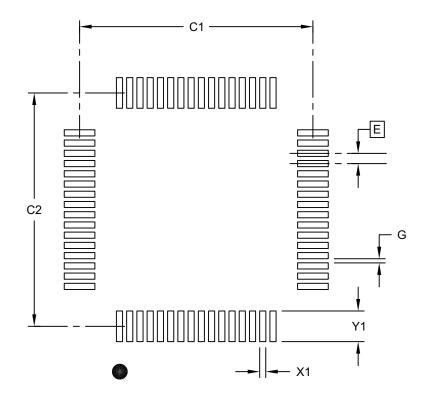

| Package / Case             | 48-TQFP                                                                           |

| Supplier Device Package    | 48-TQFP (7x7)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck256mp205t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(1)</sup> | Pin Name <sup>(1)</sup> Pin Buff<br>Type Typ |    | PPS | Description                                                                   |  |  |  |

|-------------------------|----------------------------------------------|----|-----|-------------------------------------------------------------------------------|--|--|--|

| PGD1                    | I/O                                          | ST | No  | Data I/O pin for Programming/Debugging Communication Channel 1                |  |  |  |

| PGC1                    | I                                            | ST | No  | Clock input pin for Programming/Debugging Communication<br>Channel 1          |  |  |  |

| PGD2                    | I/O                                          | ST | No  | Data I/O pin for Programming/Debugging Communication Channel 2                |  |  |  |

| PGC2                    | I                                            | ST | No  | Clock input pin for Programming/Debugging Communication<br>Channel 2          |  |  |  |

| PGD3                    | I/O                                          | ST | No  | Data I/O pin for Programming/Debugging Communication Channel 3                |  |  |  |

| PGC3                    | I                                            | ST | No  | Clock input pin for Programming/Debugging Communication<br>Channel 3          |  |  |  |

| MCLR                    | I/P                                          | ST | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device.    |  |  |  |

| AVDD                    | Р                                            | Р  | No  | Positive supply for analog modules. This pin must be connected at all times.  |  |  |  |

| AVss                    | Р                                            | Р  | No  | Ground reference for analog modules. This pin must be connected at all times. |  |  |  |

| Vdd                     | Р                                            | _  | No  | Positive supply for peripheral logic and I/O pins                             |  |  |  |

| Vss                     | Р                                            | _  | No  | Ground reference for logic and I/O pins                                       |  |  |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog input O = Output TTL = TTL input buffer P = Power I = Input DIG = Digital

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

2: PWM4L and PWM4H pins are available on PPS as well as dedicated.

3: SPI2 supports dedicated pins as well as PPS on 48, 64 and 80-pin devices.

## 4.2.5 X AND Y DATA SPACES

The dsPIC33CK256MP508 family core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

#### 4.2.6 BIST OVERVIEW

The dsPIC33CK256MP508 family features a data memory Built-In Self-Test (BIST) that has the option to be run at start-up or run time. The memory test checks that all memory locations are functional and provides a pass/fail status of the RAM that can be used by software to take action if needed. If a failure is reported, the specific location(s) are not identified.

The MBISTCON register (Register 4-1) contains control and status bits for BIST operation. The MBISTDONE bit (MBISTCON<7>) indicates if a BIST was run since the last Reset and the MBISTSTAT bit (MBISTCON<4>) provides the pass fail result.

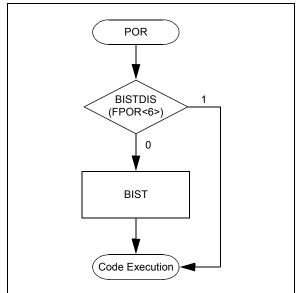

#### 4.2.7 BIST AT START-UP

The BIST can be configured to automatically run on a POR type Reset, as shown in Figure 4-10. By default, when BISTDIS (FPOR<6>) = 1, the BIST is disabled and will not be part of device start-up. If the BISTDIS bit is cleared during device programming, the BIST will run after all Configuration registers have been loaded and before code execution begins. BIST will always run on FRC+PLL with PLL settings resulting in a 125 MHz clock rate.

#### FIGURE 4-10: BIST FLOWCHART

#### 4.2.8 BIST AT RUN TIME

A BIST test can be requested to run on subsequent device Resets at any time.

A BIST will corrupt all of the RAM contents, including the Stack Pointer, and requires a subsequent Reset. The system should be prepared for a Reset before a BIST is performed. The BIST is invoked by setting the MBISTEN bit (MBISTCON<0>) and executing a Reset. The MBISTCON register is protected against accidental writes and requires an unlock sequence prior to writing. Only one bit can be set per unlock sequence. The procedure for a run-time BIST is as follows:

- 1. Execute the unlock sequence by consecutively writing 0x55 and 0xAA to the NVMKEY register.

- 2. Write 0x0001 to the MBISTCON SFR.

- 3. Execute a software RESET command.

- 4. Verify a Software Reset has occurred by reading SWR (RCON<6>) (optional).

- 5. Verify that the MBISTDONE bit is set.

- 6. Take action depending on test result indicated by MBISTSTAT.

| Register   | Address | All Resets                              | Register | Address | All Resets       | Register   | Address | All Resets                              |

|------------|---------|-----------------------------------------|----------|---------|------------------|------------|---------|-----------------------------------------|

| Interrupts |         |                                         | IPC3     | 846     | -100-100-100-100 | IPC35      | 886     | -100-100                                |

| IFS0       | 800     | 000000000-00000                         | IPC4     | 848     | -100-100-100-100 | IPC36      | 888     | 100                                     |

| IFS1       | 802     | 00000000-000000                         | IPC5     | 84A     | -100100-100      | IPC37      | 88A     | 100-100                                 |

| IFS2       | 804     | 00000-00-0000                           | IPC6     | 84C     | -100-100-100-100 | IPC38      | 88C     | 100-100                                 |

| IFS3       | 806     | 0000000-0-00000                         | IPC7     | 84E     | -100-100-100-100 | IPC40      | 890     | 100-100                                 |

| IFS4       | 808     | 000000000000000000000000000000000000000 | IPC8     | 850     | -100-100         | IPC42      | 894     | -100-100-100-100                        |

| IFS5       | 80A     | 00000000000000000-                      | IPC9     | 852     | 100-100-100      | IPC43      | 896     | -100-100-100-100                        |

| IFS6       | 80C     | 000000000000000000000000000000000000000 | IPC10    | 854     | -100100-100      | IPC44      | 898     | -100-100-100-100                        |

| IFS7       | 80E     | 000000000000000000000000000000000000000 | IPC11    | 856     | -100-100-100-100 | IPC45      | 89A     | 100-100-100                             |

| IFS8       | 810     | 000                                     | IPC12    | 858     | -100-100-100-100 | IPC47      | 89E     | -100-100-100                            |

| IFS9       | 812     | 0                                       | IPC13    | 85A     | 100100           | IPC48      | 8A0     | -100-100-100-100                        |

| IFS10      | 814     | 000000000                               | IPC14    | 85C     | -100-100-100-100 | INTCON1    | 8C0     | 000000000-0000-                         |

| IFS11      | 816     | 0000000000                              | IPC15    | 85E     | -100-100-100     | INTCON2    | 8C2     | 00000000                                |

| IFS12      | 818     | 0000                                    | IPC16    | 860     | -100100-100      | INTCON3    | 8C4     | 0                                       |

| IEC0       | 820     | 0000000000-00000                        | IPC17    | 862     | -100-100-100-100 | INTCON4    | 8C6     | 00                                      |

| IEC1       | 822     | 00000000-000000                         | IPC18    | 864     | -100-100-100-100 | INTTREG    | 8C8     | 000-0000-0000000                        |

| IEC2       | 824     | 00000-00-0000                           | IPC19    | 866     | -100-100-100-100 | Flash      | •       |                                         |

| IEC3       | 826     | 0000000-0-00000                         | IPC20    | 868     | -100-100-100     | NVMCON     | 8D0     | 000000000000                            |

| IEC4       | 828     | 000000000000000000000000000000000000000 | IPC21    | 86A     | -100-100-100-100 | NVMADRL    | 8D2     | 000000000000000000000000000000000000000 |

| IEC5       | 82A     | 00000000000000000-                      | IPC22    | 86C     | -100-100-100-100 | NVMADRH    | 8D4     | 00000000                                |

| IEC6       | 82C     | 000000000000000000000000000000000000000 | IPC23    | 86E     | -100-100-100-100 | NVMKEY     | 8D6     | 00000000                                |

| IEC7       | 82E     | 000000000000000000000000000000000000000 | IPC24    | 870     | -100-100-100-100 | NVMSRCADRL | 8D8     | 000000000000000000000000000000000000000 |

| IEC8       | 830     | 00                                      | IPC25    | 872     | -100-100-100-100 | NVMSRCADRH | 8DA     | 00000000                                |

| IEC9       | 832     | 0                                       | IPC26    | 874     | -100-100-100-100 | CBG        |         |                                         |

| IEC10      | 834     | 000000000                               | IPC27    | 876     | -100-100-100-100 | AMPCON1L   | 8DC     | 000                                     |

| IEC11      | 836     | 0000000000                              | IPC28    | 878     | -100-100-100-100 | AMPCON1H   | 8DE     | 000                                     |

| IEC12      | 838     | 0000                                    | IPC29    | 87A     | -100-100-100-100 | BIASCON    | 8F0     | 0000                                    |

| IPC0       | 840     | -100-100-100-100                        | IPC30    | 87C     | -100-100-100-100 | IBIASCON0L | 8F4     | 000000000000                            |

| IPC1       | 842     | -100-100100                             | IPC31    | 87E     | -100-100-100-100 | IBIASCON0H | 8F6     | 000000000000                            |

| IPC2       | 844     | -100-100-100-100                        | IPC32    | 880     | 100              | T          |         |                                         |

TABLE 4-9: SFR BLOCK 800h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address values are in hexadecimal. Reset values are in binary.

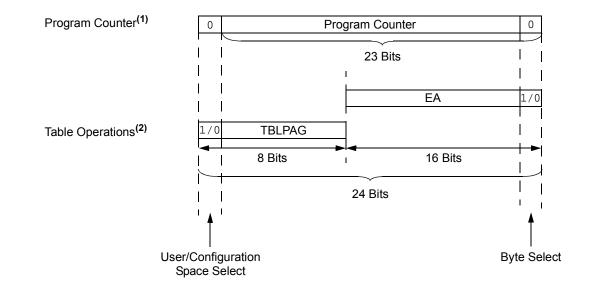

# 4.4.5 INTERFACING PROGRAM AND DATA MEMORY SPACES

The dsPIC33CK256MP508 family architecture uses a 24-bit wide Program Space (PS) and a 16-bit wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33CK256MP508 family devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

# TABLE 4-20: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address      |           |                     |               |     |  |  |

|------------------------|---------------|----------------------------|-----------|---------------------|---------------|-----|--|--|

| Access Type            | Space         | <23>                       | <22:16>   | <15>                | <14:1>        | <0> |  |  |

| Instruction Access     | User          | 0 PC<22:1>                 |           |                     |               | 0   |  |  |

| (Code Execution)       |               | 0xxx xxxx xxxx xxxx xxxx x |           |                     |               |     |  |  |

| TBLRD/TBLWT            | User          | TBLPAG<7:0> Data           |           |                     | Data EA<15:0> |     |  |  |

| (Byte/Word Read/Write) |               | 0                          | xxx xxxx  | XXXX XXXX XXXX XXXX |               | x   |  |  |

|                        | Configuration | TB                         | LPAG<7:0> | Data EA<15:0>       |               |     |  |  |

|                        |               | 1                          | xxx xxxx  | xxxx                | xxxx xxxx xxx | x   |  |  |

#### FIGURE 4-16: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

- **Note 1:** The Least Significant bit (LSb) of Program Space addresses is always fixed as '0' to maintain word alignment of data in the Program and Data Spaces.

- **2:** Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

# 5.4 ICSP™ Write Inhibit

ICSP Write Inhibit is an access restriction feature that, when activated, restricts all of Flash memory. Once activated, ICSP Write Inhibit permanently prevents ICSP Flash programming and erase operations, and cannot be deactivated. This feature is intended to prevent alteration of Flash memory contents, with behavior similar to One-Time-Programmable (OTP) devices.

RTSP, including erase and programming operations, is not restricted when ICSP Write Inhibit is activated; however, code to perform these actions must be programmed into the device before ICSP Write Inhibit is activated. This allows for a bootloader-type application to alter Flash contents with ICSP Write Inhibit activated.

Entry into ICSP and Enhanced ICSP modes is not affected by ICSP Write Inhibit. In these modes, it will continue to be possible to read configuration memory space and any user memory space regions which are not code protected. With ICSP writes inhibited, an attempt to set WR (NVMCON<15>) = 1 will maintain WR = 0, and instead, set WRERR (NVMCON<13>) = 1. All Enhanced ICSP erase and programming commands will have no effect with self-checked programming commands returning a FAIL response opcode (PASS if the destination already exactly matched the requested programming data).

Once ICSP Write Inhibit is activated, it is not possible for a device executing in Debug mode to erase/write Flash, nor can a debug tool switch the device to Production mode. ICSP Write Inhibit should therefore only be activated on devices programmed for production.

The JTAG port, when enabled, can be used to map ICSP signals to JTAG I/O pins. All Flash erase/ programming operations initiated via the JTAG port will therefore also be blocked after activating ICSP Write Inhibit.

#### 5.4.1 ACTIVATING ICSP™ WRITE INHIBIT

Caution: It is not possible to deactivate ICSP Write Inhibit.

ICSP Write Inhibit is activated by executing a pair of NVMCON double-word programming commands to save two 16-bit activation values in the configuration memory space. The target NVM addresses and values required for activation are shown in Table 5-1. Once both addresses contain their activation values, ICSP Write Inhibit will take permanent effect on the next device Reset. Neither address can be reset, erased or otherwise modified, through any means, after being successfully programmed, even if one of the addresses has not been programmed.

Only the lower 16 data bits stored at the activation addresses are evaluated; the upper 8 bits and second 24-bit word written by the double-word programming (NVMOP<3:0>) should be written as '0's. The addresses can be programmed in any order and also during separate ICSP/Enhanced ICSP/RTSP sessions, but any attempt to program an incorrect 16-bit value or use a row programming operation to program the values will be aborted without altering the existing data.

| TABLE 5-1: | ICSP™ WRITE INHIBIT  |

|------------|----------------------|

|            | ACTIVATION ADDRESSES |

|            | AND DATA             |

|              | Configuration<br>Memory Address | ICSP Write<br>Inhibit Activation<br>Value |  |  |

|--------------|---------------------------------|-------------------------------------------|--|--|

| Write Lock 1 | 0x801034                        | 0x006D63                                  |  |  |

| Write Lock 2 | 0x801038                        | 0x006870                                  |  |  |

### 8.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Enable for PORTx register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs, other than VDD, by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

## 8.2 Configuring Analog and Digital Port Pins

The ANSELx registers control the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx registers have a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

## 8.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

# 8.3 PORT Control Registers

The following registers are in the PORT module:

- Register 8-1: ANSELx (one per port)

- Register 8-2: TRISx (one per port)

- Register 8-3: PORTx (one per port)

- Register 8-4: LATx (one per port)

- Register 8-5: ODCx (one per port)

- Register 8-6: CNPUx (one per port)

- Register 8-7: CNPDx (one per port)

- Register 8-8: CNCONx (one per port optional)

- Register 8-9: CNEN0x (one per port)

- Register 8-10: CNSTATx (one per port optional)

- Register 8-11: CNEN1x (one per port)

- Register 8-12: CNFx (one per port)

#### **REGISTER 8-1:** ANSELX: ANALOG SELECT FOR PORTX REGISTER

| R/W-1                          | R/W-1                         | R/W-1            | R/W-1 | R/W-1                              | R/W-1 | R/W-1           | R/W-1 |

|--------------------------------|-------------------------------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                                |                               |                  | ANSEI | _x<15:8>                           |       |                 |       |

| bit 15                         |                               |                  |       |                                    |       |                 | bit 8 |

| R/W-1                          | R/W-1                         | R/W-1            | R/W-1 | R/W-1                              | R/W-1 | R/W-1           | R/W-1 |

|                                |                               |                  | ANSE  | Lx<7:0>                            |       |                 |       |

| bit 7                          |                               |                  |       |                                    |       |                 | bit 0 |

| Legend:                        |                               |                  |       |                                    |       |                 |       |

| R = Readable                   | Readable bit W = Writable bit |                  |       | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR '1' = Bit is |                               | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unkı | nown  |

bit 15-0

ANSELx<15:0>: Analog Select for PORTx bits

1 = Analog input is enabled and digital input is disabled on the PORTx[n] pin

0 = Analog input is disabled and digital input is enabled on the PORTx[n] pin

Unimplemented: Read as '0'

Unimplemented: Read as '0'

(see Table 8-7 for peripheral function numbers)

(see Table 8-7 for peripheral function numbers)

| U-0             | U-0 | R/W-0            | R/W-0                                               | R/W-0            | R/W-0  | R/W-0           | R/W-0  |

|-----------------|-----|------------------|-----------------------------------------------------|------------------|--------|-----------------|--------|

| —               | —   | RP49R5           | RP49R4                                              | RP49R3           | RP49R2 | RP49R1          | RP49R0 |

| bit 15          |     |                  |                                                     |                  |        |                 | bit 8  |

|                 |     |                  |                                                     |                  |        |                 |        |

| U-0             | U-0 | R/W-0            | R/W-0                                               | R/W-0            | R/W-0  | R/W-0           | R/W-0  |

| —               | —   | RP48R5           | RP48R4                                              | RP48R3           | RP48R2 | RP48R1          | RP48R0 |

| bit 7           |     |                  |                                                     |                  |        |                 | bit 0  |

|                 |     |                  |                                                     |                  |        |                 |        |

| Legend:         |     |                  |                                                     |                  |        |                 |        |

| R = Readable b  | oit | W = Writable     | W = Writable bit U = Unimplemented bit, read as '0' |                  |        |                 |        |

| -n = Value at P | OR  | '1' = Bit is set |                                                     | '0' = Bit is cle | ared   | x = Bit is unkn | iown   |

RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits

RP48R<5:0>: Peripheral Output Function is Assigned to RP48 Output Pin bits

**RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9**

#### REGISTER 8-62: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0                                | U-0        | R/W-0          | R/W-0                                   | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |  |

|------------------------------------|------------|----------------|-----------------------------------------|------------------------------------|--------|--------|--------|--|

| —                                  | —          | RP51R5         | RP51R4                                  | RP51R3                             | RP51R2 | RP51R1 | RP51R0 |  |

| bit 15                             |            | •              |                                         |                                    |        |        | bit 8  |  |

|                                    |            |                |                                         |                                    |        |        |        |  |

| U-0                                | U-0        | R/W-0          | R/W-0                                   | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |  |

| —                                  | —          | RP50R5         | RP50R4                                  | RP50R3                             | RP50R2 | RP50R1 | RP50R0 |  |

| bit 7                              |            |                |                                         |                                    |        |        | bit 0  |  |

|                                    |            |                |                                         |                                    |        |        |        |  |

| Legend:                            |            |                |                                         |                                    |        |        |        |  |

| R = Readable                       | bit        | W = Writable   | bit                                     | U = Unimplemented bit, read as '0' |        |        |        |  |

| -n = Value at POR '1' = Bit is set |            |                | '0' = Bit is cleared x = Bit is unknown |                                    |        | nown   |        |  |

|                                    |            |                |                                         |                                    |        |        |        |  |

| bit 15-14                          | Unimplemen | ted: Read as ' | )'                                      |                                    |        |        |        |  |

bit 13-8 **RP51R<5:0>:** Peripheral Output Function is Assigned to RP51 Output Pin bits (see Table 8-7 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP50R<5:0>:** Peripheral Output Function is Assigned to RP50 Output Pin bits (see Table 8-7 for peripheral function numbers)

bit 15-14

bit 13-8

bit 7-6

bit 5-0

**REGISTER 8-63:**

| U-0                   | U-0                                                                            | U-0                                   | U-0   | r-0                                     | r-0   | r-0   | r-0   |  |  |  |

|-----------------------|--------------------------------------------------------------------------------|---------------------------------------|-------|-----------------------------------------|-------|-------|-------|--|--|--|

| —                     | —                                                                              | —                                     |       | —                                       | —     |       | —     |  |  |  |

| bit 15                |                                                                                |                                       |       |                                         |       |       | bit 8 |  |  |  |

| R/W-1                 | R/W-0                                                                          | R/W-0                                 | R/W-1 | R/W-0                                   | R/W-1 | R/W-1 | R/W-0 |  |  |  |

|                       |                                                                                |                                       |       | )IV<7:0>                                |       |       |       |  |  |  |

| bit 7                 |                                                                                |                                       |       |                                         |       |       | bit 0 |  |  |  |

|                       |                                                                                |                                       |       |                                         |       |       |       |  |  |  |

| Legend:               |                                                                                | r = Reserved bi                       | •     |                                         |       |       |       |  |  |  |

| R = Readable          | e bit                                                                          | W = Writable bit                      | t     | U = Unimplemented bit, read as '0'      |       |       |       |  |  |  |

| -n = Value at         | POR                                                                            | '1' = Bit is set                      |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |  |

| bit 15-12<br>bit 11-8 | -                                                                              | nted: Read as '0'<br>/laintain as '0' |       |                                         |       |       |       |  |  |  |

| bit 7-0               | PLLFBDIV<7:0>: PLL Feedback Divider bits (also denoted as 'M', PLL multiplier) |                                       |       |                                         |       |       |       |  |  |  |

|                       | 11111111 =                                                                     | Reserved                              |       |                                         |       |       |       |  |  |  |

|                       | <br>11001000 =                                                                 | 200 Maximum <sup>(1)</sup>            |       |                                         |       |       |       |  |  |  |

|                       | <br>10010110 =                                                                 | 150 (default)                         |       |                                         |       |       |       |  |  |  |

|                       | <br>00010000 =                                                                 | : 16 Minimum <sup>(1)</sup>           |       |                                         |       |       |       |  |  |  |

|                       | <br>00000010 =<br>00000001 =<br>00000000 =                                     | Reserved                              |       |                                         |       |       |       |  |  |  |

**Note 1:** The allowed range is 16-200 (decimal). The rest of the values are reserved and should be avoided. The power on the default feedback divider is 150 (decimal) with an 8 MHz FRC input clock. The VCO frequency is 1.2 GHz.

# **REGISTER 11-21:** C1TXIFH: CAN TRANSMIT INTERRUPT STATUS REGISTER HIGH<sup>(1)</sup>

| R-0             | R-0 | R-0              | R-0                                | R-0                 | R-0 | R-0             | R-0   |

|-----------------|-----|------------------|------------------------------------|---------------------|-----|-----------------|-------|

|                 |     |                  | TFIF<                              | :31:24>             |     |                 |       |

| bit 15          |     |                  |                                    |                     |     |                 | bit 8 |

|                 |     |                  |                                    |                     |     |                 |       |

| R-0             | R-0 | R-0              | R-0                                | R-0                 | R-0 | R-0             | R-0   |

|                 |     |                  | TFIF<                              | :23:16>             |     |                 |       |

| bit 7           |     |                  |                                    |                     |     |                 | bit 0 |

|                 |     |                  |                                    |                     |     |                 |       |

| Legend:         |     |                  |                                    |                     |     |                 |       |

| R = Readable b  | bit | W = Writable bit | U = Unimplemented bit, read as '0' |                     |     |                 |       |

| -n = Value at P | OR  | '1' = Bit is set |                                    | '0' = Bit is cleare | ed  | x = Bit is unkn | own   |

bit 15-0 TFIF<31:16>: Unimplemented

Note 1: C1TXIFH: FIFO: TFIFx = 'or' of the enabled TX FIFO flags (flags need to be cleared in the FIFO register).

### **REGISTER 11-22:** C1TXIFL: CAN TRANSMIT INTERRUPT STATUS REGISTER LOW<sup>(1)</sup>

| R-0             | R-0                                                                  | R-0              | R-0   | R-0                  | R-0  | R-0             | R-0   |

|-----------------|----------------------------------------------------------------------|------------------|-------|----------------------|------|-----------------|-------|

|                 |                                                                      |                  | TFIF  | <15:8>               |      |                 |       |

| bit 15          |                                                                      |                  |       |                      |      |                 | bit 8 |

|                 |                                                                      |                  |       |                      |      |                 |       |

| R-0             | R-0                                                                  | R-0              | R-0   | R-0                  | R-0  | R-0             | R-0   |

|                 |                                                                      |                  | TFIF∙ | <7:0> <sup>(2)</sup> |      |                 |       |

| bit 7           |                                                                      |                  |       |                      |      |                 | bit 0 |

|                 |                                                                      |                  |       |                      |      |                 |       |

| Legend:         |                                                                      |                  |       |                      |      |                 |       |

| R = Readable I  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |       |                      |      |                 |       |

| -n = Value at P | OR                                                                   | '1' = Bit is set |       | '0' = Bit is clea    | ared | x = Bit is unkr | nown  |

|                 |                                                                      |                  |       |                      |      |                 |       |

bit 15-8 TFIF<15:8>: Unimplemented

bit 7-0 **TFIF<7:0>:** Transmit FIFO/TXQ Interrupt Pending bits<sup>(2)</sup>

1 = One or more enabled transmit FIFO/TXQ interrupts are pending

0 = No enabled transmit FIFO/TXQ interrupts are pending

Note 1: C1TXIFL: FIFO: TFIFx = 'or' of the enabled TX FIFO flags (flags need to be cleared in the FIFO register).

2: TFIF0 is for the transmit queue.

## REGISTER 11-49: C1BDIAG1L: CAN BUS DIAGNOSTICS REGISTER 1 LOW

| R/W-0                              | R/W-0 | R/W-0           | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-----------------|-----------------------------------------|------------------------------------|-------|-------|-------|

|                                    |       |                 | EFMSG                                   | CNT<15:8>                          |       |       |       |

| bit 15                             |       |                 |                                         |                                    |       |       | bit 8 |

|                                    |       |                 |                                         |                                    |       |       |       |

| R/W-0                              | R/W-0 | R/W-0           | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |                 | EFMSG                                   | GCNT<7:0>                          |       |       |       |

| bit 7                              |       |                 |                                         |                                    |       |       | bit 0 |

|                                    |       |                 |                                         |                                    |       |       |       |

| Legend:                            |       |                 |                                         |                                    |       |       |       |

| R = Readable                       | bit   | W = Writable bi | it                                      | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set |       |                 | '0' = Bit is cleared x = Bit is unknown |                                    |       | nown  |       |

bit 15-0 EFMSGCNT<15:0>: Error Free Message Counter bits

| R/W-0      | R/W-0                                                                       | U-0                                                                                                                                                                                       | R/W-0                                                      | U-0              | R/W-0                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0            |  |

|------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| REFCIE     | REFERCIE                                                                    | _                                                                                                                                                                                         | EIEN                                                       | —                | SHREISEL2(1)               | SHREISEL1(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SHREISEL0(1)     |  |

| bit 15     |                                                                             |                                                                                                                                                                                           |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 8            |  |

|            |                                                                             |                                                                                                                                                                                           |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |

| U-0        | R/W-0                                                                       | R/W-0                                                                                                                                                                                     | R/W-0                                                      | R/W-0            | R/W-0                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0            |  |

| _          | SHRADCS6                                                                    | SHRADCS5                                                                                                                                                                                  | SHRADCS4                                                   | SHRADCS3         | SHRADCS2                   | SHRADCS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SHRADCS0         |  |

| bit 7      |                                                                             |                                                                                                                                                                                           |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit C            |  |

|            |                                                                             |                                                                                                                                                                                           |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |

| Legend:    |                                                                             |                                                                                                                                                                                           |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |

| R = Reada  |                                                                             | W = Writable                                                                                                                                                                              |                                                            | -                | nented bit, read           | as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |  |

| -n = Value | at POR                                                                      | '1' = Bit is set                                                                                                                                                                          |                                                            | '0' = Bit is cle | ared                       | x = Bit is unkno                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | own              |  |

|            |                                                                             |                                                                                                                                                                                           |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |

| bit 15     |                                                                             | -                                                                                                                                                                                         | -                                                          | •                | mon Interrupt E            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |