Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-QFN (9x9)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck256mp206t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.4.1 PROGRAMMER'S MODEL

The programmer's model for the dsPIC33CK256MP508 family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33CK256MP508 devices contain control registers for Modulo Addressing, Bit-Reversed Addressing and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Figure 3-2.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

|            |                                          |

| Register(s) Name                  | Description                                                   |

|-----------------------------------|---------------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>     | Working Register Array                                        |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 1                            |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 2                            |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 3                            |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 4                            |

| ACCA, ACCB                        | 40-Bit DSP Accumulators (Additional 4 Alternate Accumulators) |

| PC                                | 23-Bit Program Counter                                        |

| SR                                | ALU and DSP Engine STATUS Register                            |

| SPLIM                             | Stack Pointer Limit Value Register                            |

| TBLPAG                            | Table Memory Page Address Register                            |

| DSRPAG                            | Extended Data Space (EDS) Read Page Register                  |

| RCOUNT                            | REPEAT Loop Counter Register                                  |

| DCOUNT                            | DO Loop Counter Register                                      |

| DOSTARTH, DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)                 |

| DOENDH, DOENDL                    | DO Loop End Address Register (High and Low)                   |

| CORCON                            | Contains DSP Engine, DO Loop Control and Trap Status bits     |

**Note 1:** Memory-mapped W0 through W14 represent the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

#### 4.1.3 UNIQUE DEVICE IDENTIFIER (UDID)

All dsPIC33CK256MP508 family devices are individually encoded during final manufacturing with a Unique Device Identifier or UDID. The UDID cannot be erased by a bulk erase command or any other user-accessible means. This feature allows for manufacturing traceability of Microchip Technology devices in applications where this is a requirement. It may also be used by the application manufacturer for any number of things that may require unique identification, such as:

- Tracking the device

- Unique serial number

- Unique security key

The UDID comprises five 24-bit program words. When taken together, these fields form a unique 120-bit identifier.

The UDID is stored in five read-only locations, located between 0x801200 and 0x801208 in the device configuration space. Table 4-1 lists the addresses of the identifier words and shows their contents

TABLE 4-1: UDID ADDRESSES

| UDID  | Address  | Description |

|-------|----------|-------------|

| UDID1 | 0x801200 | UDID Word 1 |

| UDID2 | 0x801202 | UDID Word 2 |

| UDID3 | 0x801204 | UDID Word 3 |

| UDID4 | 0x801206 | UDID Word 4 |

| UDID5 | 0x801208 | UDID Word 5 |

## 4.2 Data Address Space

The dsPIC33CK256MP508 family CPU has a separate 16-bit wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps are shown in Figure 4-7, Figure 4-8 and Figure 4-9.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes or 32K words.

The lower half of the data memory space (i.e., when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV).

The dsPIC33CK256MP508 family devices implement up to 16 Kbytes of data memory. If an EA points to a location outside of this area, an all-zero word or byte is returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33CK256MP508 family instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

| Register | Address | All Resets         | Register | Address | All Resets         | Register | Address | All Resets   |

|----------|---------|--------------------|----------|---------|--------------------|----------|---------|--------------|

| PPS      |         |                    | RPINR21  | D2E     | 111111111111111111 | RPOR4    | D88     | 000000000000 |

| RPCON    | D00     | 0                  | RPINR22  | D30     | 111111111111111111 | RPOR5    | D8A     | 000000000000 |

| RPINR0   | D04     | 11111111           | RPINR23  | D32     | 111111111          | RPOR6    | D8C     | 000000000000 |

| RPINR1   | D06     | 111111111111111111 | RPINR26  | D38     | 111111111          | RPOR7    | D8E     | 000000000000 |

| RPINR2   | D08     | 11111111           | RPINR27  | D3A     | 111111111111111111 | RPOR8    | D90     | 000000000000 |

| RPINR3   | D0A     | 111111111111111111 | RPINR29  | D3E     | 111111111111111111 | RPOR9    | D92     | 000000000000 |

| RPINR4   | D0C     | 111111111111111111 | RPINR30  | D40     | 111111111          | RPOR10   | D94     | 000000000000 |

| RPINR5   | D0E     | 111111111111111111 | RPINR32  | D44     | 11111111           | RPOR11   | D96     | 000000000000 |

| RPINR6   | D10     | 111111111111111111 | RPINR33  | D46     | 111111111          | RPOR12   | D98     | 000000000000 |

| RPINR7   | D12     | 111111111111111111 | RPINR37  | D4E     | 111111111111111111 | RPOR13   | D9A     | 000000000000 |

| RPINR8   | D14     | 111111111111111111 | RPINR38  | D50     | 111111111          | RPOR14   | D9C     | 000000000000 |

| RPINR9   | D16     | 111111111111111111 | RPINR42  | D58     | 111111111111111111 | RPOR15   | D9E     | 000000000000 |

| RPINR10  | D18     | 111111111111111111 | RPINR43  | D5A     | 111111111111111111 | RPOR16   | DA0     | 000000000000 |

| RPINR11  | D1A     | 111111111111111111 | RPINR44  | D5C     | 111111111111111111 | RPOR17   | DA2     | 000000000000 |

| RPINR12  | D1C     | 111111111111111111 | RPINR45  | D5E     | 111111111111111111 | RPOR18   | DA4     | 000000000000 |

| RPINR13  | D1E     | 111111111111111111 | RPINR46  | D60     | 111111111111111111 | RPOR19   | DA6     | 000000000000 |

| RPINR14  | D20     | 111111111111111111 | RPINR47  | D62     | 111111111111111111 | RPOR20   | DA8     | 000000000000 |

| RPINR15  | D22     | 111111111111111111 | RPINR48  | D64     | 111111111111111111 | RPOR21   | DAA     | 000000000000 |

| RPINR16  | D24     | 111111111111111111 | RPINR49  | D66     | 111111111          | RPOR22   | DAC     | 000000000000 |

| RPINR17  | D26     | 111111111111111111 | RPOR0    | D80     | 000000000000       | RPOR23   | DAE     | 000000000000 |

| RPINR18  | D28     | 111111111111111111 | RPOR1    | D82     | 000000000000       | RPOR24   | DB0     | 000000000000 |

| RPINR19  | D2A     | 111111111111111111 | RPOR2    | D84     | 000000000000       | RPOR25   | DB2     | 000000000000 |

| RPINR20  | D2C     | 111111111111111111 | RPOR3    | D86     | 000000000000       | RPOR26   | DB4     | 000000000000 |

#### TABLE 4-14: SFR BLOCK D00h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address values are in hexadecimal. Reset values are in binary.

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices.

The dsPIC33CK256MP508 family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33CK256MP508 family CPU.

The interrupt controller has the following features:

- Six Processor Exceptions and Software Traps

- · Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Fixed Interrupt Entry and Return Latencies

- Alternate Interrupt Vector Table (AIVT) for Debug Support

## 7.1 Interrupt Vector Table

The dsPIC33CK256MP508 family Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains six non-maskable trap vectors and up to 246 sources of interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-2, is available only when the Boot Segment (BS) is defined and the AIVT has been enabled. To enable the Alternate Interrupt Vector Table, the Configuration bit, AIVTDIS in the FSEC register, must be programmed and the AIVTEN bit must be set (INTCON2<8> = 1). When the AIVT is enabled, all interrupt and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment, defined by BSLIM<12:0>. The second half of the page is no longer usable space. The Boot Segment must be at least 2 pages to enable the AIVT.

Note: Although the Boot Segment must be enabled in order to enable the AIVT, application code does not need to be present inside of the Boot Segment. The AIVT (and IVT) will inherit the Boot Segment code protection.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33CK256MP508 family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 8-12: CNFx: INTERRUPT CHANGE NOTIFICATION FLAG FOR PORTx REGISTER

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------|-------|--------|-------|-------|-------|

|         |       |       | CNFx  | <15:8> |       |       |       |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | CNFx  | <7:0>  |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| Ecgenia.          |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 15- CNFx<15:0>: Interrupt Change Notification Flag for PORTx bits

When CNSTYLE (CNCONx<11>) = 1:

1 = An enabled edge event occurred on the PORTx[n] pin

0 = An enabled edge event did not occur on the PORTx[n] pin

Unimplemented: Read as '0'

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

|-----------------|-----|------------------|--------|-----------------------------------------|--------|--------|--------|

| —               | —   | RP33R5           | RP33R4 | RP33R3                                  | RP33R2 | RP33R1 | RP33R0 |

| bit 15          |     |                  |        |                                         |        |        | bit 8  |

|                 |     |                  |        |                                         |        |        |        |

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

| —               | —   | RP32R5           | RP32R4 | RP32R3                                  | RP32R2 | RP32R1 | RP32R0 |

| bit 7           |     |                  |        |                                         |        |        | bit 0  |

|                 |     |                  |        |                                         |        |        |        |

| Legend:         |     |                  |        |                                         |        |        |        |

| R = Readable    | bit | W = Writable     | bit    | U = Unimplemented bit, read as '0'      |        |        |        |

| -n = Value at F | POR | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |        |        | nown   |

#### REGISTER 8-54: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| bit 13-8 | <b>RP33R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP33 Output Pin bits (see Table 8-7 for peripheral function numbers) |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                              |

| bit 5-0  | <b>RP32R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP32 Output Pin bits (see Table 8-7 for peripheral function numbers) |

#### REGISTER 8-55: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0                                | U-0                                                                                     | R/W-0          | R/W-0                           | R/W-0        | R/W-0            | R/W-0    | R/W-0  |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------|----------------|---------------------------------|--------------|------------------|----------|--------|--|--|

| _                                  | —                                                                                       | RP35R5         | RP35R4                          | RP35R3       | RP35R2           | RP35R1   | RP35R0 |  |  |

| bit 15                             | ÷                                                                                       |                |                                 |              | ·                |          | bit 8  |  |  |

|                                    |                                                                                         |                |                                 |              |                  |          |        |  |  |

| U-0                                | U-0                                                                                     | R/W-0          | R/W-0                           | R/W-0        | R/W-0            | R/W-0    | R/W-0  |  |  |

|                                    | —                                                                                       | RP34R5         | RP34R4                          | RP34R3       | RP34R2           | RP34R1   | RP34R0 |  |  |

| bit 7                              |                                                                                         |                |                                 |              |                  |          | bit 0  |  |  |

|                                    |                                                                                         |                |                                 |              |                  |          |        |  |  |

| Legend:                            |                                                                                         |                |                                 |              |                  |          |        |  |  |

| R = Readable                       | e bit                                                                                   | W = Writable   | bit                             | U = Unimpler | mented bit, read | l as '0' |        |  |  |

| -n = Value at POR '1' = Bit is set |                                                                                         |                | '0' = Bit is cleared x = Bit is |              |                  | unknown  |        |  |  |

|                                    |                                                                                         |                |                                 |              |                  |          |        |  |  |

| bit 15-14                          | Unimplemen                                                                              | ted: Read as ' | כי                              |              |                  |          |        |  |  |

| bit 13-8                           | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits |                |                                 |              |                  |          |        |  |  |

(see Table 8-7 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP34R<5:0>:** Peripheral Output Function is Assigned to RP34 Output Pin bits (see Table 8-7 for peripheral function numbers)

bit 15-14

# 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note 1: This data sheet summarizes the features of this group of dsPIC33 devices. It is not intended to be a comprehensive reference source. For more information, refer to "Direct Memory Access Controller (DMA)" (DS39742) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Direct Memory Access (DMA) Controller is designed to service high data throughput peripherals operating on the SFR bus, allowing them to access data memory directly and alleviating the need for CPU-intensive management. By allowing these data-intensive peripherals to share their own data path, the main data bus is also deloaded, resulting in additional power savings.

The DMA Controller functions both as a peripheral and a direct extension of the CPU. It is located on the microcontroller data bus, between the CPU and DMA-enabled peripherals, with direct access to SRAM. This partitions the SFR bus into two buses, allowing the DMA Controller access to the DMA-capable peripherals located on the new DMA SFR bus. The controller serves as a Master device on the DMA SFR bus, controlling data flow from DMA-capable peripherals. The controller also monitors CPU instruction processing directly, allowing it to be aware of when the CPU requires access to peripherals on the DMA bus and automatically relinquishing control to the CPU as needed. This increases the effective bandwidth for handling data without DMA operations, causing a processor Stall. This makes the controller essentially transparent to the user.

The DMA Controller has these features:

- Four Independently Programmable Channels

- Concurrent Operation with the CPU (no DMA caused Wait states)

- DMA Bus Arbitration

- Five Programmable Address modes

- Four Programmable Transfer modes

- Four Flexible Internal Data Transfer modes

- Byte or Word Support for Data Transfer

- 16-Bit Source and Destination Address Register for each Channel, Dynamically Updated and Reloadable

- 16-Bit Transaction Count Register, Dynamically Updated and Reloadable

- Upper and Lower Address Limit Registers

- Counter Half-Full Level Interrupt

- Software Triggered Transfer

- Null Write mode for Symmetric Buffer Operations

- A simplified block diagram of the DMA Controller is shown if Figure 10-1.

#### REGISTER 11-25: C1TXREQH: CAN TRANSMIT REQUEST REGISTER HIGH

| S/HC-0          | S/HC-0 | S/HC-0           | S/HC-0 | S/HC-0                                  | S/HC-0          | S/HC-0 | S/HC-0 |  |  |  |

|-----------------|--------|------------------|--------|-----------------------------------------|-----------------|--------|--------|--|--|--|

| TXREQ<31:24>    |        |                  |        |                                         |                 |        |        |  |  |  |

| bit 15 bit 8    |        |                  |        |                                         |                 |        |        |  |  |  |

|                 |        |                  |        |                                         |                 |        |        |  |  |  |

| S/HC-0          | S/HC-0 | S/HC-0           | S/HC-0 | S/HC-0                                  | S/HC-0          | S/HC-0 | S/HC-0 |  |  |  |

|                 |        |                  | TXREQ  | <23:16>                                 |                 |        |        |  |  |  |

| bit 7           |        |                  |        |                                         |                 |        | bit 0  |  |  |  |

|                 |        |                  |        |                                         |                 |        |        |  |  |  |

| Legend:         |        | S = Settable bit | t      | HC = Hardwa                             | are Clearable b | it     |        |  |  |  |

| R = Readable    | bit    | W = Writable bi  | it     | U = Unimplemented bit, read as '0'      |                 |        |        |  |  |  |

| -n = Value at F | POR    | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |                 |        | nown   |  |  |  |

#### bit 15-0 TXREQ<31:16>: Unimplemented

#### REGISTER 11-26: C1TXREQL: CAN TRANSMIT REQUEST REGISTER LOW

| S/HC-0        | S/HC-0                                                                                                                                                                                                          | S/HC-0                                                        | S/HC-0        | S/HC-0                                  | S/HC-0          | S/HC-0 | S/HC-0 |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------|-----------------------------------------|-----------------|--------|--------|--|

|               |                                                                                                                                                                                                                 |                                                               | TXREC         | 2<15:8>                                 |                 |        |        |  |

| bit 15        |                                                                                                                                                                                                                 |                                                               |               |                                         |                 |        | bit 8  |  |

|               |                                                                                                                                                                                                                 |                                                               |               |                                         |                 |        |        |  |

| S/HC-0        | S/HC-0                                                                                                                                                                                                          | S/HC-0                                                        | S/HC-0        | S/HC-0                                  | S/HC-0          | S/HC-0 | S/HC-0 |  |

|               |                                                                                                                                                                                                                 |                                                               | TXREQ<7:1>    |                                         |                 |        | TXREQ0 |  |

| bit 7         |                                                                                                                                                                                                                 |                                                               |               |                                         |                 |        | bit 0  |  |

|               |                                                                                                                                                                                                                 |                                                               |               |                                         |                 |        |        |  |

| Legend:       |                                                                                                                                                                                                                 | S = Settable b                                                | it            | HC = Hardwa                             | are Clearable b | it     |        |  |

| R = Readabl   | e bit                                                                                                                                                                                                           | W = Writable b                                                | pit           | U = Unimplemented bit, read as '0'      |                 |        |        |  |

| -n = Value at | POR                                                                                                                                                                                                             | '1' = Bit is set                                              |               | '0' = Bit is cleared x = Bit is unknown |                 |        |        |  |

|               |                                                                                                                                                                                                                 |                                                               |               |                                         |                 |        |        |  |

| bit 15-8      | TXREQ<15:                                                                                                                                                                                                       | 8>: Unimplemen                                                | nted          |                                         |                 |        |        |  |

| bit 7-1       | TXREQ<7:1                                                                                                                                                                                                       | >: Message Sen                                                | d Request bit | S                                       |                 |        |        |  |

|               | <u>TXEN = 1 (c</u>                                                                                                                                                                                              | bject configured                                              | as a transmit | object):                                |                 |        |        |  |

|               | Setting this bit to '1' requests sending a message. The bit will automatically clear when the message(s) queued in the object is (are) successfully sent. This bit can NOT be used for aborting a transmission. |                                                               |               |                                         |                 |        |        |  |

|               | TXEN = 0 (object configured as a receive object):<br>This bit has no effect.                                                                                                                                    |                                                               |               |                                         |                 |        |        |  |

| bit 0         | Setting this b                                                                                                                                                                                                  | ransmit Queue N<br>bit to '1' requests<br>e object is (are) s | sending a me  | ssage. The bit                          |                 |        |        |  |

| REGISTER 12-13: F | PGxCONH: PWM GENERATOR x CONTROL REGISTER H | HIGH |

|-------------------|---------------------------------------------|------|

|-------------------|---------------------------------------------|------|

| R/W-0      | R/W-0           | R/W-0                                                                                                                                            | U-0             | R/W-0                    | R/W-0                           | R/W-0                    | R/W-0                    |  |  |  |  |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|---------------------------------|--------------------------|--------------------------|--|--|--|--|

| MDCSE      | L MPERSEL       | MPHSEL                                                                                                                                           |                 | MSTEN                    | UPMOD2                          | UPMOD1                   | UPMOD0                   |  |  |  |  |

| bit 15     | ·               |                                                                                                                                                  |                 |                          |                                 |                          | bit 8                    |  |  |  |  |

|            | DAMA            |                                                                                                                                                  |                 |                          | <b>D</b> 444 0                  |                          | DAMA                     |  |  |  |  |

| r-0        | R/W-0           | U-0                                                                                                                                              | U-0             | R/W-0                    | R/W-0                           | R/W-0                    | R/W-0                    |  |  |  |  |

|            | TRGMOD          | —                                                                                                                                                |                 | SOCS3 <sup>(1,2,3)</sup> | SOCS2 <sup>(1,2,3)</sup>        | SOCS1 <sup>(1,2,3)</sup> | SOCS0 <sup>(1,2,3)</sup> |  |  |  |  |

| bit 7      |                 |                                                                                                                                                  |                 |                          |                                 |                          | bit                      |  |  |  |  |

| Legend:    |                 | r = Reserved                                                                                                                                     | bit             |                          |                                 |                          |                          |  |  |  |  |

| R = Read   | able bit        | W = Writable                                                                                                                                     | bit             | U = Unimpleme            | ented bit, read as              | '0'                      |                          |  |  |  |  |

| -n = Value | at POR          | '1' = Bit is set                                                                                                                                 |                 | '0' = Bit is clear       |                                 | x = Bit is unkne         | own                      |  |  |  |  |

|            |                 |                                                                                                                                                  |                 |                          |                                 |                          |                          |  |  |  |  |

| bit 15     |                 | laster Duty Cy                                                                                                                                   | -               |                          |                                 |                          |                          |  |  |  |  |

|            |                 | enerator uses                                                                                                                                    | •               |                          |                                 |                          |                          |  |  |  |  |

| L:1 4 4    |                 | enerator uses                                                                                                                                    | -               |                          |                                 |                          |                          |  |  |  |  |

| bit 14     |                 | Master Period                                                                                                                                    | •               |                          |                                 |                          |                          |  |  |  |  |

|            |                 | enerator uses<br>enerator uses                                                                                                                   |                 |                          |                                 |                          |                          |  |  |  |  |

| bit 13     |                 | MPHSEL: Master Phase Register Select bit                                                                                                         |                 |                          |                                 |                          |                          |  |  |  |  |

|            |                 | 1 = PWM Generator uses MPHASE register                                                                                                           |                 |                          |                                 |                          |                          |  |  |  |  |

|            |                 | 0 = PWM Generator uses PGxPHASE register                                                                                                         |                 |                          |                                 |                          |                          |  |  |  |  |

| bit 12     | Unimpleme       | Unimplemented: Read as '0'                                                                                                                       |                 |                          |                                 |                          |                          |  |  |  |  |

| bit 11     | MSTEN: Ma       | ster Update E                                                                                                                                    | nable bit       |                          |                                 |                          |                          |  |  |  |  |

|            |                 |                                                                                                                                                  | dcasts softw    | /are set/clear of t      | he UPDREQ stat                  | us bit and EOC           | signal to othe           |  |  |  |  |

|            | -               | enerators                                                                                                                                        | not broode      |                          |                                 |                          |                          |  |  |  |  |

| 1:140.0    |                 |                                                                                                                                                  |                 |                          | status bit state o              | r EOC signal             |                          |  |  |  |  |

| bit 10-8   |                 | ed immediate u                                                                                                                                   |                 | ode Selection bit        | S                               |                          |                          |  |  |  |  |

|            |                 |                                                                                                                                                  | •               | is soon as possib        | le, when a Maste                | r update reques          | t is received.           |  |  |  |  |

|            |                 |                                                                                                                                                  | est will be tra | ansmitted if MSTE        | EN = 1 and UPDA                 | TE = 1 for the re        | equesting PWI            |  |  |  |  |

|            |                 | erator.                                                                                                                                          |                 |                          |                                 |                          |                          |  |  |  |  |

|            |                 | ed SOC update<br>registers at st                                                                                                                 |                 | cycle if a Master        | update request                  | is received A            | master undat             |  |  |  |  |

|            |                 |                                                                                                                                                  |                 |                          | PDATE = 1 for the               |                          |                          |  |  |  |  |

|            |                 | ediate update                                                                                                                                    |                 |                          |                                 |                          |                          |  |  |  |  |

|            |                 |                                                                                                                                                  |                 |                          | ble, if UPDATE = $(UPDATE = 1)$ |                          |                          |  |  |  |  |

|            |                 |                                                                                                                                                  |                 | update occurs.           | (UPDATE = 1).                   | THE OFDATE S             | latus dit will d         |  |  |  |  |

|            | 000 = SOC       |                                                                                                                                                  |                 |                          |                                 |                          |                          |  |  |  |  |

|            |                 | registers at sta<br>natically after t                                                                                                            |                 |                          | ATE = 1. The UP                 | DATE status bit          | will be cleare           |  |  |  |  |

| bit 7      |                 | Maintain as '0'                                                                                                                                  |                 |                          |                                 |                          |                          |  |  |  |  |

| Note 1:    | The PCI selecte | ed Sync signal                                                                                                                                   | is always a     | vailable to be OR        | d with the select               | ed SOC signal (          | per the                  |  |  |  |  |

|            | SOCS<3:0> bits  | s if the PCI Sy                                                                                                                                  | nc function i   | s enabled.               |                                 |                          |                          |  |  |  |  |

| 2:         |                 | •                                                                                                                                                |                 | •                        | e from the same of              |                          |                          |  |  |  |  |

|            |                 |                                                                                                                                                  |                 | -                        | CI Sync logic so t              | ne trigger signa         | ii may be                |  |  |  |  |

| 3.         | -               | nchronized to the PWM Generator clock domain.<br>/M Generators are grouped into groups of four: PG1-PG4 and PG5-PG8, if available. Any generator |                 |                          |                                 |                          |                          |  |  |  |  |

**3:** PWM Generators are grouped into groups of four: PG1-PG4 and PG5-PG8, if available. Any generator within a group of four may be used to trigger another generator within the same group.

| REGISTER 13-0. ADCON4R. ADC CONTROL REGISTER 4 HIGH | REGISTER 13-8: | ADCON4H: ADC CONTROL REGISTER 4 HIGH |

|-----------------------------------------------------|----------------|--------------------------------------|

|-----------------------------------------------------|----------------|--------------------------------------|

| U-0          | U-0             | U-0              | U-0           | U-0                                | U-0              | U-0             | U-0    |  |  |

|--------------|-----------------|------------------|---------------|------------------------------------|------------------|-----------------|--------|--|--|

| _            | —               | —                | _             | —                                  | —                | —               | _      |  |  |

| bit 15       |                 |                  |               | ·                                  |                  |                 | bit 8  |  |  |

|              |                 |                  |               |                                    |                  |                 |        |  |  |

| U-0          | U-0             | U-0              | U-0           | R/W-0                              | R/W-0            | R/W-0           | R/W-0  |  |  |

| _            | —               | —                |               | C1CHS1                             | C1CHS0           | C0CHS1          | C0CHS0 |  |  |

| bit 7        |                 |                  |               | •                                  |                  |                 | bit 0  |  |  |

|              |                 |                  |               |                                    |                  |                 |        |  |  |

| Legend:      |                 |                  |               |                                    |                  |                 |        |  |  |

| R = Readat   | ole bit         | W = Writable b   | oit           | U = Unimplem                       | nented bit, read | l as '0'        |        |  |  |

| -n = Value a | at POR          | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is un |                  | x = Bit is unkr | known  |  |  |

|              |                 |                  |               |                                    |                  |                 |        |  |  |

| bit 15-4     | Unimplemen      | ted: Read as '0  | )'            |                                    |                  |                 |        |  |  |

| bit 3-2      | C1CHS<1:0>      | : Dedicated AD   | C Core 1 Inpu | t Channel Sele                     | ction bits       |                 |        |  |  |

|              | 11 = Reserve    | d                |               |                                    |                  |                 |        |  |  |

|              | 10 = Reserve    | d                |               |                                    |                  |                 |        |  |  |

|              | 01 = ANA1       |                  |               |                                    |                  |                 |        |  |  |

|              | 00 <b>= AN1</b> |                  |               |                                    |                  |                 |        |  |  |

#### bit 1-0 COCHS<1:0>: Dedicated ADC Core 0 Input Channel Selection bits

11 = Reserved

10 = Reserved

01 = ANA0

00 **= AN0**

| R/W-0                   | U-0                                                           | R/W-0                                      | U-0                         | U-0                            | U-0                     | U-0                     | U-0                    |  |  |  |

|-------------------------|---------------------------------------------------------------|--------------------------------------------|-----------------------------|--------------------------------|-------------------------|-------------------------|------------------------|--|--|--|

| DACON                   | _                                                             | DACSIDL                                    | _                           | _                              | _                       |                         | —                      |  |  |  |

| bit 15                  |                                                               | •                                          | ·                           |                                |                         |                         | bit 8                  |  |  |  |

|                         |                                                               |                                            |                             |                                |                         |                         |                        |  |  |  |

| R/W-0                   | R/W-0                                                         | R/W-0                                      | R/W-0                       | U-0                            | R/W-0                   | R/W-0                   | R/W-0                  |  |  |  |

| CLKSEL1(1,3)            | CLKSEL0 <sup>(1,3)</sup>                                      | CLKDIV1 <sup>(1,3)</sup>                   | CLKDIV0 <sup>(1,3)</sup>    | —                              | FCLKDIV2 <sup>(2)</sup> | FCLKDIV1 <sup>(2)</sup> | FCLKDIV0 <sup>(2</sup> |  |  |  |

| bit 7                   |                                                               |                                            |                             |                                |                         |                         | bit (                  |  |  |  |

| Lonordi                 |                                                               |                                            |                             |                                |                         |                         |                        |  |  |  |

| Legend:<br>R = Readable | , hit                                                         | W = Writable b                             | :+                          | II – Unimpl                    | emented bit, rea        | d aa '0'                |                        |  |  |  |

| -n = Value at           |                                                               | '1' = Bit is set                           | ut.                         | 0 = 011111pr<br>'0' = Bit is c |                         |                         |                        |  |  |  |

|                         | FUR                                                           | I – Dit is set                             |                             |                                | lealeu                  |                         |                        |  |  |  |

| bit 15                  | DACON: Corr                                                   | nmon DAC Mod                               | ule Enable bit              |                                |                         |                         |                        |  |  |  |

|                         | 1 = Enables [                                                 |                                            |                             |                                |                         |                         |                        |  |  |  |

|                         |                                                               |                                            |                             |                                | to reduce powe          | er consumption          | ; any pending          |  |  |  |

|                         | -                                                             | de and/or unde                             |                             | are cleared                    |                         |                         |                        |  |  |  |

| bit 14                  | -                                                             | ted: Read as '0'                           |                             |                                |                         |                         |                        |  |  |  |

| bit 13                  |                                                               | AC Stop in Idle N                          |                             |                                |                         |                         |                        |  |  |  |

|                         |                                                               | ues module operati                         |                             |                                | le mode                 |                         |                        |  |  |  |

| bit 12-8                |                                                               | •                                          |                             |                                |                         |                         |                        |  |  |  |

| bit 7-6                 | -                                                             | t <b>ed:</b> Read as '0'<br>>: DAC Clock S |                             | <sub>-</sub> (1.3)             |                         |                         |                        |  |  |  |

| DIL 7-0                 | 11 = FPLLO                                                    | DAC CIUCK S                                | ource Select bit            | 5                              |                         |                         |                        |  |  |  |

|                         | 10 = AFPLLO                                                   |                                            |                             |                                |                         |                         |                        |  |  |  |

|                         | 01 = Fvco/2                                                   |                                            |                             |                                |                         |                         |                        |  |  |  |

|                         | 00 = AFvco/2                                                  |                                            | (4.0)                       |                                |                         |                         |                        |  |  |  |

| bit 5-4                 |                                                               | : DAC Clock Di                             | vider bits <sup>(1,3)</sup> |                                |                         |                         |                        |  |  |  |

|                         | 11 = Divide-by-4<br>10 = Divide-by-3 (non-uniform duty cycle) |                                            |                             |                                |                         |                         |                        |  |  |  |

|                         | 10 = Divide-by<br>01 = Divide-by                              |                                            | i duty cycle)               |                                |                         |                         |                        |  |  |  |

|                         | 00 = 1x                                                       | y-2                                        |                             |                                |                         |                         |                        |  |  |  |

| bit 3                   | Unimplement                                                   | ted: Read as '0'                           |                             |                                |                         |                         |                        |  |  |  |

| bit 2-0                 | -                                                             | >: Comparator                              |                             | der bits <sup>(2)</sup>        |                         |                         |                        |  |  |  |

|                         | 111 = Divide-l                                                | •                                          |                             |                                |                         |                         |                        |  |  |  |

|                         | 110 = Divide-by-7                                             |                                            |                             |                                |                         |                         |                        |  |  |  |

|                         | 101 = Divide-l                                                |                                            |                             |                                |                         |                         |                        |  |  |  |

|                         | 100 = Divide-l<br>011 = Divide-l                              |                                            |                             |                                |                         |                         |                        |  |  |  |

|                         | 010 = Divide-l                                                |                                            |                             |                                |                         |                         |                        |  |  |  |

|                         | 001 = Divide-l                                                |                                            |                             |                                |                         |                         |                        |  |  |  |

|                         | 000 = 1x                                                      |                                            |                             |                                |                         |                         |                        |  |  |  |

| Note 1: Th              | ese bits should                                               | only be change                             | d when DACON                | l = 0 to avoid                 | d unpredictable l       | behavior.               |                        |  |  |  |

|                         |                                                               | • •                                        |                             |                                | SEL<1:0>, and t         |                         | 2.                     |  |  |  |

|                         | -                                                             |                                            |                             |                                |                         | ,                       |                        |  |  |  |

#### REGISTER 14-1: DACCTRL1L: DAC CONTROL 1 LOW REGISTER

- 3: Clock source and dividers should yield an effective DAC clock input of 500 MHz.

# 15.0 QUADRATURE ENCODER INTERFACE (QEI)

Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive resource. For more information, refer to "Quadrature Encoder Interface (QEI)" (DS70000601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Quadrature Encoder Interface (QEI) module provides the interface to incremental encoders for obtaining mechanical position data. The dsPIC33CK256MP508 family implements 2 instances of the QEI. Quadrature Encoders, also known as incremental encoders or optical encoders, detect position and speed of rotating motion systems. Quadrature Encoders enable closed-loop control of motor control applications, such as Switched Reluctance (SR) and AC Induction Motors (ACIM).

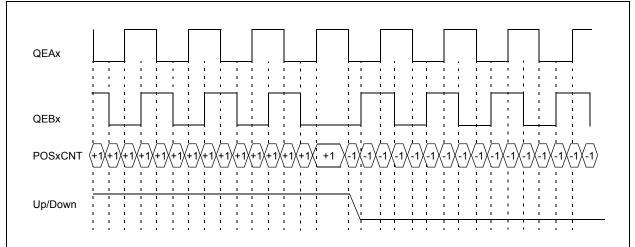

A typical Quadrature Encoder includes a slotted wheel attached to the shaft of the motor and an emitter/ detector module that senses the slots in the wheel. Typically, three output channels, Phase A (QEAx), Phase B (QEBx) and Index (INDXx), provide information on the movement of the motor shaft, including distance and direction.

The two channels, Phase A (QEAx) and Phase B (QEBx), are typically 90 degrees out of phase with respect to each other. The Phase A and Phase B channels have a unique relationship. If Phase A leads Phase B, the direction of the motor is deemed positive or forward. If Phase A lags Phase B, the direction of the motor is deemed negative or reverse. The Index pulse occurs once per mechanical revolution and is used as a reference to indicate an absolute position. Figure 15-1 illustrates the Quadrature Encoder Interface signals.

The Quadrature signals from the encoder can have four unique states ('01', '00', '10' and '11') that reflect the relationship between QEAx and QEBx. Figure 15-1 illustrates these states for one count cycle. The order of the states get reversed when the direction of travel changes.

The Quadrature Decoder increments or decrements the 32-bit up/down Position x Counter (POSxCNTH/L) registers for each Change-of-State (COS). The counter increments when QEAx leads QEBx and decrements when QEBx leads QEAx.

## FIGURE 15-1: QUADRATURE ENCODER INTERFACE SIGNALS

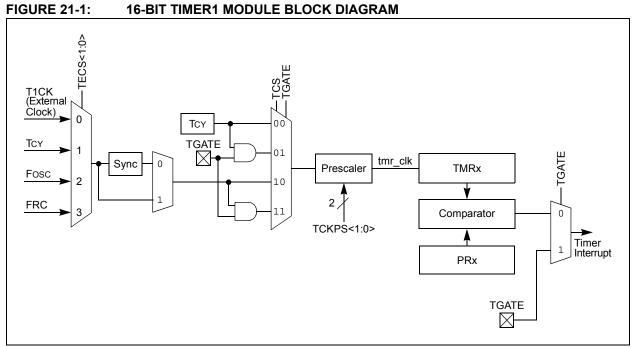

#### 21.0 TIMER1

Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- · Can be Operated in Asynchronous Counter mode

- · Asynchronous Timer

- · Operational during CPU Sleep mode

- Software Selectable Prescalers 1:1, 1:8, 1:64 and 1:256

- External Clock Selection Control

- The Timer1 External Clock Input (T1CK) can Optionally be Synchronized to the Internal Device Clock and the Clock Synchronization is Performed after the Prescaler

If Timer1 is used for SCCP, the timer should be running in Synchronous mode.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

- A block diagram of Timer1 is shown in Figure 21-1.

| R/W-0                 | R/W-0                                              | U-0                                    | U-0            | R/W-0                                | R/W-0               | R/W-0               | R/W-0               |  |  |  |

|-----------------------|----------------------------------------------------|----------------------------------------|----------------|--------------------------------------|---------------------|---------------------|---------------------|--|--|--|

| OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup>                              |                                        | _              | OPS3 <sup>(3)</sup>                  | OPS2 <sup>(3)</sup> | OPS1 <sup>(3)</sup> | OPS0 <sup>(3)</sup> |  |  |  |

| bit 15                |                                                    |                                        |                |                                      |                     |                     | bit 8               |  |  |  |

|                       |                                                    |                                        |                |                                      |                     |                     |                     |  |  |  |

| R/W-0                 | R/W-0                                              | R/W-0                                  | R/W-0          | R/W-0                                | R/W-0               | R/W-0               | R/W-0               |  |  |  |

| TRIGEN                | ONESHOT                                            | ALTSYNC                                | SYNC4          | SYNC3                                | SYNC2               | SYNC1               | SYNC0               |  |  |  |

| bit 7                 |                                                    |                                        |                |                                      |                     |                     | bit (               |  |  |  |

| Legend:               |                                                    |                                        |                |                                      |                     |                     |                     |  |  |  |

| R = Readable          | e bit                                              | W = Writable I                         | oit            | U = Unimplem                         | nented bit, read    | d as '0'            |                     |  |  |  |

| -n = Value at         | POR                                                | '1' = Bit is set                       |                | '0' = Bit is clea                    | ared                | x = Bit is unkr     | nown                |  |  |  |

|                       |                                                    |                                        |                |                                      |                     |                     |                     |  |  |  |

| bit 15                | OPSSRC: Ou                                         | itput Postscaler                       | Source Sele    | ct bit <sup>(1)</sup>                |                     |                     |                     |  |  |  |

|                       |                                                    |                                        |                | er output events                     | 6                   |                     |                     |  |  |  |

|                       |                                                    | ostscaler scales                       |                | terrupt events                       |                     |                     |                     |  |  |  |

| bit 14                |                                                    | etrigger Enable l<br>se can be retrigg |                | DICEN hit - 1                        |                     |                     |                     |  |  |  |

|                       |                                                    |                                        |                | en TRIGEN bit =                      | • 1                 |                     |                     |  |  |  |

| bit 13-12             |                                                    | ted: Read as 'o                        |                |                                      |                     |                     |                     |  |  |  |

| bit 11-8              | OPS3<3:0>:                                         | CCPx Interrupt                         | Output Posts   | cale Select bits <sup>(;</sup>       | 3)                  |                     |                     |  |  |  |

|                       | 1111 = Interrupt every 16th time base period match |                                        |                |                                      |                     |                     |                     |  |  |  |

|                       |                                                    | upt every 15th t                       | ime base per   | iod match                            |                     |                     |                     |  |  |  |

|                       | <br>0100 = Interr                                  | upt every 5th tir                      | ne base peric  | d match                              |                     |                     |                     |  |  |  |

|                       | 0011 = Interr                                      | upt every 4th tir                      | ne base peric  | d match or 4th i                     | • •                 |                     |                     |  |  |  |

|                       |                                                    |                                        |                | d match or 3rd i                     |                     |                     |                     |  |  |  |

|                       |                                                    |                                        |                | od match or 2nd<br>od match or inpu  |                     |                     |                     |  |  |  |

| bit 7                 |                                                    | Px Trigger Enal                        | -              |                                      |                     |                     |                     |  |  |  |

|                       |                                                    | peration of time                       |                | ed                                   |                     |                     |                     |  |  |  |

|                       |                                                    | peration of time                       |                |                                      |                     |                     |                     |  |  |  |

| bit 6                 |                                                    | one-Shot Trigge                        |                |                                      |                     |                     |                     |  |  |  |

|                       |                                                    | t Trigger mode<br>t Trigger mode       |                | gger duration is                     | set by OSCN         | Γ<2:0>              |                     |  |  |  |

| bit 5                 |                                                    | CPx Clock Sele                         |                |                                      |                     |                     |                     |  |  |  |

|                       |                                                    |                                        |                | dule synchroniza<br>gnal is the Time |                     |                     |                     |  |  |  |

| bit 4-0               |                                                    | CCPx Synchro                           | -              | -                                    |                     |                     |                     |  |  |  |