Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 24K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck256mp206t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.4.1 PROGRAMMER'S MODEL

The programmer's model for the dsPIC33CK256MP508 family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33CK256MP508 devices contain control registers for Modulo Addressing, Bit-Reversed Addressing and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Figure 3-2.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

|            |                                          |

| Register(s) Name                  | Description                                                   |  |  |  |

|-----------------------------------|---------------------------------------------------------------|--|--|--|

| W0 through W15 <sup>(1)</sup>     | Working Register Array                                        |  |  |  |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 1                            |  |  |  |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 2                            |  |  |  |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 3                            |  |  |  |

| W0 through W14 <sup>(1)</sup>     | Alternate Working Register Array 4                            |  |  |  |

| ACCA, ACCB                        | 40-Bit DSP Accumulators (Additional 4 Alternate Accumulators) |  |  |  |

| PC                                | 23-Bit Program Counter                                        |  |  |  |

| SR                                | ALU and DSP Engine STATUS Register                            |  |  |  |

| SPLIM                             | Stack Pointer Limit Value Register                            |  |  |  |

| TBLPAG                            | Table Memory Page Address Register                            |  |  |  |

| DSRPAG                            | Extended Data Space (EDS) Read Page Register                  |  |  |  |

| RCOUNT                            | REPEAT Loop Counter Register                                  |  |  |  |

| DCOUNT                            | DO Loop Counter Register                                      |  |  |  |

| DOSTARTH, DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)                 |  |  |  |

| DOENDH, DOENDL                    | DO Loop End Address Register (High and Low)                   |  |  |  |

| CORCON                            | Contains DSP Engine, DO Loop Control and Trap Status bits     |  |  |  |

**Note 1:** Memory-mapped W0 through W14 represent the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | 1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 2   | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                                                          |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                                                                         |

| Note 1: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                                                                           |

- Level. The value in parentheses indicates the IPL, if IPL< $3 \ge 1$ . User interrupts are disabled when IPL< $3 \ge 1$ .

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

#### 4.4.2 INSTRUCTION ADDRESSING MODES

The addressing modes shown in Table 4-18 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.4.2.1 File Register Instructions

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 4.4.2.2 MCU Instructions

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

## TABLE 4-18: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0          | U-0          | U-0                                                   | U-0              | U-0              | U-0             | R/W-0           | R/W-0 |  |  |

|--------------|--------------|-------------------------------------------------------|------------------|------------------|-----------------|-----------------|-------|--|--|

| _            | _            | —                                                     | —                | —                |                 | CAN             | NAE   |  |  |

| bit 15       |              |                                                       | ·                | -                |                 |                 | bit 8 |  |  |

|              |              |                                                       |                  |                  |                 |                 |       |  |  |

| U-0          | U-0          | U-0                                                   | R/W-0            | U-0              | U-0             | U-0             | R/W-0 |  |  |

|              | —            | —                                                     | DOOVR            | —                |                 | —               | APLL  |  |  |

| bit 7        |              |                                                       |                  |                  |                 |                 | bit 0 |  |  |

|              |              |                                                       |                  |                  |                 |                 |       |  |  |

| Legend:      |              |                                                       |                  |                  |                 |                 |       |  |  |

| R = Readab   | le bit       | W = Writable                                          | e bit            | U = Unimple      | mented bit, rea | d as '0'        |       |  |  |

| -n = Value a | t POR        | '1' = Bit is se                                       | et               | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |

|              |              |                                                       |                  |                  |                 |                 |       |  |  |

| bit 15-10    | Unimpleme    | Unimplemented: Read as '0'                            |                  |                  |                 |                 |       |  |  |

| bit 9        | CAN: CAN A   | CAN: CAN Address Error Soft Trap Status bit           |                  |                  |                 |                 |       |  |  |

|              |              | 1 = CAN address error soft trap has occurred          |                  |                  |                 |                 |       |  |  |

|              | 0 = CAN add  | 0 = CAN address error soft trap has not occurred      |                  |                  |                 |                 |       |  |  |

| bit 8        |              | NAE: NVM Address Error Soft Trap Status bit           |                  |                  |                 |                 |       |  |  |

|              |              |                                                       | t trap has occu  |                  |                 |                 |       |  |  |

|              |              |                                                       | t trap has not o | occurred         |                 |                 |       |  |  |

| bit 7-5      | -            | Unimplemented: Read as '0'                            |                  |                  |                 |                 |       |  |  |

| bit 4        |              | DOOVR: DO Stack Overflow Soft Trap Status bit         |                  |                  |                 |                 |       |  |  |

|              |              | 1 = DO stack overflow soft trap has occurred          |                  |                  |                 |                 |       |  |  |

|              |              | 0 = DO stack overflow soft trap has not occurred      |                  |                  |                 |                 |       |  |  |

| bit 3-1      | -            | Unimplemented: Read as '0'                            |                  |                  |                 |                 |       |  |  |

| bit 0        |              | APLL: Auxiliary PLL Loss of Lock Soft Trap Status bit |                  |                  |                 |                 |       |  |  |

|              |              | 1 = APLL lock soft trap has occurred                  |                  |                  |                 |                 |       |  |  |

|              | 0 = APLL loc | 0 = APLL lock soft trap has not occurred              |                  |                  |                 |                 |       |  |  |

# 8.4 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the dsPIC33CK256MP508 family devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State. Five control registers are associated with the Change Notification (CN) functionality of each I/O port. To enable the Change Notification feature for the port, the ON bit (CNCONx<15>) must be set.

The CNEN0x and CNEN1x registers contain the CN interrupt enable control bits for each of the input pins. The setting of these bits enables a CN interrupt for the corresponding pins. Also, these bits, in combination with the CNSTYLE bit (CNCONx<11>), define a type of transition when the interrupt is generated. Possible CN event options are listed in Table 8-3.

#### TABLE 8-3: CHANGE NOTIFICATION EVENT OPTIONS

| CNSTYLE Bit<br>(CNCONx<11>) | CNEN1x<br>Bit      | CNEN0x<br>Bit                                                                          | Change Notification Event<br>Description                |

|-----------------------------|--------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------|

| 0                           | Does not<br>matter | 0                                                                                      | Disabled                                                |

| 0                           | Does not<br>matter | 1 Detects a mismatch betwee<br>the last read state and the<br>current state of the pin |                                                         |

| 1                           | 0                  | 0                                                                                      | Disabled                                                |

| 1                           | 0                  | 1                                                                                      | Detects a positive transition<br>only (from '0' to '1') |

| 1                           | 1                  | 0                                                                                      | Detects a negative transition<br>only (from '1' to '0') |

| 1                           | 1                  | 1                                                                                      | Detects both positive and<br>negative transitions       |

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. In addition to the CNSTATx register, the CNFx register is implemented for each port. This register contains flags for Change Notification events. These flags are set if the valid transition edge, selected in the CNEN0x and CNEN1x registers, is detected. CNFx stores the occurrence of the event. CNFx bits must be cleared in software to get the next Change Notification interrupt. The CN interrupt is generated only for the I/Os configured as inputs (corresponding TRISx bits must be set).

| Note: | Pull-ups and pull-downs on Input Change  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | Notification pins should always be       |  |  |  |  |  |  |

|       | disabled when the port pin is configured |  |  |  |  |  |  |

|       | as a digital output.                     |  |  |  |  |  |  |

## 8.5 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 8.5.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions.

### 8.5.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. One example includes I<sup>2</sup>C modules. A similar requirement excludes all modules with analog inputs, such as the A/D Converter (ADC)

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _      | _   | RP177R5 <sup>(1)</sup> | RP177R4 <sup>(1)</sup> | RP177R3 <sup>(1)</sup> | RP177R2 <sup>(1)</sup> | RP177R1 <sup>(1)</sup> | RP177R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

|       | —   | RP176R5 <sup>(1)</sup> | RP176R4 <sup>(1)</sup> | RP176R3 <sup>(1)</sup> | RP176R2 <sup>(1)</sup> | RP176R1 <sup>(1)</sup> | RP176R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP177R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP177 Output Pin bits <sup>(1)</sup><br>(see Table 8-7 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 5-0   | <b>RP176R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP176 Output Pin bits <sup>(1)</sup> (see Table 8-7 for peripheral function numbers)    |

Note 1: These are virtual output ports.

| REGISTER 8-79: | <b>RPOR25: PERIPHERAL PIN SELECT OUTPUT REGISTER 25</b> |

|----------------|---------------------------------------------------------|

|----------------|---------------------------------------------------------|

| U-0    | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —      | —   | RP179R5 <sup>(1)</sup> | RP179R4 <sup>(1)</sup> | RP179R3 <sup>(1)</sup> | RP179R2 <sup>(1)</sup> | RP179R1 <sup>(1)</sup> | RP179R0 <sup>(1)</sup> |

| bit 15 |     |                        |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —     | —   | RP178R5 <sup>(1)</sup> | RP178R4 <sup>(1)</sup> | RP178R3 <sup>(1)</sup> | RP178R2 <sup>(1)</sup> | RP178R1 <sup>(1)</sup> | RP178R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP179R<5:0>:** Peripheral Output Function is Assigned to RP179 Output Pin bits<sup>(1)</sup> (see Table 8-7 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits<sup>(1)</sup> (see Table 8-7 for peripheral function numbers)

Note 1: These are virtual output ports.

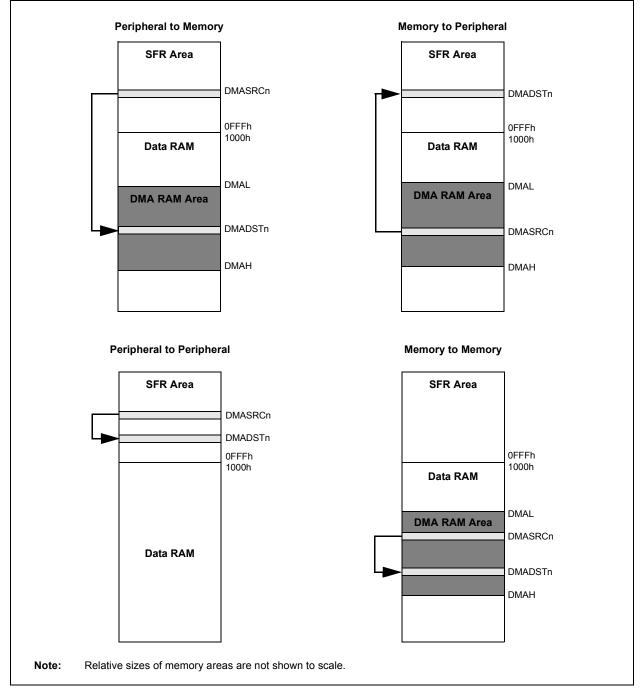

## FIGURE 10-2: TYPES OF DMA DATA TRANSFERS

| R-0                     | R/W-0                                                                                                                                                                          | R/W-0                              | R/W-0                 | R/W-0                  | R/W-0           | R/W-0            | R/W-0          |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|------------------------|-----------------|------------------|----------------|--|--|--|

| DBUFWF <sup>(1)</sup>   | CHSEL6                                                                                                                                                                         | CHSEL5                             | CHSEL4                | CHSEL3                 | CHSEL2          | CHSEL1           | CHSEL0         |  |  |  |

| bit 15                  |                                                                                                                                                                                |                                    |                       |                        |                 |                  | bit 8          |  |  |  |

|                         |                                                                                                                                                                                |                                    |                       |                        |                 |                  |                |  |  |  |

| R/W-0                   | R/W-0                                                                                                                                                                          | R/W-0                              | R/W-0                 | R/W-0                  | U-0             | U-0              | R/W-0          |  |  |  |

| HIGHIF <sup>(1,2)</sup> | LOWIF <sup>(1,2)</sup>                                                                                                                                                         | DONEIF <sup>(1)</sup>              | HALFIF <sup>(1)</sup> | OVRUNIF <sup>(1)</sup> |                 |                  | HALFEN         |  |  |  |

| bit 7                   |                                                                                                                                                                                |                                    |                       |                        |                 |                  | bit (          |  |  |  |

| Legend:                 |                                                                                                                                                                                |                                    |                       |                        |                 |                  |                |  |  |  |

|                         | , hit                                                                                                                                                                          | M - Mritabla                       | h:+                   |                        | contod bit roo  | d aa 'O'         |                |  |  |  |

| R = Readable            |                                                                                                                                                                                | W = Writable                       |                       | U = Unimplem           |                 |                  |                |  |  |  |

| -n = Value at           | POR                                                                                                                                                                            | '1' = Bit is set                   |                       | '0' = Bit is clea      | ared            | x = Bit is unkr  | iown           |  |  |  |

| bit 15                  | DBUFWF: DN                                                                                                                                                                     | MA Buffered Da                     | ata Write Flag I      | oit <sup>(1)</sup>     |                 |                  |                |  |  |  |

|                         |                                                                                                                                                                                |                                    | •                     | not been writter       | to the location | on specified in  | DMADSTn o      |  |  |  |

|                         |                                                                                                                                                                                | Cn in Null Write                   |                       |                        |                 |                  |                |  |  |  |

|                         |                                                                                                                                                                                | tent of the DN<br>Cn in Null Write |                       | been written           | to the locatio  | n specified in   | DMADSTn o      |  |  |  |

| bit 14-8                |                                                                                                                                                                                | : DMA Channe                       |                       | tion hits              |                 |                  |                |  |  |  |

|                         |                                                                                                                                                                                | -1 for a comple                    |                       |                        |                 |                  |                |  |  |  |

| bit 7                   |                                                                                                                                                                                |                                    |                       | Flag bit(1,2)          |                 |                  |                |  |  |  |

|                         | <b>HIGHIF:</b> DMA High Address Limit Interrupt Flag bit <sup>(1,2)</sup><br>1 = The DMA channel has attempted to access an address higher than DMAH or the upper limit of the |                                    |                       |                        |                 |                  |                |  |  |  |

|                         | data RAN                                                                                                                                                                       |                                    |                       |                        | g               |                  |                |  |  |  |

|                         |                                                                                                                                                                                |                                    |                       | high address li        | mit interrupt   |                  |                |  |  |  |

| bit 6                   |                                                                                                                                                                                | Low Address I                      |                       |                        |                 |                  |                |  |  |  |

|                         |                                                                                                                                                                                |                                    | attempted to a        | ccess the DMA          | SFR address     | lower than DM    | AL, but above  |  |  |  |

|                         |                                                                                                                                                                                | range (07FFh)                      | ot invokod the        | low address lin        | ait intorrunt   |                  |                |  |  |  |

| bit 5                   |                                                                                                                                                                                | A Complete Op                      |                       |                        | int interrupt   |                  |                |  |  |  |

| DIL D                   | If CHEN = 1:                                                                                                                                                                   | A Complete Op                      |                       | ipt Flag bit.          |                 |                  |                |  |  |  |

|                         |                                                                                                                                                                                | ous DMA sessi                      | on has ended          | with completion        | I               |                  |                |  |  |  |

|                         | •                                                                                                                                                                              | nt DMA sessio                      |                       | •                      |                 |                  |                |  |  |  |

|                         | If CHEN = 0:                                                                                                                                                                   |                                    |                       |                        |                 |                  |                |  |  |  |

|                         | •                                                                                                                                                                              |                                    |                       | with completion        |                 |                  |                |  |  |  |

|                         | •                                                                                                                                                                              |                                    |                       | without complet        | lion            |                  |                |  |  |  |

| bit 4                   | HALFIF: DMA 50% Watermark Level Interrupt Flag bit <sup>(1)</sup>                                                                                                              |                                    |                       |                        |                 |                  |                |  |  |  |

|                         |                                                                                                                                                                                | n has reached<br>n has not reach   |                       |                        |                 |                  |                |  |  |  |

| bit 3                   |                                                                                                                                                                                | MA Channel Ov                      |                       | • •                    |                 |                  |                |  |  |  |

|                         |                                                                                                                                                                                |                                    | -                     | still completing       | the operation   | based on the n   | revious triage |  |  |  |

|                         |                                                                                                                                                                                | un condition ha                    |                       |                        |                 | 20000 011 010 p  |                |  |  |  |

| bit 2-1                 | Unimplemen                                                                                                                                                                     | ted: Read as '                     | כי                    |                        |                 |                  |                |  |  |  |

| bit 0                   | -                                                                                                                                                                              | Ifway Completi                     |                       | bit                    |                 |                  |                |  |  |  |

|                         |                                                                                                                                                                                |                                    |                       | n has reached it       | s halfway poir  | nt and at comple | etion          |  |  |  |

|                         |                                                                                                                                                                                |                                    |                       | pletion of the tra     |                 |                  |                |  |  |  |

| Note 1: Se              | tting these flag                                                                                                                                                               | s in software de                   | oes not genera        | ate an interrupt.      |                 |                  |                |  |  |  |

|                         |                                                                                                                                                                                |                                    | -                     | or DMADSTn is          | s either greate | r than DMAH o    | r less than    |  |  |  |

# REGISTER 10-3: DMAINTn: DMA CHANNEL n INTERRUPT REGISTER

2: Testing for address limit violations (DMASRCn or DMADSTn is either greater than DMAH or less than DMAL) is NOT done before the actual access.

| R/W-0        | R/W-0                    | R/W-0                          | R/W-0         | R/W-0            | R/W-0                                     | R/W-0                    | R/W-0                    |

|--------------|--------------------------|--------------------------------|---------------|------------------|-------------------------------------------|--------------------------|--------------------------|

| ADTR1PS4     | ADTR1PS3                 | ADTR1PS2                       | ADTR1PS1      | ADTR1PS0         | ADTR1EN3                                  | ADTR1EN2                 | ADTR1EN1                 |

| bit 15       |                          |                                |               |                  |                                           |                          | bit 8                    |

|              |                          |                                |               |                  |                                           |                          |                          |

| U-0          | U-0                      | U-0                            | R/W-0         | R/W-0            | R/W-0                                     | R/W-0                    | R/W-0                    |

|              | —                        |                                | UPDTRG1       | UPDTRG0          | PGTRGSEL2 <sup>(1)</sup>                  | PGTRGSEL1 <sup>(1)</sup> | PGTRGSEL0 <sup>(1)</sup> |

| bit 7        |                          |                                |               |                  |                                           |                          | bit 0                    |

| r            |                          |                                |               |                  |                                           |                          |                          |

| Legend:      |                          |                                |               |                  |                                           |                          |                          |

| R = Readab   | ole bit                  | W = Writable                   | bit           | U = Unimple      | mented bit, read                          | as '0'                   |                          |

| -n = Value a | at POR                   | '1' = Bit is se                | t             | '0' = Bit is cle | eared                                     | x = Bit is unknow        | n                        |

|              |                          |                                |               |                  |                                           |                          |                          |

| bit 15-11    | ADTR1PS<                 | 4:0>: ADC Tri                  | gger 1 Posts  | caler Selection  | n bits                                    |                          |                          |

|              | 11111 = 1:3              | 2                              |               |                  |                                           |                          |                          |

|              | <br>00010 = 1:3          | 1                              |               |                  |                                           |                          |                          |

|              | 00001 = 1:2              |                                |               |                  |                                           |                          |                          |

|              | 00000 = 1:1              |                                |               |                  |                                           |                          |                          |

| bit 10       | ADTR1EN3                 | ADC Trigger                    | 1 Source is I | PGxTRIGC Co      | ompare Event En                           | able bit                 |                          |

|              |                          | •                              | •             |                  | s trigger source f                        |                          |                          |

|              |                          | -                              | -             |                  |                                           | or ADC Trigger 1         |                          |

| bit 9        |                          |                                |               |                  | ompare Event En                           |                          |                          |

|              |                          |                                |               |                  | s trigger source fo<br>s trigger source f |                          |                          |

| bit 8        | ADTR1EN1:                | : ADC Trigger                  | 1 Source is I | PGxTRIGA Co      | ompare Event En                           | able bit                 |                          |

|              |                          |                                |               |                  | s trigger source fo                       |                          |                          |

|              |                          | -                              | -             | t is disabled a  | s trigger source f                        | or ADC Trigger 1         |                          |

| bit 7-5      | -                        | nted: Read a                   |               |                  |                                           |                          |                          |

| bit 4-3      |                          | :0>: Update T                  |               |                  |                                           |                          |                          |

|              |                          |                                |               |                  | sets the UPDATI                           |                          |                          |

|              |                          |                                |               |                  | s the UPDATE bi                           |                          |                          |

|              |                          |                                |               | GxSTAT<4>)       |                                           |                          |                          |

| bit 2-0      | PGTRGSEL                 | <2:0>: PWM                     | Generator Tr  | igger Output S   | Selection bits <sup>(1)</sup>             |                          |                          |

|              | 111 = Rese               |                                |               |                  |                                           |                          |                          |

|              | 110 = Rese               |                                |               |                  |                                           |                          |                          |

|              | 101 - Rese<br>100 = Rese |                                |               |                  |                                           |                          |                          |

|              | 011 = PGxT               | RIGC compa                     |               | e PWM Gene       |                                           |                          |                          |

|              |                          |                                |               | e PWM Gener      |                                           |                          |                          |

|              |                          | RIGA compare<br>event is the P |               | e PWM Gener      | ator trigger                              |                          |                          |

|              | 000 - EOC                | Eveni is the F                 | www.General   |                  |                                           |                          |                          |

#### REGISTER 12-17: PGxEVTL: PWM GENERATOR x EVENT REGISTER LOW

Note 1: These events are derived from the internal PWM Generator time base comparison events.

# REGISTER 12-19: PGxyPCIL: PWM GENERATOR xy PCI REGISTER LOW (x = PWM GENERATOR #; y = F, CL, FF OR S)

|              | •                            |                  |                                 | -1, 02, 11         | ,                                       |                   |                    |

|--------------|------------------------------|------------------|---------------------------------|--------------------|-----------------------------------------|-------------------|--------------------|

| R/W-0        | R/W-0                        | R/W-0            | R/W-0                           | R/W-0              | R/W-0                                   | R/W-0             | R/W-0              |

| TSYNCDIS     | TERM2                        | TERM1            | TERM0                           | AQPS               | AQSS2                                   | AQSS1             | AQSS0              |

| bit 15       |                              |                  |                                 |                    |                                         |                   | bit 8              |

|              |                              |                  |                                 |                    |                                         |                   |                    |

| R/W-0        | R/W-0                        | R/W-0            | R/W-0                           | R/W-0              | R/W-0                                   | R/W-0             | R/W-0              |

| SWTERM       | PSYNC                        | PPS              | PSS4                            | PSS3               | PSS2                                    | PSS1              | PSS0               |

| bit 7        |                              |                  |                                 |                    |                                         |                   | bit (              |

|              |                              |                  |                                 |                    |                                         |                   |                    |

| Legend:      |                              |                  |                                 |                    |                                         |                   |                    |

| R = Readat   | ole bit                      | W = Writable     | bit                             | U = Unimpler       | mented bit, read a                      | as '0'            |                    |

| -n = Value a | at POR                       | '1' = Bit is se  | t                               | '0' = Bit is cle   | ared                                    | x = Bit is unkn   | iown               |

| bit 15       |                              |                  | ynchronization                  |                    |                                         |                   |                    |

|              | 0 = Termina                  | tion of latched  | PCI occurs at                   | PWM EOC            |                                         |                   |                    |

| bit 14-12    | TERM<2:0>                    | : Termination I  | Event Selection                 | bits               |                                         |                   |                    |

|              | 00000                        | ts PCI Source    |                                 |                    |                                         |                   |                    |

|              |                              | ts PCI Source    |                                 | orator output s    | elected by the PV                       |                   | -)                 |

|              |                              | RIGC trigger e   |                                 |                    |                                         | VIVIF CI~2.02 Dia | <b>&gt;</b> )      |

|              |                              | RIGB trigger e   |                                 |                    |                                         |                   |                    |

|              |                              | RIGA trigger e   |                                 |                    |                                         |                   |                    |

|              |                              |                  |                                 |                    | sitions from active<br>the SWTERM bit I |                   |                    |

| bit 11       |                              |                  | er Polarity Sele                |                    |                                         | ocation           |                    |

| Dit 11       | 1 = Inverted<br>0 = Not inve |                  | er i olanty Sele                |                    |                                         |                   |                    |

| bit 10-8     | AQSS<2:0>                    | : Acceptance     | Qualifier Source                | e Selection bits   |                                         |                   |                    |

|              |                              | -                | nly (qualifier fo               |                    |                                         |                   |                    |

|              |                              | ts PCI Source    |                                 |                    |                                         |                   |                    |

|              |                              | ts PCI Source    |                                 | orator output of   | plaated by the DV                       | WMDCL-2.05 hite   |                    |

|              |                              | Generator is f   |                                 |                    | elected by the PV                       |                   | <b>&gt;</b> )      |

|              | 010 = LEB is                 |                  | inggoroa                        |                    |                                         |                   |                    |

|              |                              |                  |                                 | enerator signal)   |                                         |                   |                    |

|              |                              |                  |                                 | ualifier forced to | oʻ1')                                   |                   |                    |

| bit 7        |                              | CI Software T    |                                 |                    |                                         |                   |                    |

|              |                              |                  | •                               | a termination ev   | ent. This bit loca                      | tion always read  | <b>Is as '</b> 0'. |

| bit 6        |                              | -                | ion Control bit                 |                    |                                         |                   |                    |

|              |                              |                  | nized to PWM<br>chronized to PV |                    |                                         |                   |                    |

| bit 5        | PPS: PCI Pc                  | plarity Select b | it                              |                    |                                         |                   |                    |

|              | 1 = Inverted                 |                  |                                 |                    |                                         |                   |                    |

|              | 0 = Not inve                 |                  |                                 |                    |                                         |                   |                    |

| R/W-0         | U-0                              | R/W-0                    | U-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|---------------|----------------------------------|--------------------------|-----------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| DACON         | —                                | DACSIDL                  | _                           | _                       | _                       |                         | —                      |

| bit 15        |                                  | •                        |                             |                         |                         |                         | bit                    |

|               |                                  |                          |                             |                         |                         |                         |                        |

| R/W-0         | R/W-0                            | R/W-0                    | R/W-0                       | U-0                     | R/W-0                   | R/W-0                   | R/W-0                  |

| CLKSEL1(1,3)  | CLKSEL0 <sup>(1,3)</sup>         | CLKDIV1 <sup>(1,3)</sup> | CLKDIV0 <sup>(1,3)</sup>    | —                       | FCLKDIV2 <sup>(2)</sup> | FCLKDIV1 <sup>(2)</sup> | FCLKDIV0 <sup>(2</sup> |

| bit 7         |                                  |                          |                             |                         |                         |                         | bit                    |

| <u> </u>      |                                  |                          |                             |                         |                         |                         |                        |

| Legend:       | - <b>L</b> :4                    |                          | :.                          | 11 11                   |                         | -l (O)                  |                        |

| R = Readable  |                                  | W = Writable b           | it                          | •                       | emented bit, rea        | d as '0                 |                        |

| -n = Value at | PUR                              | '1' = Bit is set         |                             | '0' = Bit is c          | leared                  |                         |                        |

| bit 15        | DACON: Com                       | nmon DAC Mod             | ule Enable hit              |                         |                         |                         |                        |

| bit 15        | 1 = Enables [                    |                          |                             |                         |                         |                         |                        |

|               |                                  |                          | and disables F              | SCM clocks              | to reduce powe          | r consumption           | ; any pendin           |

|               | Slope mo                         | de and/or unde           | rflow conditions            | are cleared             |                         |                         |                        |

| bit 14        | •                                | ted: Read as '0'         |                             |                         |                         |                         |                        |

| bit 13        |                                  | AC Stop in Idle N        |                             |                         |                         |                         |                        |

|               |                                  | les module oper          |                             |                         | le mode                 |                         |                        |

| h:+ 40.0      |                                  | module operati           |                             |                         |                         |                         |                        |

| bit 12-8      | •                                | ted: Read as '0'         |                             | - (1.3)                 |                         |                         |                        |

| bit 7-6       | 11 = FPLLO                       | >: DAC Clock S           | ource Select bit            | S( ,,,,,                |                         |                         |                        |

|               | 11 = PPLLO<br>10 = AFPLLO        |                          |                             |                         |                         |                         |                        |

|               | 01 = Fvco/2                      |                          |                             |                         |                         |                         |                        |

|               | 00 = AFvco/2                     |                          |                             |                         |                         |                         |                        |

| bit 5-4       |                                  | : DAC Clock Di           | vider bits <sup>(1,3)</sup> |                         |                         |                         |                        |

|               | 11 = Divide-by                   | •                        |                             |                         |                         |                         |                        |

|               | 10 = Divide-by<br>01 = Divide-by | y-3 (non-uniform         | n duty cycle)               |                         |                         |                         |                        |

|               | 01 = Divide-by = 00 = 1x         | y-2                      |                             |                         |                         |                         |                        |

| bit 3         | Unimplement                      | ted: Read as '0'         | ,                           |                         |                         |                         |                        |

| bit 2-0       | •                                | >: Comparator            |                             | der bits <sup>(2)</sup> |                         |                         |                        |

|               | 111 = Divide-l                   | •                        |                             |                         |                         |                         |                        |

|               | 110 = Divide-l                   | by-7                     |                             |                         |                         |                         |                        |

|               | 101 = Divide-l                   |                          |                             |                         |                         |                         |                        |

|               | 100 = Divide-l<br>011 = Divide-l |                          |                             |                         |                         |                         |                        |

|               | 010 = Divide-l                   |                          |                             |                         |                         |                         |                        |

|               | 001 = Divide-l                   | by-2                     |                             |                         |                         |                         |                        |

|               | 000 = 1x                         |                          |                             |                         |                         |                         |                        |

| Note 1: Th    | ese bits should                  | only be change           | d when DACON                | l = 0 to avoid          | d unpredictable l       | behavior.               |                        |

|               |                                  | • •                      |                             |                         | SEL<1:0>, and t         |                         | 2.                     |

|               |                                  |                          |                             |                         |                         |                         |                        |

### REGISTER 14-1: DACCTRL1L: DAC CONTROL 1 LOW REGISTER

- 3: Clock source and dividers should yield an effective DAC clock input of 500 MHz.

## 20.2 Receive Mode

The module can be configured for receive operation by setting the RCVEN (SENTxCON1<11>) bit. The time between each falling edge is compared to SYNCMIN<15:0> (SENTxCON3<15:0>) and SYNCMAX<15:0> (SENTxCON2<15:0>), and if the measured time lies between the minimum and maximum limits, the module begins to receive data. The validated Sync time is captured in the SENTxSYNC register and the tick time is calculated. Subsequent falling edges are verified to be within the valid data width and the data is stored in the SENTxDATL/H registers. An interrupt event is generated at the completion of the message and the user software should read the SENTx Data registers before the reception of the next nibble. The equation for SYNCMIN<15:0> and SYNCMAX<15:0> is shown in Equation 20-3.

#### EQUATION 20-3: SYNCMIN<15:0> AND SYNCMAX<15:0> CALCULATIONS

$TTICK = TCLK \bullet (TICKTIME < 15:0 > + 1)$

FRAMETIME < 15:0 > = TTICK/TFRAME

SyncCount = 8 x FRCV x TTICK

SYNCMIN<15:0> = 0.8 x SyncCount

SYNCMAX<15:0> = 1.2 x SyncCount

$FRAMETIME < 15:0 \ge 122 + 27N$

$FRAMETIME < 15:0 > \ge 848 + 12N$

#### Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6  $F_{RCV}$  = FCY x Prescaler  $T_{CLK}$  = FCY/Prescaler

For TTICK = 3.0  $\mu$ s and FCLK = 4 MHz, SYNCMIN<15:0> = 76.

| Note: | To ensure a Sync period can be identified, |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | the value written to SYNCMIN<15:0>         |  |  |  |  |  |  |  |  |  |

|       | must be less than the value written to     |  |  |  |  |  |  |  |  |  |

|       | SYNCMAX<15:0>.                             |  |  |  |  |  |  |  |  |  |

#### 20.2.1 RECEIVE MODE CONFIGURATION

#### 20.2.1.1 Initializing the SENTx Module

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 1 for Receive mode.

- 2. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 3. Write CRCEN (SENTxCON1<8>) for hardware or software CRC validation.

- 4. Write PPP (SENTxCON1<7>) = 1 if pause pulse is present.

- 5. Write SENTxCON2 with the value of SYNCMAXx (Nominal Sync Period + 20%).

- Write SENTxCON3 with the value of SYNCMINx (Nominal Sync Period – 20%).

- 7. Enable interrupts and set interrupt priority.

- 8. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

The data should be read from the SENTxDATL/H registers after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt trigger.

| R/W-0                 | R/W-0                                              | U-0                                    | U-0            | R/W-0                               | R/W-0               | R/W-0               | R/W-0               |  |  |  |

|-----------------------|----------------------------------------------------|----------------------------------------|----------------|-------------------------------------|---------------------|---------------------|---------------------|--|--|--|

| OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup>                              |                                        | _              | OPS3 <sup>(3)</sup>                 | OPS2 <sup>(3)</sup> | OPS1 <sup>(3)</sup> | OPS0 <sup>(3)</sup> |  |  |  |

| bit 15                |                                                    |                                        |                |                                     |                     |                     | bit 8               |  |  |  |

|                       |                                                    |                                        |                |                                     |                     |                     |                     |  |  |  |

| R/W-0                 | R/W-0                                              | R/W-0                                  | R/W-0          | R/W-0                               | R/W-0               | R/W-0               | R/W-0               |  |  |  |

| TRIGEN                | ONESHOT                                            | ALTSYNC                                | SYNC4          | SYNC3                               | SYNC2               | SYNC1               | SYNC0               |  |  |  |

| bit 7                 |                                                    |                                        |                |                                     |                     |                     | bit (               |  |  |  |

| Legend:               |                                                    |                                        |                |                                     |                     |                     |                     |  |  |  |