Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 69                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck256mp208t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the family devices of the dsPIC33CK256MP508 requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins regardless if ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- PGCx/PGDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.4 "ICSP Pins")

- OSCI and OSCO pins when an external oscillator source is used (see Section 2.5 "External Oscillator Pins")

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSs is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| Register      | Address | All Resets                              | Register  | Address | All Resets                              | Register  | Address | All Resets                              |

|---------------|---------|-----------------------------------------|-----------|---------|-----------------------------------------|-----------|---------|-----------------------------------------|

| I2C1 and I2C2 | 2       |                                         | U1SCCON   | 258     | 00000-                                  | SPI1IMSKH | 2C2     | 0000000-000000                          |

| I2C1CONL      | 200     | 01000000000000                          | U1SCINT   | 25A     | 00-00000-000                            | SPI1URDTL | 2C4     | 000000000000000000000000000000000000000 |

| I2C1CONH      | 202     | 0000000                                 | U1INT     | 25C     | 0                                       | SPI1URDTH | 2C6     | 000000000000000000000000000000000000000 |

| I2C1STAT      | 204     | 00000000000000                          | U2MODE    | 260     | 000-0000000000                          | SPI2CON1L | 2C8     | 00000000000000000                       |

| I2C1ADD       | 208     | 0000000000                              | U2MODEH   | 262     | 0000000000000                           | SPI2CON1H | 2CA     | 000000000000000000000000000000000000000 |

| I2C1MSK       | 20C     | 0000000000                              | U2STA     | 264     | 00000001000000                          | SPI2CON2L | 2CC     | 00000                                   |

| I2C1BRG       | 210     | 000000000000000000000000000000000000000 | U2STAH    | 266     | 0000-00000101110                        | SPI2CON2H | 2CE     |                                         |

| I2C1TRN       | 214     | 111111111                               | U2BRG     | 268     | 000000000000000000000000000000000000000 | SPI2STATL | 2D0     | 000001-1-00                             |

| I2C1RCV       | 218     | 00000000                                | U2BRGH    | 26A     | 0000                                    | SPI2STATH | 2D2     | 000000000000                            |

| I2C2CONL      | 21C     | 01000000000000                          | U2RXREG   | 26C     | xxxxxxxx                                | SPI2BUFL  | 2D4     | 000000000000000000000000000000000000000 |

| I2C2CONH      | 21E     | 0000000                                 | U2TXREG   | 270     | xxxxxxxx                                | SPI2BUFH  | 2D6     | 000000000000000000000000000000000000000 |

| I2C2STAT      | 220     | 00000000000000                          | U2P1      | 274     | 000000000                               | SPI2BRGL  | 2D8     | xxxxxxxxxxxxxx                          |

| I2C2ADD       | 224     | 0000000000                              | U2P2      | 276     | 000000000                               | SPI2BRGH  | 2DA     |                                         |

| I2C2MSK       | 228     | 0000000000                              | U2P3      | 278     | 000000000000000000000000000000000000000 | SPI2IMSKL | 2DC     | 000000-0-00                             |

| I2C2BRG       | 22C     | 000000000000000000000000000000000000000 | U2P3H     | 27A     | 00000000                                | SPI2IMSKH | 2DE     | 0000000-000000                          |

| I2C2TRN       | 230     | 111111111                               | U2TXCHK   | 27C     | 00000000                                | SPI2URDTL | 2E0     | 000000000000000000000000000000000000000 |

| I2C2RCV       | 234     | 00000000                                | U2RXCHK   | 27E     | 00000000                                | SPI2URDTH | 2E2     | 000000000000000000000000000000000000000 |

| UART1 and U   | IART2   |                                         | U2SCCON   | 280     | 00000-                                  | SPI3CON1L | 2E4     | 0000000000000000000000000000000000000   |

| U1MODE        | 238     | 000-0000000000                          | U2SCINT   | 282     | 00-00000-000                            | SPI3CON1H | 2E6     | 000000000000000000000000000000000000000 |

| U1MODEH       | 23A     | 0000000000000                           | U2INT     | 284     | 0                                       | SPI3CON2L | 2E8     | 00000                                   |

| U1STA         | 23C     | 00000001000000                          | SPI       |         |                                         | SPI3CON2H | 2EA     |                                         |

| U1STAH        | 23E     | 0000-00000101110                        | SPI1CON1L | 2AC     | 000000000000000                         | SPI3STATL | 2EC     | 000001-1-00                             |

| U1BRG         | 240     | 000000000000000000                      | SPI1CON1H | 2AE     | 000000000000000000000000000000000000000 | SPI3STATH | 2EE     | 000000000000                            |

| U1BRGH        | 242     | 0000                                    | SPI1CON2L | 2B0     | 00000                                   | SPI3BUFL  | 2F0     | 000000000000000000000000000000000000000 |

| U1RXREG       | 244     | xxxxxxxx                                | SPI1CON2H | 2B2     |                                         | SPI3BUFH  | 2F2     | 000000000000000000000000000000000000000 |

| U1TXREG       | 248     | xxxxxxxx                                | SPI1STATL | 2B4     | 000001-1-00                             | SPI3BRGL  | 2F4     | xxxxxxxxxxxxxx                          |

| U1P1          | 24C     | 000000000                               | SPI1STATH | 2B6     | 000000000000                            | SPI3BRGH  | 2F6     |                                         |

| U1P2          | 24E     | 000000000                               | SPI1BUFL  | 2B8     | 000000000000000000000000000000000000000 | SPI3IMSKL | 2F8     | 000000-0-00                             |

| U1P3          | 250     | 000000000000000000000000000000000000000 | SPI1BUFH  | 2BA     | 000000000000000000000000000000000000000 | SPI3IMSKH | 2FA     | 000000-000000                           |

| U1P3H         | 252     | 00000000                                | SPI1BRGL  | 2BC     | xxxxxxxxxxxxxxx                         | SPI3URDTL | 2FC     | 000000000000000000000000000000000000000 |

| U1TXCHK       | 254     | 00000000                                | SPI1BRGH  | 2BE     |                                         | SPI3URDTH | 2F3     | 000000000000000000000000000000000000000 |

| U1RXCHK       | 256     | 00000000                                | SPI1IMSKL | 2C0     | 000000-0-00                             |           |         |                                         |

## TABLE 4-4: SFR BLOCK 200h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address values are in hexadecimal. Reset values are in binary.

# TABLE 7-1: INTERRUPT VECTOR DETAILS

|                                       | Vector | IRQ   |                   | In       | Interrupt Bit Location |              |  |

|---------------------------------------|--------|-------|-------------------|----------|------------------------|--------------|--|

| Interrupt Source                      | #      | #     | IVT Address       | Flag     | Enable                 | Priority     |  |

| INT0 – External Interrupt 0           | 8      | 0     | 0x000014          | IFS0<0>  | IEC0<0>                | IPC0<2:0>    |  |

| T1 – Timer1                           | 9      | 1     | 0x000016          | IFS0<1>  | IEC0<1>                | IPC0<6:4>    |  |

| CNA – Change Notice Interrupt A       | 10     | 2     | 0x000018          | IFS0<2>  | IEC0<2>                | IPC0<10:8>   |  |

| CNB – Change Notice Interrupt B       | 11     | 3     | 0x00001A          | IFS0<3>  | IEC0<3>                | IPC0<14:12>  |  |

| DMA0 – DMA Channel 0                  | 12     | 4     | 0x00001C          | IFS0<4>  | IEC0<4>                | IPC1<2:0>    |  |

| Reserved                              | 13     | 5     | 0x00001E          | —        |                        |              |  |

| CCP1 – Input Capture/Output Compare 1 | 14     | 6     | 0x000020          | IFS0<6>  | IEC0<6>                | IPC1<10:8>   |  |

| CCT1 – CCP1 Timer                     | 15     | 7     | 0x000022          | IFS0<7>  | IEC0<7>                | IPC1<14:12>  |  |

| DMA1 – DMA Channel 1                  | 16     | 8     | 0x000024          | IFS0<8>  | IEC0<8>                | IPC2<2:0>    |  |

| SPI1RX – SPI1 Receiver                | 17     | 9     | 0x000026          | IFS0<9>  | IEC0<9>                | IPC2<6:4>    |  |

| SPI1TX – SPI1 Transmitter             | 18     | 10    | 0x000028          | IFS0<10> | IEC0<10>               | IPC2<10:8>   |  |

| U1RX – UART1 Receiver                 | 19     | 11    | 0x00002A          | IFS0<11> | IEC0<11>               | IPC2<14:12>  |  |

| U1TX – UART1 Transmitter              | 20     | 12    | 0x00002C          | IFS0<12> | IEC0<12>               | IPC3<2:0>    |  |

| ECCSBE – ECC Single Bit Error         | 21     | 13    | 0x00002E          | IFS0<13> | IEC0<13>               | IPC3<6:4>    |  |

| NVM – NVM Write Complete              | 22     | 14    | 0x000030          | IFS0<14> | IEC0<14>               | IPC3<10:8>   |  |

| INT1 – External Interrupt 1           | 23     | 15    | 0x000032          | IFS0<15> | IEC0<15>               | IPC3<14:12>  |  |

| SI2C1 – I2C1 Slave Event              | 24     | 16    | 0x000034          | IFS1<0>  | IEC1<0>                | IPC4<2:0>    |  |

| MI2C1 – I2C1 Master Event             | 25     | 17    | 0x000036          | IFS1<1>  | IEC1<1>                | IPC4<6:4>    |  |

| DMA2 – DMA Channel 2                  | 26     | 18    | 0x000038          | IFS1<2>  | IEC1<2>                | IPC4<10:8>   |  |

| CNC – Change Notice Interrupt C       | 27     | 19    | 0x00003A          | IFS1<3>  | IEC1<3>                | IPC4<14:12>  |  |

| INT2 – External Interrupt 2           | 28     | 20    | 0x00003C          | IFS1<4>  | IEC1<4>                | IPC5<2:0>    |  |

| DMA3 – DMA Channel 3                  | 29     | 21    | 0x00003E          | IFS1<5>  | IEC1<5>                | IPC5<6:4>    |  |

| Reserved                              | 30     | 22    | 0x000040          | —        | _                      | _            |  |

| CCP2 – Input Capture/Output Compare 2 | 31     | 23    | 0x000042          | IFS1<7>  | IEC1<7>                | IPC5<14:12>  |  |

| CCT2 – CCP2 Timer                     | 32     | 24    | 0x000044          | IFS1<8>  | IEC1<8>                | IPC6<2:0>    |  |

| CAN1 – CAN1 Combined Error            | 33     | 25    | 0x000046          | IFS1<9>  | IEC1<9>                | IPC6<6:4>    |  |

| INT3 – External Interrupt 3           | 34     | 26    | 0x000048          | IFS1<10> | IEC1<10>               | IPC6<10:8>   |  |

| U2RX – UART2 Receiver                 | 35     | 27    | 0x00004A          | IFS1<11> | IEC1<11>               | IPC6<14:12>  |  |

| U2TX – UART2 Transmitter              | 36     | 28    | 0x00004C          | IFS1<12> | IEC1<12>               | IPC7<2:0>    |  |

| SPI2RX – SPI2 Receiver                | 37     | 29    | 0x00004E          | IFS1<13> | IEC1<13>               | IPC7<6:4>    |  |

| SPI2TX – SPI2 Transmitter             | 38     | 30    | 0x000050          | IFS1<14> | IEC1<14>               | IPC7<10:8>   |  |

| C1RX – CAN1 RX Data Ready             | 39     | 31    | 0x000052          | IFS1<15> | IEC1<15>               | IPC7<14:12>  |  |

| Reserved                              | 40-42  | 32-34 | 0x000054-0x000058 | —        |                        | _            |  |

| CCP3 – Input Capture/Output Compare 3 | 43     | 35    | 0x00005A          | IFS2<3>  | IEC2<3>                | IPC8<14:12>  |  |

| CCT3 – CCP3 Timer                     | 44     | 36    | 0x00005C          | IFS2<4>  | IEC2<4>                | IPC9<2:0>    |  |

| SI2C2 – I2C2 Slave Event              | 45     | 37    | 0x00005E          | IFS2<5>  | IEC2<5>                | IPC9<6:4>    |  |

| MI2C2 – I2C2 Master Event             | 46     | 38    | 0x000060          | IFS2<6>  | IEC2<6>                | IPC9<10:8>   |  |

| Reserved                              | 47     | 39    | 0x000062          | —        | —                      | _            |  |

| CCP4 – Input Capture/Output Compare 4 | 48     | 40    | 0x000064          | IFS2<8>  | IEC2<8>                | IPC10<2:0>   |  |

| CCT4 – CCP4 Timer                     | 49     | 41    | 0x000066          | IFS2<9>  | IEC2<9>                | IPC10<6:4>   |  |

| Reserved                              | 50     | 42    | 0x000068          | —        | —                      | _            |  |

| CCP5 – Input Capture/Output Compare 5 | 51     | 43    | 0x00006A          | IFS2<11> | IEC2<11>               | IPC10<14:12> |  |

| CCT5 – CCP5 Timer                     | 52     | 44    | 0x00006C          | IFS2<12> | IEC2<12>               | IPC11<2:0>   |  |

| DMT – Deadman Timer                   | 53     | 45    | 0x00006E          | IFS2<13> | IEC2<13>               | IPC11<6:4>   |  |

| CCP6 – Input Capture/Output Compare 6 | 54     | 46    | 0x000070          | IFS2<14> | IEC2<14>               | IPC11<10:8>  |  |

| CCT6 – CCP6 Timer                     | 55     | 47    | 0x000072          | IFS2<15> | IEC2<15>               | IPC11<14:12> |  |

# 8.5.6 OUTPUT MAPPING

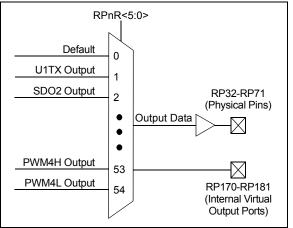

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 8-54 through Register 8-80). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 8-7 and Figure 8-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 8-3: MULTIPLEXING REMAPPABLE OUTPUTS FOR RPn

| Note 1: | There are 6 virtual output ports which are not connected to any I/O ports (RP176- |  |  |  |  |

|---------|-----------------------------------------------------------------------------------|--|--|--|--|

|         | RP181). These virtual ports can be                                                |  |  |  |  |

|         | accessed by RPOR20, RPOR21 and                                                    |  |  |  |  |

|         | RPOR22.                                                                           |  |  |  |  |

# 8.5.7 MAPPING LIMITATIONS

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally, any combination of peripheral mappings, across any or all of the RPn pins, is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs, and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view (see Table 8-6).

| RP Pin     | I/O Port                                                                         |  |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------|--|--|--|--|--|--|

| RP78       | Port Pin RD14                                                                    |  |  |  |  |  |  |

| RP79       | Port Pin RD15                                                                    |  |  |  |  |  |  |

| RP80-RP175 | Reserved                                                                         |  |  |  |  |  |  |

| RP176      | Virtual Pin RPV0                                                                 |  |  |  |  |  |  |

| RP177      | Virtual Pin RPV1                                                                 |  |  |  |  |  |  |

| RP178      | Virtual Pin RPV2                                                                 |  |  |  |  |  |  |

| RP179      | Virtual Pin RPV3                                                                 |  |  |  |  |  |  |

| RP180      | Virtual Pin RPV4                                                                 |  |  |  |  |  |  |

| RP181      | Virtual Pin RPV5                                                                 |  |  |  |  |  |  |

|            | RP78<br>RP79<br>RP80-RP175<br>RP176<br>RP177<br>RP177<br>RP178<br>RP179<br>RP180 |  |  |  |  |  |  |

#### TABLE 8-6: REMAPPABLE OUTPUT PIN REGISTERS (CONTINUED)

# 11.2 Can Control Registers

### REGISTER 11-1: C1CONH: CAN CONTROL REGISTER HIGH

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | S/HC-0 | R/W-1  | R/W-0  | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TXBWS3 | TXBWS2 | TXBWS1 | TXBWS0 | ABAT   | REQOP2 | REQOP1 | REQOP0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R-1    | R-0    | R-0    | R/W-1                | R/W-1               | R/W-0                  | R/W-0                | R/W-0                |

|--------|--------|--------|----------------------|---------------------|------------------------|----------------------|----------------------|

| OPMOD2 | OPMOD1 | OPMOD0 | TXQEN <sup>(1)</sup> | STEF <sup>(1)</sup> | SERRLOM <sup>(1)</sup> | ESIGM <sup>(1)</sup> | RTXAT <sup>(1)</sup> |

| bit 7  |        |        |                      |                     |                        |                      | bit 0                |

| Legend:           | S = Settable bit | HC = Hardware Clearat  | HC = Hardware Clearable bit        |  |

|-------------------|------------------|------------------------|------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |

bit 15-12 **TXBWS<3:0>:** Transmit Bandwidth Sharing bits

|          | 1111-1100 = 4096<br>1011 = 2048<br>1010 = 1024<br>1001 = 512<br>1000 = 256<br>0111 = 128<br>0110 = 64<br>0101 = 32<br>0100 = 16<br>0011 = 8<br>0010 = 4<br>0001 = 2<br>0000 = No delay                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11   | ABAT: Abort All Pending Transmissions bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          | <ul> <li>1 = Signals all transmit buffers to abort transmission</li> <li>0 = Module will clear this bit when all transmissions are aborted</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 10-8 | <b>REQOP&lt;2:0&gt;:</b> Request Operation Mode bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | <ul> <li>111 = Sets Restricted Operation mode</li> <li>110 = Sets Normal CAN 2.0 mode; error frames on CAN FD frames</li> <li>101 = Sets External Loopback mode</li> <li>100 = Sets Configuration mode</li> <li>011 = Sets Listen Only mode</li> <li>010 = Sets Internal Loopback mode</li> <li>001 = Sets Internal Loopback mode</li> <li>001 = Sets Disable mode</li> <li>000 = Sets Normal CAN FD mode; supports mixing of full CAN FD and classic CAN 2.0 frames</li> </ul>                                                                         |

| bit 7-5  | OPMOD<2:0>: Operation Mode Status bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | <ul> <li>111 = Module is in Restricted Operation mode</li> <li>110 = Module is in Normal CAN 2.0 mode; error frames on CAN FD frames</li> <li>101 = Module is in External Loopback mode</li> <li>100 = Module is in Configuration mode</li> <li>011 = Module is in Listen Only mode</li> <li>010 = Module is in Internal Loopback mode</li> <li>010 = Module is in Internal Loopback mode</li> <li>001 = Module is in Disable mode</li> <li>000 = Module is in Normal CAN FD mode; supports mixing of full CAN FD and classic CAN 2.0 frames</li> </ul> |

**Note 1:** These bits can only be modified in Configuration mode (OPMOD<2:0> = 100).

### REGISTER 11-33: C1FIFOCONLx: CAN FIFO CONTROL REGISTER x (x = 1 TO 7) LOW (CONTINUED)

| bit 2 | TFERFFIE: Transmit/Receive FIFO Empty/Full Interrupt Enable bit           |

|-------|---------------------------------------------------------------------------|

|       | TXEN = 1 (FIFO configured as a transmit FIFO):                            |

|       | Transmit FIFO Empty Interrupt Enable                                      |

|       | 1 = Interrupt is enabled for FIFO empty                                   |

|       | 0 = Interrupt is disabled for FIFO empty                                  |

|       | TXEN = 0 (FIFO configured as a receive FIFO):                             |

|       | Receive FIFO Full Interrupt Enable                                        |

|       | 1 = Interrupt is enabled for FIFO full                                    |

|       | 0 = Interrupt is disabled for FIFO full                                   |

| bit 1 | TFHRFHIE: Transmit/Receive FIFO Half Empty/Half Full Interrupt Enable bit |

|       | TXEN = 1 (FIFO configured as a transmit FIFO):                            |

|       | Transmit FIFO Half Empty Interrupt Enable                                 |

|       | 1 = Interrupt is enabled for FIFO half empty                              |

|       | 0 = Interrupt is disabled for FIFO half empty                             |

|       | TXEN = 0 (FIFO configured as a receive FIFO):                             |

|       | Receive FIFO Half Full Interrupt Enable                                   |

|       | 1 = Interrupt is enabled for FIFO half full                               |

|       | 0 = Interrupt is disabled for FIFO half full                              |

| bit 0 | TFNRFNIE: Transmit/Receive FIFO Not Full/Not Empty Interrupt Enable bit   |

|       | TXEN = 1 (FIFO configured as a transmit FIFO):                            |

|       | Transmit FIFO Not Full Interrupt Enable                                   |

|       | 1 = Interrupt is enabled for FIFO not full                                |

|       | 0 = Interrupt is disabled for FIFO not full                               |

|       | TXEN = 0 (FIFO configured as a receive FIFO):                             |

|       | Receive FIFO Not Empty Interrupt Enable                                   |

|       | 1 = Interrupt is enabled for FIFO not empty                               |

|       | 0 = Interrupt is disabled for FIFO not empty                              |

**Note 1:** This bit can only be modified in Configuration mode (OPMOD<2:0> = 100).

### REGISTER 11-38: C1FIFOUAHx: CAN FIFO USER ADDRESS REGISTER x (x = 1 TO 7) HIGH<sup>(1)</sup>

| R-x      | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|----------|-----|-----|--------|---------|-----|-----|-------|

|          |     |     | FIFOUA | <31:24> |     |     |       |

| bit 15   |     |     |        |         |     |     | bit 8 |

| R-x      | R-x | R-x | R-x    | R-x     | R-x | R-x | R-x   |

|          |     |     | FIFOUA | <23:16> |     |     |       |

| bit 7    |     |     |        |         |     |     | bit 0 |

|          |     |     |        |         |     |     |       |

| l ecend. |     |     |        |         |     |     |       |

| Legenu.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **FIFOUA<31:16>:** FIFO User Address bits <u>TXEN = 1 (FIFO configured as a transmit buffer):</u> A read of this register will return the address where the next message is to be written (FIFO head). <u>TXEN = 0 (FIFO configured as a receive buffer):</u> A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

# REGISTER 11-39: C1FIFOUALx: CAN FIFO USER ADDRESS REGISTER x (x = 1 TO 7) LOW<sup>(1)</sup>

| R-x             | R-x | R-x              | R-x                                     | R-x     | R-x | R-x | R-x   |  |

|-----------------|-----|------------------|-----------------------------------------|---------|-----|-----|-------|--|

|                 |     |                  | FIFOUA                                  | \<15:8> |     |     |       |  |

| bit 15          |     |                  |                                         |         |     |     | bit 8 |  |

| R-x             | R-x | R-x              | R-x                                     | R-x     | R-x | R-x | R-x   |  |

|                 |     |                  | FIFOU                                   | A<7:0>  |     |     |       |  |

| bit 7           |     |                  |                                         |         |     |     | bit 0 |  |

| Legend:         |     |                  |                                         |         |     |     |       |  |

| R = Readable b  | bit | W = Writable bit | it U = Unimplemented bit, read as '0'   |         |     |     |       |  |

| -n = Value at P | OR  | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |         |     |     |       |  |

bit 15-0

FIFOUA<15:0>: FIFO User Address bits

TXEN = 1 (FIFO configured as a transmit buffer):

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0 (FIFO configured as a receive buffer):

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This register is not ensured to read correctly in Configuration mode and should only be accessed when the module is not in Configuration mode.

### REGISTER 13-17: ADEISTATL: ADC EARLY INTERRUPT STATUS REGISTER LOW

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|-------|-------|-----------------|-------|-------|-------|

|                                                                      |       |       | EIST  | AT<15:8>        |       |       |       |

| bit 15                                                               |       |       |       |                 |       |       | bit 8 |

|                                                                      |       |       |       |                 |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |       |       | EIST  | AT<7:0>         |       |       |       |

| bit 7                                                                |       |       |       |                 |       |       | bit 0 |

|                                                                      |       |       |       |                 |       |       |       |

| Legend:                                                              |       |       |       |                 |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       | d as '0'        |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is u |       |       |       | x = Bit is unkr | nown  |       |       |

bit 15-0 EISTAT<15:0>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

### REGISTER 13-18: ADEISTATH: ADC EARLY INTERRUPT STATUS REGISTER HIGH

| U-0                                | U-0   | U-0            | U-0    | U-0                                     | U-0              | R/W-0    | R/W-0   |

|------------------------------------|-------|----------------|--------|-----------------------------------------|------------------|----------|---------|

| —                                  | _     | —              | —      | —                                       | —                | EISTAT   | <25:24> |

| bit 15                             |       |                |        |                                         |                  |          | bit 8   |

|                                    |       |                |        |                                         |                  |          |         |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0  | R/W-0                                   | R/W-0            | R/W-0    | R/W-0   |

|                                    |       |                | EISTAT | <23:16>                                 |                  |          |         |

| bit 7                              |       |                |        |                                         |                  |          | bit 0   |

|                                    |       |                |        |                                         |                  |          |         |

| Legend:                            |       |                |        |                                         |                  |          |         |

| R = Readable                       | bit   | W = Writable I | bit    | U = Unimpler                            | nented bit, read | l as '0' |         |

| -n = Value at POR '1' = Bit is set |       |                |        | '0' = Bit is cleared x = Bit is unknown |                  |          | nown    |

|                                    |       |                |        |                                         |                  |          |         |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 EISTAT<25:16>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

# REGISTER 15-5: POSxCNTL: POSITION x COUNTER REGISTER LOW

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|----------------------|------------------------------------|--------------------|-------|-------|--|

|                                    |       |       | POSC                 | NT<15:8>                           |                    |       |       |  |

| bit 15                             |       |       |                      |                                    |                    |       | bit 8 |  |

|                                    |       |       |                      |                                    |                    |       |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |

|                                    |       |       | POSC                 | CNT<7:0>                           |                    |       |       |  |

| bit 7                              |       |       |                      |                                    |                    |       | bit 0 |  |

|                                    |       |       |                      |                                    |                    |       |       |  |

| Legend:                            |       |       |                      |                                    |                    |       |       |  |

| R = Readable bit W = Writable bit  |       |       | bit                  | U = Unimplemented bit, read as '0' |                    |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared |                                    | x = Bit is unknown |       |       |  |

|                                    |       |       |                      |                                    |                    |       |       |  |

bit 15-0 POSCNT<15:0>: Low Word Used to Form 32-Bit Position Counter Register (POSxCNT) bits

### REGISTER 15-6: POSxCNTH: POSITION x COUNTER REGISTER HIGH

| R/W-0                              | R/W-0 | R/W-0  | R/W-0                                | R/W-0                              | R/W-0 | R/W-0 | R/W-0  |  |

|------------------------------------|-------|--------|--------------------------------------|------------------------------------|-------|-------|--------|--|

|                                    |       |        | POSC                                 | NT<31:24>                          |       |       |        |  |

| bit 15                             |       |        |                                      |                                    |       |       | bit 8  |  |

|                                    |       | 5444.6 | 5444.6                               | 54446                              |       | 54446 | 5444.6 |  |

| R/W-0                              | R/W-0 | R/W-0  | R/W-0                                | R/W-0                              | R/W-0 | R/W-0 | R/W-0  |  |

|                                    |       |        | POSCI                                | NT<23:16>                          |       |       |        |  |

| bit 7                              |       |        |                                      |                                    |       |       | bit 0  |  |

| Legend:                            |       |        |                                      |                                    |       |       |        |  |

| R = Readable bit W = Writable bit  |       |        |                                      | U = Unimplemented bit, read as '0' |       |       |        |  |

| -n = Value at POR '1' = Bit is set |       |        | '0' = Bit is cleared x = Bit is unkr |                                    |       | nown  |        |  |

bit 15-0 **POSCNT<31:16>:** High Word Used to Form 32-Bit Position Counter Register (POSxCNT) bits

# REGISTER 15-8: VELxCNT: VELOCITY x COUNTER REGISTER

| R/W-0                                                   | R/W-0 | R/W-0          | R/W-0 | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |  |

|---------------------------------------------------------|-------|----------------|-------|------------------------------------|-----------------|-------|-------|--|

|                                                         |       |                | VELCI | NT<15:8>                           |                 |       |       |  |

| bit 15                                                  |       |                |       |                                    |                 |       | bit 8 |  |

|                                                         |       |                |       |                                    |                 |       |       |  |

| R/W-0                                                   | R/W-0 | R/W-0          | R/W-0 | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |  |

|                                                         |       |                | VELC  | NT<7:0>                            |                 |       |       |  |

| bit 7                                                   |       |                |       |                                    |                 |       | bit 0 |  |

|                                                         |       |                |       |                                    |                 |       |       |  |

| Legend:                                                 |       |                |       |                                    |                 |       |       |  |

| R = Readable                                            | bit   | W = Writable b | bit   | U = Unimplemented bit, read as '0' |                 |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |       |                |       | ared                               | x = Bit is unkr | nown  |       |  |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

# REGISTER 15-9: VELxCNTH: VELOCITY x COUNTER REGISTER HIGH<sup>(1)</sup>

| R/W-0           | R/W-0                                                                | R/W-0 | R/W-0                | R/W-0     | R/W-0              | R/W-0 | R/W-0 |

|-----------------|----------------------------------------------------------------------|-------|----------------------|-----------|--------------------|-------|-------|

|                 |                                                                      |       | VELC                 | NT<31:24> |                    |       |       |

| bit 15          |                                                                      |       |                      |           |                    |       | bit 8 |

|                 |                                                                      |       |                      |           |                    |       |       |

| R/W-0           | R/W-0                                                                | R/W-0 | R/W-0                | R/W-0     | R/W-0              | R/W-0 | R/W-0 |

|                 |                                                                      |       | VELC                 | NT<23:16> |                    |       |       |

| bit 7           |                                                                      |       |                      |           |                    |       | bit 0 |

|                 |                                                                      |       |                      |           |                    |       |       |

| Legend:         |                                                                      |       |                      |           |                    |       |       |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                      |           |                    |       |       |

| -n = Value at I | -n = Value at POR '1' = Bit is set                                   |       | '0' = Bit is cleared |           | x = Bit is unknown |       |       |

|                 |                                                                      |       |                      |           |                    |       |       |

bit 15-0 VELCNT<31:16>: Velocity Counter bits

Note 1: This register is not present on all devices.

# REGISTER 15-20: QEIxLECL: QEIx LESS THAN OR EQUAL COMPARE REGISTER LOW

| R/W-0                              | R/W-0 | R/W-0          | R/W-0        | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|----------------|--------------|-----------------------------------------|-------|-------|-------|--|

|                                    |       |                | QEILE        | EC<15:8>                                |       |       |       |  |

| bit 15                             |       |                |              |                                         |       |       | bit 8 |  |

|                                    |       |                |              |                                         |       |       |       |  |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0        | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |                | QEIL         | EC<7:0>                                 |       |       |       |  |

| bit 7                              |       |                |              |                                         |       |       | bit 0 |  |

| Legend:                            |       |                |              |                                         |       |       |       |  |

| R = Readable                       | bit   | W = Writable b | U = Unimplen | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |                |              | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |

bit 15-0 **QEILEC<15:0>:** Low Word Used to Form 32-Bit Less Than or Equal Compare Register (QEIxLEC) bits

### REGISTER 15-21: QEIxLECH: QEIx LESS THAN OR EQUAL COMPARE REGISTER HIGH

| R/W-0                             | R/W-0 | R/W-0            | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0 |  |

|-----------------------------------|-------|------------------|------------------|------------------------------------|----------------------|-------|-------|--|

|                                   |       |                  | QEILE            | C<31:24>                           |                      |       |       |  |

| bit 15                            |       |                  |                  |                                    |                      |       | bit 8 |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0 |  |

|                                   |       | -                | QEILE            | C<23:16>                           | -                    |       | -     |  |

| bit 7                             |       |                  |                  |                                    |                      |       | bit 0 |  |

|                                   |       |                  |                  |                                    |                      |       |       |  |

| Legend:                           |       |                  |                  |                                    |                      |       |       |  |

| R = Readable bit W = Writable bit |       |                  | bit              | U = Unimplemented bit, read as '0' |                      |       |       |  |

| -n = Value at POR '1' :           |       | '1' = Bit is set | '1' = Bit is set |                                    | '0' = Bit is cleared |       | nown  |  |

bit 15-0 **QEILEC<31:16>:** High Word Used to Form 32-Bit Less Than or Equal Compare Register (QEIxLEC) bits

| <b>REGISTER 16-11:</b> | UxP3: UARTx TIMING PARAMETER 3 REGISTER |

|------------------------|-----------------------------------------|

|------------------------|-----------------------------------------|

| R/W-0         | R/W-0                               | R/W-0                                                     | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0         |

|---------------|-------------------------------------|-----------------------------------------------------------|----------------|-------------------|------------------|-----------------|---------------|

|               |                                     |                                                           | P3<′           | 15:8>             |                  |                 |               |

| bit 15        |                                     |                                                           |                |                   |                  |                 | bit 8         |

| R/W-0         | R/W-0                               | R/W-0                                                     | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0         |

| R/W-U         | R/W-U                               | R/W-0                                                     |                |                   | R/W-0            | R/W-0           | R/W-0         |

| 1.1.7         |                                     |                                                           | P3<            | 7:0>              |                  |                 |               |

| bit 7         |                                     |                                                           |                |                   |                  |                 | bit 0         |

| Lonordi       |                                     |                                                           |                |                   |                  |                 |               |

| Legend:       |                                     |                                                           |                |                   |                  |                 |               |

| R = Readabl   |                                     | W = Writable bi                                           | t              | -                 | nented bit, read | l as '0'        |               |

| -n = Value at | t POR                               | '1' = Bit is set                                          |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |

| bit 15-0      | DMX RX:                             | arameter 3 bits<br>number to receiv<br><u>&lt;:</u>       | e – 1, not inc | luding Start coc  | le (bits<8:0>).  |                 |               |

|               | Number of b                         | ytes to receive (bit                                      | ts<7:0>).      |                   |                  |                 |               |

|               | (bits<7:0>).<br><u>Smart Card I</u> | ik the UxP2 addre<br><u>Mode:</u><br>• Counter bits (bits |                | P2 address bit    | is used, 0 = F   | P2 address bit  | is masked off |

### REGISTER 16-12: UxP3H: UARTx TIMING PARAMETER 3 REGISTER HIGH

| U-0          | U-0                       | U-0              | U-0         | U-0                                | U-0   | U-0                | U-0   |  |  |

|--------------|---------------------------|------------------|-------------|------------------------------------|-------|--------------------|-------|--|--|

|              | —                         | _                | —           | —                                  | —     | _                  | _     |  |  |

| bit 15       |                           |                  |             | ÷                                  |       |                    | bit 8 |  |  |

|              |                           |                  |             |                                    |       |                    |       |  |  |

| R/W-0        | R/W-0                     | R/W-0            | R/W-0       | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|              |                           |                  | P3<2        | 23:16>                             |       |                    |       |  |  |

| bit 7        |                           |                  |             |                                    |       |                    | bit 0 |  |  |

|              |                           |                  |             |                                    |       |                    |       |  |  |

| Legend:      |                           |                  |             |                                    |       |                    |       |  |  |

| R = Readat   | ole bit                   | W = Writable     | bit         | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value a | at POR                    | '1' = Bit is set |             | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |

|              |                           |                  |             |                                    |       |                    |       |  |  |

| bit 15-8     | Unimplement               | ted: Read as '0  | )'          |                                    |       |                    |       |  |  |

| bit 7-0      | <b>P3&lt;23:16&gt;:</b> P | arameter 3 Hig   | h bits      |                                    |       |                    |       |  |  |

|              | Smart Card M              | lode:            |             |                                    |       |                    |       |  |  |

|              | Waiting Time              | Counter bits (bi | ts<23:16>). |                                    |       |                    |       |  |  |

|              | Other Modes:              |                  |             |                                    |       |                    |       |  |  |

|              | Not used.                 |                  |             |                                    |       |                    |       |  |  |

|              |                           |                  |             |                                    |       |                    |       |  |  |

# REGISTER 18-1: I2CxCONL: I2Cx CONTROL REGISTER LOW (CONTINUED)

| bit 8   | SMEN: SMBus Input Levels Enable bit                                                                                                                                                                                              |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables input logic so thresholds are compliant with the SMBus specification</li> <li>0 = Disables SMBus-specific inputs</li> </ul>                                                                                 |

| bit 7   | GCEN: General Call Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                 |

|         | <ul> <li>1 = Enables interrupt when a general call address is received in I2CxRSR; module is enabled for reception</li> <li>0 = General call address is disabled.</li> </ul>                                                     |

| bit 6   | STREN: SCLx Clock Stretch Enable bit                                                                                                                                                                                             |

|         | In I <sup>2</sup> C Slave mode only; used in conjunction with the SCLREL bit.<br>1 = Enables clock stretching<br>0 = Disables clock stretching                                                                                   |

| bit 5   | ACKDT: Acknowledge Data bit                                                                                                                                                                                                      |

|         | In I <sup>2</sup> C Master mode during Master Receive mode. The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.                                                          |

|         | In I <sup>2</sup> C Slave mode when AHEN = 1 or DHEN = 1. The value that the Slave will transmit when it initiates<br>an Acknowledge sequence at the end of an address or data reception.<br>1 = NACK is sent<br>0 = ACK is sent |

| bit 4   | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                                                                           |

|         | In I <sup>2</sup> C Master mode only; applicable during Master Receive mode.<br>1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit<br>0 = Acknowledge sequence is Idle                       |

| bit 3   | RCEN: Receive Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                     |

|         | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C; automatically cleared by hardware at end of 8-bit receive data byte</li> <li>0 = Receive sequence is not in progress</li> </ul>                                            |

| bit 2   | <b>PEN:</b> Stop Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                        |

|         | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins</li> <li>0 = Stop condition is Idle</li> </ul>                                                                                                                       |

| bit 1   | <b>RSEN:</b> Restart Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                    |

|         | <ul> <li>1 = Initiates Restart condition on SDAx and SCLx pins</li> <li>0 = Restart condition is Idle</li> </ul>                                                                                                                 |

| bit 0   | SEN: Start Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                              |

|         | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins</li> <li>0 = Start condition is Idle</li> </ul>                                                                                                                     |

| Note 1: | Automatically cleared to '0' at the beginning of Slave transmission; automatically cleared to '0' at the end of Slave reception.                                                                                                 |

2: Automatically cleared to '0' at the beginning of Slave transmission.

### REGISTER 18-3: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <b>S:</b> I2Cx Start bit<br>Updated when Start, Reset or Stop is detected; cleared when the I <sup>2</sup> C module is disabled, I2CEN = 0.<br>1 = Indicates that a Start (or Repeated Start) bit has been detected last<br>0 = Start bit was not detected last |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as I <sup>2</sup> C Slave)                                                                                                                                                                              |

|       | <ul> <li>1 = Read: Indicates the data transfer is output from the Slave</li> <li>0 = Write: Indicates the data transfer is input to the Slave</li> </ul>                                                                                                        |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                             |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> </ul>                                                                                                                                             |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                                            |

|       | 1 = Transmit is in progress, I2CxTRN is full (8-bits of data)                                                                                                                                                                                                   |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                 |

## REGISTER 18-4: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      | —   | —   | —   | —   | —   | MSK   | <9:8> |

| bit 15 |     |     |     |     |     |       | bit 8 |

|        |     |     |     |     |     |       |       |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| MSK<7:0>    |       |       |       |       |       |       |       |  |

| bit 7 bit 0 |       |       |       |       |       |       |       |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 MSK<9:0>: I2Cx Mask for Address Bit x Select bits

1 = Enables masking for bit x of the incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

# 20.1 Transmit Mode

By default, the SENTx module is configured for transmit operation. The module can be configured for continuous asynchronous message frame transmission, or alternatively, for Synchronous mode triggered by software. When enabled, the transmitter will send a Sync, followed by the appropriate number of data nibbles, an optional CRC and optional pause pulse. The tick period used by the SENTx transmitter is set by writing a value to the TICKTIME<15:0> (SENTxCON2<15:0>) bits. The tick period calculations are shown in Equation 20-1.

#### EQUATION 20-1: TICK PERIOD CALCULATION

$TICKTIME < 15:0 > = \frac{TTICK}{TCLK} - 1$

An optional pause pulse can be used in Asynchronous mode to provide a fixed message frame time period. The frame period used by the SENTx transmitter is set by writing a value to the FRAMETIME<15:0> (SENTxCON3<15:0>) bits. The formulas used to calculate the value of frame time are shown in Equation 20-2.

### EQUATION 20-2: FRAME TIME CALCULATIONS

FRAMETIME<15:0> = TTICK/TFRAME

$FRAMETIME < 15:0 \ge 122 + 27N$

$FRAMETIME < 15:0 \ge 848 + 12N$

Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6

**Note:** The module will not produce a pause period with less than 12 ticks, regardless of the FRAMETIME<15:0> value. FRAMETIME<15:0> values beyond 2047 will have no effect on the length of a data frame.

### 20.1.1 TRANSMIT MODE CONFIGURATION

### 20.1.1.1 Initializing the SENTx Module

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 0 for Transmit mode.

- Write TXM (SENTxCON1<10>) = 0 for Asynchronous Transmit mode or TXM = 1 for Synchronous mode.

- 3. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 4. Write CRCEN (SENTxCON1<8>) for hardware or software CRC calculation.

- 5. Write PPP (SENTxCON1<7>) for optional pause pulse.

- 6. If PPP = 1, write TFRAME to SENTxCON3.

- 7. Write SENTxCON2 with the appropriate value for the desired tick period.

- 8. Enable interrupts and set interrupt priority.

- 9. Write initial status and data values to SENTxDATH/L.

- 10. If CRCEN = 0, calculate CRC and write the value to CRC<3:0> (SENTxDATL<3:0>).

- 11. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

User software updates to SENTxDATH/L must be performed after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt to trigger data writes.

# 22.6 Control Registers

# REGISTER 22-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

| R/W-0         | U-0                                        | R/W-0            | R/W-0          | R/W-0                            | R/W-0            | R/W-0           | R/W-0          |  |

|---------------|--------------------------------------------|------------------|----------------|----------------------------------|------------------|-----------------|----------------|--|

| CCPON         | —                                          | CCPSIDL          | CCPSLP         | TMRSYNC                          | CLKSEL2          | CLKSEL1         | CLKSEL0        |  |

| bit 15        |                                            |                  |                |                                  |                  |                 | bit 8          |  |

|               |                                            |                  |                |                                  |                  |                 |                |  |

| R/W-0         | R/W-0                                      | R/W-0            | R/W-0          | R/W-0                            | R/W-0            | R/W-0           | R/W-0          |  |

| TMRPS1        | TMRPS0                                     | T32              | CCSEL          | MOD3                             | MOD2             | MOD1            | MOD0           |  |

| bit 7         |                                            |                  |                |                                  |                  |                 | bit 0          |  |

|               |                                            |                  |                |                                  |                  |                 |                |  |

| Legend:       |                                            |                  |                |                                  |                  |                 |                |  |

| R = Readable  | e bit                                      | W = Writable     | oit            | U = Unimplem                     | nented bit, read | l as '0'        |                |  |

| -n = Value at | POR                                        | '1' = Bit is set |                | '0' = Bit is clea                | ared             | x = Bit is unkr | iown           |  |

|               |                                            |                  |                |                                  |                  |                 |                |  |

| bit 15        |                                            | Px Module Enal   |                |                                  |                  |                 |                |  |

|               |                                            |                  | an operating m | node specified b                 | by the MOD<3:    | 0> control bits |                |  |

| 1.1.4.4       | 0 = Module is                              |                  |                |                                  |                  |                 |                |  |

| bit 14        | -                                          | ted: Read as '(  |                |                                  |                  |                 |                |  |

| bit 13        |                                            | CPx Stop in Idle |                | device enters Id                 | lla mada         |                 |                |  |

|               |                                            | s module opera   |                |                                  | lie mode         |                 |                |  |

| bit 12        |                                            | Px Sleep Mode    |                |                                  |                  |                 |                |  |

|               |                                            | ontinues to ope  |                | modes                            |                  |                 |                |  |

|               | 0 = Module does not operate in Sleep modes |                  |                |                                  |                  |                 |                |  |

| bit 11        | TMRSYNC: T                                 | ime Base Cloc    | k Synchroniza  | tion bit                         |                  |                 |                |  |

|               | •                                          |                  | me base clock  | is selected and                  | d synchronized   | to the internal | system clocks  |  |

|               |                                            | _<2:0> ≠ 000)    | ime hase di    | ock is selecte                   | and does         | not require s   | unchronization |  |

|               |                                            | _<2:0> = 000)    |                | JCK IS SELECTE                   |                  | not require s   | ynenionzation  |  |

| bit 10-8      |                                            | >: CCPx Time     | Base Clock Se  | elect bits                       |                  |                 |                |  |

|               | 111 = PPS T                                | xCK input        |                |                                  |                  |                 |                |  |

|               | 110 = CLC4                                 |                  |                |                                  |                  |                 |                |  |

|               | 101 = CLC3<br>100 = CLC2                   |                  |                |                                  |                  |                 |                |  |

|               | 011 = CLC2                                 |                  |                |                                  |                  |                 |                |  |

|               | 010 = Fosc                                 |                  |                |                                  |                  |                 |                |  |

|               |                                            | nce Clock (REF   | CLKO)          |                                  |                  |                 |                |  |

| 1.1.7.0       | 000 = Fosc/2                               | ( )              |                | 1.10                             |                  |                 |                |  |

| bit 7-6       |                                            | : Time Base Pr   | escale Select  | DITS                             |                  |                 |                |  |

|               | 11 = 1:64 Pre<br>10 = 1:16 Pre             |                  |                |                                  |                  |                 |                |  |

|               | 01 = 1:4 Pres                              |                  |                |                                  |                  |                 |                |  |

|               | 00 = 1:1 Pres                              | caler            |                |                                  |                  |                 |                |  |