Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 100MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 24K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

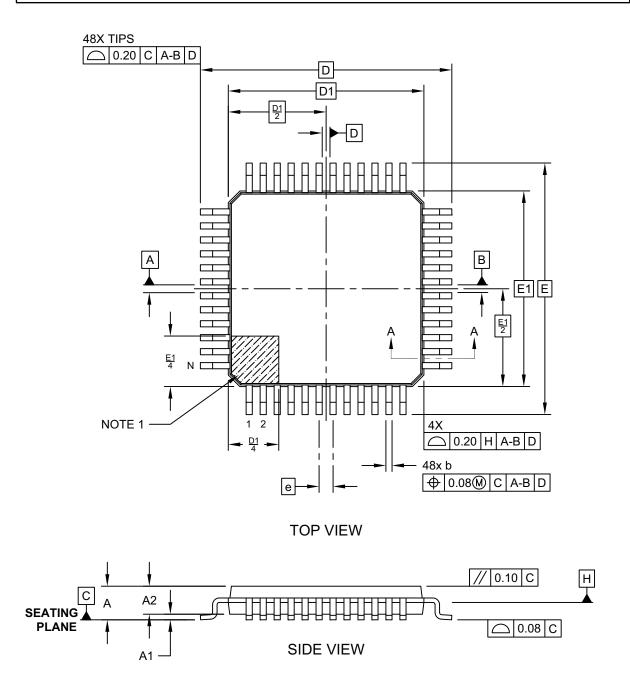

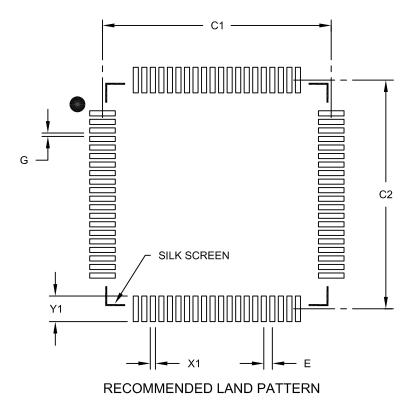

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck256mp506-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.5 Dual Partition Flash Configuration

For dsPIC33CK256MP508 devices operating in Dual Partition Flash Program Memory modes, the Inactive Partition can be erased and programmed without stalling the processor. The same programming algorithms are used for programming and erasing the Flash in the Inactive Partition, as described in **Section 5.2 "RTSP Operation"**. On top of the page erase option, the entire Flash memory of the Inactive Partition can be erased by configuring the NVMOP<3:0> bits in the NVMCON register.

Note 1: The application software to be loaded into the Inactive Partition will have the address of the Active Partition. The bootloader firmware will need to offset the address by 0x400000 in order to write to the Inactive Partition.

## 5.5.1 FLASH PARTITION SWAPPING

The Boot Sequence Number is used for determining the Active Partition at start-up and is encoded within the FBTSEQ Configuration register bits. Unlike most Configuration registers, which only utilize the lower 16 bits of the program memory, FBTSEQ is a 24-bit Configuration Word. The Boot Sequence Number (BSEQ) is a 12-bit value and is stored in FBTSEQ twice. The true value is stored in bits, FBTSEQ<11:0>, and its complement is stored in bits, FBTSEQ<23:12>. At device Reset, the sequence numbers are read and the partition with the lowest sequence number becomes the Active Partition. If one of the Boot Sequence Numbers is invalid, the device will select the partition with the valid Boot Sequence Number, or default to Partition 1 if both sequence numbers are invalid. See Section 30.0 "Special Features" for more information.

The BOOTSWP instruction provides an alternative means of swapping the Active and Inactive Partitions (soft swap) without the need for a device Reset. The BOOTSWP must always be followed by a GOTO instruction. The BOOTSWP instruction swaps the Active and Inactive Partitions, and the PC vectors to the location specified by the GOTO instruction in the newly Active Partition.

It is important to note that interrupts should temporarily be disabled while performing the soft swap sequence and that after the partition swap, all peripherals and interrupts which were enabled remain enabled. Additionally, the RAM and stack will maintain state after the switch. As a result, it is recommended that applications using soft swaps jump to a routine that will reinitialize the device in order to ensure the firmware runs as expected. The Configuration registers will have no effect during a soft swap. For robustness of operation, in order to execute the BOOTSWP instruction, it is necessary to execute the NVM unlocking sequence as follows:

- 1. Write 0x55 to NVMKEY.

- 2. Write 0xAA to NVMKEY.

- 3. Execute the BOOTSWP instruction.

If the unlocking sequence is not performed, the BOOTSWP instruction will be executed as a forced NOP and a GOTO instruction, following the BOOTSWP instruction, will be executed, causing the PC to jump to that location in the current operating partition.

The SFTSWP and P2ACTIV bits in the NVMCON register are used to determine a successful swap of the Active and Inactive Partitions, as well as which partition is active. After the BOOTSWP and GOTO instructions, the SFTSWP bit should be polled to verify the partition swap has occurred and then cleared for the next panel swap event.

## 5.5.2 DUAL PARTITION MODES

While operating in Dual Partition mode, the dsPIC33CK256MP508 family devices have the option for both partitions to have their own defined security segments, as shown in Figure 27-4. Alternatively, the device can operate in Protected Dual Partition mode, where Partition 1 becomes permanently erase/write-protected. Protected Dual Partition mode allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1.

dsPIC33CK256MP508 family devices can also operate in Privileged Dual Partition mode, where additional security protections are implemented to allow for protection of intellectual property when multiple parties have software within the device. In Privileged Dual Partition mode, both partitions place additional restrictions on the FBSLIM register. These prevent changes to the size of the Boot Segment and General Segment, ensuring that neither segment will be altered.

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit       |

|-------|----------------------------------------------|

|       | 1 = Address error trap has occurred          |

|       | 0 = Address error trap has not occurred      |

| bit 2 | STKERR: Stack Error Trap Status bit          |

|       | 1 = Stack error trap has occurred            |

|       | 0 = Stack error trap has not occurred        |

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit  |

|       | 1 = Oscillator failure trap has occurred     |

|       | 0 = Oscillator failure trap has not occurred |

|       |                                              |

bit 0 Unimplemented: Read as '0'

## TABLE 8-6: REMAPPABLE OUTPUT PIN REGISTERS

| Register     | RP Pin | I/O Port      |

|--------------|--------|---------------|

| RPOR0<5:0>   | RP32   | Port Pin RB0  |

| RPOR0<13:8>  | RP33   | Port Pin RB1  |

| RPOR1<5:0>   | RP34   | Port Pin RB2  |

| RPOR1<13:8>  | RP35   | Port Pin RB3  |

| RPOR2<5:0>   | RP36   | Port Pin RB4  |

| RPOR2<13:8>  | RP37   | Port Pin RB5  |

| RPOR3<5:0>   | RP38   | Port Pin RB6  |

| RPOR3<13:8>  | RP39   | Port Pin RB7  |

| RPOR4<5:0>   | RP40   | Port Pin RB8  |

| RPOR4<13:8>  | RP41   | Port Pin RB9  |

| RPOR5<5:0>   | RP42   | Port Pin RB10 |

| RPOR5<13:8>  | RP43   | Port Pin RB11 |

| RPOR6<5:0>   | RP44   | Port Pin RB12 |

| RPOR6<13:8>  | RP45   | Port Pin RB13 |

| RPOR7<5:0>   | RP46   | Port Pin RB14 |

| RPOR7<13:8>  | RP47   | Port Pin RB15 |

| RPOR8<5:0>   | RP48   | Port Pin RC0  |

| RPOR8<13:8>  | RP49   | Port Pin RC1  |

| RPOR9<5:0>   | RP50   | Port Pin RC2  |

| RPOR9<13:8>  | RP51   | Port Pin RC3  |

| RPOR10<5:0>  | RP52   | Port Pin RC4  |

| RPOR10<13:8> | RP53   | Port Pin RC5  |

| RPOR11<5:0>  | RP54   | Port Pin RC6  |

| RPOR11<13:8> | RP55   | Port Pin RC7  |

| RPOR12<5:0>  | RP56   | Port Pin RC8  |

| RPOR12<13:8> | RP57   | Port Pin RC9  |

| RPOR13<5:0>  | RP58   | Port Pin RC10 |

| RPOR13<13:8> | RP59   | Port Pin RC11 |

| RPOR14<5:0>  | RP60   | Port Pin RC12 |

| RPOR14<13:8> | RP61   | Port Pin RC13 |

| RPOR15<5:0>  | RP62   | Port Pin RC14 |

| RPOR15<13:8> | RP63   | Port Pin RC15 |

| RPOR16<5:0>  | RP64   | Port Pin RD0  |

| RPOR16<13:8> | RP65   | Port Pin RD1  |

| RPOR17<5:0>  | RP66   | Port Pin RD2  |

| RPOR17<13:8> | RP67   | Port Pin RD3  |

| RPOR18<5:0>  | RP68   | Port Pin RD4  |

| RPOR18<13:8> | RP69   | Port Pin RD5  |

| RPOR19<5:0>  | RP70   | Port Pin RD6  |

| RPOR19<13:8> | RP71   | Port Pin RD7  |

| RPOR20<5:0>  | RP72   | Port Pin RD8  |

| RPOR20<13:8> | RP73   | Port Pin RD9  |

| RPOR21<5:0>  | RP74   | Port Pin D10  |

| RPOR21<13:8> | RP75   | Port Pin RD11 |

| RPOR22<5:0>  | RP76   | Port Pin RD12 |

| RPOR22<13:8> | RP77   | Port Pin RD13 |

## REGISTER 8-41: RPINR30: PERIPHERAL PIN SELECT INPUT REGISTER 30

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   |     | -   | —   | —   | —   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SS3R7 | SS3R6 | SS3R5 | SS3R4 | SS3R3 | SS3R2 | SS3R1 | SS3R0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **SS3R<7:0>:** Assign SPI3 Slave Select (SS2) to the Corresponding RPn Pin bits See Table 8-4.

#### REGISTER 8-42: RPINR32: PERIPHERAL PIN SELECT INPUT REGISTER 32

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TCKI9R7 | TCKI9R6 | TCKI9R5 | TCKI9R4 | TCKI9R3 | TCKI9R2 | TCKI9R1 | TCKI9R0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| U-0     |

| —       | —       |         | _       | _       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 **TCKI9R<7:0>:** Assign MCCP Timer9 Input (TCKI9) to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0 Unimplemented: Read as '0'

## 9.6 Oscillator Control Registers

| U-0     | R-0   | R-0   | R-0   | U-0               | R/W-y                | R/W-y                | R/W-y                |

|---------|-------|-------|-------|-------------------|----------------------|----------------------|----------------------|

| —       | COSC2 | COSC1 | COSC0 | —                 | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSC0 <sup>(2)</sup> |

| bit 15  |       |       |       |                   |                      |                      | bit 8                |

|         |       |       |       |                   |                      |                      |                      |

| R/W-0   | U-0   | R-0   | U-0   | R/W-0             | U-0                  | U-0                  | R/W-0                |

| CLKLOCK |       | LOCK  | —     | CF <sup>(3)</sup> | —                    | —                    | OSWEN                |

| bit 7   |       |       |       |                   |                      |                      | bit 0                |

#### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| Legend:           | y = Value set from Co | y = Value set from Configuration bits on POR |                    |  |  |

|-------------------|-----------------------|----------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                        | t, read as '0'     |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                         | x = Bit is unknown |  |  |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits (read-only)

- 111 = Fast RC Oscillator (FRC) with Divide-by-n (FRCDIVN)

- 110 = Backup FRC (BFRC)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Reserved default to FRC

- 011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(2)</sup>

- 111 = Fast RC Oscillator (FRC) with Divide-by-n (FRCDIVN)

- 110 = Backup FRC (BFRC)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Reserved default to FRC

- 011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

#### bit 7 CLKLOCK: Clock Lock Enable bit

- 1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and PLL configurations may be modified

- 0 = Clock and PLL selections are not locked, configurations may be modified

- bit 6 Unimplemented: Read as '0'

- bit 5 LOCK: PLL Lock Status bit (read-only)

- 1 = Indicates that PLL is in lock or PLL start-up timer is satisfied

- 0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled

- bit 4 Unimplemented: Read as '0'

- **Note 1:** Writes to this register require an unlock sequence.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

## 12.0 HIGH-RESOLUTION PWM WITH FINE EDGE PLACEMENT

Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Resolution PWM with Fine Edge Placement" (DS70005320) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The High-Speed PWM (HSPWM) module is a Pulse-Width Modulated (PWM) module to support both motor control and power supply applications. This flexible module provides features to support many types of Motor Control (MC) and Power Control (PC) applications, including:

- AC-to-DC Converters

- DC-to-DC Converters

- AC and DC Motors: BLDC, PMSM, ACIM, SRM, etc.

- Inverters

- Battery Chargers

- Digital Lighting

- Power Factor Correction (PFC)

## 12.1 Features

- 8 Independent PWM Generators, each with Dual Outputs

- · Operating modes:

- Independent Edge mode

- Variable Phase PWM mode

- Center-Aligned mode

- Double Update Center-Aligned mode

- Dual Edge Center-Aligned mode

- Dual PWM mode

- · Output modes:

- Complementary

- Independent

- Push-Pull

- Dead-Time Generator

- Leading-Edge Blanking (LEB)

- · Output Override for Fault Handling

- Flexible Period/Duty Cycle Updating Options

- Programmable Control Inputs (PCI)

- Advanced Triggering Options

- 6 Combinatorial Logic Outputs

- · 6 PWM Event Outputs

#### R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 CLIEN<sup>(2)</sup> FI TIFN<sup>(1)</sup> SIFN<sup>(4)</sup> FFIFN<sup>(3)</sup> **IEVTSEL1 IEVTSEL0** \_\_\_\_ \_ bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ADTR2EN3 ADTR2EN2 ADTR2EN1 ADTR10FS4 ADTR10FS3 ADTR10FS2 ADTR10FS1 ADTR10FS0 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown FLTIEN: PCI Fault Interrupt Enable bit<sup>(1)</sup> bit 15 1 = Fault interrupt is enabled 0 = Fault interrupt is disabled bit 14 CLIEN: PCI Current-Limit Interrupt Enable bit<sup>(2)</sup> 1 = Current-limit interrupt is enabled 0 = Current-limit interrupt is disabled bit 13 FFIEN: PCI Feed-Forward Interrupt Enable bit<sup>(3)</sup> 1 = Feed-forward interrupt is enabled 0 = Feed-forward interrupt is disabled SIEN: PCI Sync Interrupt Enable bit<sup>(4)</sup> bit 12 1 = Sync interrupt is enabled 0 = Sync interrupt is disabled bit 11-10 Unimplemented: Read as '0' bit 9-8 IEVTSEL<1:0>: Interrupt Event Selection bits 11 = Time base interrupts are disabled (Sync, Fault, current-limit and feed-forward events can be independently enabled) 10 = Interrupts CPU at ADC Trigger 1 event 01 = Interrupts CPU at TRIGA compare event 00 = Interrupts CPU at EOC bit 7 ADTR2EN3: ADC Trigger 2 Source is PGxTRIGC Compare Event Enable bit 1 = PGxTRIGC register compare event is enabled as trigger source for ADC Trigger 2 0 = PGxTRIGC register compare event is disabled as trigger source for ADC Trigger 2 bit 6 ADTR2EN2: ADC Trigger 2 Source is PGxTRIGB Compare Event Enable bit 1 = PGxTRIGB register compare event is enabled as trigger source for ADC Trigger 2 0 = PGxTRIGB register compare event is disabled as trigger source for ADC Trigger 2 bit 5 ADTR2EN1: ADC Trigger 2 Source is PGxTRIGA Compare Event Enable bit 1 = PGxTRIGA register compare event is enabled as trigger source for ADC Trigger 2 0 = PGxTRIGA register compare event is disabled as trigger source for ADC Trigger 2 bit 4-0 ADTR10FS<4:0>: ADC Trigger 1 Offset Selection bits 11111 = Offset by 31 trigger events 00010 = Offset by 2 trigger events 00001 = Offset by 1 trigger event 00000 = No offset **Note 1:** An interrupt is only generated on the rising edge of the PCI Fault active signal. 2: An interrupt is only generated on the rising edge of the PCI current-limit active signal.

#### REGISTER 12-18: PGxEVTH: PWM GENERATOR x EVENT REGISTER HIGH

- 3: An interrupt is only generated on the rising edge of the PCI feed-forward active signal.4: An interrupt is only generated on the rising edge of the PCI Sync active signal.

- DS70005349B-page 278

Table 15-1 shows the truth table that describes how the Quadrature signals are decoded.

# TABLE 15-1:TRUTH TABLE FOR<br/>QUADRATURE ENCODER

| Quad | rent<br>rature<br>ate | Previous<br>Quadrature<br>State |     | Action                       |

|------|-----------------------|---------------------------------|-----|------------------------------|

| QEA  | QEB                   | QEA                             | QEB |                              |

| 1    | 1                     | 1                               | 1   | No count or direction change |

| 1    | 1                     | 1                               | 0   | Count up                     |

| 1    | 1                     | 0                               | 1   | Count down                   |

| 1    | 1                     | 0                               | 0   | Invalid state change; ignore |

| 1    | 0                     | 1                               | 1   | Count down                   |

| 1    | 0                     | 1                               | 0   | No count or direction change |

| 1    | 0                     | 0                               | 1   | Invalid state change; ignore |

| 1    | 0                     | 0                               | 0   | Count up                     |

| 0    | 1                     | 1                               | 1   | Count up                     |

| 0    | 1                     | 1                               | 0   | Invalid state change; ignore |

| 0    | 1                     | 0                               | 1   | No count or direction change |

| 0    | 1                     | 0                               | 0   | Count down                   |

| 0    | 0                     | 1                               | 1   | Invalid state change; ignore |

| 0    | 0                     | 1                               | 0   | Count down                   |

| 0    | 0                     | 0                               | 1   | Count up                     |

| 0    | 0                     | 0                               | 0   | No count or direction change |

Figure 15-2 illustrates the simplified block diagram of the QEI module. The QEI module consists of decoder logic to interpret the Phase A (QEAx) and Phase B (QEBx) signals, and an up/down counter to accumulate the count. The counter pulses are generated when the Quadrature state changes. The count direction information must be maintained in a register until a direction change is detected. The module also includes digital noise filters, which condition the input signal. The QEI module consists of the following major features:

- Four Input Pins: Two Phase Signals, an Index Pulse and a Home Pulse

- Programmable Digital Noise Filters on Inputs

- Quadrature Decoder providing Counter Pulses and Count Direction

- Count Direction Status

- 4x Count Resolution

- Index (INDXx) Pulse to Reset the Position Counter

- General Purpose 32-Bit Timer/Counter mode

- · Interrupts generated by QEI or Counter Events

- 32-Bit Velocity Counter

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 32-Bit Position Initialization/Capture Register

- 32-Bit Compare Less Than and Greater Than Registers

- External Up/Down Count mode

- · External Gated Count mode

- External Gated Timer mode

- Interval Timer mode

| R-0, HSC      | R-0, HSC                                        | R-0, HSC                                                  | U-0             | U-0                                                                 | R/C-0, HSC                   | R-0, HSC         | R-0, HSC        |

|---------------|-------------------------------------------------|-----------------------------------------------------------|-----------------|---------------------------------------------------------------------|------------------------------|------------------|-----------------|

| ACKSTAT       | TRSTAT                                          | ACKTIM                                                    | _               |                                                                     | BCL                          | GCSTAT           | ADD10           |

| bit 15        |                                                 |                                                           |                 |                                                                     |                              |                  | bit 8           |

|               |                                                 |                                                           |                 |                                                                     |                              |                  |                 |

| R/C-0, HS     | R/C-0, HS                                       | R-0, HSC                                                  | R-0, HSC        | R-0, HSC                                                            | R-0, HSC                     | R-0, HSC         | R-0, HSC        |

| IWCOL         | I2COV                                           | D/Ā                                                       | Р               | S                                                                   | R/W                          | RBF              | TBF             |

| bit 7         |                                                 |                                                           |                 |                                                                     |                              |                  | bit C           |

|               |                                                 |                                                           |                 |                                                                     |                              |                  |                 |

| Legend:       |                                                 | C = Clearable                                             | bit             |                                                                     | are Settable/C               |                  |                 |

| R = Readable  | e bit                                           | W = Writable                                              | oit             | U = Unimplen                                                        | nented bit, read             | l as '0'         |                 |

| -n = Value at | POR                                             | '1' = Bit is set                                          |                 | '0' = Bit is clea                                                   | ared                         | HS = Hardwa      | re Settable bit |

| bit 15        | 1 = Acknowle                                    | cknowledge Sta<br>dge was not re<br>dge was receiv        | ceived from SI  | ed in all Master<br>ave                                             | and Slave mod                | les)             |                 |

| bit 14        | 1 = Master tra                                  | nsmit Status bit<br>ansmit is in prog<br>ansmit is not in | gress (8 bits + | ng as I <sup>2</sup> C Mast<br>ACK)                                 | er; applicable to            | o Master transr  | mit operation)  |

| bit 13        | 1 = Indicates                                   | I <sup>2</sup> C bus is in ar                             | Acknowledge     | lid in I <sup>2</sup> C Slave<br>sequence, set<br>d on 9th rising e | on 8th falling e             |                  | lock            |

| bit 12-11     | Unimplement                                     | ted: Read as '                                            | )'              | -                                                                   |                              |                  |                 |

| bit 10        |                                                 |                                                           |                 | e mode; cleare                                                      |                              |                  | d, I2CEN = 0)   |

|               |                                                 | ision has been<br>Illision has bee                        |                 | ng a Master or S                                                    | Slave transmit o             | operation        |                 |

| bit 9         |                                                 |                                                           |                 | after Stop detec                                                    | tion)                        |                  |                 |

|               | 1 = General c                                   | all address was                                           | s received      |                                                                     |                              |                  |                 |

| 1.11.0        |                                                 | all address was                                           |                 |                                                                     | . (*                         |                  |                 |

| bit 8         |                                                 | lt Address Stati                                          |                 | after Stop dete                                                     | cuon)                        |                  |                 |

|               |                                                 | lress was mate                                            |                 |                                                                     |                              |                  |                 |

| bit 7         | IWCOL: I2Cx                                     | Write Collision                                           | Detect bit      |                                                                     |                              |                  |                 |

|               | 1 = An attemp<br>in softwar<br>0 = No collision | re                                                        | e I2CxTRN reg   | ister failed beca                                                   | ause the I <sup>2</sup> C mo | dule is busy; m  | ust be cleared  |

| bit 6         | 12COV: 12Cx 1                                   | Receive Overflo                                           | ow Flag bit     |                                                                     |                              |                  |                 |

|               |                                                 | ransmit mode,                                             |                 | ✓ register is still<br>ed in software                               | holding the pre              | evious byte; I20 | COV is a "don'i |

| bit 5         |                                                 | dress bit (when                                           | oporating as    | $^{2}$ C Slave)                                                     |                              |                  |                 |

|               | 1 = Indicates                                   | that the last by                                          | e received wa   | s data                                                              | an addroop                   |                  |                 |

| bit 1         |                                                 | -                                                         | e received of   | transmitted was                                                     | 5 all audiess                |                  |                 |

| bit 4         | 1 = Indicates                                   |                                                           | nas been dete   | cted; cleared wh<br>cted last                                       | nen the I <sup>2</sup> C mo  | dule is disabled | d, I2CEN = 0.   |

## REGISTER 18-3: I2CxSTAT: I2Cx STATUS REGISTER

## REGISTER 18-3: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: I2Cx Start bit<br>Updated when Start, Reset or Stop is detected; cleared when the I <sup>2</sup> C module is disabled, I2CEN = 0.<br>1 = Indicates that a Start (or Repeated Start) bit has been detected last<br>0 = Start bit was not detected last |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as I <sup>2</sup> C Slave)                                                                                                                                                                       |

|       | <ul> <li>1 = Read: Indicates the data transfer is output from the Slave</li> <li>0 = Write: Indicates the data transfer is input to the Slave</li> </ul>                                                                                                 |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                      |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> </ul>                                                                                                                                      |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                                     |

|       | 1 = Transmit is in progress, I2CxTRN is full (8-bits of data)                                                                                                                                                                                            |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                                                                                                                                                                               |

|       |                                                                                                                                                                                                                                                          |

## REGISTER 18-4: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| _      | —   | —   | —   | —   | _   | MSK   | <9:8> |

| bit 15 |     |     |     |     |     |       | bit 8 |

|        |     |     |     |     |     |       |       |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | MSK   | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 MSK<9:0>: I2Cx Mask for Address Bit x Select bits

1 = Enables masking for bit x of the incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

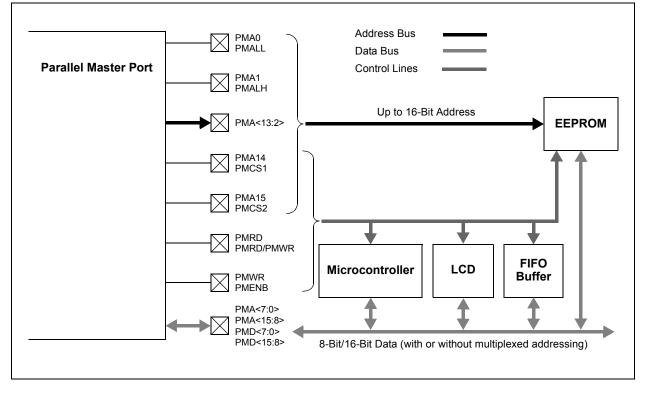

## 19.0 PARALLEL MASTER PORT (PMP)

- Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Parallel Master Port (PMP)" (DS70005344) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Not all device variants include the PMP. Refer to Table 1 and Table 2 for availability.

The Parallel Master Port (PMP) is a parallel 8-bit/16-bit I/O module specifically designed to communicate with a wide variety of parallel devices, such as communication peripherals, LCDs, external memory devices and microcontrollers. Because the interfaces to parallel peripherals vary significantly, the PMP module is highly configurable. The key features of the PMP module include:

- · Master and Slave Operating modes

- Up to 16 Programmable Address Lines

- · Up to Two Chip Select Lines

- Programmable Strobe Options:

- Individual read and write strobes or read/write strobe with enable strobe

- Address Auto-Increment/Auto-Decrement

- Programmable Address/Data Multiplexing

- Programmable Polarity on Control Signals

- Legacy Parallel Slave Port Support

- Enhanced Parallel Slave Support:

- Address support

- 4 bytes deep, auto-incrementing buffer

- Schmitt Trigger or TTL Input Buffers

- Programmable Wait States

- Dual Buffer Mode with Separate Read and Write Registers

- · Read Initiate Control

#### FIGURE 19-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

#### REGISTER 19-10: PMSTAT: PARALLEL MASTER PORT STATUS REGISTER (SLAVE MODES ONLY)

|               | -                               |                                   |                 |                          |                   |                 |       |  |  |

|---------------|---------------------------------|-----------------------------------|-----------------|--------------------------|-------------------|-----------------|-------|--|--|

| R-0           | R/W-0                           | U-0                               | U-0             | R-0                      | R-0               | R-0             | R-0   |  |  |

| IBF           | IBOV                            | _                                 | —               | IB3F                     | IB2F              | IB1F            | IB0F  |  |  |

| bit 15        |                                 |                                   |                 |                          |                   |                 | bit 8 |  |  |

|               |                                 |                                   |                 |                          |                   |                 |       |  |  |

| R-1           | R/W-0                           | U-0                               | U-0             | R-1                      | R-1               | R-1             | R-1   |  |  |

| OBE           | OBUF                            | OBUF — — OB3E OB2E OB1E O         |                 |                          |                   |                 |       |  |  |

| bit 7         |                                 |                                   |                 |                          |                   |                 | bit 0 |  |  |

| Legend:       |                                 |                                   |                 |                          |                   |                 |       |  |  |

| R = Readabl   | e bit                           | W = Writable                      | bit             | U = Unimpler             | mented bit, read  | l as '0'        |       |  |  |

| -n = Value at | POR                             | '1' = Bit is set                  |                 | '0' = Bit is cle         | ared              | x = Bit is unkr | nown  |  |  |

|               |                                 |                                   |                 |                          |                   |                 |       |  |  |

| bit 15        |                                 | ffer Full Status                  |                 | c                        |                   |                 |       |  |  |

|               |                                 | le Input Buffer                   | 0               | full<br>er registers are | empty             |                 |       |  |  |

| bit 14        |                                 | Buffer Overflow                   | •               |                          | empty             |                 |       |  |  |

|               | •                               |                                   |                 | ffer occurred (n         | nust be cleared   | in software)    |       |  |  |

|               | 0 = No overfl                   |                                   | p <b>,</b>      |                          |                   | ,               |       |  |  |

|               |                                 | . ,                               |                 | y be cleared (=          | 0) in software.   |                 |       |  |  |

| bit 13-12     | Unimplemen                      | ted: Read as '                    | 0'              |                          |                   |                 |       |  |  |

| bit 11-8      | •                               | out Buffer x Sta                  |                 |                          |                   |                 |       |  |  |

|               |                                 | er contains dat<br>er does not co |                 | · ·                      | ading buffer will | clear this bit) |       |  |  |

| bit 7         | OBE: Output                     | Buffer Empty S                    | Status bit      |                          |                   |                 |       |  |  |

|               |                                 | ole Output Buff                   |                 |                          |                   |                 |       |  |  |

|               | 0 = Some or a                   | all of the reada                  | ble Output Bu   | Iffer registers a        | re full           |                 |       |  |  |

| bit 6         | •                               | it Buffer Under                   |                 |                          |                   |                 |       |  |  |

|               |                                 |                                   | empty outpu     | t byte buffer (m         | lust be cleared   | in software)    |       |  |  |

|               | 0 = No under<br>This bit is set |                                   | are: it can onl | v be cleared (=          | 0) in software.   |                 |       |  |  |

| bit 5-4       |                                 | ted: Read as '                    |                 | y se cloarea (           | o) in contra o.   |                 |       |  |  |

| bit 3-0       | •                               | Output Buffer x                   |                 | bits                     |                   |                 |       |  |  |

|               |                                 |                                   |                 |                          |                   |                 |       |  |  |

|               | 1 = Output bu                   | uffer is empty ()                 | writing data to | the buffer will          | clear this bit)   |                 |       |  |  |

## REGISTER 19-13: PMRDIN: PARALLEL MASTER PORT READ INPUT DATA REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0                  | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|--------|------------------------|------------------|-----------------|-------|

|                 |       |                  | RDATAI | N<15:8> <sup>(2)</sup> |                  |                 |       |

| bit 15          |       |                  |        |                        |                  |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0                  | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | RDATA  | IN<7:0> <sup>(2)</sup> |                  |                 |       |

| bit 7           |       |                  |        |                        |                  |                 | bit 0 |

| Legend:         |       |                  |        |                        |                  |                 |       |

| R = Readable    | bit   | W = Writable bi  | it     | U = Unimplen           | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |        | '0' = Bit is cle       | ared             | x = Bit is unkr | nown  |

bit 15-0 RDATAIN<15:0>: Port Read Input Data bits<sup>(2)</sup>

- **Note 1:** This register is only used when the DUALBUF bit (PMCONH<1>) is set to '1' and exclusively for reads. If the DUALBUF bit is '0', the PMDIN1 register (Register 19-7) is used for reads instead of PMRDIN.

- **2:** Only used when MODE16 = 1.

#### REGISTER 22-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS (CONTINUED)

bit 3-0 MOD<3:0>: CCPx Mode Select bits

#### For CCSEL = 1 (Input Capture modes):

- 1xxx = Reserved

- 011x = Reserved

- 0101 = Capture every 16th rising edge

- 0100 = Capture every 4th rising edge

- 0011 = Capture every rising and falling edge

- 0010 = Capture every falling edge

- 0001 = Capture every rising edge

- 0000 = Capture every rising and falling edge (Edge Detect mode)

#### For CCSEL = 0 (Output Compare/Timer modes):

- 1111 = External Input mode: Pulse generator is disabled, source is selected by ICS<2:0>

- 1110 = Reserved

- 110x = Reserved

- 10xx = Reserved

- 0111 = Reserved

- 0110 = Reserved

- 0101 = Dual Edge Compare mode, buffered

- 0100 = Dual Edge Compare mode

- 0011 = 16-Bit/32-Bit Single Edge mode, toggles output on compare match

- 0010 = 16-Bit/32-Bit Single Edge mode, drives output low on compare match

- 0001 = 16-Bit/32-Bit Single Edge mode, drives output high on compare match

- 0000 = 16-Bit/32-Bit Timer mode, output functions are disabled

## REGISTER 24-9: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0   | R/W-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------|---------|---------|-------|-------|-------|

|         |       |       | PTGC0LI | M<15:8> |       |       |       |

| bit 15  |       |       |         |         |       |       | bit 8 |

|         |       |       |         |         |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | PTGC0L  | IM<7:0> |       |       |       |

| bit 7   |       |       |         |         |       |       | bit 0 |

|         |       |       |         |         |       |       |       |

| Legend: |       |       |         |         |       |       |       |

|         |       |       |         |         |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits This register is used to specify the loop count for the PTGJMPC0 Step command or as a Limit register for the General Purpose Counter 0.

Note 1: These bits are read-only when the module is executing Step commands.

## REGISTER 24-10: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| 1      |       |       |          |         |       |       |       |

|--------|-------|-------|----------|---------|-------|-------|-------|

| R/W-0  | R/W-0 | R/W-0 | R/W-0    | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1LII | M<15:8> |       |       |       |

| bit 15 |       |       |          |         |       |       | bit 8 |

|        |       |       |          |         |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0    | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1LI  | M<7:0>  |       |       |       |

| bit 7             |                  |                       |                    | bit 0 |

|-------------------|------------------|-----------------------|--------------------|-------|

|                   |                  |                       |                    |       |

| Legend:           |                  |                       |                    |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | read as '0'        |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |       |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits This register is used to specify the loop count for the PTGJMPC1 Step command or as a Limit register for the General Purpose Counter 1.

**Note 1:** These bits are read-only when the module is executing step commands.

| ) Step<br>Comman            | d OPTION<3:0> | Option Description                                                                   |

|-----------------------------|---------------|--------------------------------------------------------------------------------------|

| PTGWHI(1)                   | 0000          | PTGI0 (see Table 24-3 for input assignments).                                        |

| or                          | •             | •                                                                                    |

| PTGWLO(1)                   | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 1111          | PTGI15 (see Table 24-3 for input assignments).                                       |

| PTGIRQ <sup>(1)</sup>       | 0000          | Generate PTG Interrupt 0.                                                            |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 0111          | Generate PTG Interrupt 7.                                                            |

|                             | 1000          | Reserved; do not use.                                                                |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 1111          | Reserved; do not use.                                                                |

| PTGTRIG                     | 00000         | PTGO0 (see Table 24-4 for output assignments).                                       |

|                             | 00001         | PTGO1 (see Table 24-4 for output assignments).                                       |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 11110         | PTGO30 (see Table 24-4 for output assignments).                                      |

| (1)                         | 11111         | PTGO31 (see Table 24-4 for output assignments).                                      |

| PTGWHI(1)                   | 0000          | PTGI0 (see specific device data sheet for input assignments).                        |

| or<br><sub>PTGWLO</sub> (1) | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •<br>DTC/45 (and specific davies data short for input periodente)                    |

| (1)                         | 1111          | PTGI15 (see specific device data sheet for input assignments).                       |

| PTGIRQ(1)                   | 0000          | Generate PTG Interrupt 0 (see specific device data sheet for interrupt assignments). |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             |                                                                                      |

|                             | 0111          | Generate PTG Interrupt 7 (see specific device data sheet for interrupt assignments). |

|                             | 1000          | Reserved; do not use.                                                                |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 1111          | Reserved; do not use.                                                                |

| PTGTRIG                     | 00000         | PTGO0 (see specific device data sheet for assignments).                              |

|                             | 00001         | PTGO1 (see specific device data sheet for assignments).                              |

## TABLE 24-2: PTG COMMAND OPTIONS (CONTINUED)

Note 1: All reserved commands or options will execute, but they do not have any affect (i.e., execute as a NOP instruction).

| U-1                              | U-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-1                                                                                                                                                                                                                                                                                                         | U-1                                                                                                                                                                                                                                                                                                                                                             | U-1            | U-1                 | U-1            |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------|----------------|

| _                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                               |                | —                   | _              |

| bit 23                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                 |                |                     | bit 16         |

| U-1                              | R/PO-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/PO-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/PO-1                                                                                                                                                                                                                                                                                                      | U-1                                                                                                                                                                                                                                                                                                                                                             | R/PO-1         | R/PO-1              | R/PO-1         |

| —                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CTXT4<2:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                 |                | CTXT3<2:0>          |                |

| bit 15                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                 |                |                     | bit 8          |

| U-1                              | R/PO-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/PO-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/PO-1                                                                                                                                                                                                                                                                                                      | U-1                                                                                                                                                                                                                                                                                                                                                             | R/PO-1         | R/PO-1              | R/PO-1         |

| _                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CTXT2<2:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                               |                | CTXT1<2:0>          |                |

| bit 7                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                 |                |                     | bit C          |

| Legend:                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PO = Progran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | n Once bit                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                 |                |                     |                |