Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 100MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

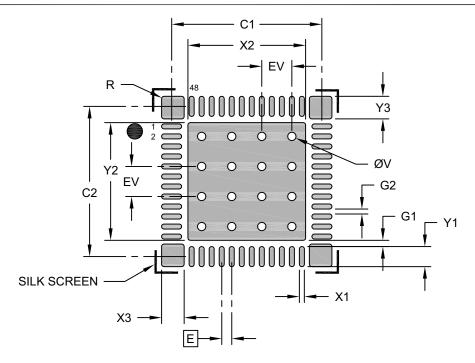

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck256mp506-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: PINOUT                       | I/O DE      | ESCRIP         | TIONS              |                                                          |

|-----------------------------------------|-------------|----------------|--------------------|----------------------------------------------------------|

| Pin Name <sup>(1)</sup>                 | Pin<br>Type | Buffer<br>Type | PPS                | Description                                              |

| U2CTS                                   | I           | ST             | Yes                | UART2 Clear-to-Send                                      |

| U2RTS                                   | 0           |                | Yes                | UART2 Request-to-Send                                    |

| U2RX                                    | I           | ST             | Yes                | UART2 receive                                            |

| U2TX                                    | 0           |                | Yes                | UART2 transmit                                           |

| U2DSR                                   | I.          | ST             | Yes                | UART2 Data-Set-Ready                                     |

| U2DTR                                   | 0           |                | Yes                | UART2 Data-Terminal-Ready                                |

| U3CTS                                   | 1           | ST             | Yes                | UART3 Clear-to-Send                                      |

| U3RTS                                   | Ó           | _              | Yes                | UART3 Request-to-Send                                    |

| U3RX                                    | I           | ST             | Yes                | UART3 receive                                            |

| U3TX                                    | Ö           | _              | Yes                | UART3 transmit                                           |

| U3DSR                                   | Ĭ           | ST             | Yes                | UART3 Data-Set-Ready                                     |

| U3DTR                                   | Ó           | _              | Yes                | UART3 Data-Terminal-Ready                                |

| SCK1                                    | 1/0         | ST             | Yes                | Synchronous serial clock input/output for SPI1           |

| SDI1                                    | 1/0         | ST             | Yes                | SPI1 data in                                             |

| SD01                                    | 0           |                | Yes                | SPI1 data out                                            |

| SS1                                     | 1/0         | ST             |                    | SPI1 slave synchronization or frame pulse I/O            |

| SCK2                                    | 1/0         | ST             | Yes <sup>(3)</sup> |                                                          |

| SDI2                                    |             | ST             |                    | SPI2 data in                                             |

|                                         |             | 51             |                    | SPI2 data out                                            |

| SDO2                                    | 0           |                | Yes <sup>(3)</sup> |                                                          |

| SS2                                     | I/O         | ST             |                    | SPI2 slave synchronization or frame pulse I/O            |

| SCK3                                    | I/O         | ST             | Yes                | Synchronous serial clock input/output for SPI3           |

| SDI3                                    | I           | ST             | Yes                | SPI3 data in                                             |

| SDO3                                    | 0           |                | Yes                | SPI3 data out                                            |

| SS3                                     | I/O         | ST             | Yes                | SPI3 slave synchronization or frame pulse I/O            |

| SCL1                                    | I/O         | ST             | No                 | Synchronous serial clock input/output for I2C1           |

| SDA1                                    | I/O         | ST             | No                 | Synchronous serial data input/output for I2C1            |

| ASCL1                                   | I/O         | ST             | No                 | Alternate synchronous serial clock input/output for I2C1 |

| ASDA1                                   | I/O         | ST             | No                 | Alternate synchronous serial data input/output for I2C1  |

| SCL2                                    | I/O         | ST             | No                 | Synchronous serial clock input/output for I2C2           |

| SDA2                                    | I/O         | ST             | No                 | Synchronous serial data input/output for I2C2            |

| ASCL2                                   | I/O         | ST             | No                 | Alternate synchronous serial clock input/output for I2C2 |

| ASDA2                                   | I/O         | ST             | No                 | Alternate synchronous serial data input/output for I2C2  |

| SCL3                                    | I/O         | ST             | No                 | Synchronous serial clock input/output for I2C3           |

| SDA3                                    | I/O         | ST             | No                 | Synchronous serial data input/output for I2C3            |

| ASCL3                                   | I/O         | ST             | No                 | Alternate synchronous serial clock input/output for I2C3 |

| ASDA3                                   | I/O         | ST             | No                 | Alternate synchronous serial data input/output for I2C3  |

| QEIA1-QEIA2                             | 1           | ST             | Yes                | QEI Inputs A1 and A2                                     |

| QEIB1-QEIB2                             | İ           | ST             | Yes                | QEI Inputs B1 and B2                                     |

| QEINDX1-QEINDX2                         | İ           | ST             | Yes                | QEI Index Inputs 1 and 2                                 |

| QEIHOM1-QEIHOM2                         | i           | ST             | Yes                | QEI Home Inputs 1 and 2                                  |

| QEICMP1-QEICMP2                         | Ó           | _              | Yes                | QEI Comparator Outputs 1 and 2                           |

| SENT1-SENT2                             | -           | ST             | Yes                | SENT1 and SENT2 inputs                                   |

| SENT1-SENT2<br>SENT1OUT-SENT2OUT        | 0           |                | Yes                | SENT1 and SENT2 inputs                                   |

|                                         |             | tible inc      | 1                  |                                                          |

| Legend: CMOS = CMOS<br>ST = Schmitt Tri |             |                |                    |                                                          |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select

O = Output TTL = TTL input buffer I = Input DIG = Digital

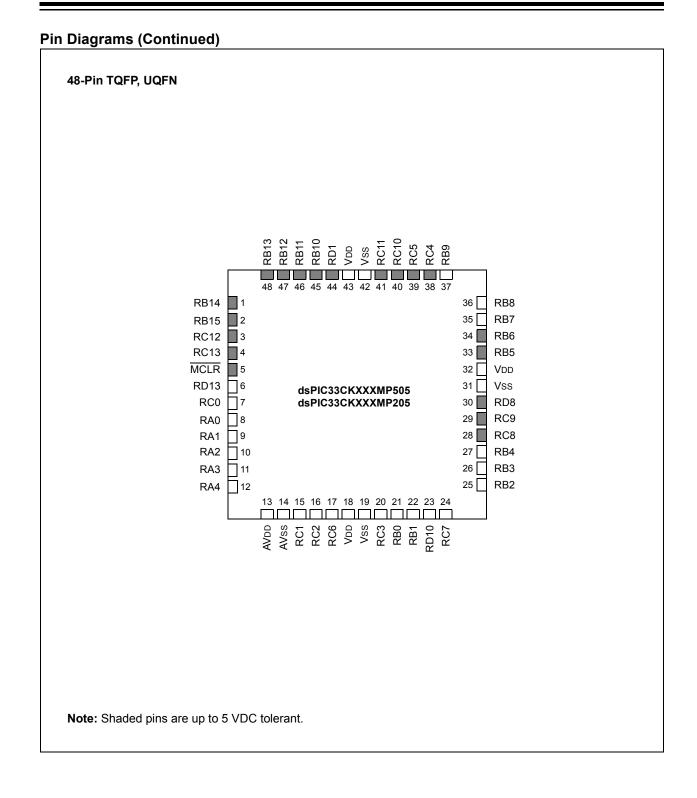

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

2: PWM4L and PWM4H pins are available on PPS as well as dedicated.

**3:** SPI2 supports dedicated pins as well as PPS on 48, 64 and 80-pin devices.

| Pin Name <sup>(1)</sup> | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                   |

|-------------------------|-------------|----------------|-----|-------------------------------------------------------------------------------|

| PGD1                    | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 1                |

| PGC1                    | I           | ST             | No  | Clock input pin for Programming/Debugging Communication<br>Channel 1          |

| PGD2                    | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 2                |

| PGC2                    | I           | ST             | No  | Clock input pin for Programming/Debugging Communication<br>Channel 2          |

| PGD3                    | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 3                |

| PGC3                    | I           | ST             | No  | Clock input pin for Programming/Debugging Communication<br>Channel 3          |

| MCLR                    | I/P         | ST             | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device.    |

| AVDD                    | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times.  |

| AVss                    | Р           | Р              | No  | Ground reference for analog modules. This pin must be connected at all times. |

| Vdd                     | Р           | _              | No  | Positive supply for peripheral logic and I/O pins                             |

| Vss                     | Р           | _              | No  | Ground reference for logic and I/O pins                                       |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog input O = Output TTL = TTL input buffer P = Power I = Input DIG = Digital

Note 1: Not all pins are available in all package variants. See the "Pin Diagrams" section for pin availability.

2: PWM4L and PWM4H pins are available on PPS as well as dedicated.

3: SPI2 supports dedicated pins as well as PPS on 48, 64 and 80-pin devices.

dsPIC33CK256MP508 FAMILY

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0      | U-0 | U-0 | U-0   | U-0    | U-0 | U-0 | U-0   |

|----------|-----|-----|-------|--------|-----|-----|-------|

| —        | —   | —   | —     | —      | —   | —   | —     |

| bit 15   |     |     |       |        |     |     | bit 8 |

| W-0      | W-0 | W-0 | W-0   | W-0    | W-0 | W-0 | W-0   |

|          |     |     | NVMKE | Y<7:0> |     |     |       |

| bit 7    |     |     |       |        |     |     | bit 0 |

|          |     |     |       |        |     |     |       |

| l egend: |     |     |       |        |     |     |       |

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** NVM Key Register bits (write-only)

#### REGISTER 5-5: NVMSRCADR: NVM SOURCE DATA ADDRESS REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0             | R/W-0          | R/W-0          | R/W-0 |

|-----------------|-------|------------------|--------|-------------------|----------------|----------------|-------|

|                 |       |                  | NVMSRC | ADR<15:8>         |                |                |       |

| bit 15          |       |                  |        |                   |                |                | bit 8 |

|                 |       |                  |        |                   |                |                |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0             | R/W-0          | R/W-0          | R/W-0 |

|                 |       |                  | NVMSRC | ADR<7:0>          |                |                |       |

| bit 7           |       |                  |        |                   |                |                | bit 0 |

|                 |       |                  |        |                   |                |                |       |

| Legend:         |       |                  |        |                   |                |                |       |

| R = Readable    | bit   | W = Writable bit |        | U = Unimplem      | ented bit, rea | d as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |        | '0' = Bit is clea | ared           | x = Bit is unk | nown  |

#### bit 15-0 **NVMSRCADR<15:0>:** NVM Source Data Address bits The RAM address of the data to be programmed into Flash when the NVMOP<3:0> bits are set to row programming.

# dsPIC33CK256MP508 FAMILY

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/Os and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 8.5.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

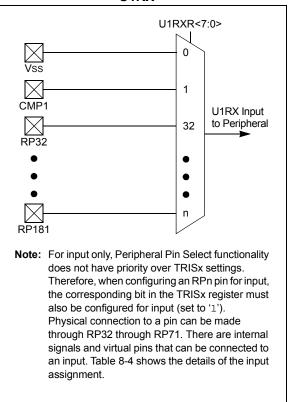

### 8.5.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping. Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit index value maps the RPn pin with the corresponding value, or internal signal, to that peripheral. See Table 8-4 for a list of available inputs.

For example, Figure 8-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 8-2:

#### REMAPPABLE INPUT FOR U1RX

## 8.5.8 I/O HELPFUL TIPS

- In some cases, certain pins, as defined in Table 33-15 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or lesser than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low-side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins, by default, after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Select for PORTx registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristics specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the Absolute Maximum Ratings in Section 33.0 "Electrical Characteristics" of this data sheet. For example:

Vон = 2.4v @ Iон = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 34.0 "DC and AC Device Characteristics Graphs"** for additional information. Unimplemented: Read as '0'

Unimplemented: Read as '0'

(see Table 8-7 for peripheral function numbers)

(see Table 8-7 for peripheral function numbers)

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|-----|------------------|--------|------------------|------------------|-----------------|--------|

| —               | —   | RP57R5           | RP57R4 | RP57R3           | RP57R2           | RP57R1          | RP57R0 |

| bit 15          |     | -                |        |                  |                  |                 | bit 8  |

|                 |     |                  |        |                  |                  |                 |        |

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| —               | _   | RP56R5           | RP56R4 | RP56R3           | RP56R2           | RP56R1          | RP56R0 |

| bit 7           |     |                  |        |                  |                  |                 | bit 0  |

|                 |     |                  |        |                  |                  |                 |        |

| Legend:         |     |                  |        |                  |                  |                 |        |

| R = Readable    | bit | W = Writable     | bit    | U = Unimpler     | nented bit, read | as '0'          |        |

| -n = Value at P | POR | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

RP57R<5:0>: Peripheral Output Function is Assigned to RP57 Output Pin bits

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

#### REGISTER 8-66: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| REGISTER 8-67: | <b>RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13</b> |

|----------------|---------------------------------------------------------|

|              |            |                                     |        |                                         | •••••••          |          |        |

|--------------|------------|-------------------------------------|--------|-----------------------------------------|------------------|----------|--------|

| U-0          | U-0        | R/W-0                               | R/W-0  | R/W-0                                   | R/W-0            | R/W-0    | R/W-0  |

| _            | _          | RP59R5                              | RP59R4 | RP59R3                                  | RP59R2           | RP59R1   | RP59R0 |

| bit 15       |            | ·                                   |        |                                         |                  |          | bit 8  |

|              |            |                                     |        |                                         |                  |          |        |

| U-0          | U-0        | R/W-0                               | R/W-0  | R/W-0                                   | R/W-0            | R/W-0    | R/W-0  |

| —            | —          | RP58R5                              | RP58R4 | RP58R3                                  | RP58R2           | RP58R1   | RP58R0 |

| bit 7        |            |                                     |        |                                         |                  |          | bit C  |

|              |            |                                     |        |                                         |                  |          |        |

| Legend:      |            |                                     |        |                                         |                  |          |        |

| R = Readab   | le bit     | W = Writable                        | bit    | U = Unimpler                            | mented bit, read | d as '0' |        |

| -n = Value a | t POR      | '1' = Bit is set                    |        | '0' = Bit is cleared x = Bit is unknown |                  |          |        |

|              |            |                                     |        |                                         |                  |          |        |

| bit 15-14    | Unimplemen | ted: Read as '                      | 0'     |                                         |                  |          |        |

| bit 13-8     |            | : Peripheral Ou<br>7 for peripheral | •      | •                                       | RP59 Output F    | Pin bits |        |

| bit 7-6      | Unimplemen | ted: Read as '                      | 0'     |                                         |                  |          |        |

bit 5-0 **RP58R<5:0>:** Peripheral Output Function is Assigned to RP58 Output Pin bits (see Table 8-7 for peripheral function numbers)

bit 15-14

bit 13-8

bit 7-6

bit 5-0

#### REGISTER 12-2: FSCL: FREQUENCY SCALE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|----------------|-------|

|                 |       |                  | FSCI  | _<15:8>          |                 |                |       |

| bit 15          |       |                  |       |                  |                 |                | bit 8 |

|                 |       |                  |       |                  |                 |                |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|                 |       |                  | FSC   | L<7:0>           |                 |                |       |

| bit 7           |       |                  |       |                  |                 |                | bit 0 |

|                 |       |                  |       |                  |                 |                |       |

| Legend:         |       |                  |       |                  |                 |                |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimpler     | mented bit, rea | d as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unk | nown  |

bit 15-0 **FSCL<15:0>:** Frequency Scale Register bits The value in this register is added to the frequency scaling accumulator at each pwm\_master\_clk. When the accumulated value exceeds the value of FSMINPER, a clock pulse is produced.

#### REGISTER 12-3: FSMINPER: FREQUENCY SCALING MINIMUM PERIOD REGISTER

| R/W-0            | R/W-0 | R/W-0            | R/W-0  | R/W-0              | R/W-0           | R/W-0           | R/W-0 |

|------------------|-------|------------------|--------|--------------------|-----------------|-----------------|-------|

|                  |       |                  | FSMINP | ER<15:8>           |                 |                 |       |

| bit 15           |       |                  |        |                    |                 |                 | bit 8 |

| R/W-0            | R/W-0 | R/W-0            | R/W-0  | R/W-0              | R/W-0           | R/W-0           | R/W-0 |

|                  |       |                  | FSMINF | PER<7:0>           |                 |                 |       |

| bit 7            |       |                  |        |                    |                 |                 | bit 0 |

| Legend:          |       |                  |        |                    |                 |                 |       |

| R = Readable b   | it    | W = Writable bit |        | U = Unimpleme      | ented bit, read | l as '0'        |       |

| -n = Value at PC | )R    | '1' = Bit is set |        | '0' = Bit is clear | ed              | x = Bit is unkn | own   |

bit 15-0 **FSMINPER<15:0>:** Frequency Scaling Minimum Period Register bits This register holds the minimum clock period (maximum clock frequency) that can be produced by the frequency scaling circuit.

| R/W-0      | R/W-0                                                                       | U-0                                                                                                                                                                               | R/W-0                                                      | U-0              | R/W-0                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0            |  |  |  |

|------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|

| REFCIE     | REFERCIE                                                                    | _                                                                                                                                                                                 | EIEN                                                       | —                | SHREISEL2(1)               | SHREISEL1(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SHREISEL0(1)     |  |  |  |

| bit 15     |                                                                             |                                                                                                                                                                                   |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 8            |  |  |  |

|            |                                                                             |                                                                                                                                                                                   |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |  |  |

| U-0        | R/W-0                                                                       | R/W-0                                                                                                                                                                             | R/W-0                                                      | R/W-0            | R/W-0                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0            |  |  |  |

| _          | SHRADCS6                                                                    | SHRADCS5                                                                                                                                                                          | SHRADCS4                                                   | SHRADCS3         | SHRADCS2                   | SHRADCS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SHRADCS0         |  |  |  |

| bit 7      |                                                                             |                                                                                                                                                                                   |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit C            |  |  |  |

|            |                                                                             |                                                                                                                                                                                   |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |  |  |

| Legend:    |                                                                             |                                                                                                                                                                                   |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |  |  |

| R = Reada  |                                                                             | W = Writable                                                                                                                                                                      |                                                            | -                | nented bit, read           | as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |  |  |  |

| -n = Value | at POR                                                                      | '1' = Bit is set                                                                                                                                                                  |                                                            | '0' = Bit is cle | ared                       | x = Bit is unkno                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | own              |  |  |  |

|            |                                                                             |                                                                                                                                                                                   |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |  |  |

| bit 15     |                                                                             | -                                                                                                                                                                                 | -                                                          | •                | mon Interrupt E            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |  |  |

|            |                                                                             | interrupt will b                                                                                                                                                                  | 0                                                          |                  | gap will become<br>v event | e ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |  |  |  |

| bit 14     |                                                                             |                                                                                                                                                                                   |                                                            | • •              |                            | nable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |  |  |  |

|            |                                                                             | <b>REFERCIE:</b> Band Gap or Reference Voltage Error Common Interrupt Enable bit<br>1 = Common interrupt will be generated when a band gap or reference voltage error is detected |                                                            |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |  |  |

|            |                                                                             |                                                                                                                                                                                   |                                                            |                  | eference voltag            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |  |  |

| bit 13     | Unimplemer                                                                  | ted: Read as                                                                                                                                                                      | 0'                                                         |                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |  |  |