Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck256mp506t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4.4 ARITHMETIC LOGIC UNIT (ALU)

The dsPIC33CK256MP508 family ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70000157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.4.4.1 Multiplier

Using the high-speed, 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.4.4.2 Divider

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/ 16-bit instructions take the same number of cycles to execute. There are additional instructions: DIV2 and DIVF2. Divide instructions will complete in 6 cycles.

#### 3.4.5 DSP ENGINE

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are, ADD, SUB, NEG, MIN and MAX.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed, unsigned or mixed-sign DSP multiply (USx)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

| TABLE 3-2: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation  | ACC<br>Write-Back |  |  |  |

|-------------|-------------------------|-------------------|--|--|--|

| CLR         | A = 0                   | Yes               |  |  |  |

| ED          | $A = (x - y)^2$         | No                |  |  |  |

| EDAC        | $A = A + (x - y)^2$     | No                |  |  |  |

| MAC         | $A = A + (x \bullet y)$ | Yes               |  |  |  |

| MAC         | $A = A + x^2$           | No                |  |  |  |

| MOVSAC      | No change in A          | Yes               |  |  |  |

| MPY         | $A = x \bullet y$       | No                |  |  |  |

| MPY         | $A = x^2$               | No                |  |  |  |

| MPY.N       | $A = -x \bullet y$      | No                |  |  |  |

| MSC         | $A = A - x \bullet y$   | Yes               |  |  |  |

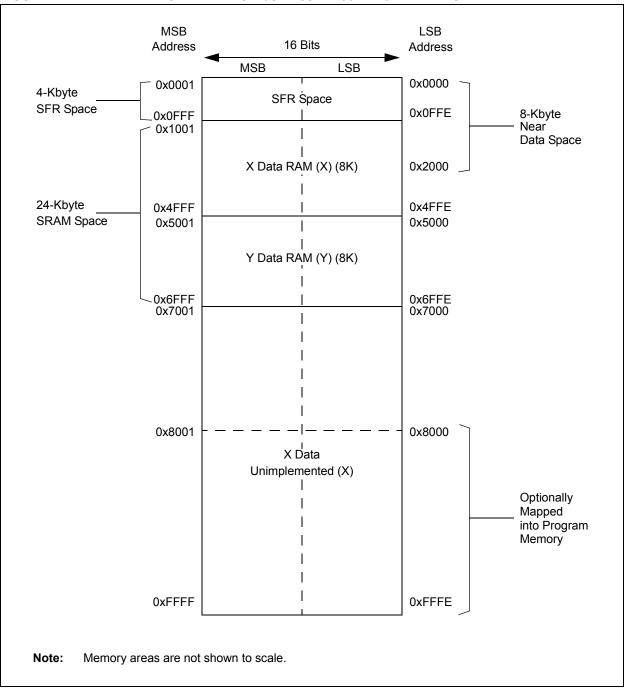

FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33CK256MPX0X DEVICES

## 5.3.2 ERROR CORRECTING CODE (ECC)

In order to improve program memory performance and durability, these devices include Error Correcting Code (ECC) functionality as an integral part of the Flash memory controller. ECC can determine the presence of single bit errors in program data, including which bit is in error, and correct the data automatically without user intervention. ECC cannot be disabled.

When data is written to program memory, ECC generates a 7-bit Hamming code parity value for every two (24-bit) instruction words. The data is stored in blocks of 48 data bits and 7 parity bits; parity data is not memory-mapped and is inaccessible. When the data is read back, the ECC calculates the parity on it and compares it to the previously stored parity value. If a parity mismatch occurs, there are two possible outcomes:

- Single bit error has occurred and has been automatically corrected on readback.

- Double-bit error has occurred and the read data is not changed.

Single bit error occurrence can be identified by the state of the ECCSBEIF (IFS0<13>) bit. An interrupt can be generated when the corresponding interrupt enable bit is set, ECCSBEIE (IEC0<13>). The ECCSTATL register contains the parity information for single bit errors. The SECOUT<7:0> bits field contains the expected calculated SEC parity and the SECIN<7:0> bits contain the actual value from a Flash read operation. The SECSYNDx bits (ECCSTATH<7:0>) indicate the bit position of the single bit error within the 48-bit pair of instruction words. When no error is present, SECINx equals SECOUTx and SECSYNDx is zero.

Double-bit errors result in a generic hard trap. The ECCDBE bit (INTCON4<1>) will be set to identify the source of the hard trap. If no Interrupt Service Routine is implemented for the hard trap, a device Reset will also occur. The ECCSTATH register contains double-bit error status information. The DEDOUT bit is the expected calculated DED parity and DEDIN is the actual value from a Flash read operation. When no error is present, DEDIN equals DEDOUT.

#### 5.3.3 ECC FAULT INJECTION

To test Fault handling, an EEC error can be generated. Both single and double-bit errors can be generated in both the read and write data paths. Read path Fault injection first reads the Flash data and then modifies it prior to entering the ECC logic. Write path Fault injection modifies the actual data prior to it being written into the target Flash and will cause an EEC error on a subsequent Flash read. The following procedure is used to inject a Fault:

- 1. Load the Flash target address into the ECCADDR register.

- Select 1st Fault bit determined by FLT1PTRx (ECCCONH<7:0>). The target bit is inverted to create the Fault.

- If a double Fault is desired, select the 2nd Fault bit determined by FLT2PTRx (ECCCONH<15:8>), otherwise set to all '1's.

- 4. Write the NVMKEY unlock sequence (see Section 5.5.3 "Program Flash Memory Control Registers").

- 5. Enable the ECC Fault injection logic by setting the FLTINJ bit (ECCCONL<0>).

- 6. Perform a read or write to the Flash target address.

### REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                      | •                    |       |       |       |       | bit 8 |

|                      |                      |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N     | OV    | Z     | С     |

| bit 7                |                      |                      |       |       |       |       | bit 0 |

|                      |                      |                      |       |       |       |       |       |

|                      |                      | a a:                 |       |       |       |       |       |

| Legend:           | C = Clearable bit |                        |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** For complete register details, see Register 3-1.

2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

**3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

#### **REGISTER 7-7:** INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0             | U-0                                                                         | R-0                                                   | U-0             | R-0              | R-0               | R-0                | R-0             |  |  |

|-----------------|-----------------------------------------------------------------------------|-------------------------------------------------------|-----------------|------------------|-------------------|--------------------|-----------------|--|--|

| _               | —                                                                           | VHOLD                                                 | —               | ILR3             | ILR2              | ILR1               | ILR0            |  |  |

| bit 15          |                                                                             |                                                       |                 |                  |                   |                    | bit 8           |  |  |

|                 |                                                                             |                                                       |                 |                  |                   |                    |                 |  |  |

| R-0             | R-0                                                                         | R-0                                                   | R-0             | R-0              | R-0               | R-0                | R-0             |  |  |

| VECNUM7         | VECNUM6                                                                     | VECNUM5                                               | VECNUM4         | VECNUM3          | VECNUM2           | VECNUM1            | VECNUM0         |  |  |

| bit 7           |                                                                             |                                                       |                 |                  |                   |                    | bit (           |  |  |

| Legend:         |                                                                             |                                                       |                 |                  |                   |                    |                 |  |  |

| R = Readable    | bit                                                                         | W = Writable                                          | bit             | U = Unimpler     | mented bit, read  | l as '0'           |                 |  |  |

| -n = Value at F | POR                                                                         | '1' = Bit is set                                      |                 | '0' = Bit is cle | ared              | x = Bit is unkr    | nown            |  |  |

|                 |                                                                             |                                                       |                 |                  |                   |                    |                 |  |  |

| bit 15-14       | •                                                                           | ted: Read as '                                        |                 |                  |                   |                    |                 |  |  |

| bit 13          | VHOLD: Vect                                                                 | tor Number Ca                                         | oture Enable b  | oit              |                   |                    |                 |  |  |

|                 |                                                                             |                                                       | l current value | of vector numb   | per encoding tree | e (i.e., highest p | riority pending |  |  |

|                 | interrupt)                                                                  |                                                       | nto VECNII IM<  | 7·0> at Interru  | pt Acknowledge    | and retained u     | Intil nevt IACk |  |  |

| bit 12          |                                                                             | ted: Read as '                                        |                 |                  | ipt Acknowledge   |                    |                 |  |  |

| bit 11-8        | -                                                                           | ew CPU Interru                                        |                 | ol bite          |                   |                    |                 |  |  |

| bit 11-0        |                                                                             | Interrupt Priorit                                     | •               |                  |                   |                    |                 |  |  |

|                 |                                                                             | interrupt i nom                                       |                 |                  |                   |                    |                 |  |  |

|                 |                                                                             | Interrupt Priorit                                     | -               |                  |                   |                    |                 |  |  |

|                 |                                                                             | Interrupt Priorit                                     | 5               |                  |                   |                    |                 |  |  |

| bit 7-0         |                                                                             | 0>: Vector Nun                                        |                 | g Interrupt bits | 6                 |                    |                 |  |  |

|                 |                                                                             | 255, Reserved                                         | ; do not use    |                  |                   |                    |                 |  |  |

|                 |                                                                             | 9, IC1 – Input (                                      | Capture 1       |                  |                   |                    |                 |  |  |

|                 | 00001000 = 8, INTO – External Interrupt 0                                   |                                                       |                 |                  |                   |                    |                 |  |  |

|                 | 00000111 = 7, Reserved; do not use<br>00000110 = 6, Generic soft error trap |                                                       |                 |                  |                   |                    |                 |  |  |

|                 |                                                                             | <ol> <li>Generic soft</li> <li>Reserved; d</li> </ol> |                 |                  |                   |                    |                 |  |  |

|                 |                                                                             | 4, Math error tr                                      |                 |                  |                   |                    |                 |  |  |

|                 | 00000011 =                                                                  | 3, Stack error t                                      | rap             |                  |                   |                    |                 |  |  |

|                 |                                                                             | 2, Generic har                                        |                 |                  |                   |                    |                 |  |  |

|                 |                                                                             | 1, Address erro<br>0, Oscillator fai                  |                 |                  |                   |                    |                 |  |  |

|                 | - 00000000 -                                                                | o, Oscillator Idi                                     | iuap            |                  |                   |                    |                 |  |  |

#### 8.5.10 PERIPHERAL PIN SELECT REGISTERS

## **REGISTER 8-13:** RPCON: PERIPHERAL REMAPPING CONFIGURATION REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|--------|-----|-----|-------|

|        | —   | _   | _   | IOLOCK | —   | —   | —     |

| bit 15 |     |     |     |        |     |     | bit 8 |

|        |     |     |     |        |     |     |       |

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0 | U-0 | U-0   |

|        |     |     | -   | -      |     | _   | —     |

| bit 7  |     |     |     |        |     |     | bit 0 |

|        |     |     |     |        |     |     |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-12 **Unimplemented:** Read as '0'

bit 11 IOLOCK: Peripheral Remapping Register Lock bit

$\ensuremath{\mathtt{1}}$  = All Peripheral Remapping registers are locked and cannot be written

$\ensuremath{\scriptscriptstyle 0}$  = All Peripheral Remapping registers are unlocked and can be written

bit 10-0 Unimplemented: Read as '0'

**Note 1:** Writing to this register needs an unlock sequence.

#### REGISTER 8-14: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| INT1R7 | INT1R6 | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| U-0    |

| —      |        |        | —      | _      | —      | —      |        |

bit 0

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 **INT1R<7:0>:** Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0 Unimplemented: Read as '0'

bit 7

## 9.5 Oscillator Configuration

The oscillator system has both Configuration registers and SFRs to configure, control and monitor the system. The FOSCSEL and FOSC Configuration registers (Register 30-4 and Register 30-5, respectively) are used for initial setup. Table 9-1 lists the configuration settings that select the device's oscillator source and operating mode at a Power-on Reset (POR).

| TABLE 9-1: | CONFIGURATION BIT VALUES FOR CLOCK SELECTION |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

| Oscillator<br>Source | Oscillator Mode                                  | FNOSC<2:0><br>Value | POSCMD<1:0><br>Value | Notes |

|----------------------|--------------------------------------------------|---------------------|----------------------|-------|

| S0                   | Fast RC Oscillator (FRC)                         | 000                 | xx                   | 1     |

| S1                   | Fast RC Oscillator with PLL (FRCPLL)             | 001                 | xx                   | 1     |

| S2                   | Primary Oscillator (EC)                          | 010                 | 00                   | 1     |

| S2                   | Primary Oscillator (XT)                          | 010                 | 01                   |       |

| S2                   | Primary Oscillator (HS)                          | 010                 | 10                   |       |

| S3                   | Primary Oscillator with PLL (ECPLL)              | 011                 | 00                   | 1     |

| S3                   | Primary Oscillator with PLL (XTPLL)              | 011                 | 01                   |       |

| S3                   | Primary Oscillator with PLL (HSPLL)              | 011                 | 10                   |       |

| S4                   | Reserved                                         | 100                 | xx                   |       |

| S5                   | Low-Power RC Oscillator (LPRC)                   | 101                 | xx                   | 1     |

| S6                   | Backup FRC (BFRC)                                | 110                 | xx                   | 1     |

| S7                   | Fast RC Oscillator with ÷ N Divider<br>(FRCDIVN) | 111                 | XX                   | 1, 2  |

Note 1: The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### REGISTER 11-49: C1BDIAG1L: CAN BUS DIAGNOSTICS REGISTER 1 LOW

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                             | R/W-0                              | R/W-0          | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|-----------------------------------|------------------------------------|----------------|-------|-------|--|

|                                    |       |       | EFMSG                             | CNT<15:8>                          |                |       |       |  |

| bit 15                             |       |       |                                   |                                    |                |       | bit 8 |  |

|                                    |       |       |                                   |                                    |                |       |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                             | R/W-0                              | R/W-0          | R/W-0 | R/W-0 |  |

|                                    |       |       | EFMSG                             | GCNT<7:0>                          |                |       |       |  |

| bit 7                              |       |       |                                   |                                    |                |       | bit 0 |  |

|                                    |       |       |                                   |                                    |                |       |       |  |

| Legend:                            |       |       |                                   |                                    |                |       |       |  |

| R = Readable bit W = Writable bit  |       |       | it                                | U = Unimplemented bit, read as '0' |                |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is u |                                    | x = Bit is unk | nown  |       |  |

bit 15-0 EFMSGCNT<15:0>: Error Free Message Counter bits

NOTES:

## REGISTER 12-27: PGxTRIGA: PWM GENERATOR x TRIGGER A REGISTER

| R/W-0                              | R/W-0 | R/W-0           | R/W-0             | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-----------------|-------------------|------------------------------------|--------------------|-------|-------|--|

|                                    |       |                 | PGxTF             | RIGA<15:8>                         |                    |       |       |  |

| bit 15                             |       |                 |                   |                                    |                    |       | bit 8 |  |

| R/W-0                              | R/W-0 | R/W-0           | R/W-0             | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |

|                                    |       |                 | PGxT              | RIGA<7:0>                          |                    |       |       |  |

| bit 7                              |       |                 |                   |                                    |                    |       | bit 0 |  |

|                                    |       |                 |                   |                                    |                    |       |       |  |

| Legend:                            |       |                 |                   |                                    |                    |       |       |  |

| R = Readable                       | e bit | W = Writable bi | t                 | U = Unimplemented bit, read as '0' |                    |       |       |  |

| -n = Value at POR '1' = Bit is set |       |                 | '0' = Bit is clea | ared                               | x = Bit is unknown |       |       |  |

bit 15-0 **PGxTRIGA<15:0>:** PWM Generator x Trigger A Register bits

#### REGISTER 12-28: PGxTRIGB: PWM GENERATOR x TRIGGER B REGISTER

| R/W-0                              | R/W-0 | R/W-0           | R/W-0             | R/W-0        | R/W-0              | R/W-0     | R/W-0 |

|------------------------------------|-------|-----------------|-------------------|--------------|--------------------|-----------|-------|

|                                    |       |                 | PGxTF             | RIGB<15:8>   |                    |           |       |

| bit 15                             |       |                 |                   |              |                    |           | bit 8 |

| R/W-0                              | R/W-0 | R/W-0           | R/W-0             | R/W-0        | R/W-0              | R/W-0     | R/W-0 |

|                                    |       |                 | PGxT              | RIGB<7:0>    |                    |           |       |

| bit 7                              |       |                 |                   |              |                    |           | bit 0 |

| Legend:                            |       |                 |                   |              |                    |           |       |

| •                                  |       |                 |                   |              |                    |           |       |

| R = Readable                       | e bit | W = Writable bi | t                 | U = Unimplen | nented bit, rea    | ad as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                 | '0' = Bit is clea | ared         | x = Bit is unknown |           |       |

bit 15-0 PGxTRIGB<15:0>: PWM Generator x Trigger B Register bits

#### REGISTER 12-29: PGxTRIGC: PWM GENERATOR x TRIGGER C REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                  | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|------------------------------------|-------|-------|----------------------------------------|--------------|-----------------|----------|-------|

|                                    |       |       | PGxTF                                  | RIGC<15:8>   |                 |          |       |

| bit 15                             |       |       |                                        |              |                 |          | bit 8 |

|                                    |       |       |                                        | 54446        |                 | 54446    | -     |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                  | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|                                    |       |       | PGxT                                   | RIGC<7:0>    |                 |          |       |

| bit 7                              |       |       |                                        |              |                 |          | bit 0 |

| Legend:                            |       |       |                                        |              |                 |          |       |

| R = Readable bit W = Writable bit  |       |       | t                                      | U = Unimplen | nented bit, rea | d as '0' |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknow |              |                 | own      |       |

bit 15-0 PGxTRIGC<15:0>: PWM Generator x Trigger C Register bits

# REGISTER 13-27: ADTRIGnL/ADTRIGnH: ADC CHANNEL TRIGGER n(x) SELECTION REGISTERS LOW AND HIGH (x = 0 TO 25; n = 0 TO 6)

| U-0    | U-0 | U-0 | R/W-0        | R/W-0        | R/W-0        | R/W-0        | R/W-0        |

|--------|-----|-----|--------------|--------------|--------------|--------------|--------------|

| _      | —   | _   | TRGSRC(x+1)4 | TRGSRC(x+1)3 | TRGSRC(x+1)2 | TRGSRC(x+1)1 | TRGSRC(x+1)0 |

| bit 15 |     |     |              |              |              |              | bit 8        |

| U-0   | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-------|-----|-----|----------|----------|----------|----------|----------|

|       | —   | —   | TRGSRCx4 | TRGSRCx3 | TRGSRCx2 | TRGSRCx1 | TRGSRCx0 |

| bit 7 |     |     |          |          |          |          | bit 0    |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-13 Unimplemented: Read as '0'

| bit 12-8 | <b>TRGSRC(x+1)&lt;4:0&gt;:</b> Trigger Source Selection for Corresponding Analog Inputs bits (TRGSRC1 to TRGSRC25 – Odd) |

|----------|--------------------------------------------------------------------------------------------------------------------------|

|          | 11111 = ADTRG31 (PPS input)                                                                                              |

|          | 11110 = PTG                                                                                                              |

|          | 11101 = CLC2                                                                                                             |

|          | 11100 = CLC1                                                                                                             |

|          | 11011 = MCCP9                                                                                                            |

|          | 11010 = SCCP7                                                                                                            |

|          | 11001 = SCCP6                                                                                                            |

|          | 11000 <b>= SCCP5</b>                                                                                                     |

|          | 10111 = SCCP4                                                                                                            |

|          | 10110 = SCCP3                                                                                                            |

|          | 10101 <b>= SCCP2</b>                                                                                                     |

|          | 10100 = SCCP1                                                                                                            |

|          | 10011 = PWM8 Trigger 2                                                                                                   |

|          | 10010 <b>= PWM8 Trigger 1</b>                                                                                            |

|          | 10001 = PWM7 Trigger 2                                                                                                   |

|          | 10000 <b>= PWM7 Trigger 1</b>                                                                                            |

|          | 01111 = PWM6 Trigger 2                                                                                                   |

|          | 01110 = PWM6 Trigger 1                                                                                                   |

|          | 01101 = PWM5 Trigger 2                                                                                                   |

|          | 01100 = PWM5 Trigger 1                                                                                                   |

|          | 01011 = PWM4 Trigger 2                                                                                                   |

|          | 01010 = PWM4 Trigger 1                                                                                                   |

|          | 01001 = PWM3 Trigger 2                                                                                                   |

|          | 01000 = PWM3 Trigger 1                                                                                                   |

|          | 00111 = PWM2 Trigger 2                                                                                                   |

|          | 00110 = PWM2 Trigger 1                                                                                                   |

|          | 00101 = PWM1 Trigger 2                                                                                                   |

|          | 00100 = PWM1 Trigger 1                                                                                                   |

|          | 00011 = Reserved                                                                                                         |

|          | 00010 = Level software trigger                                                                                           |

|          | 00001 = Common software trigger<br>00000 = No trigger is enabled                                                         |

|          |                                                                                                                          |

| hit 7_5  | Unimplemented: Read as '0'                                                                                               |

bit 7-5 Unimplemented: Read as '0'

#### REGISTER 13-27: ADTRIGnL/ADTRIGnH: ADC CHANNEL TRIGGER n(x) SELECTION REGISTERS LOW AND HIGH (x = 0 TO 25; n = 0 TO 6) (CONTINUED)

bit 4-0 TRGSRCx<4:0>: Common Interrupt Enable for Corresponding Analog Inputs bits (TRGSRC0 to TRGSRC24 – Even) 11111 = ADTRG31 (PPS input) 11110 = PTG 11101 = CLC2 11100 = CLC1 11011 = MCCP9 11010 = SCCP7 11001 = SCCP6 11000 = SCCP5 10111 = SCCP4 10110 = SCCP3 10101 = SCCP2 10100 = SCCP1 10011 = PWM8 Trigger 2 10010 = PWM8 Trigger 1 10001 = PWM7 Trigger 2 10000 = PWM7 Trigger 1 01111 = PWM6 Trigger 2 01110 = PWM6 Trigger 1 01101 = PWM5 Trigger 2 01100 = PWM5 Trigger 1 01011 = PWM4 Trigger 2 01010 = PWM4 Trigger 1 01001 = PWM3 Trigger 2 01000 = PWM3 Trigger 1 00111 = PWM2 Trigger 2 00110 = PWM2 Trigger 1 00101 = PWM1 Trigger 2 00100 = PWM1 Trigger 1 00011 = Reserved 00010 = Level software trigger 00001 = Common software trigger 00000 = No trigger is enabled

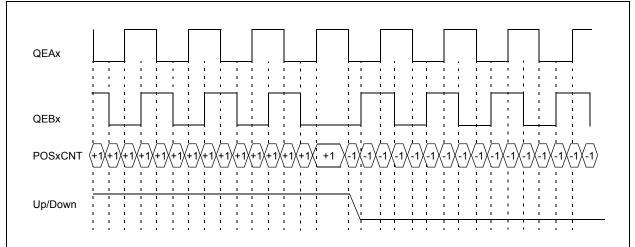

## 15.0 QUADRATURE ENCODER INTERFACE (QEI)

Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive resource. For more information, refer to "Quadrature Encoder Interface (QEI)" (DS70000601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Quadrature Encoder Interface (QEI) module provides the interface to incremental encoders for obtaining mechanical position data. The dsPIC33CK256MP508 family implements 2 instances of the QEI. Quadrature Encoders, also known as incremental encoders or optical encoders, detect position and speed of rotating motion systems. Quadrature Encoders enable closed-loop control of motor control applications, such as Switched Reluctance (SR) and AC Induction Motors (ACIM).

A typical Quadrature Encoder includes a slotted wheel attached to the shaft of the motor and an emitter/ detector module that senses the slots in the wheel. Typically, three output channels, Phase A (QEAx), Phase B (QEBx) and Index (INDXx), provide information on the movement of the motor shaft, including distance and direction.

The two channels, Phase A (QEAx) and Phase B (QEBx), are typically 90 degrees out of phase with respect to each other. The Phase A and Phase B channels have a unique relationship. If Phase A leads Phase B, the direction of the motor is deemed positive or forward. If Phase A lags Phase B, the direction of the motor is deemed negative or reverse. The Index pulse occurs once per mechanical revolution and is used as a reference to indicate an absolute position. Figure 15-1 illustrates the Quadrature Encoder Interface signals.

The Quadrature signals from the encoder can have four unique states ('01', '00', '10' and '11') that reflect the relationship between QEAx and QEBx. Figure 15-1 illustrates these states for one count cycle. The order of the states get reversed when the direction of travel changes.

The Quadrature Decoder increments or decrements the 32-bit up/down Position x Counter (POSxCNTH/L) registers for each Change-of-State (COS). The counter increments when QEAx leads QEBx and decrements when QEBx leads QEAx.

## FIGURE 15-1: QUADRATURE ENCODER INTERFACE SIGNALS

## 18.4 Control Registers

### REGISTER 18-1: I2CxCONL: I2Cx CONTROL REGISTER LOW

| I2CEN<br>pit 15 | U-0                                                                                                                                                                     | R/W-0, HC                           | R/W-1                           | R/W-0                       | R/W-0              | R/W-0            | R/W-0        |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------|-----------------------------|--------------------|------------------|--------------|--|--|--|

| oit 15          |                                                                                                                                                                         | I2CSIDL                             | SCLREL <sup>(1)</sup>           | STRICT                      | A10M               | DISSLW           | SMEN         |  |  |  |

|                 |                                                                                                                                                                         |                                     |                                 | •                           |                    |                  | bit          |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                                   | R/W-0                               | R/W-0, HC                       | R/W-0, HC                   | R/W-0, HC          | R/W-0, HC        | R/W-0, HC    |  |  |  |

| GCEN            | STREN                                                                                                                                                                   | ACKDT                               | ACKEN                           | RCEN                        | PEN                | RSEN             | SEN          |  |  |  |

| Dit 7           | STILLIN                                                                                                                                                                 | AGRUT                               | AGNEN                           | NOLN                        |                    | NOLIN            | bit          |  |  |  |

|                 |                                                                                                                                                                         |                                     |                                 |                             |                    |                  |              |  |  |  |

| Legend:         |                                                                                                                                                                         | HC = Hardware                       | e Clearable bit                 |                             |                    |                  |              |  |  |  |

| R = Readable    | bit                                                                                                                                                                     | W = Writable b                      | bit                             | U = Unimplem                | nented bit, read   | l as '0'         |              |  |  |  |

| n = Value at l  | POR                                                                                                                                                                     | '1' = Bit is set                    |                                 | '0' = Bit is clea           | ared               | x = Bit is unkr  | iown         |  |  |  |

| oit 15          | 12CEN: 12Cx                                                                                                                                                             | Enable bit (writa                   | able from softwa                | are only)                   |                    |                  |              |  |  |  |

|                 | 1 = Enables t                                                                                                                                                           | the I2Cx module                     | , and configure                 | s the SDAx and              |                    | serial port pins | 5            |  |  |  |

| oit 14          | Unimplemen                                                                                                                                                              | ted: Read as '0                     | ,                               |                             |                    |                  |              |  |  |  |

| oit 13          | I2CSIDL: I2C                                                                                                                                                            | x Stop in Idle M                    | ode bit                         |                             |                    |                  |              |  |  |  |

|                 |                                                                                                                                                                         | ues module ope<br>s module operat   |                                 |                             | e mode             |                  |              |  |  |  |

| oit 12          | SCLREL: SC                                                                                                                                                              | Lx Release Cor                      | ntrol bit (I <sup>2</sup> C Sla | ive mode only) <sup>(</sup> | 1)                 |                  |              |  |  |  |

|                 |                                                                                                                                                                         | the SCLx clock                      |                                 |                             |                    |                  |              |  |  |  |

|                 | If STREN = 1                                                                                                                                                            |                                     |                                 |                             |                    |                  |              |  |  |  |

|                 |                                                                                                                                                                         | e may write '0' to                  | initiate a clock                | stretch and wri             | ite '1' to release | e the clock. Har | dware clea   |  |  |  |

|                 |                                                                                                                                                                         | ing of every Sla<br>reception. Hard |                                 |                             |                    |                  | every Slav   |  |  |  |

|                 | If STREN = 0                                                                                                                                                            |                                     |                                 |                             |                    |                  |              |  |  |  |

|                 |                                                                                                                                                                         | e may only write<br>smission. Hard  |                                 |                             |                    |                  |              |  |  |  |

| oit 11          | -                                                                                                                                                                       | K Strict Reserve                    |                                 | -                           |                    |                  |              |  |  |  |

|                 | (In Slave                                                                                                                                                               | erved addressir<br>Mode) – The de   | evice doesn't re                |                             |                    |                  | sses falling |  |  |  |

|                 |                                                                                                                                                                         | gory are NACKe<br>ar Mode) – The    |                                 | ed to generate :            | addresses with     | reserved addr    | ess snace    |  |  |  |

|                 | <ul> <li>(In Master Mode) – The device is allowed to generate addresses with reserved address space.</li> <li>0 = Reserved addressing would be Acknowledged.</li> </ul> |                                     |                                 |                             |                    |                  |              |  |  |  |

|                 |                                                                                                                                                                         | Mode) – The c                       |                                 |                             |                    |                  |              |  |  |  |

|                 |                                                                                                                                                                         | ere is a match w<br>er Mode) – Rese |                                 | eserved addres              | ses, the device    | e will generate  | an ACK.      |  |  |  |

|                 |                                                                                                                                                                         | Slave Address                       |                                 |                             |                    |                  |              |  |  |  |

| oit 10          |                                                                                                                                                                         | is a 10-bit Slav                    | •                               |                             |                    |                  |              |  |  |  |

| pit 10          |                                                                                                                                                                         |                                     |                                 |                             |                    |                  |              |  |  |  |

| oit 10          | 0 = 120  xADD                                                                                                                                                           | is a 7-bit Slave                    | address                         |                             |                    |                  |              |  |  |  |

| oit 10<br>oit 9 | DISSLW: Sle                                                                                                                                                             | w Rate Control                      | Disable bit                     |                             |                    |                  |              |  |  |  |

|                 | DISSLW: Sle                                                                                                                                                             |                                     | Disable bit<br>led for Standar  |                             | •                  | disabled for 1   | MHz mode)    |  |  |  |

2: Automatically cleared to '0' at the beginning of Slave transmission.

NOTES:

# dsPIC33CK256MP508 FAMILY

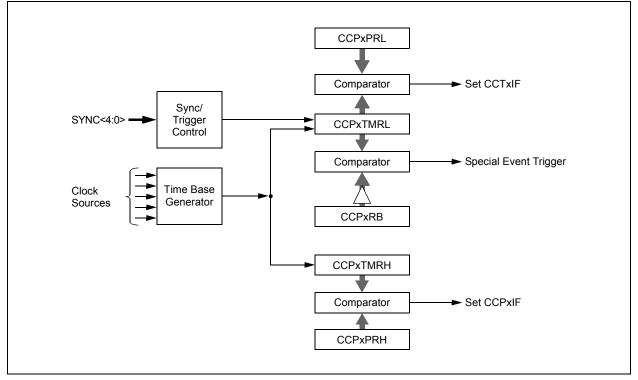

## FIGURE 22-3: DUAL 16-BIT TIMER MODE

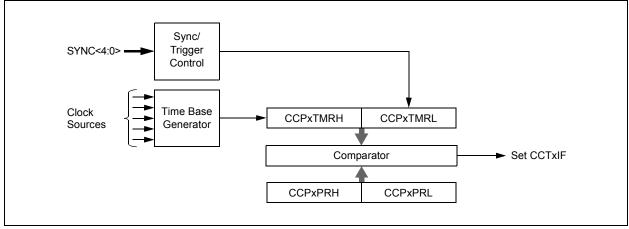

## FIGURE 22-4: 32-BIT TIMER MODE

### REGISTER 30-6: FWDT CONFIGURATION REGISTER

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R/PO-1 | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  |

|--------|---------|---------|---------|---------|---------|---------|---------|

| FWDTEN | SWDTPS4 | SWDTPS3 | SWDTPS2 | SWDTPS1 | SWDTPS0 | WDTWIN1 | WDTWIN0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| R/PO-1 | R/PO-1   | R/PO-1   | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  |

|--------|----------|----------|---------|---------|---------|---------|---------|

| WINDIS | RCLKSEL1 | RCLKSEL0 | RWDTPS4 | RWDTPS3 | RWDTPS2 | RWDTPS1 | RWDTPS0 |

| bit 7  |          |          |         |         |         |         | bit 0   |

| Legend:           | PO = Program Once bit |                             |                    |  |  |

|-------------------|-----------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read | it, read as '0'    |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared        | x = Bit is unknown |  |  |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                 |

|-----------|----------------------------------------------------------------------------------------------------------------------------|

| bit 15    | FWDTEN: Watchdog Timer Enable bit                                                                                          |

|           | 1 = WDT is enabled in hardware                                                                                             |

|           | 0 = WDT controller via the ON bit (WDTCONL<15>)                                                                            |

| bit 14-10 | SWDTPS<4:0>: Sleep Mode Watchdog Timer Period Select bits                                                                  |

|           | 11111 = Divide by 2 ^ 30 = 1,073,741,824                                                                                   |

|           | 11110 = Divide by 2 ^ 29 = 526,870,912                                                                                     |

|           | 00001 = Divide by 2 ^ 2, 4                                                                                                 |

|           | 00000 = Divide by 2 ^ 1, 2                                                                                                 |

| bit 9-8   | WDTWIN<1:0>: Watchdog Timer Window Select bits                                                                             |

|           | 11 = WDT window is 25% of the WDT period                                                                                   |

|           | 10 = WDT window is 37.5% of the WDT period                                                                                 |

|           | 01 = WDT window is 50% of the WDT period<br>00 = WDT Window is 75% of the WDT period                                       |

| bit 7     | WINDIS: Watchdog Timer Window Enable bit                                                                                   |

| bit 7     | 1 = Watchdog Timer is in Non-Window mode                                                                                   |

|           | 0 = Watchdog Timer is in Window mode                                                                                       |

| bit 6-5   | RCLKSEL<1:0>: Watchdog Timer Clock Select bits                                                                             |

|           | 11 = LPRC clock                                                                                                            |

|           | 10 = Uses FRC when WINDIS = 0, system clock is not INTOSC/LPRC and device is not in Sleep;                                 |

|           | otherwise, uses INTOSC/LPRC<br>01 = Uses peripheral clock when system clock is not INTOSC/LPRC and device is not in Sleep; |

|           | otherwise, uses INTOSC/LPRC                                                                                                |

|           | 00 = Reserved                                                                                                              |

| bit 4-0   | RWDTPS<4:0>: Run Mode Watchdog Timer Period Select bits                                                                    |

|           | 11111 = Divide by 2 ^ 30 = 1,073,741,824                                                                                   |

|           | 11110 = Divide by 2 ^ 29 = 526,870,912                                                                                     |

|           | 00001 = Divide by 2 ^ 2, 4                                                                                                 |

|           | 00000 = Divide by 2 ^ 1, 2                                                                                                 |

|           |                                                                                                                            |

| Base<br>Instr<br># | Assembly<br>Mnemonic |         |                   | # of<br>Words                                       | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |             |

|--------------------|----------------------|---------|-------------------|-----------------------------------------------------|-------------------------------|--------------------------|-------------|

| 1                  | ADD                  |         |                   | Add Accumulators                                    | 1                             | 1                        | OA,OB,SA,SB |

|                    |                      | ADD     | f                 | f = f + WREG                                        | 1                             | 1                        | C,DC,N,OV,Z |

|                    |                      | ADD     | f,WREG            | WREG = f + WREG                                     | 1                             | 1                        | C,DC,N,OV,Z |

|                    |                      | ADD     | #lit10,Wn         | Wd = lit10 + Wd                                     | 1                             | 1                        | C,DC,N,OV,Z |

|                    |                      | ADD     | Wb,Ws,Wd          | Wd = Wb + Ws                                        | 1                             | 1                        | C,DC,N,OV,Z |

|                    |                      | ADD     | Wb,#lit5,Wd       | Wd = Wb + lit5                                      | 1                             | 1                        | C,DC,N,OV,Z |

|                    |                      | ADD     | Wso,#Slit4,Acc    | 16-bit Signed Add to Accumulator                    | 1                             | 1                        | OA,OB,SA,SB |

| 2                  | ADDC                 | ADDC    | f                 | f = f + WREG + (C)                                  | 1                             | 1                        | C,DC,N,OV,Z |

|                    |                      | ADDC    | f,WREG            | WREG = $f + WREG + (C)$                             | 1                             | 1                        | C,DC,N,OV,Z |

|                    |                      | ADDC    | #lit10,Wn         | Wd = lit10 + Wd + (C)                               | 1                             | 1                        | C,DC,N,OV,Z |

|                    |                      | ADDC    | Wb,Ws,Wd          | Wd = Wb + Ws + (C)                                  | 1                             | 1                        | C,DC,N,OV,Z |

|                    |                      | ADDC    | Wb,#lit5,Wd       | Wd = Wb + lit5 + (C)                                | 1                             | 1                        | C,DC,N,OV,Z |

| 3                  | AND                  | AND     | f                 | f = f .AND. WREG                                    | 1                             | 1                        | N,Z         |

|                    |                      | AND     | f,WREG            | WREG = f .AND. WREG                                 | 1                             | 1                        | N,Z         |

|                    |                      | AND     | #lit10,Wn         | Wd = lit10 .AND. Wd                                 | 1                             | 1                        | N,Z         |

|                    |                      | AND     | Wb,Ws,Wd          | Wd = Wb .AND. Ws                                    | 1                             | 1                        | N,Z         |

|                    |                      | AND     | Wb,#lit5,Wd       | Wd = Wb .AND. lit5                                  | 1                             | 1                        | N,Z         |

| 4                  | ASR                  | ASR     | f                 | f = Arithmetic Right Shift f                        | 1                             | 1                        | C,N,OV,Z    |

|                    |                      | ASR     | f,WREG            | WREG = Arithmetic Right Shift f                     | 1                             | 1                        | C,N,OV,Z    |

|                    |                      | ASR     | Ws,Wd             | Wd = Arithmetic Right Shift Ws                      | 1                             | 1                        | C,N,OV,Z    |

|                    |                      | ASR     | Wb,Wns,Wnd        | Wnd = Arithmetic Right Shift Wb by Wns              | 1                             | 1                        | N,Z         |

|                    |                      | ASR     | Wb,#lit5,Wnd      | Wnd = Arithmetic Right Shift Wb by lit5             | 1                             | 1                        | N,Z         |

| 5                  | BCLR                 | BCLR    | f,#bit4           | Bit Clear f                                         | 1                             | 1                        | None        |

|                    |                      | BCLR    | Ws,#bit4          | Bit Clear Ws                                        | 1                             | 1                        | None        |

| 6                  | BFEXT                | BFEXT   | bit4,wid5,Ws,Wb   | Bit Field Extract from Ws to Wb                     | 2                             | 2                        | None        |

|                    |                      | BFEXT   | bit4,wid5,f,Wb    | Bit Field Extract from f to Wb                      | 2                             | 2                        | None        |

| 7                  | BFINS                | BFINS   | bit4,wid5,Wb,Ws   | Bit Field Insert from Wb into Ws                    | 2                             | 2                        | None        |

|                    |                      | BFINS   | bit4,wid5,Wb,f    | Bit Field Insert from Wb into f                     | 2                             | 2                        | None        |

|                    |                      | BFINS   | bit4,wid5,lit8,Ws | Bit Field Insert from #lit8 to Ws                   | 2                             | 2                        | None        |

| 8                  | BOOTSWP              | BOOTSWP |                   | Swap the Active and Inactive Program Flash<br>Space | None                          |                          |             |

#### TABLE 31-2: INSTRUCTION SET OVERVIEW

Note 1: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

2: The divide instructions must be preceded with a "REPEAT #5" instruction, such that they are executed six consecutive times.

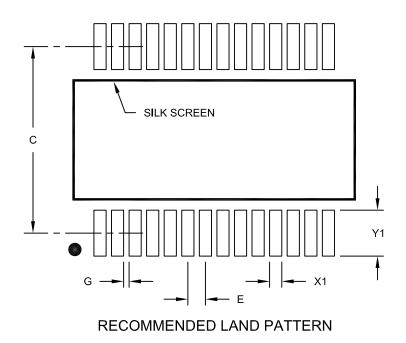

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension Limits         |             | MIN      | NOM  | MAX  |

| Contact Pitch            | E           | 0.65 BSC |      |      |

| Contact Pad Spacing      | С           |          | 7.20 |      |

| Contact Pad Width (X28)  | X1          |          |      | 0.45 |

| Contact Pad Length (X28) | Y1          |          |      | 1.75 |

| Distance Between Pads    | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A